数字电路第八章

数字集成电路第8章

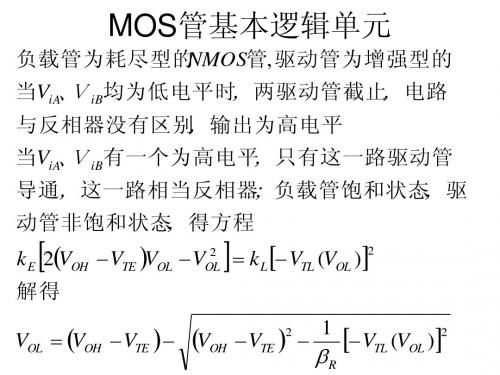

最坏情况, 只有一个驱动管导通时 的VoL 值, 对于给定

2 Gon Ron

2 VOL I D kE VOH VTE VOL 2 I D / VOL k E VOH VTE VOL

Gon k A VOH VTE VOL k B VOH VTE VOL

改进多米诺CMOS逻辑

• 省掉多米诺缓冲器,级联的各逻辑块交替地 由P型管和N型管构成 • 当¢=0,第一级预充到高电平(NMOS管逻辑), 第二级预充到低电平,第三级预充到高电平. • 由于第二级由PMOS管构成,在预充电期间, PMOS管都处于截止状态. • 由于第二级预充到低电平,第三级NMOS管也 都处于截止状态. • 因此可以进行多米诺连接

A B R L L

2VTL (VOL )

2 2 OL

VOH

VTD VOL

V 2

NMOS与非门

R 相当倒相器的两倍 , 要得到相同的

VOL 与非门每个驱动门所占 芯片面积相 当倒相器的两倍 ; 两个驱动管相串联 , 导通时等效电阻等于两 者之和 RON RONA RONB RON 2 RONA 2 RONB

NMOS与非门输出电容

VB VOH VB 0 或 V A VOH V A VOH COUT CGDA CGSA CGDB CGDL C LINE CG k (VOH , VOL )(C DBA C SBA C DBB C SBL ) V A 0 VB 0 或 VB VOH V A 0 COUT CGDA CGDL C LINE CG k (VOH , VOL )(C DBA C SBL )

数字电路与逻辑设计第八章

A B C

A B C & D (a)

& D

9

(b)

第八章

可编程逻辑器件

二. 输入缓冲器 典型输入缓冲器的PLD表示 法如右图所示。它的两个输出 A B、C是其输入A的原和反(见 图中真值表)。

1

B

C

A B C 0 0 1 1 1 0

三. 连接方式 PLD阵列交叉点上的三种连接方式如图(a)所示。实点“·” 表示硬线连接,即固定连接;“×”表示可编程连接;没有 “×” 和“·”的表示两线不连接。如图(b)中的输出F=A· C。

25

第八章

可编程逻辑器件

产品在出厂时,所有FAMOS的浮栅均不带电,FAMOS管处于截止状态。 写入信息时,在对应单元的漏极加上足够高的负压,使漏极与衬底之 间的PN结击穿,雪崩击穿产生的高能电子穿过SiO2层堆积在浮置栅上,使 FAMOS管导通。对应FAMOS管的截止或导通,可使位线上输出的电平为高或 低,以表示该存储元存放的信息是“1”或“0”。 由于浮栅被绝缘的二氧化硅包着,编程时堆积的电子设有放电回路, 故电荷不会消失,信息能够长期保存。 如果用紫外线照射FAMOS管,则浮栅上积累的电子将形成光电流而泄放, 从而导电沟道消失,管子又恢复截止状态。 为了使编程后能进行擦除和重写,在芯片的封装外壳装有透明的石英 窗口。对编程好的EPROM要用不透光的胶纸将受光窗口封住,以免信息丢失。

PLD“与”阵列的输入为外部输入原变量及在阵列中经过反 相后的反变量。它们按所要求的规律连接到各个与门的输入端, 并在各与门的输出端产生某些输入变量的“与”项作为“或” 阵列的输入,这些“与”项按一定的要求连接到相应或门的输 入端,在每个或门的输出端产生输入变量的“与-或”函数表 达式。

第八章 数字集成电路基本单元及版图

§7.数字电路标准单元库设计简介

基本设计思想 用人工设计好的各种成熟的、优化的、 版图等高的单元电路,存储在一个单元数据 库中。根据用户的要求,把电路分成各个单 元的连接组合。通过调用单元库的这些单元, 以适当方式把它们排成几行,使芯片成长方 形,行间留出足够的空隙作为单元行间的连 线通道。利用EDA工具,根据已有的布局、 布线算法,可以自动布出用户所要求的IC。

TTL基本电路及版图实现

IC的版图设计已把电路与工艺融为一体,所以一般 较复杂的电路都是先设计实验电路(或单元电路), 根据实验电路的测试结果获得有关电路功能和电路 参数的第一手资料。 掌握了这些资料,就可以根据元件的不同要求,在 设计中采取相应措施,保证电路达到设计目标。必 要时还要调整个别工艺或工艺参数。 当然设计出的版图要经过实践不断加以改进,一个 成熟的产品一般都要经过几次改版才行。

υ1

T3 Re2

负 载

v0 -

-

GND

TTL基本电路

(1)电路组成 该电路由三部分组成: 1)由双极型晶体管T1和电阻Rb1组成电路输入级。 2)由T2、Re2和Rc2组成中间驱动电路,将单端信号 υB2转换为双端信号υB3和υB4。 3)由T3、T4、Rc4和二级管D组成输出级。 (2)工作原理 输入为高电平时,输出为低电平。 输入为低电平时,输出为高电平。

CMOS反相器

瞬态特性

我们希望反相器的上升时间和下降时间近似相等,则 需要使PMOS管的沟道宽度必须加宽到NMOS管沟道 宽度的 n / p倍左右。 V (t)

i

+VDD 0 t Vo(t) +VDD 0.9VDD 0.1VDD 0

td tf tr

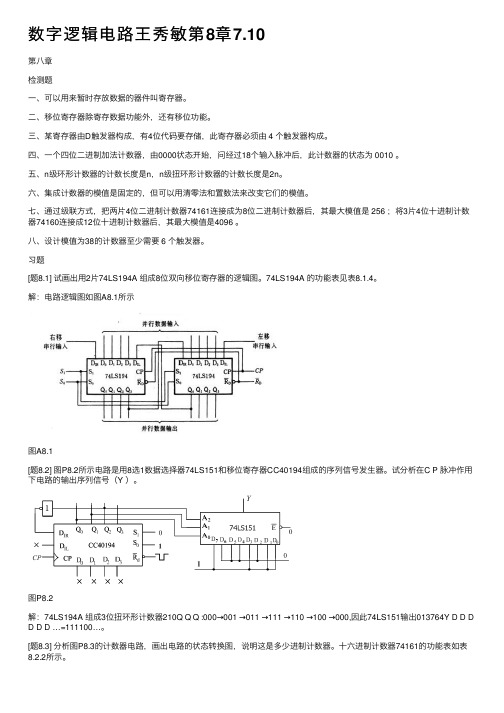

数字逻辑电路王秀敏第8章7.10

数字逻辑电路王秀敏第8章7.10第⼋章检测题⼀、可以⽤来暂时存放数据的器件叫寄存器。

⼆、移位寄存器除寄存数据功能外,还有移位功能。

三、某寄存器由D触发器构成,有4位代码要存储,此寄存器必须由 4 个触发器构成。

四、⼀个四位⼆进制加法计数器,由0000状态开始,问经过18个输⼊脉冲后,此计数器的状态为 0010 。

五、n级环形计数器的计数长度是n,n级扭环形计数器的计数长度是2n。

六、集成计数器的模值是固定的,但可以⽤清零法和置数法来改变它们的模值。

七、通过级联⽅式,把两⽚4位⼆进制计数器74161连接成为8位⼆进制计数器后,其最⼤模值是 256 ;将3⽚4位⼗进制计数器74160连接成12位⼗进制计数器后,其最⼤模值是4096 。

⼋、设计模值为38的计数器⾄少需要 6 个触发器。

习题[题8.1] 试画出⽤2⽚74LS194A 组成8位双向移位寄存器的逻辑图。

74LS194A 的功能表见表8.1.4。

解:电路逻辑图如图A8.1所⽰图A8.1[题8.2] 图P8.2所⽰电路是⽤8选1数据选择器74LS151和移位寄存器CC40194组成的序列信号发⽣器。

试分析在C P 脉冲作⽤下电路的输出序列信号(Y )。

图P8.2解:74LS194A 组成3位扭环形计数器210Q Q Q :000→001 →011 →111 →110 →100 →000,因此74LS151输出013764Y D D D D D D …=111100…。

[题8.3] 分析图P8.3的计数器电路,画出电路的状态转换图,说明这是多少进制计数器。

⼗六进制计数器74161的功能表如表8.2.2所⽰。

图P8.3解:采⽤同步预置数法,31LD Q Q =。

计数器起始状态为0011,结束状态为1010,所以该计数器为⼋进制加法计数器。

状态转换图略。

[题8.4] 分析图P8.4的计数器电路,说明这是多少进制的计数器,并画出电路的状态转换图。

⼗进制计数器74160的功能表如表8.2.6所⽰。

数电第8章

系统具有加密功能:多数PLD器件,如GAL 或高密度可编程逻辑器件,本身具有加密功 能。设计者在设计时选中加密项,可编程逻 辑器件就被加密。器件的逻辑功能无法被读 出,有效地防止电路被抄袭。

2018/11/11

数字电路逻辑设计

8

8.2 可编程逻辑器件PLD概述

PLD是70年代发展起来的新型逻辑器件,相继出现 了ROM 、 FPLA、PAL 、GAL、EPLD和FPGA及 由输入缓冲器构成,产生输 由或门阵列构成,将与阵列输出的乘积项有 由与门阵列构成,产生输 由三态门寄存器构成,产生 isp等。前四种属于低密度 PLD,后三种属高密度 入变量的原变量和反变量 选择的进行或运算,形成与或式,实现函数 入变量的与项(乘积项) 输出信号,提供反馈信号 PLD。 PLD的基本结构

数字电路逻辑设计 13

2018/11/11

80年代中期的PLD:通用阵列逻辑(GAL)器件问世 ,并取代了PAL。GAL器件是在PAL器件基础上发 展起来的新一代器件。和PAL一样,它的与门阵列 是可编程的,或门阵列是固定的。但由于采用了高 速电可擦CMOS工艺,可以反复擦除和改写,很适 宜于样机的研制。它具有CMOS低功耗特性,且速 度可以与TTL可编程器件相比。特别是在结构上采 用了“输出逻辑宏单元”电路,为用户提供了逻辑 设计和使用上的较大灵活性。

通用集成电路:集成电路是指常用的中、小规模数 字电路(如74系列、4000系列等),其逻辑功能设 计以实现数字系统的基本功能块为目的,一般比较 简单,并且固定不变。 优点:通用性强,使用方便灵活。 缺点:体积、功耗和重量较大,可靠性和可维护性 较差等。

数字电子技术基础 2

2018/11/11

专用型集成电路(ASIC)

精品大学课件--南开大学数字电子--第八章

本文档由标准美女(标准王国)整理,仅作学习交流使用。

如文档存在缺页、字迹模糊、乱码等情况,请大家通过论坛消息与我联系。

第八章数—模(D/A)和模-数(A/D)转换指标:转换精度——转换结果的准确程度。

转换速度——转换的快慢。

D/A 转换有: 权电阻网络型、T 型网络型、权电流网络型等。

A/D 转换有: 直接型、间接型。

8.1 D/A 转换器如果有一电路,其输出电压与输入的数字量成正比,即可作D/A 转换器。

一、权电阻网络D/A 转换器 1、电路2、原理 由图知)2222(22222001122333031221300123⨯+⨯+⨯+⨯=+++=d d d d R V d R V d R V d R V d R V I I I I i REF REFREF REF REF =+++440011223342)2222(22D V d d d d V Ri V REF REF o -=⨯+⨯+⨯+⨯-=⋅-= (d 为0或1) 如果n 位,则 n REFo D V V 42-= 。

。

~-的变化范围为REF n n o V V 2120- 缺点:电阻相差太大,精度难保证,不便集成。

二、倒T 型电阻网络DAC 由电阻网络、模拟开关(电子开关)、运放三部分组成。

V REF 是参考电压。

S 是电子开关,d 是数字信号,1时S 接参考电压,0时接地。

1、电路2、原理由于反相端为虚地,所以,总电流I 不变,各电阻支路电流也不变。

RV I REF =4400112233401232)2222(2)16842(D V d d d d V d Id I d I d I R R i V REF REF o -=⨯+⨯+⨯+⨯-=+++-=⋅-= 同样,若n 位,则 n nREF o D VV 2-=。

优点: 电阻种类少,精度高;各支路电路直接流入运放,不存在时间差,所以无尖峰脉冲。

且转换速度快。

是用的最多的一种DAC 。

数字电路课件:第8章 半导体存储器与总线接口-教学

CS O7

OE

13

U2

...

~ 数据总线 D7

D0 8

...

A02764

8.. O0Fra bibliotek. ... ... A12

CS O7

OE U8

8-4 可编程逻辑阵列(PLA)

一、概述

PLD中的连接及与、或运算符号

内部存储单元的三种连接方式:固定、擦除及编程

t WR t DH

1.位扩展

三. RAM的容量扩展

用8片1024(1K)×1位RAM构成的1024×8位RAM系统。

I /O 0

I /O1

I /O7

I/O 1024×1RA M

... A0 A1 A9 R/W CS

I/O

I/O

1024×1RA M

...

1024×1RA M

... A0 A1 A9 R/W CS

码

入

器

An- 1

...

...

W0 字线 W1

Wi

W2n- 1

...

...

存储单元

0单元 1单元

i单元

2n-1 单元

...

位线

D0 D1

Db- 1

输出数据

2. ROM的基本 A1

工作原理:

由地址译码器

A0

和或门存储矩阵组成。

地

W0

址 W1

译

W2

码

W3

器

例:存储容量为 4×4的ROM

≥1 D3 ≥1 D2 ≥1 D1 ≥1 D0

用8片2764扩展成64k×8位的EPROM:

13

~地址总线 13

A0 A12 OE

...

数电第八章57页PPT

0

vd

0

vO

1

v

0

I2

V DD V TH

0 vO

0

tw

t1

t2

I2

vO1

t

t

I2 =VTH产生如下正反馈过程:

vI2 vO vO1

迅速使 o1 = 1 o =0 电容放电 c =0

电路由暂稳态自动返回到稳态

1

0

t

vO1

vO

G1 1

t

vI Cd

vd

Rd

t

1 G2

CD

v

C

v I2 R

vO

A1

A2 B vI

A2

Q

B

Q

VCC

vI

0 vO1

t1 tw1

0 vO

tw2

0

t tw1

t

tw2 t

4. 组成噪声消除电路

如用I作为下降沿触发的计数器触发脉冲,干扰加入,就会造 成计数错误.

C

R

VCC

Cext Rext/Cext

噪声

7412

A1 1

Q

A2

Q

1D C1

vI

vO

Q

vI

B

R

vO

单稳触发器的输出脉宽应大于噪声宽度而小于信号脉宽,才可 消除噪声。

VT+

(1

R1 R2

)VTH

(3) υI1 VTH电路,维持 υ O=VOH 不变

(4)当υI下降, υI1也下降 ,只要υI1 > VTH, 则保持 υo =VOH

当 υI1 =VTH,电路产生如下正反馈 :

R2