基于FPGA的视频图像采集与处理系统设计

基于FPGA的图像采集卡的设计

基于FPGA的图像采集卡的设计1 引言现代化生产和科学研究对视频图像采集系统的要求日益提高。

传统的图像采集卡速度慢、处理功能简单、采用分立元件、电路非常复杂;而且可靠性差、不易调试、不能很好地满足特殊要求。

FPGA(现场可编程门阵列)是专用集成电路中集成度最高的一种,用户可对FPGA 内部的逻辑模块和I/O模块重新配置,以实现用户所需逻辑功能。

用户对FPGA的编程数据放入芯片,通过上电加载到FPGA中,对其进行初始化;也可在线对其编程,实现系统在线重构。

基于FPGA技术的图像采集主要是通过集成的FPGA开发板,使用软件编程把图像的采集控制程序写入FPGA开发板的芯片上,通过仿真技术来进行图像的采集处理分析。

通过这种方式,便于及时地发现设计中的错误,从而有效地缩短研发时间。

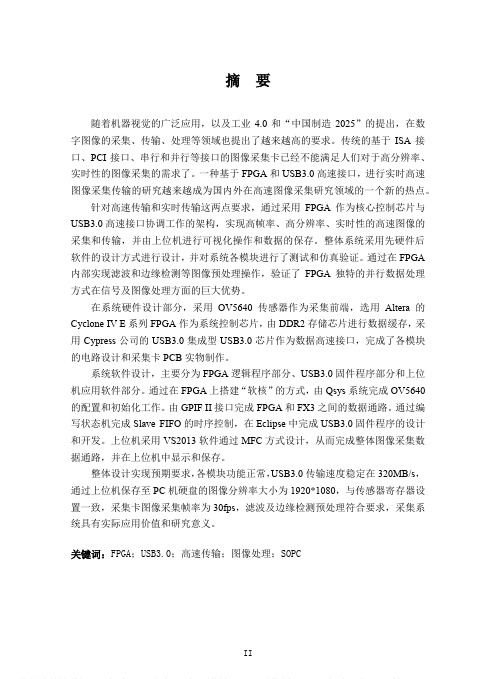

2 系统的组成及基本原理该图像采集系统主要由模拟视频信号解码模块,I2C控制接口模块,采样控制模块,SDRAM 存储控制模块。

SAA7113H芯片把从CCD采集来的模拟视频信号转化成YUV=422格式的数字图像信号。

这些信号在同步脉冲的作用下进入采集控制器。

采样控制器在奇偶场控制信号下把图像信息存入SDRAM中。

该系统可以实现由隔行扫描图像到逐行图像的转化及存储。

2.1模拟视频信号解码由于SAA7113H芯片具有I2C接口,该模块则通过I2C总线来配置SAA7113H初始化的信息。

工作涉及SAA7113H的初始化字的配置、工作方式的配置;行同步开始和结束标志位、确定亮度、色度、饱和度的大小以及输出图像数据信号的格式。

2.2 I2C控制接口模块I2C模块作为SAA7113H寄存器初始配置的整体控制模块。

具体可以分成I2C_cmd和数据传输2个模块I2C_cmd模块为纯组合逻辑电路,完成信号的发送控制任务,配合rom_data[7.0]和rom_addr[7.0]信号完成数据的寻址与存入等工作;而数据传输模块主要和I2C_cmd模块一起组合成I2C的数据控制写入模块,他主要负责对I2C_cmd模块的输出信号进行缓存,并在其输出端输出I2C总线的串行数据SDA以及I2C总线的串行时钟信号SCL。

基于FPGA的MIPI CSI-2图像采集系统设计

基于FPGA的MIPI CSI-2图像采集系统设计赵清壮【摘要】This paper elaborates a design of MIPI CSI-2 high-definition camera interface image acquisition system based on FPGA. Now, MIPI high-definition CCD is used widely, this design uses FPGA to achieve MIPI high-definition CCD collect and provides two outputs of LCD screen and USB, the data transmission is stable and reliable, it make MIPI interface camera applied widely by the other circuit systems, accelerates system development and saves cost.%阐述一种基于FPGA的MIPI CSI-2接口高清摄像头图像采集系统设计,该设计用FPGA实现当前应用广泛的MIPI高清CCD采集,并提供LCD屏、USB两路输出,数据传输稳定可靠,把MIPI接口摄像头应用到更广泛的其他电路系统中,加快系统开发,节省成本。

【期刊名称】《价值工程》【年(卷),期】2015(000)029【总页数】2页(P84-85)【关键词】MIPI;CSI-2;图像采集;FPGA【作者】赵清壮【作者单位】广州飒特红外特股份有限公司,广州510000【正文语种】中文【中图分类】TP302.10 引言CSI(Camera Serial Interface)是由MIPI(Mobile Industry Processor Interface)联盟下Camera工作组制定的接口标准,是MIPI联盟发起的为移动应用处理器制定的开放标准,MIPI联盟由ARM、诺基亚、意法半导体和德州仪器发起成立,作为移动行业领导者的合作组织,MIPI联盟旨在确定并推动移动应用处理器接口的开放性标准。

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的视频采集显示系统

随着 高 品质 实 时 视 频 显示 技 术 低 , 民用 领域 如 天 气预报 、 资源探测 、 机器 人 视觉 以及 各 种医学 图像 的实 时分 析 ; 军 用 领域 如 导 弹精 确 制 导 、 战场 动 态分 析 等 , 均需要 高 质量实 时视 频显 示 系统 的支 持 。近年 来低 成 本的 F P G A( F i l e d P r o g r a m ma b l e G a t e A r r a y ) 不 断 推 陈 出新 , 利用 E D A工具对 F P G A芯 片 进 行 多 样 性 设 计 , 已经 成为 电子设 计 的通 用 平 台 , 并逐 步 向支 持 系统 级 设计 的方 向发 展 。 与专 用 集 成 电 路 相 比 , F P G A芯 片 具有 快速 的定 制 性 和 高灵 活 性 , 扩 展 性 强 的特 点 。作

3 叶技 2 0 1 3 年 第 2 6 卷 第2 期

E l e c t r o n i c S c i . &T e c h . / F e b . 1 5. 2 0 1 3

基于 F P G A 的视 频 采 集 显 示 系统

李 国兴 ,杨

摘 要

芳

7 2 3 0 0 0 )

( 陕西理工学院 物理 与电信工程学 院 ,陕西 汉 中

显 示 。 整 个 系统 获得 了较 好 图像 采 集 、 显 示 效果 。 关键词 F P G A;视 频 处理 ;T F T L C D;N i o s I I

中图分类号

T N 7 9 ;T P 2 7 4 . 2

文献标识码

A

文章编号

1 0 0 7— 7 8 2 0 ( 2 0 1 3 ) 0 2— 0 2 2— 0 4

基于FPGA的数字图像处理系统设计与实现

基于FPGA的数字图像处理系统设计与实现现代社会中,数字图像处理(Digital Image Processing, DIP)已经成为了一个不可或缺的技术。

它可以处理和分析图像,使其更清晰、更美观或者更容易被识别。

而要实现这个技术,我们就需要借助FPGA技术,设计并实现一个基于FPGA的数字图像处理系统。

一、FPGA技术的优势首先,我们来看看为什么要使用FPGA技术。

相对于传统的数字电路设计,FPGA具有以下优势:1. 灵活性高:FPGA可以进行可编程设计,因此可以根据不同需求进行灵活的设计和修改。

这种灵活性可以在数字图像处理的过程中,根据图像的不同特点来修改处理方式,提高图像处理的效率和质量。

2. 时序可控性强:FPGA在设计时可以很好地控制时序,避免一些不必要的时序问题。

对于数字图像处理来说,时序问题可能会导致图像刷新失真等问题。

3. 可重构性强:由于FPGA可以进行可编程的设计,因此被定义为“可重构硬件”。

使用FPGA进行数字图像处理系统设计时,可以实现对系统的快速修改和优化。

4. 运算性能强:FPGA具有并行处理的优势,处理图像时可以同时进行多个数据的计算,大幅提高计算速度。

这样可以使得数字图像处理系统的运算性能更优秀。

基于FPGA的数字图像处理系统,可以充分发挥FPGA的优势,提高图像处理的效率和质量。

二、数字图像处理系统的设计与实现接下来,我们来看看基于FPGA的数字图像处理系统的设计与实现。

对于数字图像处理系统的设计,我们需要从以下几个方面来考虑:1. 系统架构设计:包括数字信号处理(DSP)模块,图像采集器和显像器等,这些模块常常与FPGA相连,构建一个完整的数字图像处理系统。

2. 系统功能设计:本系统可实现图像增强、滤波、边缘检测、图像分割等多种功能,每种功能对应不同的算法和处理方式。

3. 系统软件设计:FPGA硬件设计不同于传统的软件开发,需要针对硬件的特殊性进行开发。

因此需采用专业的硬件设计语言,如Verilog和VHDL等语言,并进行仿真与硬件验证。

基于FPGA的图像采集处理系统

基于FPGA的图像采集处理系统在现代科技领域,特别是计算机视觉和机器学习领域,图像采集和处理已经成为一项至关重要的任务。

在许多应用中,需要快速、准确地对图像进行处理,这推动了图像采集和处理系统的研究和发展。

现场可编程门阵列(FPGA)作为一种可编程逻辑器件,具有并行处理能力强、功耗低、可重构等优点,使其成为构建高性能图像采集处理系统的理想选择。

FPGA是一种可通过编程来配置其硬件资源的集成电路,它由大量的可配置逻辑块、内存块和输入/输出块组成。

这些逻辑块和内存块可以在FPGA上被重新配置,以实现不同的逻辑功能和算法。

输入/输出块可以用于与外部设备进行通信。

基于FPGA的图像采集处理系统通常包括图像采集、预处理、传输、主处理和输出等几个主要环节。

这个阶段主要通过相机等设备获取图像数据。

相机与FPGA之间的接口可以是并行的,也可以是串行的。

并行接口通常传输速度更快,但需要更多的线缆;串行接口则使用更少的线缆,但传输速度可能较慢。

这个阶段主要是对采集到的原始图像数据进行初步处理,如去噪、灰度化、彩色化等。

这些处理任务可以在FPGA上并行进行,以提高处理速度。

经过预处理的图像数据需要通过接口或总线传输到主处理单元(通常是CPU或GPU)进行处理。

在传输过程中,可以使用DMA(直接内存访问)技术,以减少CPU的负载。

在这个阶段,主处理单元(通常是CPU或GPU)会对传输过来的图像数据进行复杂处理,如特征提取、目标检测、图像识别等。

这些处理任务需要大量的计算资源和算法支持。

处理后的图像数据可以通过接口或总线传输到显示设备或用于进一步的处理。

基于FPGA的图像采集处理系统具有处理速度快、可重构性强、功耗低等优点,使其在许多领域都有广泛的应用前景。

特别是在需要实时图像处理的场景中,如无人驾驶、机器视觉等,基于FPGA的图像采集处理系统将具有更高的性能和效率。

随着FPGA技术和相关算法的发展,我们可以预见,基于FPGA的图像采集处理系统将在未来得到更广泛的应用和推广。

基于FPGA的双通道CMOS图像采集系统设计

0 引 言

整 个 系 统 的 可 靠 性 。 同 时 , 用 2片 大 容 量 的 S R M 以 采 D A

目前 , 越来越多 的图像采集 系统采用 C S图像传 感 MO

器 …作为图像采 集器件 。随着 集成 电路设 计技 术 的不断 提高 , MO C S图像传 感器 的采集速 度不 断增大 。在 实际 应用 中, 传统 的单通道 数据传输 方式和单 片机实现 的图像 处理系统 已经远远无法满 足设计要 求 , 须采用新 的数据 必 传输方式和设计方法来实现图像采集 、 传输和存储功能。

本 文 设 计 了一 种 以 F G 芯 片 为 核 心 处 理 器 的 双 通 道 PA

乒乓操作 的方式进行 数据存储 , 保证 能够实时地接 收图像

传感器产生的图像数据 。 经综合 分 析 和考 虑,P A采 用 A e FG hr a的 C c n yl e o E 2 3 F8 C 视频采集芯片用 飞利 浦的 S A 132块 型 P C 5 4 4 8, A 71 , 号为 K S 42的 S R M 和 F G 463 D A P A构成 图像 帧存储 与传输

Ab ta t Re lt r c s ig o g s u u l o t — e k i mb d e ma e p o e sn y tm. a i g sr c : a — me p o e sn fi e i s al a b t e n c n e e d d i g rc s i g s s i ma y l e T kn

teavnaeo aae poes g af l por al gt ar ( P A)b sdC S i g cu io h da t fprll rcsi , e rga g l n id mm b a r y F G e e a ae MO mae aq it n si ss m ids nd T em d l s ut eds n fs i fsotFF yt ei e . h o u rc r ei ,rtni t u( IO)adpn—ags r cn l e r ue e s g et u g i r n igpn o t h o g s e sd tee o i a

基于FPGA的LVDS视频图像采集与预处理系统的设计实现

基于FPGA的LVDS视频图像采集与预处理系统的设计实现作者:黄国鹏刘卫东乔明胜陈兴锋来源:《现代显示》2009年第02期文章编号:1006-6268(2009)02-0032-04摘要:以LED背光源液晶电视为应用背景,在FPGA硬件平台上实现了LVDS视频图像采集和直方图预处理系统的设计。

关键词:现可编程门阵列;低压差分信号;直方图;约束中图分类号:TN911.73文献标识码:ADesign and Implement of FPGA-based LVDS Video Acquisition and Preprocessing SystemHUANG Guo-peng1,LIU Wei-dong1,2,QIAO Ming-sheng2,CHEN Xing-feng1(1.Dept. of Electrical Engineering ,Ocean University of China,Qingdao 266100;2. Hisense Electric Co.,Ltd, Qingdao 266071)Abstract:This paper ,taking LED backlight for LCD TV as application background, has researched to achieve LVDS video acquisition and preprocessing system based on FPGA .Keywords: FPGA;LVDS;histogram;constraints引言FPGA在信号实时处理领域得到越来越广泛的应用。

相比ASIC和DSP,FPGA有更高的吞吐量、位级的可编程能力、开发周期短和风险大大降低等优点。

随着65nm甚至45nm工艺技术的面世,FPGA在逻辑门集成数量和工作的频率上取得了很大的提高。

在大数量数据处理领域,其并行处理数据的优势可以得到充分体现,特别是在在图像帧速率和分辨率要求比较高的场合使用高速大容量FPGA可以得到令人满意的结果。

基于FPGA的实时视频图像采集与显示系统的设计与实现

基于FPGA的实时视频图像采集与显示系统的设计与实现作者:贡镇来源:《现代电子技术》2013年第13期摘要:主要针对目前视频图像处理发展的现状,结合FPGA技术,设计了一个基于FPGA的实时视频图像采集与显示系统。

系统采用FPGA作为主控芯片,搭载专用的编码解码芯片进行图像的采集与显示,主要包括解码芯片的初始化、编码芯片的初始化、FPGA图像采集、PLL设置等几个功能模块。

采用FPGA的标准设计流程及一些常用技巧来对整个系统进行编程。

重点在于利用FPFA开发平台对普通相机输出的图像进行采集与显示,最终能在连接的RCA端口显示屏显示。

关键词: FPGA;视频图像采集;编码芯片;解码芯片中图分类号: TN911⁃34 文献标识码: A 文章编号: 1004⁃373X(2013)13⁃0046⁃03Design and Implementation of real⁃time video image captureand display system based on FPGAGONG Zhen(Anhui University of Science and Technology, Huainan 232000, China)Abstract: Based on the current development status of the video image processing and FPGA technology, a FPGA⁃based real⁃time video image capture and display system is designed in this paper. Equipped with dedicated coding and decoding ship for image capture and display, the system adopts FPGA as the main control chip, which are composed of decoding chip initialization module, the encoding chip initialization module, FPGA image acquisition module and PLL setting module. FPGA⁃standard design flow and some commonly used techniques are taken to program the entire system. The focus is to realize the ordinary camera output image acquisition and display via the FPFA development platform, and ultimately connect the RCA port display screen.Keywords: FPGA; video image capture; coding chip; decoding chip0 引言随着时代的发展,人们在图像处理领域取得了相当多的成果,研究出了很多算法,例如中值滤波、高通滤波等。

基于FPGA的图像处理系统设计与实现

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

学位论文作者签名: 日期: 年 月 日

学位论文版权使用授权书

本学位论文作者完全了解学校有关保留、使用学位论文的规定,即:学校有权 保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借 阅。 本人授权华中科技大学可以将本学位论文的全部或部分内容编入有关数据库进 行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。 保密□,在 本论文属于 不保密□。 (请在以上方框内打“√” ) 年解密后适用本授权书。

II

华 中 科 技 大 学 硕 士 学 位 论 文

目

录

摘 要 ............................................................................................................ I Abstract ......................................................................................................... II 1 绪 论 1.1 课题来源、目的和意义 ................................................................. (1) 1.2 国内外发展现状 ............................................................................. (1) 1.3 本文主要内容 ..........................................................系统整体方案 2.1 系统设计需求 ................................................................................. (8) 2.2 系统设计整体结构 ......................................................................... (8) 2.3 系统设计整体方案 ....................................................................... (10) 2.4 本章小结 ....................................................................................... (12) 3 视频图像采集与处理系统硬件设计 3.1 CCD 工作原理 .............................................................................. (13) 3.2 ITU-R BT.656 数字视频格式 ....................................................... (14) 3.3 硬件电路设计 ............................................................................... (17) 3.4 电源系统设计 ............................................................................... (21) 3.5 本章小结 ....................................................................................... (24) 4 下位机逻辑驱动程序开发 4.1 逻辑驱动程序总体框架 ............................................................... (25) 4.2 视频前端电路控制器设计 ........................................................... (26)

Design of Video Image Acquisition and Processing System Based on FPGA

Candidate : Yang Qin Major : Mechatronics Engineering

Supervisor : Prof. Zhou Yunfei

分类号 学校代码 10487

学号 密级

M201070474

硕士学位论文

基于 FPGA 的视频图像采集 与处理系统设计

学位申请人:

杨

钦

学 科 专 业 : 机械电子工程 指 导 教 师: 周云飞 教授 答 辩 日 期 : 2013 年 01 月 19 日

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Engineering

学位论文作者签名: 日期: 年 月 日

指导教师签名: 日期: 年 月 日

华 中 科 技 大 学 硕 士 学 位 论 文

摘

要

为获取摄像头输出的视频图像并实现实时处理,本文利用 FPGA 并行处理能力强和 SDRAM 存储容量大的特点, 提出了一种 CCD 摄像头+FPGA+SDRAM+视频编解码芯片 的采集与处理系统设计方案。 该方案包括上位机界面控制部分和下位机硬件采集处理部 分。 上位机界面控制部分完成对下位机的 VGA 显示模式初始化,并下发指令让下位机 上传一帧的视频数据,实现截屏的功能,同时将上传的视频数据存入文本。随后可调用 图像处理界面完成图像的相应处理,包括阈值处理、边沿检测处理和形态学处理。 下位机根据上位机的初始化命令, 完成对整个采集处理系统的配置, 随后开始启动。 按照 CCD 摄像头输出的模拟 CVBS 信号的处理过程,下位机在 FPGA 中设计了视频前 端电路控制器、视频数据预处理器、SDRAM 控制器、VGA 显示控制器和通讯接口控制 器, 实现了对视频解码芯片的工作配置, 视频数据的解析、 预处理、 SDRAM 存储、 VGA 显示和通讯上传。其中处理模块采用 Sobel 边沿检测算子和 Prewitt 边沿检测算子。 软硬件验证结果表明,上位机可以实时修改下位机的数据预处理模式,并实现相应 的 VGA 显示,包括彩色显示、灰度显示和边沿检测显示。同时可以接收下位机的一帧 视频数据,并实现阈值处理、边沿检测处理和形态学处理。验证结果较好地符合了设计 要求。 关键词:视频图像 FPGA VGA 控制器 形态学处理

Huazhong University of Science and Technology Wuhan, Hubei 430074, P. R. China Jan, 2013

独创性声明

本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的 研究成果。尽我所知,除文中已经标明引用的内容外,本论文不包含任何其它个人 或集体已经发表或撰写过的研究成果。对本文的研究做出贡献的个人和集体,均已 在文中以明确方式标明。本人完全意识到本声明的法律结果由本人承担。

I

华 中 科 技 大 学 硕 士 学 位 论 文

Abstract

In order to acquire the camera output video image and realize real-time data processing, a project is proposed by using FPGA’s strong parallel processing ability and SDRAM’s large memory capacity. The project contains CCD camera, FPGA, SDRAM and video codec chip. Video codec chip is comprised of encoding chip ADV7123 and decoding chip ADV7403. The whole project composes two control parts: one is upper computer control part and the other is lower computer and hardware control part. Upper computer control part completes the initialization of the VGA display mode and sends particular command to FPGA to start to sample a frame data. Afterwards, the data will be uploaded to upper control part and be stored into text file. Subsequently, users can call image prcessing interface to do corresponding processing, including threshold processing, edge detection processing and morphology processing. Based on the initial command, lower computer and hardware control part completes the specific initialization of the acquisition and processing system. According to the steps of video signal processing, six modules are implemented, including the I2C controller, decoder of ITU-R BT.656, video signal processor, SDRAM controller, VGA display controller module and UART controller module. These modules accomplish video decoder chip’s configuration, parsing, processing, storage, display and uploading. Among those modules, the processing module uses Sobel edge detection operator and Prewitt edge inspection operator. As a result, hardware and software validation results show that upper computer control part can revise FPGA’s data preprocessing mode in real time, and realize the corresponding VGA display, which includes color display, gray display and edge detection display. Simultaneously upper part can receive a frame data from lower computer part and realize the threshold processing, edge detection processing and morphology processing.Verification results well in accord with the design requirements. Keywords: Video image, FPGA, VGA controller, Morphology processing