(完整word版)vhdl基本语法

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

VHDL数据类型vhdl语法

二、VHDL数据类型与数据对象

数据对象 常 量

(Data Objects)

信 号 变 量

二、VHDL数据类型与数据对象

ห้องสมุดไป่ตู้

(1) 常量 定义格式: Constant 常量名称: 数据类型 :=给定值; 常量通常来来定义延迟和功耗等参数。 注意!常数定义的同时进行赋初值。 常数可以在实体说明、结构体描述中使用。

例如: vabc=a & b & c;

如果a=‘1’ , b=‘0’ , c=‘1’ , 则 vabc=“101” 。

二、VHDL数据类型与数据对象

用户自定义数据类型: (1) 列举数据类型 Type 列举名称 is (元素1,元素2,…) 例子: Type state is(S0,S1,S2,S3); Signal A: state;

信号赋值的语法格式为:信号名 <= 表达式; 如:Signal S1 : Std_logic_vector(3 Downto 0); S1 <= “0000”;

注意!信号定义的时候尽管可以直接赋初值,但系统往往忽略。 建议信号对象定义后再进行赋值。

二、VHDL数据类型与数据对象

(3)变量

定义格式 Variable 变量名称: 数据类型 [:=初始值]; 变量只能用于“进程” 之中,变量的赋值是 立即生效的,常用于高层次抽象的算法描述 当中。

二、VHDL数据类型与数据对象

例如: Signal Y : Std_logic_vector(7 downto 0); Signal X : Integer range 0 to 255; Y<= CONV_STD_LOGIC_VECTOR(X,8);

二、VHDL数据类型与数据对象 CONV_INTEGER 将数据类型 UNSIGNED, SIGNED转换为 INTEGER 类型. CONV_UNSIGNED 将数据类型INTEGER, SIGNED转换为 UNSIGNED 类型. CONV_SIGNED 将数据类型INTEGER, UNSIGNED转换为 SIGNED类型. CONV_STD_LOGIC_VECTOR 将数据类型INTEGER, UNSIGNED, SIGNED, STD_LOGIC转换为STD_LOGIC_VECTOR 类型.

第10章VHDL基本语句

END LOOP L2; ...

11

11

10.1.4 LOOP语句

(2) FOR_LOOP语句,语法格式如下: [LOOP标号:] FOR 循环变量 IN 循环次数范围 顺序语句

LOOP

END LOOP [LOOP标号];

SIGNAL tmp :STD_LOGIC ;

BEGIN

奇校验就是看2进制数旳1旳个数为奇数

PROCESS(a)

就在校验位填0 偶数就填1 使1旳个数

BEGIN

变成奇数个. 偶校验相反 把1旳个数变

tmp <='0';

成偶数.

FOR n IN 0 TO 7 LOOP 然后传送数据,接受后在做相应旳奇偶

FOR后旳”循环变量”是一种临时变量,属LOOP语句旳局 部变量,不必事先定义. 这个变量只能作为赋值源,不能被赋值,它 由LOOP语句自动定义. 使用时应该注意,在LOOP语句范围内不 要再使用其他与此循环变量同名旳标识符.

“循环次数范围”要求LOOP语句中旳顺序语句被执行次数. 循环变量从范围初值开始,每执行完一次顺序增1,直至最大值.

第 10 章 VHDL基本语句

1

1

10.1 顺序语句

VHDL有6种基本顺序语句:赋值语句、流程控制语句、等待 语句、子程序调用语句、返回语句、空操作语句.

10.1.1 赋值语句

信号赋值语句

10.1.2 IF语句

10.1.3 CASE语句

变量赋值语句

多条件选择

值体现式旳 4种形式

单个一般数值,如6。

数值选择范围,如(2 TO 4)。

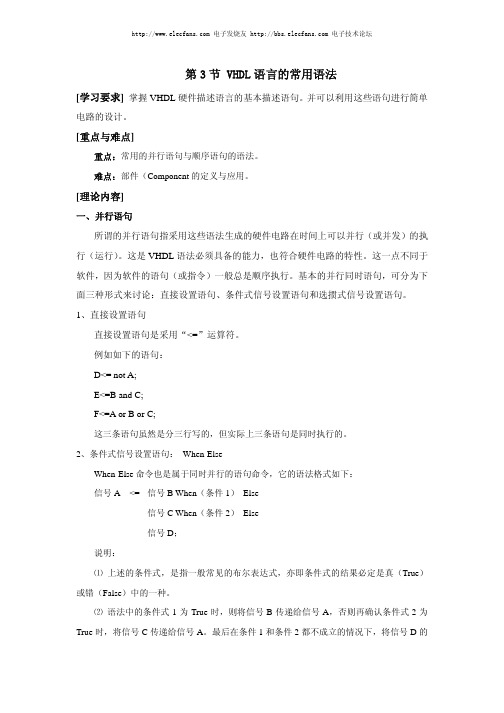

VHDL语言的常用语法

电子发烧友 电子技术论坛

值传递给信号 A。 When-Else 命令的应用范围非常广泛,例如:编码器、译码器、多路选择器等的 VHDL

命令编写,都可以采用这条命令。 3、选择式信号设置语句:With-Select

Process(进程)语句是一种并行处理语句,在一个构造体中多个 Process 语句可以同时

电子发烧友 电子技术论坛

并行运行。因此,Process 语句是 VHD 语言中描述硬件系统并行行为的最基本的语句。其语 法结构如下:

S<=X&Y; Process Begin

If S=”00” then Z<=’0’;

Elsif S=”01” then Z<=’1’;

Elsif S=”10” then Z<=’1’;

Else Z,=’0’;

End if; End process; end c;

--************用 Case-When 语句实现的结构体**************** architecture d of True_Table is

[进程名]: Process (信号 1,信号 2,…) Begin

…. End Process; 进程 Process 语句中总是带有 1 个或几个信号量。这些信号是 PROCESS 的输入信号(不 一定是所有的输入信号),在 VHDL 语言中也称为敏感量。这些信号无论哪一个发生变化(如 由“0”变“1”或由“1”变“0”)都将启动该 Process 语句。一旦启动以后,Process 中的 语句将从上到下逐句执行一遍。当最后一条语句执行完毕以后,就返回到开始的 Process 语 句,等待下一次变化的出现。当没有敏感量时,进程将无限循环执行。 二、顺序语句 所谓的顺序语句如前面所提到的,就是语句是按先后顺序执行的。顺序描述语句只能出 现在并行语句 Process 中。 1、If-else 语句 语法格式:

vhdl语法

一、VHDL概述

(2)ENTITY定义区

作用: ENTITY (实体)用于定义电路的 外观,即I/O端口的类型和数量。 定义格式: Entity 实体名 is Port( a : in bit; b : in bit; c : out bit); End 实体名;

端口名

端口模式

数据类型

一、VHDL概述

When-Else条件赋值语句 语法格式为:

Signal_name<= expression1 When logic_expression1 Else expression2 When logic_expression2 Else expression3;

例如:f <= ‟1‟ when (x1=x2) else „0‟;

(2) 信号 定义格式 I.(端口)信号 Port(端口信号名称:数据类型); 例如:Port(A:in std_logic); II.内部信号 Signal 信号名称: 数据类型 [:=初始值]; 例如:Signal B: std_logic;

“信号”数据对象的物理意义

端口信号代表电路的输入/输出; 内部信号代表电路中间信号或中间连接线路,其在 元件之间起互连作用。

& 连接符,将两个数 据对象或矢量连接成维 数更大的矢量,它可给 代码书写带来方便。

例如: vabc=a & b & c;

如果a=„1‟ , b=„0‟ , c=„1‟ , 则 vabc=“101” 。

二、VHDL数据类型与数据对象

数据对象 常 量

(Data Objects)

信 号 变 量

二、VHDL数据类型与数据对象

(1)Library和Package部分

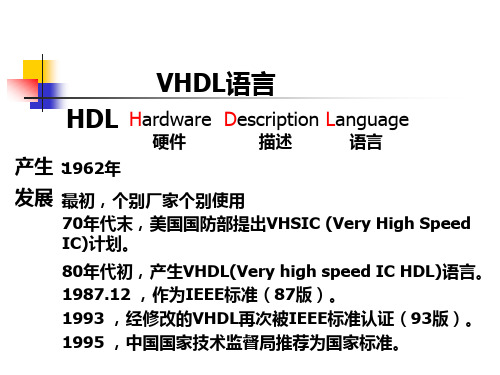

VHDL语言

VHDL语言的基本结构

实体结构

ENTITY 实体名 IS PORT ( 端口名1,端口名2,…端口名n :方向 数据类型名; … 端口名a,端口名b,…端口名m :方向 数据类型名);

80年代初,产生VHDL(Very high speed IC HDL)语言。 1987.12 ,作为IEEE标准(87版)。 1993 ,经修改的VHDL再次被IEEE标准认证(93版)。 1995 ,中国国家技术监督局推荐为国家标准。

VHDL语言的优点

支持自上而下的设计方法(整体描述)

半加器描述事例: WHEN “00” => so<=‘0’; co<=‘0’ ; WHEN “01” => so<=‘1’; co<=‘0’ ; WHEN “10” => so<=‘1’; co<=‘0’ ; WHEN “11” => so<=‘0’; co<=‘1’ ;

P.42 表3-3

VHDL语言的基本结构

实体 用以描述外部端口

构造体 用以描述内部结构及行为

实体结构

ENTITY 实体名 IS PORT ( 端口名1,端口名2,…端口名n :方向 数据类型名; … 端口名a,端口名b,…端口名m :方向 数据类型名);

END 实体名;

半加器实体说明举例 ENTITY h_adder IS

。 l任何标识符必须以英文字母开头。 l必须是单一下划线“_”,且其前后都必须有英文字母或数字。 l标识符中的英语字母不分大小写。 l允许包含图形符号(如回车符、换行符等),也允许包含空格符。

VHDL语法结构

变形:

If 条件式1 Then 语句命令A方块 End If; If 条件式1 Then 语句命令A方块 Else 语句命令2方块 End If;

Case-When(描述选择)

语法格式: Case 选择信号 Is When 信号值1 => 语句命令A方块 When 信号值2 => 语句命令B方块 : When Others => 语句命令N方块 End Case; 说明: 1、常用于选择执行有明确描述的信号。 2、有效状态机常用语句。

顺序语句

顺序语句命令类似一般的程序语言,如C等的执行方式,是一次 一个命令,且依书写方式由上而下的执行。

过程(Process)

语法格式:

[过程名称]:Process[ (感测信号1,感测信号2…) ] [定义区] Begin 语句 End Process [过程名称];

说明:

1、中括号所包含的部分,可省略。 2、“感测信号”代表这个信号有任何变化时,将促使这个过程执行一次。 3、在一个结构(architecture)里,可以放置数个过程(Process)。 4、与C语言函数比较。

数组数据类型

常被用在组合同样数据类型的元素,例如ROM、RAM等。 定义:Type 数组名 is Array(序列值)of 数据类型; 例如: Type Byte is Array(7 downto 0) of Bit; Type Word is Array( 31 downto 0) of Bit;

);

逻辑序列信号

VHDL提供以下功能语句: Bit_Vector :位序列 Std_Logic_Vector :标准逻辑序列

Architecture a of Test is Signal A : Std_logic_vector(3 downto 0); Signal B : Std_logic_vector(0 to 3); Begin B <= A; End a;

vhdl基本语素语法语句杨

二、VHDL数据类型与数据对

象

• 在VHDL程序中,我们经常会遇到这样的语句:

• Port(

X: in std_logic);

• Signal

A : std_logic;

• Variable

B : std_logic_vector(7

downto 0);

• Constant

C : integer;

二、VHDL数据类型与数据对象

(3)标准逻辑(Std_logic);

• 标识关键字: Std_Logic;

• 取值空间:

•{

• ‘X’ , -----Forcing Unknown

• • • • • • •

‘0’ , ‘1’ , ‘Z’ , ‘W’, ‘L’ , ‘H’ , ‘U’,

-----------------------------------WFFHW UWooineegerradaccankeiikknnfI0Ugmgi1nnp10ekdend对 特 实 对 采标oawn,数 性 逻 用准cne字 描 辑 标因逻逻 述 信 准此辑辑 更 号 逻在类电 加 的 辑V型H路 完 定 类D(L的 整 义 型程9值逻 , 通 .序逻辑 真 常中辑,)

VHDL命令语句

并列语句 顺序语句

第56页/共110页

并列语句

• (1)直接赋值语句:<= 赋值运算符 • (2)条件赋值语句:When-Else • (3)选择赋值语句:With-Select-When • (4) Process(进程)语句 • (5) Block(块)语句 • (6) 函数调用语句(后面章节讲) • (7) Component(元件)例化语句 • (8)For-Generate语句

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL 基础语法篇——VHDLVHDL硬件描述语言1.1 VHDL概述1.1.1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、Fortran等计算机高级语言,在VHDL语言中保留了部分高级语言的原语句,如if语句、子程序和函数等,便于阅读和应用。

具体特点如下:1. 支持从系统级到门级电路的描述,既支持自底向上(bottom-up)的设计也支持从顶向下(top-down)的设计,同时也支持结构、行为和数据流三种形式的混合描述。

2. VHDL的设计单元的基本组成部分是实体(entity)和结构体(architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送。

利用单元(componet)、块(block)、过程(procure)和函数(function)等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。

采用包的概念,便于标准设计文档资料的保存和广泛使用。

3. VHDL语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型,VHDL的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。

既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。

4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作,VHDL语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。

1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran和C等计算机高级语言的语句,如IF语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL语言。

但是VHDL毕竟是一种描述数字电路的工业标准语言,该种语言的标识符号、数据类型、数据对象以及描述各种电路的语句形式和程序结构等方面具有特殊的规定,如果一开始就介绍它的语法规定,会使初学者感到枯燥无味,不得要领。

较好的办法是选取几个具有代表性的VHDL程序实例,先介绍整体的程序结构,再逐步介绍程序中的语法概念。

一个VHDL语言的设计程序描述的是一个电路单元,这个电路单元可以是一个门电路,或者是一个计数器,也可以是一个CPU。

一般情况下,一个完整的VHDL语言程序至少要包含程序包、实体和结构体三个部分。

实体给出电路单元的外部输入输出接口信号和引脚信息,结构体给出了电路单元的内部结构和信号的行为特点, 程序包定义在设计结构体和实体中将用到的常数、数据类型、子程序和设计好的电路单元等。

一位全加器的逻辑表达式是:S=A⊕B⊕CiCo=AB+ACi+BCi全加器的VHDL程序的文件名称是fulladder.VHD,其中VHD是VHDL程序的文件扩展名,程序如下:LIBRARY IEEE; --IEEE标准库USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY fulladder IS -- fulladder是实体名称PORT(A, B, Ci : IN STD_LOGIC; --定义输入/输出信号Co, S : OUT STD_LOGIC);END fulladder;ARCHITECTURE addstr OF fulladder IS --addstr是结构体名BEGINS <= A XOR B XOR Ci;Co <= (A AND B) OR (A AND Ci) OR (B AND Ci);END addstr;从这个例子中可以看出,一段完整的VHDL代码主要由以下几部分组成:第一部分是程序包,程序包是用VHDL语言编写的共享文件,定义在设计结构体和实体中将用到的常数、数据类型、子程序和设计好的电路单元等,放在文件目录名称为IEEE的程序包库中。

第二部分是程序的实体,定义电路单元的输入/输出引脚信号。

程序的实体名称fulladder是任意取的,但是必须与VHDL程序的文件名称相同。

实体的标识符是ENTITY,实体以ENTITY开头,以END结束。

其中,定义A、B、Ci是输入信号引脚,定义Co和S是输出信号引脚。

第三部分是程序的结构体,具体描述电路的内部结构和逻辑功能。

结构体有三种描述方式,分别是行为(BEHA VIOR)描述、数据流(DATAFLOW)描述方式和结构(STRUCTURE) 描述方式,其中数据流(DA TAFLOW)描述方式又称为寄存器(RTL)描述方式,例中结构体的描述方式属于数据流描述方式。

结构体以标识符ARCHITECTURE开头,以END结尾。

结构体的名称addstr是任意取的。

小提示:VHDL每条语句是以分号“;”作为结束符的,并且VHDL对空格是不敏感的,所以符合之间空格的数目是可以自己设定的。

可以按自己的习惯任意添加,增强代码可读性。

1.1.3 VHDL语言的实体(ENTITY)说明语句实体是VHDL程序设计中最基本的组成部分,在实体中定义了该设计芯片中所需要的输入/输出信号引脚。

端口信号名称表示芯片的输入/输出信号的引脚名,这种端口信号通常被称为外部信号,信号的输入/输出状态被称为端口模式,在实体中还定义信号的数据类型。

实体说明语句的格式为:ENTITY 实体名称ISGENERIC(常数名称1:类型[:=缺省值];常数名称2:类型[:=缺省值];…常数名称N:类型[:=缺省值];);PORT(端口信号名称1:输入/输出状态数据类型;端口信号名称2:输入/输出状态数据类型;…端口信号名称N:输入/输出状态数据类型);END 实体名称;小提示:VHDL语言具有87标准与93标准两种格式,以上为VHDL的87标准,对于93标准要使用END ENTITY 实体名称;结束实体。

注意为了保证代码的可综合性与通用性,最好采用87标准的VHDL格式,有些EDA工具不一定支持93标准的VHDL语言格式。

(Quartus II支持VHDL93、87标准)类属GENERIC常用来定义实体端口大小,数据宽度,元件例化数目等。

一般在简单的设计中不常用。

例1-1-2一个同步十六进制加法计数器,带有计数控制、异步清零、和进位输出等功能。

电路有三个输入端和五个输出端,分别是时钟脉冲输入端CLK,计数器状态控制端EN,异步清零控制端Rd,四位计数输出端Q0, Q1, Q2, Q3和一个进位输出端Co。

当计数器输出0000~1110时,Co=0,只有当计数器输出1111时,Co=1。

该设计的实体部分如下:ENTITY cntm16 ISPORT(EN : IN STD_LOGIC;Rd : IN STD_LOGIC;CLK : IN STD_LOGIC;Co : OUT STD_LOGIC;Q : BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END cntm16;1. 实体名称表示所设计电路的电路名称,必须与VHDL文件名相同,实体名称是“cntm16”,所存的VHDL文件名必须是“cntm16.VHD”。

2. 端口信号名称表示芯片的输入/输出信号的引脚名,这种端口信号通常被称为外部信号,端口信号名称可以表示一个信号,也可以表示一组信号(BUS),由数据类型定义,如EN,Rd,CLK,Co分别表示计数允许信号,异步清零信号,时钟输入信号和进位输出信号,Q是一组输出信号,用来表示四位同步二进制计数器的四位计数输出信号。

3. 端口信号输入/输出状态有以下几种状态:IN 信号进入电路单元。

OUT 信号从电路单元输出。

INOUT 信号是双向的,既可以进入电路单元也可以从电路单元输出。

BUFFER 信号从电路单元输出,同时在电路单元内部可以使用该输出信号。

小提示:O UT 与BUFFER信号的区别就在于信号是否往内部有反馈,将输出端口定义为BUFFER型,可以省去一个用于中间运算的一个临时信号,但是并不推荐这么做。

4. 端口数据类型(TYPE)定义端口信号的数据类型,在VHDL中,常用的端口信号数据类型如下:(1)位(BIT)型:表示一位信号的值,可以取值‘0’和‘1’,放在单引号里面表示,如X < =‘1’,Y <=‘0’。

(2)位向量(BIT_VECTOR)型:表示一组位型信号值,在使用时必须标明位向量的宽度(个数)和位向量的排列顺序,例如:Q : OUT BIT_VECTOR(3 downto 0),表示Q3,Q2,Q1,Q0四个位型信号。

位向量的信号值放在双引号里面表示,例如Q <= “0000”;(3)标准逻辑位(STD_LOGIC)型:IEEE标准的逻辑类型,它是BIT型数据类型的扩展,可以取值‘U’,‘X’,‘0’,‘1’,‘Z’,‘W’,‘L’,‘H’,‘-’等。

(4)标准逻辑位向量(STD_LOGIC_VECTOR)型:IEEE标准的逻辑向量,表示一组标准逻辑位型信号值。

VHDL是与类型高度相关的语言,不允许将一种数据类型的信号赋予另一种数据类型的信号。

除了上述介绍的数据类型外,还有其他多种数据类型用于定义内部信号和变量,请参见1-2节。

小提示:相同类型(模型相同,数据类型相同)的端口可以写在同一行,如:ENTITY cntm16 ISPORT(EN, Rd,CLK : IN STD_LOGIC;Co : OUT STD_LOGIC;Q : BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END cntm16;此外要注意,最后一个端口结尾没有分号!1.1.4 VHDL语言的结构体(ARCHITECTURE)结构体是VHDL程序设计中的最主要组成部分,是描述设计单元的具体结构和功能,在程序中,结构体放在实体的后面。

每一个结构体都有名称,结构体的名称是由设计者任取的,结构体是以标识符ARCHITECTURE开头,以END结尾。

结构体可以有三种描述方式,分别是行为(BEA VHER)描述方式、数据流(DATAFLOW)描述方式和结构(STRUCTURE)描述方式,其中数据流(DA TAFLOW)描述方式又称为寄存器(RTL)描述方式。

不同的结构体采用不同的描述语句。

结构体的一般格式为:ARCHITECTURE 结构体名OF 实体名称IS说明语句BEGIN电路描述语句END 结构体名;结构体说明语句是对结构体中用到的数据对象的数据类型、元件和子程序等加以说明。