VHDL基本语法

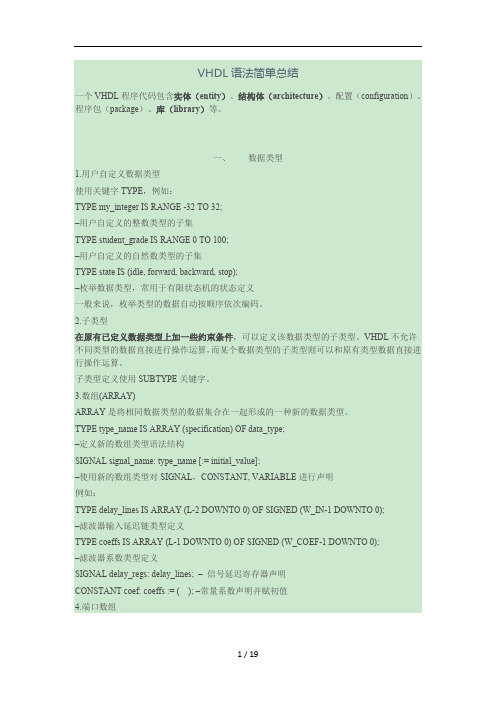

VHDL语法简单总结

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

vhdl基本语法 ifdef

VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

它是由美国国防部(DOD)于20世纪80年代初期的VHSIC(Very High Speed Integrated Circuits)项目中开发的。

VHDL的基本语法包括一些常用的关键字和结构,其中ifdef是其中之一。

ifdef是VHDL中的一个条件编译指令,用于根据给定的条件来判断是否包含某段代码。

在VHDL中,ifdef语句的基本语法如下:```vhdl`ifdef condition-- code to be included if condition is true`else-- code to be included if condition is false`endif```在上面的代码中,condition是一个条件表达式,可以是一个参数、宏定义或者其他已经定义过的条件。

如果condition为真,则会编译`ifdef和`endif之间的代码;如果condition为假,则会编译`else和`endif之间的代码。

使用ifdef可以让我们根据不同的条件来控制代码的编译和包含,这在一些复杂的项目中非常有用。

下面是使用ifdef的一个简单示例:```vhdl`ifdef DEBUGreport "Debug mode is enabled";`elsereport "Debug mode is disabled";`endif```在上面的代码中,如果DEBUG宏被定义了,那么report语句"Debug mode is enabled"将被编译进去;否则将编译进去"Debug mode is disabled"。

除了`ifdef语句外,VHDL还提供了一些其他的条件编译指令,如`ifndef(如果给定条件为假则编译)、`elsif(如果前面的条件为假则继续判断下一个条件)、`elsif和`endif。

VHDL基本语句

例

ARCHITECTURE example OF mux4 IS BEGIN PROCESS (sel) 注 BEGIN ●CASE中的选择值必须在表达式的取值范围内; CASE sel IS WHEN 0=> q <= d0 ; ●CASE语句是无序的,所有表达式值都是并行 WHEN 1=> q <= d1 ; 处理;而IF语句是有序的,最起始、最优先 WHEN 2=> q<= d3 ; WHEN 3=> q<= d4 ; 的先处理; WHEN others => NULL; ●可以有很多分支,但OTHERS分支只能有一个, END CASE; 且只能位于最后;用来使所有选择值能涵盖表 END PROCESS; END example; 达式的所有取值,以免插入不必要的锁存器

3、用于多选控制的IF语句:

格式 IF 条件1 THEN

<顺序处理语句1>;

ELSIF 条件2 THEN <顺序处理语句2>; : ELSIF 条件n-1 THEN <顺序处理语句n-1>; ELSE <顺序处理语句n>; END IF;

P1: PROCESS (clk) BEGIN

IF (clk‘ event and clk=‗1‘ ) THEN

顺序语句

赋值语句

VHDL设计实体内的数据传递以及对端口界面外部数据的读写 都必须通过赋值语句的运行来实现。 功能是将一个值或表达式的运算结果传递给某一数据对象。 赋值语句有两种: 信号赋值语句和变量赋值语句 区别

VHDL语言的基本语法

B:二进制基数符号,表示二进制数位0或1。 二进制基数符号,表示二进制数位0 O:八进制基数符号。 八进制基数符号。 X:十六进制基数符号(0~F) 。 十六进制基数符号(0~ (0 例如: 1_1101_1110 1_1101_1110” 例如:B“1_1101_1110 --二进制数数组,位矢数组长度是9 --二进制数数组,位矢数组长度是9 二进制数数组 AD0 X“AD0” AD --十六进制数数组,位矢数组长度是12 --十六进制数数组,位矢数组长度是12 十六进制数数组

4、下标名及下标段名 下标名用于指示数组型变量或信号的某一 下标名用于指示数组型变量或信号的某一 元素, 元素,如:a(2) , b(n) 下标段名则用于指示数组型变量或信号的 下标段名则用于指示数组型变量或信号的 某一段元素,其语句格式如下: 某一段元素,其语句格式如下:

数组类型信号名或变量名(表达式 表达式2]); 数组类型信号名或变量名 表达式1 [TO/DOWNTO 表达式 ; 表达式

信号的使用和定义范围是实体、结构体和程序包 信号的使用和定义范围是实体、结构体和程序包.

在程序中: 在程序中 (1) 信号值的代入采用“<=”代入符,而且信号 信号值的代入采用“ ”代入符, 代入时可以附加延时。 代入时可以附加延时。 (2) 变量赋值时用“:=”,不可附加延时。 变量赋值时用“ ” 不可附加延时。 (3) 信号的初始赋值符号仍是“:=”。 信号的初始赋值符号仍是“ ” 例: X<=Y AFTER 10 ns; ; --X,Y都是信号,且Y的值经过 都是信号, 的值经过10ns延 , 都是信号 的值经过 延 时以后才被代入X。 时以后才被代入 。

(1) 赋值语句右方的表达式必须是一个与目标变量有相同 数据类型的数值。 数据类型的数值。 (2) 变量不能用于硬件连线和存储元件。 变量不能用于硬件连线和存储元件。 (3) 变量的适用范围仅限于定义了变量的进程或子程序中。 变量的适用范围仅限于定义了变量的进程或子程序中。 (4) 若将变量用于进程之外,必须将该值赋给一个相同的 若将变量用于进程之外, 类型的信号,即进程之间传递数据靠的是信号。 类型的信号,即进程之间传递数据靠的是信号。

《VHDL语法基础》PPT课件

(5) 在结构体ART3中,COMPONENT→END COMPONENT 语句结构对所要调用的或门和半加器两元件作了声明 (COMPONENT DECLARATION),并由SIGNAL语句定义了三 个信号D、E和F,作为中间信号转存点,以利于几个器件间的信 号连接。接下去的“PORT MAP( )”语句称为元件例化语句 (COMPONENT INSTANTIATION)。所谓例化,在电路板上, 相当于往上装配元器件;在逻辑原理图上,相当于从元件库中取 了一个元件符号放在电路原理图上,并对此符号的各引脚进行连 线。例化也可理解为元件映射或元件连接,MAP是映射的意思。 例如,语句“U2:H_ADDER PORT MAP(A=>E,B=>CIN, CO=>F,SO=>SUM)”表示将实体H_ADDER描述的元件U2的引 脚信号A、B、CO和SO分别连向外部信号E、CIN、F和SUM。

(2) VHDL具有丰富的仿真语句和库函数,使得在任何大系 统的设计早期,就能查验设计系统的功能可行性,随时可对系 统进行仿真模拟,使设计者对整个工程的结构和功能可行性做 出判断。

(3) VHDL语句的行为描述能力和程序结构,决定了它具 有支持大规模设计的分解和已有设计的再利用功能。符合市场 需求的大规模系统高效、高速的完成必须有多人甚至多个开发 组共同并行工作才能实现,VHDL中设计实体的概念、程序包 的概念、设计库的概念为设计的分解和并行工作提供了有利的 支持。

END ENTITY OR2; --实体OR2的结构体ART1的说明

ARCHITECTURE ART1 OF OR2 IS

BEGIN C<=A OR B; END ARCHITECTURE ART1;

2) 半加器的逻辑描述 -- IEEE库的使用说明

VHDL语法入门

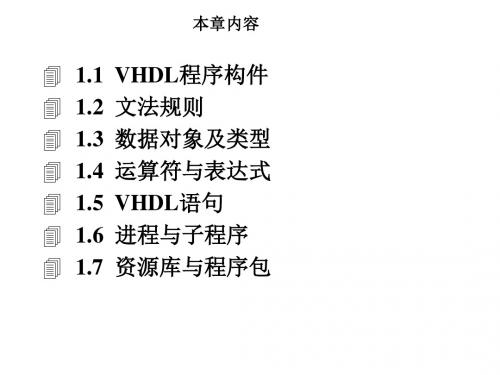

1.1 VHDL程序构件

配置说明

将具体的构造体分配给实体说明 示例

configuration conf1 of xor_gate is for data_flow end for; end conf1;

configuration conf2 of xor_gate is for structure end for; end conf1;

字符串

被双引号括起来的ASCII字符,如,“Hello”;

位串

被双引号括起来的数字序列,其前冠以基数说明符;如, B“0110_1111”,O“117”,X“FFE0”;

1.2 文法规则

文法格式

关键字、标识符:不区分大小写; 注释:‘--’,且只在该文本行有效; 分隔:‘;’为行分隔,VHDL的语句行可写在不同文本行

[端口说明;]

end [设计实体名] ;

1.1 VHDL程序构件

1.1 VHDL程序构件 IN

从外部输入至实体; 单向端口;

entity

1.1 VHDL程序构件 OUT

从实体输出至外部; 单向端口;

entity

1.1 VHDL程序构件 INOUT

可以从外部输入至实体; 也可以从实体输出至外部; 双向端口;

变量:

用于进程、子程序等模块的内部; 局部性数据对象;

1.3 数据对象及类型

例子:信号与变量

p2: process(a) variable tmp: integer:=1; begin tmp:=tmp*2; c2<=a+tmp; end process; end;

entity exmp1 is port(a: in Integer; b: out Integer); end; architecture behv of exmp1 is signal c1,c2: Integer; begin b<=c1+c2; p1: process(a) variable tmp: integer:=0; begin tmp:=tmp+1; c1<=a+tmp; end process;

VHDL语法简单情况总结

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

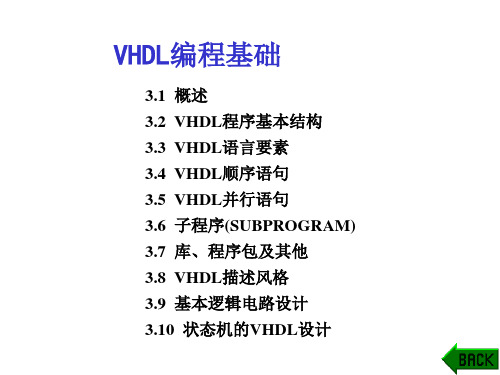

第3章VHDL语法基础

--设初始值

FOR I IN 1 DOWNTO 0 LOOP

IF (A(I)=‘1’ AND B(I)=‘0’) THEN

A_LESS _B<=FALSE;

EXIT;

ELSIF (A(I)=‘0’ AND B(I)=‘1’) THEN

A_LESS _B<=TRUE;

--A<B

EXIT;

ELSE NULL;

PROCESS(A) IS

BEGIN TMP <=‘0’;

FOR N IN 0 TO 7 LOOP

TMP <=TMP XOR A(N);

END LOOP; Y<= TMP;

结果:

END PROCESS;

Y=‘0’— A含偶数个‘1’,

END ARCHITECTURE ART;

Y=‘1’— A含奇数个‘1’。

BEGIN

PROCESS(A,B,C) IS

VARIABLE N: BOOLEAN;

BEGIN

C

IF A THEN N:=B;

ELSE N:=C; END IF; OUTPUT <=N; END PROCESS;

A

OUTPUT

B

对应的硬件电路

END ARCHITECTURE ART;

例3: 由两个2选1多路选择器构成的电路逻辑描述如图所示, 其中,当P1和P2为高电平时下端的通道接通。

A

S2 S1

D C

Z B A

ARCHITECTURE ART OF MUX41 IS

SIGNA S :STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

S<=S1 & S2;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

变量不是真正的物理量 , 因此不能 出现在敏感信号表中. 出现在敏感信号表中. 在 process 语句中只作为输出存在的 信号 ( 出现在信号赋值符 " < =" 的左 边 ) 不能作为敏感信 号. 既出现在信号赋值符 "<=" 的左边 , 又出现在信号赋值符 "<=" 右边的信 号 , 可以出现在敏感信号表中 , 这是因 为这些信号既作为这块电路的输出 , 又 是电路内部的反馈信号. 是电路内部的反馈信号.

例7 2 与非门. 与非门. 参见程序' (参见程序'例7') ) 说明: 说明: 本例中 , 首先将与非门输入信号 a 和 b 并置 , 生成一个 2 位的 std_logic_vector 信号 sel .信号 C 是与非门的输出. 是与非门的输出.第一个 when 中的 "|" 代表或者 , 即 3 个条件中的任何一 语句. 个满足 , 执行 C <='1' 语句.

格式 : IF 条件 1 THEN 若干顺序执行语句 1 ELSIF 条件 2 THEN 若干顺序执行语句 2 … ELSIF 条件 n-1 THEN 若干顺序执行语句 n-1 ELSE 若干顺序执行语句 n END IF;

(5) 进程语句 进程语句(PROCESS)

进程语句是一个十分重要的语句 进程语句是一个十分重要的语句 , 本质上它描述了一个功能独立的电路 本质上它描述了一个功能独立的电路 块.

CASE语句与 语句一样也是个顺序执 语句与IF语句一样也是个顺序执 语句与 行语句,但使用上有区别. 行语句,但使用上有区别. CASE语句执行时是无序的,所有表达 语句执行时是无序的, 语句执行时是无序的 式是并行处理; 语句是有序的, 式是并行处理;而IF语句是有序的, 语句是有序的 先处理最优先的条件, 先处理最优先的条件,后处理次优先 条件. 条件. 在某种情况下,两种语句都可以使用, 在某种情况下,两种语句都可以使用, 语句比IF语句描述更简捷 但 CASE语句比 语句描述更简捷, 语句比 语句描述更简捷, 更清晰.故应优先选用CASE语句. 语句. 更清晰.故应优先选用 语句

例5: : 语句描述 用PROCESS语句描述 位寄存器. 语句描述16 位寄存器. 参见程序' (参见程序'例5') ) 说明: 说明:

Register_16bits 是实体名 ,behave 是结 构体名. 构体名. reset 是异步复位信号 , 当为 '0' 位寄存器复位. 时 , 将 16 位寄存器复位.当时钟 clk 的上 如果写允许信号wen为 升沿到来时 , 如果写允许信号 为 如果wen '1',16 位输入信号 d 送输出 q; 如果 保持不变. 为'0', 输出 q 保: 1.进程的启动由敏感信号表中所标明的 进程的启动由敏感信号表中所标明的 信号来触发. 信号来触发. 2.每个PROCESS语句内部语句顺序执行; 语句内部语句顺序执行; 每个 3.多个PROCESS语句同时并行执行; 语句同时并行执行; 多个

例4: :

D 触发器 触发器: SIGNAL d ,clk,q:STD_LOGIC; PROCESS(clk) BEGIN IF clk'event AND clk='1' THEN q <=d; END IF; END PROCESS;

VHDL的层次结构设计 的层次结构设计

层次结构设计是设计较大规模硬件 的重要优点 的必要手段 , 也是 VHDL 的重要优点. .层次结构的设计方法是把一个大的系 层次结构的设计 层次结构的设计方法是把一个大的系 统划分为若干子系统 , 顶层描述各子系 之间的关系 的关系. 统的接口条件和各子系统 之间的关系. 各子系统的具体实现放在低层描述. 各子系统的具体实现放在低层描述. 同样 , 一个子系统也可以划分为若干更 小的子系统 小的子系统 , 一直划分下去 , 直到最基 本的子系统为止. 本的子系统为止.

process 语句有许多变种 , 这里只介绍 最基本的形式.

格式 : [ 进程名 :] PROCESS ( 敏感信号 1, 敏感信 号 2, … , 敏感信号 n) [ 若干变量说明语句 ] BEGIN 若干顺序执行语句 END PROCESS [ 进程名 ];

process 语句中有个敏感信号表 , 各敏感信号之间用逗号分开. 各敏感信号之间用逗号分开. 所谓敏感信号就是指当它的状态发 语句执行. 生变化时 , 启动 process 语句执行. 由于 process 语句代表一块功能独立 的电路 , 它的某些输入信号的状态 变 化 , 势必引起电路输出的变化 , 这些立 即引起 ( 当然要经过短暂的时间延迟 ) 输出信号状态 变化的信号就是敏感信 号.

除了 not 运算符的优先级最高外 , 其余逻辑 运算从左到右展开. 运算符的优先级相同 , 运算从左到右展开. 因此要注意加括号 , 如 : (a AND b) OR (e AND f) 不能写成 a AND b OR e AND f

2. 并置运算符 并置运算符 "&" 用于位的连接 , 形成矢 也可连接矢量生成更大的矢量. 量.也可连接矢量生成更大的矢量.

关系运算有如下规则 : (1) 在进行关系运算时 , 两个对象的数 据类型必须相同. 据类型必须相同. (2) 等于,不等于运算适用于所有数据 等于, 类型. 类型. (3) 大于,小于,大于等于和小于等于 大于,小于, 适用于整数,实数, 适用于整数,实数,位,位矢量的比 较.

4. 运算符的优先级 各运算符优先级从最高到最低的顺序 ( 同一行运算符优先级相同 ) 如下 : ** ( 乘方 );abs( 取绝对值 ); ; ; * ( 乘 )/( 除 );mod( 取模 ); ; ; +( 正号 ); - ( 负号 ); ; ; +( 加 );- ( 减 );&( 并置 ); ; ; ; sll( 逻辑左移 ); srl( 逻辑右移 ); ; ; rol( 逻辑循环左移 ) ; 逻辑循环左 ror( 逻辑循环右移 ); ;

2. 变量赋值语旬

格式 : 变量名 := 表达式 ; 由于在电路设计中 , 变量不与某一物理 量一一对应 , 它只起到设计的辅助作用 , 用 于保存中间结果, 于保存中间结果,做数组的下标等 , 因此变 量的赋值没有时间延迟. 量的赋值没有时间延迟.

例:

VARIABLE x,y,z: INTEGER RANGE 0 TO 255; x:=0; y:=132; z:=x;

SIGNAL a,b: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL c: STD_LOGIC_VECTOR(2 DOWNTO 0); a AND ('1' & c); c & a; --结果生成 4 位的 结果生成 std_logic_vector --结果生成 7 位的 结果生成 std_logic_vector

SIGNAL d,clk,q;

IF clk'event AND cIk = '1' THEN Q q <= d; END IF;

Qd

D

Clk

对于描述触发器来说 , 经常要用到时钟的 上升沿和下降沿 . 下面是描述它们的 4 种 方法 : clock'event AND clock ='1' clock'event AND clock ='0' rising_edge(clock)' falling_edge(clock)' --上升沿 上升沿 --下降沿 下降沿 --上升沿 上升沿 --下降沿 下降沿

举例 : SIGNAL t1,clk,clk1:STD_LOGIC; ; SIGNAL r0,r1: STD_LOGIC_VECTOR(15 DOWNTO 0); t1 <= '1'; clk1 <= NOT clk; r0 <= x" 0000"; rl <="0000000000000000";

(5)赋值语句 赋值语句

赋值语句的作用是给信号或者变量 赋值 , 它将赋值符号右边表达式的值 它将赋值符号右边表达式的值 赋给左边的信号或者变量. 赋给左边的信号或者变量. 赋值语句分为信号赋值语句和变量 赋值语句. 赋值语句.

1. 信号赋值语句 信号赋值语句 格式 : 信号名 <= 表达式 ; 由于信号是个真正的物理量 , 它对 应着电子电路的某一条连线 std_logic 或者一组连线 (std_logic_vector ) , 因此它的赋值一定有时间延迟. 因此它的赋值一定有时间延迟.

(6) IF 语句

IF语句属于描述硬件行为的语句.共有 语句属于描述硬件行为的语句. 语句属于描述硬件行为的语句 三种用法. 三种用法. 1.用于门闩控制的语句. 用于门闩控制的语句. 用于门闩控制的语句 格式: 格式: IF 条件 THEN 若干顺序执行语句 END IF;

触发器. 例1: 用 if 语句设计的 D 触发器. : ( 程序片断) 程序片断)

例:

SIGANL a,b,e,f:STD_LOGIC; SIGANL c,d: STD_LOGIC_VECTOR(7 DOWNTO 0); a AND b; a OR b; NOT a --正确 正确 c AND d; c XOR d; NOT C --正确 正确 a AND c; --错误 , 因为数据类型不同 ; 错

3. 算术运算符 算术运算符有 14 种 ,最常用的算术 最常用的算术 运算符是 + 和 -. . 例:

SIGNAL a,b: STD_LOGIC_VECTOR(3 DOWNTO 0); a+b; a+'1';