浮点数运算与加法器

计算机组成原理 [袁春风]chap3_4

![计算机组成原理 [袁春风]chap3_4](https://img.taocdn.com/s3/m/dce5a8e0856a561252d36fce.png)

浮点数运算及结果 浮点数的加减运算 浮点数的乘除运算 精度考虑 IEEE754中几个特殊值的含义 浮点运算部件的设置

1

南京大学计算机系 多媒体技术研究所 袁春风

3.6.1 浮点数运算及结果

设两个规格化浮点数分别为 A=Ma . 2Ea B=Mb.2Eb ,则 A+B =[Ma + Mb.2 -(Ea-Eb)]. 2Ea (假设Ea>=Eb ) A*B =(Ma * Mb).2 Ea+Eb A/B =(Ma / Mb).2 Ea-Eb 上述运算结果可能出现以下几种情况

24

南京大学计算机系 多媒体技术研究所 袁春风

一位十进制加法器

S3 S2 S1 S0

+

+

+

C4 S3* C4* + A3 B3

25

S2* +

SБайду номын сангаас* +

S0* +

A2 B2

A1 B1

A0 B0

南京大学计算机系 多媒体技术研究所 袁春风

n位十进制加法器

n个一位十进制加法器= 一个n位十进制串行加法器

13

南京大学计算机系 多媒体技术研究所 袁春风

14

南京大学计算机系 多媒体技术研究所 袁春风

IEEE754的舍入方式

r=0

r=1 U+1

0

U

U+0.5

15

强迫为 偶数

南京大学计算机系 多媒体技术研究所 袁春风

IEEE754的舍入方式

r=1 U-1

r=0 U

U-0.5

16

0

南京大学计算机系 多媒体技术研究所 袁春风

浮点数的运算步骤

浮点数的运算步骤浮点数的加减运算⼀般由以下五个步骤完成:对阶、尾数运算、规格化、舍⼊处理、溢出判断⼀、对阶所谓对阶是指将两个进⾏运算的浮点数的阶码对齐的操作。

对阶的⽬的是为使两个浮点数的尾数能够进⾏加减运算。

因为,当进⾏M x·2Ex 与M y·2Ey加减运算时,只有使两浮点数的指数值部分相同,才能将相同的指数值作为公因数提出来,然后进⾏尾数的加减运算。

对阶的具体⽅法是:⾸先求出两浮点数阶码的差,即⊿E=E x-E y,将⼩阶码加上⊿E,使之与⼤阶码相等,同时将⼩阶码对应的浮点数的尾数右移相应位数,以保证该浮点数的值不变。

⼏点注意:(1)对阶的原则是⼩阶对⼤阶,之所以这样做是因为若⼤阶对⼩阶,则尾数的数值部分的⾼位需移出,⽽⼩阶对⼤阶移出的是尾数的数值部分的低位,这样损失的精度更⼩。

(2)若⊿E=0,说明两浮点数的阶码已经相同,⽆需再做对阶操作了。

(3)采⽤补码表⽰的尾数右移时,符号位保持不变。

(4)由于尾数右移时是将最低位移出,会损失⼀定的精度,为减少误差,可先保留若⼲移出的位,供以后舍⼊处理⽤。

⼆、尾数运算尾数运算就是进⾏完成对阶后的尾数相加减。

这⾥采⽤的就是我们前⾯讲过的纯⼩数的定点数加减运算。

三、结果规格化在机器中,为保证浮点数表⽰的唯⼀性,浮点数在机器中都是以规格化形式存储的。

对于IEEE754标准的浮点数来说,就是尾数必须是1.M 的形式。

由于在进⾏上述两个定点⼩数的尾数相加减运算后,尾数有可能是⾮规格化形式,为此必须进⾏规格化操作。

规格化操作包括左规和右规两种情况。

左规操作:将尾数左移,同时阶码减值,直⾄尾数成为1.M的形式。

例如,浮点数0.0011·25是⾮规格化的形式,需进⾏左规操作,将其尾数左移3位,同时阶码减3,就变成1.1100·22规格化形式了。

右规操作:将尾数右移1位,同时阶码增1,便成为规格化的形式了。

要注意的是,右规操作只需将尾数右移⼀位即可,这种情况出现在尾数的最⾼位(⼩数点前⼀位)运算时出现了进位,使尾数成为10.xxxx或11.xxxx的形式。

第六讲定点运算器及浮点数运算演示文稿

P和G的含义

第3位的进位输出(即整个4位运算进位输出)公式为: Cn+4 =Y3+X3Cn+3 =Y3+Y2X3+Y1X2X3+Y0X1X2X3+X0X1X2X3Cn 设 G=Y3+Y2X3+Y1X2X3+Y0X1X2X3

P=X0X1X2X3

则 Cn+4=G+PCn

其中G称为进位发生输出,P称为进位传送输出。 在电路中多加这两个进位输出的目的,是为了便于实现多片

当前第19页\共有62页\编于星期五\23点

先行进位部件74182CLA所提供的进位逻辑关系如下: Cn+x= G0+P0Cn Cn+y= G1+P1Cn+x= G1+G0P1+P0P1Cn Cn+z= G2+P2Cn+y= G2+G1P2+G0P1P2+P0P1P2Cn Cn+4 = G3+P3Cn+z= G3+G2P3+G1P1P2+G0P1P2P3+P0P1P2P3Cn

C4=G0+P0 C0 C8=G1+P1 C4

C12=G2+P2 C8 C16=G3+P3 C12

C8 = G1+P1 C4 = G1 + P1 (G0+P0 C0 ) = G1+G0P1+P0P1C0

C12= G2+P2 C8 = G2 + P2 (G1+G0P1+P0P1Cn) = G2+G1P2+G0P1P2+P0P1P2C0

G=Y3+Y2X3+Y1X2X3+Y0X1X2X3 P=X0X1X2X3

当前第16页\共有62页\编于星期五\23点

2.5 浮点运算和浮点运算器

单击此处编辑母版标题样式 单击此处编辑母版文本样式 第二级 浮点数运算真正的溢出 第三级在尾数相加的ຫໍສະໝຸດ 候发生尾数上溢,并在向右规格化的时

候使阶码也发生上溢

计算机组成与系统结构

2.5 浮点运算和浮点运算器

单击此处编辑母版标题样式 【例2-18】设x=2010×0.11011011,y=2100×(-0.10101100), 求 x+y。 单击此处编辑母版文本样式 【解】假设两数均以补码表示,阶码采用双符号位,尾数采 第二级 用单符号位,其浮点表示分别为 第三级 [x]浮=00 010 0.11011011,[y]浮=00 100 1.01010100 ①求阶差并对阶 △E=Ex-Ey=[Ex]补+[-Ey]补=00 010+11 100=(11 110)补=(11 010)原=(-2)10,x的阶码小,应使Mx右移2位,Ex加2 ∴[x]浮=00 100 0.00110110(11) (11)表示Mx右移2位后移出的最低两位数

有一个为0,那么运算结果马上可知,而不必进行后续的一

系列操作,以节省运算时间

计算机组成与系统结构

2.5 浮点运算和浮点运算器

2)对阶 单击此处编辑母版标题样式 单击此处编辑母版文本样式 看两个浮点数的阶码是否相同,即小数点位置是否对齐 第二级 如阶码相同,则表示小数点位置是对齐的,尾数可直接 第三级 进行加减运算 若两数阶码不同,则表示小数点位置没有对齐,不能直

6)溢出处理 单击此处编辑母版标题样式 单击此处编辑母版文本样式 第二级 尾数溢出 第三级

尾数相加的溢出不是真正的溢出

可以借由向右规格化作出调整

计算机组成与系统结构

浮点运算

2.5浮点运算与浮点运算器2.5.1浮点数的运算规则浮点数的形式X=Mx * 2E x▲ 尾数的右移: 若尾数是原码表示,每右移一位,符号位不参加移位,尾数高位补0;若尾数是补码表示,每右移一位,符号位参加右移,并保持补码的符号不变。

一、浮点加法和减法设有两个浮点数:X=Mx * 2E x Y=My * 2E y它们的加减步骤是:1、对阶——使两个数的阶码相等,才能进行尾数的加减。

对阶原则——小阶向大阶看齐,即小阶的尾数向右移位(相当于小数点左移),每右移一位,其阶码加1,直到两数的阶码相等为止,右移的位数等于阶差△E 。

例1:两浮点数X=201*0.1101, Y=211*(-0.1010),将两个数对阶。

解:假设两数在计算机中以补码表示。

[△E]补=[Ex]补 – [Ey]补=[Ex]补 + [–Ey]补=00 01 + 11 01=11 10即△E=-2,表示Ex 比Ey 小2,因此将X 的尾数右移2位:右移一位,得[X]浮=00 10,00.0110再右移一位,得[X]浮=00 11,00.0011对阶完毕。

2、尾数求和+ 尾数和为:3、规格化(1)对于补码来说 规格化(2)规格化的方法浮点数的尾数相加后得到补码的形式M ,对比符号位和小数点后的第一位,如果它们不等,即为00. 1…和11. 0…的形式,就是规格化的数;如果它们相等,即00. 0…或11. 1…,就不是规格化的数,此时要进行左规格化,或左规。

向左规格化——尾数左移1位,阶码减1。

当结果出现01.…或10. …的形式时,要进行右规格化,或右规。

00 001111 011011 1001 正数:00. 1… 负数:11. 0…向右规格化——尾数右移1位,阶码加1。

4、舍入在对阶或向右规格化时,尾数要向右移位,这样,被右移的尾数的低位部分会被丢掉,从而造成一定的误差,因此要进行舍入处理。

舍入的方法——“0舍1入”:如果右移时,被丢掉数位的最高位是0则舍去,反之则将尾数的末位加“1”。

三菱PLC浮点数运算指令 - 三菱plc

三菱PLC浮点数运算指令 - 三菱plc浮点数运算指令(FNC110-FNC1320)用于浮点数的处理,浮点数为32位数,包括浮点数的比较、变换、四则运算、开平方运算和三角函数等13条指令。

所有的浮点数处理指令都是32位指令,在使用时,大多数指令的助记符前面必须加上32位运算的标识符“D"。

它们分布在指令编号为FNC110~FNC119、FNC120~FNC129、FNC130~FNC139之中。

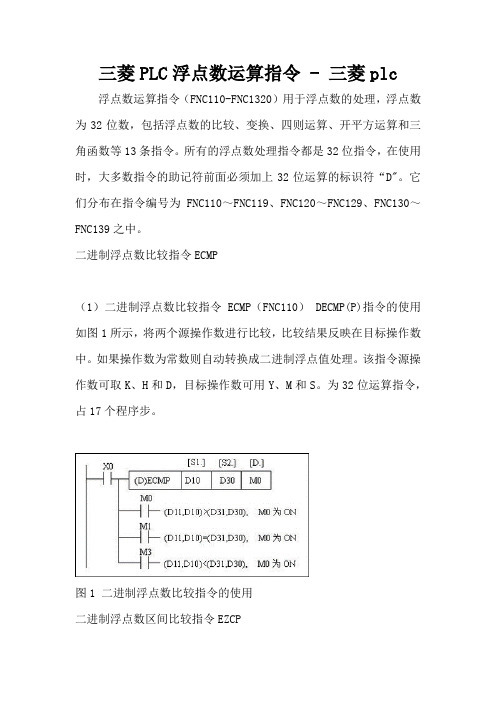

二进制浮点数比较指令ECMP(1)二进制浮点数比较指令ECMP(FNC110) DECMP(P)指令的使用如图1所示,将两个源操作数进行比较,比较结果反映在目标操作数中。

如果操作数为常数则自动转换成二进制浮点值处理。

该指令源操作数可取K、H和D,目标操作数可用Y、M和S。

为32位运算指令,占17个程序步。

图1 二进制浮点数比较指令的使用二进制浮点数区间比较指令EZCP(2)二进制浮点数区间比较指令EZCP(FNC111) EZCP(P)指令的功能是将源操作数的内容与用二进制浮点值指定的上下二点的范围比较,对应的结果用ON/OFF反映在目标操作数上,如图2所示。

该指令为32位运算指令,占17个程序步。

源操作数可以是K,H和D;目标操作数为Y、M和S。

[S1.]应小于[S2.],操作数为常数时将被自动转换成二进制浮点值处理。

图2 二进制浮点数区间比较指令的使用加法指令EADD减法指令ESUB乘法指令EMVL除法指令EDIV(3)二进制浮点数的四则运算指令浮点数的四则运算指令有加法指令EADD (FNC120)、减法指令ESUB(FNC121)、乘法指令EMVL(FNC122)和除法指令EDIV(FNC123)四条指令。

四则运算指令的使用说明如图3所示,它们都是将两个源操作数中的浮点数进行运算后送入目标操作数。

当除数为0时出现运算错误,不执行指令。

此类指令只有32位运算,占13个程序步。

运算结果影响标志位M8020(零标志)、M8021(借位标志)、M8022(进位标志)。

基于RISC指令系统的32位浮点加减法运算器设计

基于RISC指令系统的32位浮点加减法运算器设计摘要:浮点运算部件一直是限制微处理器性能的一个关键因素。

在分析了浮点运算器的结构和算法,提出了一种支持IEEE-754标准的浮点加减法运算器的实现方案,并详细介绍了该运算器的结构和算法。

方案采用了四级流水线的结构,即:0操作数检查、对阶、尾数运算、结果规格化及舍入处理。

每个步骤可以单独作为一个模块,在每个模块之间增加了寄存器,利用这些寄存器可以为下一个操作准备正确的数据。

关键词:流水线,IEEE-754标准,警戒位,舍入法32 bit Floating-Point Addition and Subtraction ALU Design Based onRISC StructureABSTRACT:Floating-Point arithmetic unit is always key factor of restricting microprocessor performance.This paper analyses structure and algorithm of Floating-Point ALU and brings forward a scenario about Floating-Point addition and subtraction ALU which supports IEEE-754 standard. The scenario adopts 4-Level pipelining structure: 0 operation numbers check、match exponent、fraction arithmetic、result normalization and rounding. Each step can be act as a single module. Among these modules, there are some registers which can prepare correct data for next operation.Keywords: pipelining, IEEE-754 Standard, Guard Digit, Rounding Method1 引言随着SOC技术、IP技术以及集成电路技术的发展,RISC软核处理器的研究与开发设计开始受到了人们的重视。

单双精度浮点运算加法器的实现

有效 字段实 际上 只储存 了尾数 部分 。下面显示 了 3 2 位单精度 和6 4 位双精度 的格式 , 阶码部分 既要 能够要能够代表正 阶码 , 又要能够代表负 阶 码, 为 了做 到这一点 , 阶码部分 实际储存 的是浮点数 指数加上

一

个偏 移量 , 在I E E E 一 7 5 4 标 准 中单精 度浮点 数的阶码偏 移量

一

2浮点数 加 法算 法

1 ) 指数相减 : 两数阶码不相等 , 表示小数点位置没有对齐 , 必须 使两 阶码相等 , 才执 行加法操 作 。比较 两个阶码 大小 , 求 阶码差值 l d J 。

2 ) 指数对 齐 : 采 用“ 小阶 向大阶对齐 ” , 将 阶码 较小的浮点

数的尾数右移 l d l , 使两个浮点数 阶码相等 , 实现对 阶。 3 ) 尾 数有效位 相加 : 根据操作 码( 加或减) 和操作 数的符号 完成有效位加或减 。 4 ) 尾 数转换 : 计算 出尾数 的结果都 为补码表示 的 , 需转换 为原码。 5 ) 规格化 与舍 入 : 结果 规格 化使尾数为 1 . F , 找出高位第一 个1 的位置 , 根据它所在 的位置 , 然后尾数左移 或右移 , 调整阶

浮点数加法 mips

浮点数加法 mips在MIPS体系结构中,浮点数加法使用特定的指令集进行操作。

下面是一些关于MIPS浮点数加法的相关参考内容。

1. MIPS浮点数加法指令:MIPS体系结构中用于执行浮点数加法的指令是"fadd.s"和"fadd.d"。

其中,"fadd.s"用于单精度浮点数加法,"fadd.d"用于双精度浮点数加法。

fadd.s fd, fs, ft # fd = fs + ftfadd.d fd, fs, ft # fd = fs + ft其中,fd、fs、ft是浮点寄存器 (Floating-Point Register),分别用于存储结果、第一个操作数和第二个操作数。

2. 浮点数表示方法:MIPS使用IEEE 754标准来表示浮点数。

单精度浮点数使用32位,其中1位为符号位,8位为指数位,23位为尾数位。

双精度浮点数使用64位,其中1位为符号位,11位为指数位,52位为尾数位。

3. 浮点数加法的溢出和舍入:在执行浮点数加法时,可能会发生溢出或舍入的情况。

溢出是指结果超出了所能表示的范围,舍入是指结果需要舍弃一部分小数位。

MIPS中的浮点数加法指令会根据具体情况进行溢出处理和舍入操作。

4. 浮点数加法的使用示例:下面是一个使用MIPS浮点数加法指令的示例代码,该代码计算了两个单精度浮点数的和:```assembly.dataresult: .float 0.0a: .float 1.5b: .float 2.7.textmain:lwc1 $f1, a # load a into $f1lwc1 $f2, b # load b into $f2fadd.s $f3, $f1, $f2 # add $f1 and $f2, and store result in $f3 swc1 $f3, result # store result in memory# print result (assume syscalls for printing are available)li $v0, 2lw $a0, resultsyscall# terminate programli $v0, 10syscall```以上示例代码首先将两个单精度浮点数"a"和"b"加载到浮点寄存器$f1和$f2中,然后使用"fadd.s"指令将两个数相加并将结果存储在$f3中,最后将结果打印出来。

组成原理课程设计报告浮点数加法器

航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:浮点数加法器院(系):计算机学院专业:计算机科学与技术班级:学号:姓名:指导教师:完成日期:目录第1章总体设计方案31.1设计原理31.2设计思路31.3设计环境41.3.1 硬件环境41.3.2 EDA环境4第2章详细设计方案62.1总体方案的设计与实现62.2功能模块的设计与实现72.2.1 原补转换模块的设计与实现72.2.2 阶码选择模块的设计与实现92.2.3 数值选择模块的设计与实现122.2.4 数据移位模块的设计与实现142.2.5 加法模块的设计与实现182.3总电路仿真测试21第3章编程下载与硬件测试243.1编程下载243.2硬件测试及结果分析24参考文献26附录27第1章总体设计方案1.1 设计原理本次课程设计的题目为浮点数加法器的设计,使用Xilinx Foundation F3.1可编程器件开发工具软件,以及伟福COP2000试验箱实现目的设计。

具体要求为必须用基本逻辑门实现,浮点数的长度固定。

根据所学可知,浮点数共由两部分组成。

第一部分是阶码,第二部分是数据。

这两部分又分别分为两部分。

阶码由阶符和数值组成,数据由数符和数字组成。

由于在计算机的存储和运算中,数据由补码表示。

故首先应将输入的原码转化为补码。

在此过程中,正数保持不变,负数则对除符号位以外的各位按位取反,再进行加1操作。

然后对两数的阶码进行运算,决定移位的次数和结果的阶码。

在移位时,对正数进行补0操作,对负数则进行补1操作。

再对移位后的数据视为定点数进行相加运算。

进而实现浮点数相加的功能。

最后再将得到的结果转化为原码,进行输出。

1.2设计思路按照课设题目要求及原理图,先设计出电路的具体模块图,浮点数加法器的设计共包含如下五个模块:①原补转换模块②阶码选择模块③数值选择模块④数据移位模块⑤超前进位加法模块在五个部分中分别设计实现相应功能的器件,包括二选一数据选择器等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/9/23

3.4 加法器和ALU

2.进位链电路

并行加法器中的每一个全加器都有一个 从低位送来的进位和一个传送给较高位的 进位。我们将各位之间传递进位信号的逻 辑线路连接起来构成的进位网络称为进位 链。

2020/9/23

3.4 加法器和ALU

单级先行进位

这种进位方式就是将n位全加器分成若干个小组 ,小组内的进位同时产生,实行并行进位,小组 与小组之间采用串行进位,这种进位又称为组内 并行、组间串行。

以16位加法器为例,可分为4组,每组4位。第1 组组内的进位逻辑函数C0 、C1 、C2、、C3的 表达式与前述相同,C0-C3信号是同时产生的, 实现上述进位逻辑函数的电路称之为四位先行进 位电路CLA(Carry Look Ahead),其延迟时间 是2ty。

2020/9/23

3.4 加法器和ALU

C4=G4+P4C3 C5=G5+P5C4= G5+ P5G4+ P5P4C3 C6=G6+P6C5= G6+ P6G5+ P6P5G4+ P6 P5P4C3 C7=G7+P7C6= G7+ P7G6+ P7P6G5+ P7P6 P5 G4+ P7P6 P5P4C3

2020/9/23

3.4 加法器与ALU

S16~S13

S12~S9

S8~S5

S4~S1

4位CLA

4位CLA

4位CLA

4位CLA

C16 加法器 C12 加法器 C8 加法器 C4 加法器

C0

A16~A13

A12~A9

A8~A5

A4~A1

B16~B13

B12~B9

B8~B5

B4~B1

2020/9/23

C8=G8+P8C7 C9=G9+P9C8= G9+ P9G8+ P9P8C7 C10=G10+P10C9= G10+ P10G9+ P10P9G8+ P10 P9P8C7 C11=G11+P11C10= G11+ P11G10+ P11P10G9+ P11P10 P9 G8+ P11P10 P9P8C7

A12~A9

A8~A5

B16~B13

B12~B9

2020/9/23

B8~B5

A4~A1 B4~B1

3.4 加法器和ALU

3.4.2 ALU电路

为了实现算术/逻辑多功能运算,则必须 对全加器(FA)的功能进行扩展,具体方 法是:先不将输入Ai、Bi和下一位的进位 数Ci直接进行全加,而是将Ai和Bi先组合 成由控制参数S0、S1、S2、S3控制的组 合函数Xi、Yi,如图3-16所示,然后再将 Xi、Yi和下一位进位数通过全加器进行全 加。这样,不同的控制参数可以得到不同 的组合函数,因而能够实现多种算术运算 和逻辑运算。

Sn

S2

S1

Cn

FA

…

Cn-1

C2

FA C1

FA

C0

An Bn

2020/9/23

A2 B2

A1 B1

3.4 加法器和ALU

(2)并行进位链电路 把n个全加器串接起来,就可以进行两个n位数的相加

。这种加法器称为串行进位的并行加法器。串行进位又 称行波进位,每一级进位直接依赖于前一级的进位,即 C0进=G位0+信P号0C是-1 逐级形成的。 C1=G并1行+P进1C位0=链G是1+指P并1G行0+加P法1P器0C中-1的进位信号是同时产生 C2的=G,2+又P称2C先1=行G进2+位P、2G同1+时P进2P位1G、0+跳P跃2 P进1P位0C等-1,其特点是 C3各=G级3+进P位3C信2=号同时形成。 ➢G3+ P单3G级2+先P行3P进2G位1+方P式3P2 P1 G0+ P3P2 P1P0C-1

本节目标

➢本节主要学习以下内容: 加法器与进位链 ALU的组成 浮点数的加减法运算法则 浮点数的乘除法运算法则

➢理解浮点数乘、除法的基本运算方法,了 解算术逻辑运算单元ALU和加法器与进位 链电路的基本组成

2020/9/23

3.4 加法器和ALU

3.4.1 加法器与进位链电路

1.加法器 计算机中最基本的运算部件是加法器,通常

,加法器和其他必要的逻辑电路组合在一起,可 以在计算机中进行一些基本运算。

(1)全加器 基本的加法单元称为全加器。它要求

三 进个位C输i-入1,量并:产操生作两数个A输i和出B量i、:低本位位传和来S的i、 向高位的进位Ci。

2020/9/23

3.4 加法器和ALU

一位全加器真值表

输 入 Ai Bi Ci 000 001 010 011 100 101 110 111

输 出

Si

Ci+ 1

00

10

10

01

10

01

01

11

Si=Ai⊕Bi⊕Ci-1 Ci=AiBi+(Ai ⊕ Bi)Ci-1

2020/9/23

3.4 加法器和ALU

2020/9/23

3.4 加法器和ALU

(2)串行加法器和并行加法器 加法器可分为串行加法器和并行加法器。在串

行加法器中,只有一个全加器,数据逐位串行送 入加法器进行运算,如果操作数长n位,加法就 要分n次进行,串行加法器具有器件少、成本低 的优点,但运算速度太慢。

2020/9/23

3.4 加法器和ALU

C8=G8+P8C7 C9=G9+P9C8= G9+ P9G8+ P9P8C7 C10=G10+P10C9= G10+ P10G9+ P10P9G8+ P10 P9P8C7 C11=G11+P11C10= G11+ P11G10+ P11P10G9+ P11P10 P9 G8+ P11P10 P9P8C7

3.4 加法器和ALU

多级先行进位

下面以16位的加法器为例,分析两级先行 进位加法器的设计方法。

C16CLA电路G4 NhomakorabeaP4G3 P3

S16~S13

S12~S9

G2 P2 S8~S5

G1 P1 S4~S1

BCLA加 C12 BCLA加 C8 BCLA加 C4 BCLA加

法器

法器

法器

法器

C0

A16~A13

由全加器的逻辑表达式可知:

Si=Ai⊕Bi⊕Ci-1

Ci Gi PiCi1

Ci=AiBi+(Ai ⊕ Bi)Ci-1

2020/9/23

Gi

Pi

3.4 加法器和ALU

(1)串行进位链电路

把n个全加器串接起来,就可以进行两个n位 数的相加。这种加法器称为串行进位的并行加 法器。串行进位又称行波进位,每一级进位直 接依赖于前一级的进位,即进位信号是逐级形 成的。