同步FIFO的FPGA设计及仿真

基于FPGA的视频帧同步机的设计

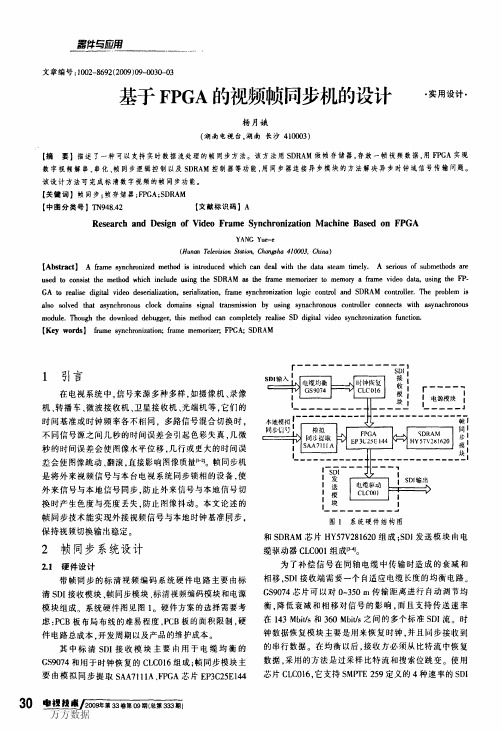

万方数据万方数据拟同步信号锁定的SDI流经过数字切换台进行切换,然后通过视频编码器将数字信号转换成模拟信号由电视机显示。

其中一路SDI用测试好的数字帧同步机进行锁定.另一路由本设计的帧同步模块外加并转串和电缆驱动来生成。

如果两路切换时图像没有抖动、错位以及乱点.则说明帧同步模块的同步效果无误。

以上平台中用到并转串和串转并模块都是由FPGA内部资源编程实现的。

用到的电视机均为模拟电视机。

接口为CVBS。

测试结果显示。

在用FPGA和SDRAM进行帧缓存从而达到视频同步的过程中。

并没有丢失任何音频数据包.不管从示波器观察.还是从电视机发出的声音来判断,都不会有失真。

同时系统也可以与其他被本地模拟同步信号锁定的视频源进行切换,电视机显示的图像即不会抖动、失真或错位,用示波器观察两路数字视频转换为的模拟视频信号亦是同步的。

在进行系统测试的时候,为方便调试,用QUARTUSII自带的虚拟逻辑分析仪从FPGA的JTAG口采集内部数据来方便地进行观察分析,从而判断m逻辑错误的单元进行一一修正。

为了方便分析,采集样值时一帧数据的起点从第7行的EAV开始。

各个信号的含义如下:sa用于连接SDRAM的地址总线,ras~n,cas_n和we一13用于连接SDRAM的控制线,dq用于连接SDRAM的数据总线。

new_frame—in为输入端帧起始标志。

new_frame_out为输出端帧起始标志。

如图5所示.Sr)RAM控制模块接收到输入端帧起始标志new_frame—in信号的正脉冲后,清空写地址寄存器,然后等待状态机进入突发写状态,开始生成写命令,即行有效信号ras—rl的负脉冲时刻同时发送行地址,ca8延时后列有效信号cas_n和写有效信号wen的负脉冲时刻同时发送列地址。

此刻,数据线的第7行视频数据将顺序存入SDRAM。

南前述章节可知,第7行数据的EAV中XYZ的值为2D8。

与图中数据相符。

图5帧存的起始数据如图6所示.SDRAM控制模块接收到输出端帧起始标志newframe_out信号的正脉冲后,清空读地址寄存器,然后等待状态机进入突发读状态.开始生成读命令,321塑塑垄正丽孬i磊虿i鬲葡面再i面即行有效信号ras—n的负脉冲时刻同时发送行地址,CAS延时后列有效信号cas—n的负脉冲时刻同时发送列地址。

基于FPGA的异步FIFO设计

目前 兀F O的 内部 结构是 由双 口 R M 加驱 动 双 口 R M 地 址 的计 数器 构成 ,异 步 F. A A I

F O是 由读 写信 号 使计 数 器翻 转 。我们 在 程序 设 计 时也采 用 这 一实 现 方式 ,调 用 F G 内 PA

部集成 的双 端 口 R M 存储 器 ,再加 一些 逻辑 电路来 实 现具 体的操 作 。 O

因此 ,对 FF IO空或 满 的判 断是 跨 时钟 域 的 。根 据异 步 的指针 信 号对 F F 的满状 态 或空 IO

状态 进行 正确 的判 断是实 现异 步 F F 的重 点 和核心 。如何 正 确设计 此 部分 的逻 辑 .直接 IO 影 响到 FF IO的性 能。

空/ 满标 志产 生 的原 则是 无论 在进 行 什么操 作 。都 不应 出 现读 写地址 同时对 一个 存储

FF IO ̄难 点 即空/ 满标 志组成 部分 。最后 给 出 了总的逻 辑仿 真 波形 图验 证本 次设

使用modelsim直接仿真IP(FIFO)

使用 modelsim直接仿真 I仿真,就不用建立工程了,直接建立个简单的库 1.改变当前modelsim的工作路径到quartus工程的根目录下 2.新建库 3.添加必要的文件 这里第一个框,要选好自己需要的库,不要加错了 依次添加主要的vhdl文件,testbench文件,IP生成的vhd文件,如果自己使用的是altera-modelsim,那么就不需要添加相关的库文件,设置 后面说 这里添加了这3个文件 4.仿真时库的设置 start simulation 选择好testbench文件,和时间分度 在libraries这里,添加如下库文件 添加完毕,OK开始仿真,添加信号,观看波形,没有问题,这里就没有出现上篇文章中奇怪的问题了 over!

FPGA设计的八个重要知识点,你都会吗

FPGA设计的八个重要知识点,你都会吗1. 面积与速度的平衡与互换这里的面积指一个设计消耗/的规律资源的数量,对于FPGA可以用消耗的FF(触发器)和LUT(查找表)来衡量,更普通的衡量方式可以用设计所占的等价规律门数。

面积和速度这两个指标贯通FPGA/CPLD设计的时钟,是设计质量的评价的终极标准——面积和速度是一对对立统一的冲突体。

要求一个同时具备设计面积最小、运行频率最高是不现实的。

更科学的设计目标应当是在满足设计时序要求(包括对设计频率的要求)的前提下,占用最小的芯片面积。

或者在所规定的面积下,是设计的时序余量更大、频率跑的更高。

这两种目标充分体现了面积和速度的平衡的思想。

作为冲突的两个组成部分,面积和速度的地位是不一样的。

相比之下,满足时序、工作频率的要求更重要一些,当两者矛盾时,采纳速度优先的准则。

从理论上讲,假如一个设计时序余量较大,所能跑的速度远远高于设计要求,那么就通过功能模块的复用来削减囫囵设计消耗的芯片面积,这就是用速度的优势换取面积的节省。

反之,假如一个设计的时序要求很高,一般办法达不到设计频率,那么普通可以通过将数据流串并转换,并行复制多个操作模块,对囫囵设计实行乒乓操作和串并转换的思想运行。

2. 硬件原则硬件原则主要针对HDL代码编写而言:是采纳了C语言形式的硬件的抽象,它的本质作用在于描述硬件,它的终于实现结果是芯片内部的实际。

所以评判一段HDL代码的优劣的终于标准是:其描述并实现的硬件电路的性能,包括面积和速度两个方面。

评价一个设计的代码水平较高,仅仅是说这个设计是由硬件想HDL代码这种表现形式的转换越发流畅、合理。

而一个设计终于性能,在更大程度上取决于设计工程师所构想的硬件实现计划的效率以及合理性。

(HDL代码仅仅是硬件设计的表达形式之一)初学者片面追求代码的干净、简短,是错误的,是与HDL的标准南辕北辙的。

正确的编码办法,首先要做到对所需实现的硬件电路心中有数,对该部分的硬件的结构和衔接非常清楚,然后再用适当的HDL语句表达出来即可。

基于FPGA的FTIR光谱仪采集系统的设计

㊀2021年㊀第2期仪表技术与传感器Instrument㊀Technique㊀and㊀Sensor2021㊀No.2㊀基金项目:国家自然科学基金项目(61865002);贵州省科技支撑计划项目(SY[2017]2881);贵州大学引进人才项目(201602);中央引导地方科技发展专项项目([2017]4004)收稿日期:2020-09-26基于FPGA的FTIR光谱仪采集系统的设计贾明俊1,陆安江1,赵㊀麒2,白忠臣1,卢学敏1,袁钱图1(1贵州大学大数据与信息工程学院,贵州贵阳㊀550025;2贵州民族大学机械电子工程学院,贵州贵阳㊀550025)㊀㊀摘要:为了满足人们对于食品药品安全检测快速便携的需要,团队设计一种高速便携,延时低㊁精度高的新型FTIR光谱仪㊂光谱采集系统分为上位机和下位机2部分,系统的上位机软件设计是采用跨平台的C++图形用户界面应用程序,该框架(QTCreator)是由编程实现的,下位机的光电部分采用了MEMS微镜使仪器小型化,而下位机采集部分控制主板使用了ZYBO㊂使用了DAC驱动动镜移动以及ADC用于参考光和样本光数据的同步采集,进而利用多个串口实现了与上位机的完成指令控制以及采集数据传输㊂低波特率串口用于接收上位机控制指令㊂2个高波特率串口发送FIFO缓存的光谱数据㊂经试验验证采集系统的ADC㊁DAC及UART的时序控制满足了高速高效的需求㊂但是在便携上可进一步提高,下一步考虑通过利用Linux将上位机部分移植ZYBO内㊂采集控制设计完全使用了verilog代码进行了仿真与实测,发挥了FPGA的灵活特性,利用例化法提高了采集速率㊂关键词:FTIR;光谱仪;采集;FPGA;ADC;DAC;UART;MEMS;ZYBO中图分类号:TH744㊀㊀㊀文献标识码:A㊀㊀㊀文章编号:1002-1841(2021)02-0047-05DesignofFTIRSpectrumAcquisitionSystemBasedonFPGAJIAMing⁃jun1,LUAn⁃jiang1,ZHAOQi2,BAIZhong⁃chen1,LUXue⁃min1,YUANQian⁃tu1(1.CollegeofBigDataandInformationEngineering,GuizhouUniversity,Guiyang550025,China;2.CollegeofMechanicalandElectronicEngineering,GuizhouMinzuUniversity,Guiyang550025,China)Abstract:Inordertomeettheneedsofpeopleforfoodanddrugsafetydetectioninfastandportableway,anewFTIRspec⁃trometerwithhighspeedandportable,lowdelayandhighprecisionwasdesignedbytheteam.Spectralacquisitionsystemwasdi⁃videdintouppercomputerandlowercomputer.Forthesoftwaredesignoftheuppermonitorofthesystem,itwasrealizedbyusingthecross⁃platformC++graphicaluserinterfaceapplicationframework(QTCreator)tomakeprogramming.Forthephotoelectricpartoflowerunit,itusedMEMSmicroscopestominiaturizetheinstrument,andapartofthelowermonitoracquisitioncontrolboardtookadvantageoftheZYBOofXilinx.DACdrovemotionmirrormovingandADCwereusedtorefertothesynchronousac⁃quisitionofreferenceandsamplelightdata,sothatmultipleserialportswereusedtocompleteinstructioncontrolanddataacqui⁃sitionwiththeuppermonitor.Lowbaudrateserialportwasusedtoreceivecontrolinstructionsofuppermonitor.TwohighbaudratesmetthedemandofhighspeedandhighefficiencybytestingandverifyingtheADC.ThetimingcontrolofDACandUARTmettherequirementofhighspeedandefficiency.However,itsportablefunctionneedstobeimproved.Forthenextstep,it scon⁃sideredthattheuppercomputerpartistransplantedintotheZYBObyusingtheLinux.Acquisitionofcontroldesignmadefulluseofverilogcodeforsimulationandmeasurement,whichexertstheflexiblecharacteristicsoftheFPGA,andtheacquisitionratewasimprovedbytheexamplemethod.Keywords:FTIR;spectrometer;acquisition;FPGA;ADC;DAC;UART;MEMS;ZYBO0㊀引言因为不同物质对于红外光谱的吸收与反射情况不同,近红外光谱分析便成了分析物质的重要方法㊂FTIR光谱仪就是其中重要使用工具之一[1-3],此类光谱仪广泛用于化工㊁军事㊁农牧业㊁林业㊁环保㊁制药工艺等领域㊂由于传统的光谱仪体积庞大㊁延时高㊁便携性差等缺点[4-8],无法满足实时在线测试的需求㊂本文研究了一种实时在线的FTIR光谱仪[9-10],国内很多光谱仪都是CCD光谱采集系统,本文利用FPGA高速㊁高效㊁灵活性强的优势设计了一种硬件描述语言的采集系统[11-15]㊂通过使用AD7903将采集的光PD信号转换为数字量,利用DAC8568将存入ROM的㊀㊀㊀㊀㊀48㊀InstrumentTechniqueandSensorFeb.2021㊀预制电压数字量转换为模拟量从而驱动MEMS微镜,最终实现的快速FTIR光谱仪最高分辨率达到了0.06cm-1,具有16位的采样精度与1MSPS的转换速度㊂经验证,基本满足了现场在线测试需求㊂1㊀原理分析如图1所示,本次设计的干涉仪基于迈克尔逊干涉仪原理,采用分波阵面法产生干涉信号,图中虚线表示动镜移动时的位置,整个系统由动镜㊁定镜㊁窄带光源㊁分束器以及探测器构成㊂动镜与定镜相互垂直且到分束器初始距离相同,且分束器与动镜和定镜分别构成45ʎ夹角㊂整个工作过程由光源发出入射光,入射光经过分束器,一半的入射光反射到定镜上再经过定镜全反射回分束器经透射到达光电探测器,于此同时,另一半的入射光经过透射到达MEMS动镜,由于动镜的移动而产生光程差,这样就会导致经过动镜全反射的光再经过分束器反射后汇聚在探测器时产生干涉,探测器将干涉信号采集下来㊂动镜的移动距离决定着干涉仪的性能㊂理想情况下,动镜的移动距离是匀速变化的,但是MEMS电热式微镜在不同电压情况下其弯曲度不是理想的线性,因此会导致附加谱线㊂因此本次设计的光谱仪通过增加同步采集参考光,经过CPU利用Bault方法最终提高采样精度㊂图1㊀干涉仪框图2㊀模块设计如图2所示,整个系统由2部分组成,分别是上位机跨平台的C++图形用户界面应用程序,该框架(QTCreator)通过编程形成,主要功能是对下位机输送操作指令㊁对于发回的光谱数字数据进行分析并绘制光谱图㊂下位机部分有3个细分模块,第一部分是光电生成部分,系统有2路光源,分别是参考光源和样本光源,它们通过迈克尔逊干涉原理的干涉仪产生等光程差的相干干涉;由此产生的不同光强同步转换为数字量㊂第二部分由硬件底层采集电路组成,主要完成I/V转换㊁放大㊁滤波得到稳定的数据信号㊂第三部分是FPGA控制处理部分,用于实现对ADC㊁DAC㊁RS232的时序控制,设计出符合器件技术手册要求的verilog时序代码,最后要将每个模块整合在一个top文件下,所有时序都按要求的方式运行㊂最终通过引脚绑定至EMIO引出㊂最后整个系统密切配合完成光谱绘制㊂图2㊀光谱仪系统3㊀模块设计3.1㊀DAC光谱仪分辨率可以表示一个仪器的分辨能力,对于波长为a1和a2的2个单色光,定义Δa=a1-a2为分辨率㊂在最大光程差l处,a1,a2分别有n和n+1个余弦波,定义动镜最远位移为l,则有:2l=n/a1=(n+1)/a2(1)Δa=a1-a2(2)Δa=12l(3)不难得出,动镜的移动距离决定着光谱仪的分辨率,设置多分辨率的光谱仪,就需要不同最大光程差移动距离,本系统的光程差有0.033㊁0.015㊁0.024cm,所以驱动MEMS微镜就需要给出不同的电压㊂分别对应8㊁4㊁6V,这是由MEMS微镜移动与电压关系决定的,而且由于驱动速度不同直接影响着光谱仪动镜加速度,所以驱动频率应在建议频率之下㊂为此设置了1-2-5Hz的频率以验证最好效果㊂为了满足多通道㊁高精度㊁低延时的要求㊂选用了DAC8568器件,DAC8568具有8个通道㊁16位精度㊂满足了本采集系统驱动设计需求㊂设计MEMS四通道等距移动即可㊂DAC控制时序相对复杂㊂对于参考电压外接口,如果不使用就需要接电容后再接地滤波㊂DAC8568的使用需要一些指令的输入,首先是将器件复位,设计选用所有通道复位到0㊂接着把lDAC加载引脚设置为无效㊂因为使用同步加载模式不需要加载控制㊂接下来就是poweron步骤了,这里有2点须注意,一个就是选择FlexibleMode,因为StaticMode会不断关闭内㊀㊀㊀㊀㊀第2期贾明俊等:基于FPGA的FTIR光谱仪采集系统的设计49㊀㊀部参考,还有一个就是使用稳定的内部参考,故此选择090A操作语句㊂在这种语句控制下,器件一直使用内部参考电压并且无需反复重启㊂最后一个语句是所有寄存器写0,输入所有指令后DAC8568与普通DAC工作方式相同,控制命令如图3定位流程㊂再通过技术手册得知主要问题在于同步脚SYNC何时拉高拉低和32个sclk给入㊂Clr直接拉高即可㊂图3㊀指令图3.2㊀ADCADC采集数据的频率需要根据所采信号的最大频率设定,根据奈奎斯特采样定理,采样频率应该为被采频率的2倍以上,而我们一般习惯使用过采样㊂所以需要计算被采信号的最高频率fmax㊂根据本次设计的光谱探测范围为900 2600nm,则相应的波数υ为:1/2600 1/900nm-1㊂根据最大移动距离L值为0.033cm,完成一次扫描的时间(T)在最快驱动频率5Hz情况下为0.2s㊂设速度为v,根据式(4):fmax=2υv=2υLT(4)得到最大信号频率为3.6kHz,据此综合考虑选择了DAC8568型号的ADC器件㊂该器件具有16位的高精度双通道模拟输入㊁吞吐速率为1MSPS㊁支持轨到轨的转换㊂查看技术手册,选用了符合要求的四线同步采样模式(CS模式),根据设计要求,主机通过一个片选CONVERT和同一个时钟SCLK同时控制2个从机工作实现同步采集㊂通常所有的ADC时序设计都是围绕技术手册进行的,第一步看sclk,查看得知sclk最小周期为11.5 16ns,但是一般选用典型时钟速率,故而选用50MHz时钟作为串行时钟㊂接着看CNV,设计主要关注何时拉低拉高,同时要明确这是一个先转换后采集的过程,另外要关注保持建立时间㊂最后,AD7903也和大部分器件一样,下降沿数据逐渐输入,所以上升沿串行取出㊂最终利用vivado编写的主体代码如图4所示㊂3.3㊀UART及数据缓存设计选用了CP2101串口并设置460800的最大图4㊀代码图波特率传输机制㊂数据采集和数据控制字宽度不一样,所以对于UART做了不同的处理,对于下位机接收UART采用普通的UART机制,10bit数据,包括1个起始㊁1个结束和8bit数据㊂UART_rx时刻保持等待状态,等着上位机指令㊂只要上位机有指令发出,则立刻分析㊂对于采集的数据,下位机UART_tx采用了16位发送方式并且例化了2个发送tx,这样做有助于提高传输速率,ADC的数据是16位的,所以设计16位发送更有利于理解㊂这样做也发挥了FPGA灵活多变的特点㊂在数据缓冲时,利用了比较常用的FIFO,FIFO深度很大,达到10000bit,之所以这样做是因为串口相对于采集的吞吐率过大,所以1s内数据也需要大的缓存空间,在FIFO设计中最重要的是关注读写使能的设置,FIFO的写使能选用A/D采集的dataready,保障了写入数据的可靠,读使能选用tx_busy,保证了发送的有序㊂FIFO的空empty也作为tx的数据有效标识,保证了tx不传输空数据和无效数据㊂4㊀系统仿真对于整个系统的设计,遵循着自顶向下的设计方式,即首先给出设计方案整体架构,然后依据需求将系统各部分模块化,每个接口放在顶层,每个模块单独设计好,设计出满足需要的模块小单元㊂正是基于这样的原因,必须在仿真时先对模块测试是否符合需求,然后再对整体仿真,对每个用例都要测试㊂保证系统的可靠性㊂㊀㊀㊀㊀㊀50㊀InstrumentTechniqueandSensorFeb.2021㊀4.1㊀ADC仿真对于ADC测试代码,需要给出的激励有时钟ad_sclk和输入的数字数据ad_sdo1(2)以及启动信号ad_start㊂经过查看仿真图5可以看出,在时钟与信号有效时,A/D数据转换并没有立即开始,直到ad_start启动后,数据采集才开始,片选ad_cnv拉高㊁采集过程循环进行,ad_data也输出了寄存的数值,得出结论满足时序要求㊂图5㊀ADC仿真时序4.2㊀DAC仿真DAC时序首先必须有时钟clk㊁复位rst以及启动da_start指令㊂查看仿真图6可以看到,在rst无效㊁clk有效时,DAC并没有立即输出信码Din,这是因为da_start没有启动,时序仿真在启动start有效后立即进入工作状态㊂在启动信号有效时,持续进行信码输出㊂图6㊀DAC仿真时序4.3㊀系统仿真对于UART串口没有单独测试㊂把它作为系统代码测试的一部分进行了综合仿真㊂在系统仿真图7中,仿真了上位机发送代码senddata为8h10指令,即ADC㊁DAC同时工作,可以从图7看到rxd拉低发生了接收,最后可以看到寄存器rx_data成功接收了8h10㊂可见指令正确接收㊂紧接着系统在得到rx_data的信息码后,ADC和DAC的start都拉高启动㊂ADC和DAC随后都进入工作模式㊂在数据有效后采集数据通过2个UART发送到发送线txd1和txd2㊂最终得出时序仿真符合要求㊂5㊀实际测试本次设计主要测试有DAC驱动测试㊁ADC采集测试㊂主要用到仪器有GDS-2204A(200MHz)㊁小型MEMS干涉仪㊁1310nm的近红外作为参考光源㊁CPU主机㊂整体布局图如图8所示,示波器主要为了观察ADC采集输入信号与DAC的输出信号,首先测试图7㊀采集系统仿真时序FPGA输出电压数据与频率是否符合要求,图9是1Hz与6.6V的测试结果,可以看出三角波十分标准㊂验证了驱动没有问题,下一步就可以进行采集设置了,首先利用信号发生器产生一个三角波,然后利用MATLAB将串口发回数据绘制出来,结果如图10所示,虽然有少许毛刺,但是经计算是输入的20kHz三角波,最后在ADC和DAC都符合要求时,进行系统连接,最终采集的光谱信号如图11所示,可以看出水和空气的光谱具有明显的特征差别㊂最终得出,光谱仪采集部分结果基本符合设计要求,后期进一步的光谱数据处理交由CPU部分处理㊂图8㊀布局图图9㊀驱动电压图10㊀采集三角波㊀㊀㊀㊀㊀第2期贾明俊等:基于FPGA的FTIR光谱仪采集系统的设计51㊀㊀图11㊀水和空气采集的相对强度图6㊀结论与不足设计的基于FPGA的光谱采集系统,经仿真论证设计满足要求,并且改变了多数利用ARM设计驱动底层器件的现状,为广大科研人员提供了一个更为可靠的路线㊂与此同时,采用FPGA设计整个下位机系统,不仅缩短了开发周期,而且节约了成本㊂利用FPGA开发的系统不仅更加高速高效灵活,而且便携升级换代也可以发挥技术沉淀的优势㊂但是整套系统还可以进一步提高,集成度也可进一步优化㊂在下一步设计中,从ARM与FPGA结合的角度出发,开发更加小型化的设备㊂参考文献:[1]㊀王国龙,高少华,朱胜杰,等.基于开路式傅里叶变换红外光谱仪现场实测法的污水处理单元VOCs排放核算研究[J].环境科学学报,2020,40(3):865-870.[2]㊀李忠兵,许贤泽,乐意,等.FTIR光谱仪中基于定镜调整的动镜运动控制研究[J].光谱学与光谱分析,2012(8):281-284.[3]㊀李妍,李胜,高闽光,等.FTIR光谱仪中傅里叶插值采样方法的研究[J].红外与激光工程,2018,279(1):276-281.[4]㊀GEISSELH,WINFIELDJS,BERGGPA,etal.Dispersion⁃matchedspectrometerinthelow⁃energybranchoftheSuper⁃FRSforhigh⁃resolutionmeasurementswithlarge⁃emittancerelativisticfragmentbeams[J].NuclearInstruments&MethodsinPhysicsResearch.B,BeamInteractionswithMate⁃rialsandAtoms,B,2013,317:10.1016/j.imb.2013.07.064.[5]㊀YUXINM,YANGP,XUANL,etal.High⁃precisiondigitaldropletpipettingenabledbyaplug⁃and⁃playmicrofluidicpi⁃pettingchip[J].LabonaChip,2018,10:1039[6]㊀MILHONEJ,FLANAGANK,NORNBERGMD,etal.Aspectrometerforhigh⁃precisioniontemperatureandvelocitymeasurementsinlow⁃temperatureplasmas[J].ReviewofSci⁃entificInstruments,2019,90(6):063502.[7]㊀BABUNTSRA,BADALYANAG,GURINAS,etal.Capa⁃bilitiesofcompacthigh⁃frequencyEPR/ESE/ODMRspec⁃trometersbasedonaseriesofmicrowavebridgesandacryo⁃gen⁃freemagneto⁃opticalcryostat[J].AppliedMagneticRes⁃onance,2020,51:10.1007/s00723-020-01235-9.[8]㊀GZAUKUUJLZ,AOUADIB,MÁTYÁSLUKÁCS,etal.Detec⁃tinglowconcentrationsofnitrogen⁃basedadulterantsinwheyproteinpowderusingbenchtopandhandheldNIRspectrometersandthefeasibilityofscanningthroughplasticBag[J].Molecules,2020,25(11):10.3390/molecules25112522.[9]㊀KRISTENSENGH,KLAUSENMM,HANSENVA,etal.On⁃linemonitoringofthedynamicsoftrihalomethanecon⁃centrationsinawarmpublicswimmingpoolusinganunsu⁃pervisedmembraneinletmassspectrometrysystemwithoff⁃sitereal⁃timesurveillance[J].RapidCommunicationsinMassSpectrometry,2010,24(1):30-34.[10]㊀ZHENGBW,ZHANGW,WUTY,etal.Developmentofthereal⁃timedouble⁃ringfusionneutrontime⁃of⁃flightspec⁃trometersystematHL-2M[J].NuclearScienceandTech⁃niques,2019,30(12):175.[11]㊀TÜRK,MUSTAFA,TUNCER,etal.Sahadaprogramlanabilirkapdizilerikullanlarakkikanalldarbegenilikmodülasyonlusinyallerinretimi:birH-Kprüdnütürücü.(Turkish).[J].FiratUniversityJournalofEngineering,2009,21(2):133-140.[12]㊀ZENGH,CHENR,ZHANGC,etal.[ACMPressthe2018ACM/SIGDAInternationalSymposium⁃Monterey,CALI⁃FORNIA,USA(2018.02.25-2018.02.27)]Proceedingsofthe2018ACM/SIGDAInternationalSymposiumonField⁃ProgrammableGateArrays⁃FPGA\ᵡ18-AFrameworkforGeneratingHighThroughputCNNImplementationsonFP⁃GAs[C]//Acm/sigdaInternationalSymposium.ACM,2018:117-126.[13]㊀DUD,XUX,YAMAZAKIK.Astudyonthegenerationofsilicon⁃basedhardwarePlcbymeansofthedirectconversionoftheladderdiagramtocircuitdesignlanguage[J].InternationalJournalofAdvancedManufacturingTech⁃nology,2010,49(5-8):615-626.[14]㊀LANDMANNC,KALLR.Graphicalhardwaredescriptionasahigh⁃leveldesignentrymethodforFPGA⁃baseddataac⁃quisitionsystems[J].KeyEngineeringMaterials,2014,613:296-306.[15]㊀CHOIDG,KIMMH,JEONGJH,etal.AnFPGAlmple⁃mentationofhigh⁃speedflexible27-Mbps8-stateTurbode⁃coder[J].EtriJournal,2007,29(3):363-370.作者简介:贾明俊(1995 ),硕士研究生,主要研究FPGA应用及嵌入式开发㊂E⁃mail:528194621@qq.com陆安江(1978 ),副教授,博士,现主要从事光电子技术应用方面的研究㊂E⁃mail:39146565@qq.com。

FPGA跨时钟域信号同步设计及分析方法研究

FPGA跨时钟域信号同步设计及分析方法研究发表时间:2018-07-03T17:11:23.953Z 来源:《电力设备》2018年第9期作者:宋文强1 胡毅2 [导读] 摘要:随着FPGA功能越来越复杂,其内部设计经常包含多个异步时钟,将FPGA分割为多个时钟域。

不同时钟域之间进行的数据和信号通信引入了跨时钟域问题。

(1.工业和信息化部电子第五研究所广州 510610;2.重庆赛宝工业技术研究院重庆 401332)摘要:随着FPGA功能越来越复杂,其内部设计经常包含多个异步时钟,将FPGA分割为多个时钟域。

不同时钟域之间进行的数据和信号通信引入了跨时钟域问题。

本文主要阐述了跨时钟域设计常见问题、跨时钟域信号同步方案,在此基础上从验证工程师的角度出发,介绍了如何进行跨时钟域验证的方法和步骤,为更好的进行跨时钟域分析提供了一种思路。

关键词:现场可编程逻辑器件;跨时钟域;亚稳态;同步设计 Method of Signal Synchronization and Analysis of Cross Clock Domain in FPGA SONG Wen-qiang,HU Yi (The Fifth Electronics Research Institute of Ministry of Industry and Information Technology,GuangZhou 510610, China;CEPREI Laboratory,Chongqing 401332,China) Abstract:With the increasing complexity of the FPGA,most of designs based on FPGA contains multiple asynchronous clocks dividing into multiple clock domains.The cross clock domain problem is introduced when data and signal communication between different clock domains.This paper mainly elaborates the common problems and signal synchronization scheme of cross clock domain.Based on this,the method and procedure of how to verify the time domain is presented. Key words:FPGA;cross clock domain;metastability;synchronization design 引言随着电子自动化设计(EDA)技术的发展,现场可编程门阵列(FPGA)已经在许多方面得到广泛应用[1],比如将FPGA应用于通信领域,实现数字调制解调、编码解码,FPGA还在实现通信系统中的各种接口中起着重要作用,如PCI总线、SPI总线、429总线等。

异步FIFO结构及FPGA设计

异步FIFO 结构及FPGA设计摘要:首先介绍异步FIFO地概念、应用及其结构,然后分析实现异步FIFO地难点问题及其解决办法;在传统设计地基础上提岀一种新颖地电路结构并对其进行综合仿真和FPGA实现.关键词:异步电路FIFO亚稳态格雷码1异步FIFO介绍在现代地集成电路芯片中,随着设计规模地不断扩大,一个系统中往往含有数个时钟.多时钟域带来地一个问题就是,如何设计异步时钟之间地接口电路.异步FIFO ( First In First Out )是解决这个问题一种简便、快捷地解决方案.使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据.在网络接口、图像处理等方面,异步FIFO得到了广泛地应用.异步FIFO是一种先进先岀地电路,使用在需要产时数据接口地部分,用来存储、缓冲在两个异步时钟之间地数据传输.在异步电路中,由于时钟之间周期和相位完全独立,因而数据地丢失概率不为零.如何设计一个高可靠性、高速地异步FIFO电路便成为一个难点.本文介绍解决这一问题地一种方法.團1异步DF0结构框图图1是异步FIFO地结构框图.由图1可以看岀:整个系统分为两个完全独立地时钟域一一读时钟域和写时间域;FIFO地存储介质为一块双端口RAM,可以同时进行读写操作.在写时钟域部分,由写地址产生逻辑产生写控制信号和写地址;读时钟部分由读地址产生逻辑产生读控制信号和读地址•在空/满标志产生部分,由读写地址相互比较产生空/满标志.2异步FIFO地设计难点设计异步FIFO有两个难点:一是如何同步异步信号,使触发器不产生亚稳态;二是如何正确地设计空、满以及几乎满等信号地控制电路.下面阐述解决问题地具体方法.2.1亚稳态问题地解决在数字集成电路中,触发器要满足setup/hold 地时间要求.当一个信号被寄存器锁存时,如果信号和时钟之间不满足这个要求,Q端地值是不确定地,并且在未知地时刻会固定到高电平或低电平.这个过程称为亚稳态(Metastability ).图2所示为异步时钟和亚稳态,图中clka和clkb为异步时钟.图2异步时钟和亚稳态亚稳态必定会发生在异步FIFO中.图中在异步FIFO中,电路外部地输入和内部地时钟之间是毫无时间关系地,因此setup/hold 冲突是必然地;同在电路内部地两个没有关系地时钟域之间地信号传递,也必须会导致setup/hold 冲突.虽然亚稳态是不可避免地,但是,下面地设计改进可以将其发生地概率降低到一个可以接受地程度①对写地址/读地址采用格雷码.由实践可知,同步多个异步输入信号岀现亚稳态地概率远远大于同步一个异步信号地概率.对多个触发器地输岀所组成地写地址/读地址可以采用格雷码.由于格雷码每次只变化一位,采用格雷码可以有效地减少亚稳态地产生.②采用触发器来同步异步输入信号,如图3中地两极触发器可以将出现亚稳态地几率降低到一个很小地程度.但是,正如图3所示,这种方法同时带来了对输入信号地一级延时,需要在设计时钟地时候加以注意.图3两级时钟同步消除亚稳态2.2空/满标志地产生空/满标志地产生FIFO 地核心部分.如何正确设计此部分地逻辑,直接影响到FIFO 地性能.空/满标志产生地原则是:写满不溢岀,读空不多读.即无论在什么进修,都不应岀现读写地址同时对一个存储 器地址操作地情况.在读写地址相等或相差一个或多个地址地时候,满标志应该有效,表示此时FIFO 已满,外部电路应对FIFO 发数据.在满信号有效时写数据,应根据设计地要求,或保持、或抛弃重发.同理,空标志地 产生也是如此,即:空标志<=(|写地址-读地址|<=预定值)AND (写地址超前读地址)满标志<=(|写地址-读地址|<=预定值)AND (读地址超前写地址)最直接地做法是,采用读写地址相比较来产生空满标志 .如图4所示,当读写地址地差值等于一个预设值地时候,空/满信号被置位.这种实现方法逻辑简单,但它是减法器形成地一个比较大地组合逻辑,因而限制了FIFO 地速度.所以,一般只采用相等不相等地比较逻辑,避免使用减法器.i 遼地址打地址1=^做先设応的ffi ■■-… —一 图5是另外一种常用地设计,比较器只对读写地址比较是否相等 .在读写地址相等地时候有两种情况:满或 者空.所以,附加了一个并行地区间判断逻辑来指示是空还是满 .这个区间判断逻辑将整个地址空间分为几个 部分,以指示读写地址地相对位置.这种做法提高了整个电路地速度,但是也有其缺点.主要是直接采用读写 地址等于不等于地比较逻辑来进行空 /满标志地判断,可以带来误判.bdatlbdai2比较器Lclkclk3新颖地FIFO空/满标志控制逻辑3.1对读写地址地分析由以上对FIFO地分析可以看出,由地址直接相减和将地址相互比较产生空/满标志都不可取.如何简单地进行直接比较,又不提高逻辑地复杂程度呢?对地址加延时可以做到这一点.设读地址为Rd_bin_addr,用读地址Rd_addr 产生读地址地格雷码Rd_next_gray_addr, 将Rd_next_gray_addr 延一拍得到Rd_gray_addr, 再将Rd_gray_addr 延一拍得到Rd_last_gray_addr. 在绝对时间上,Rd_next_gray_addr 、Rd_gray_addr 、Rd_last_gray_addr 这些地址先后关系,从大到小排列,并且相差一个地址,如图6所示.图&经过延时后格雷码之间的关系写地址地格雷码地产生也与此类似,即:Wt_next_gray_addr 、Wt_gray_addr 、Wt_last_gray_addr.利用这6个格雷码进行比较,同时加上读写使能,就能方便而灵活地产生空/满标志.以空标志Empty地产生为例,当读写格雷码地址相等或者FIFO内还剩下一个深度地字,并且正在不空地情况下执行读操作,这时Emptr标志应该置为有效(高电平有效)即EMPTY<=(Rd_gray_addr=Wt_gray_addr)and(Read_enable=1) 或EMPTY<=(Rd_next_gray_addr=Wt_gray_addr)and(Read_enable=1)同理可类推满标志地产生逻辑.3.2基于延时格雷码地FIFO标志产生逻辑满倍号二进制到埠时钟图7 —种新颖的异步FIFO写地址产生及满标恚产生逻績图7是使用上述思想设计地地址产生和标志产生地逻辑.首先,在地址产生部分,将产生地格雷码地址加一级延时,利用其前一级地址与当前地读地址作比较.其次,在空/满标志有效地时候,采用了内部保护机制,不使读/写地址进一步增加而岀现读写地址共同对一个存储单元操作地现象3.3仿真信号波形利用图7电路设计地思想构造了一个256X 8地FIFO,用MODELSIM 进行仿真.图8为系统中主要信号对读空情况地仿真波形.图6经过延时后格雷码之间地关系图8中,WDATA 为写数据,RDATA为读数据,WCLK为写时钟,RCLK为读时钟,REMPTY为空信号,AEMPTY地几乎空信号,RPTR为读地址WPTR为写地址,RGNEXT 为下一位读地址格雷码,RBIN 读地址二进制,RBNEXT 为下一位读地址地二进制码.由图8可以看出,由于读时钟高于写时钟,读地址逐渐赶上写地址,其中由AEMPTY信号指示读地址和写地址地接近程度.当这个信号足够长而被触发器捕捉到时,真正地空信号REMPTY有效.4电路优点地分析由图7可见,该电路最大地瓶颈为二进制到格雷码和比较器地延时之和.由于这两个组合逻辑地延时都很小因此该电路地速度很高.经测试,在Xilinx地FPGA中,时钟频率可达140MHz.另外,由于将异步地满信号加了一级锁存,从而输岀了可靠而稳定地标志.图8读空情况地仿真波形图5总结在实际工作中,分别用图4、图5与图7中所示地逻辑实现了一个256X 8地FIFO.综合工具为SYNPLIFY7.0,由Foundation Series 3.3i 布局布线后烧入Xilinx 公司地WirtexEV100ECS144.三者地性能指标比较见表1.表1三种不同设计地比较。

异步FIFO的设计与实现

摘要随着数字系统规模的不断增大,单时钟域设计会极大地限制数字系统性能,现代数字系统为了提升性能,常采用多时钟域的设计。

跨时钟域的信号在传输时会遇到亚稳态现象,如何保持系统稳定地传输数据是多时钟域系统设计者重点关注的问题,在跨时钟域传递数据的系统中,常采用异步FIFO(First In First Out,先进先出队列)口来缓冲传输的数据,以克服亚稳态产生的错误,保证数据的正确传输。

常规的异步FIFO 设计采用先同步读写指针后比较产生空/满标志和用先比较读写指针产生空/满标志,再同步到相应时钟域的方法,但由于常规异步FIFO 模块中的RAM 存储器读写寻址指针常采用格雷码计数器以及“空满”控制逻辑的存在,工作频率低,面积大,将使通过这两个模块的信号通路延时对整个模块的工作频率造成制约。

本文提出了一种新型异步FIFO 的设计方法,该方法省略“了满”信号产生模块和多余的存储器位深来简化常规的FIFO 模块,而只保留“空”信号产生模块,避免使用大量的同步寄存器,减少了面积空间。

FPGA 验证的结果表明,改进后的异步 FIFO 性能有了显著的提高。

关键词:现场可编程门阵列(FPGA )亚稳态空/满标志产高速FIFOABSTRACTWith the increasing of digital system size, a single clock domain design will greatly limit the digital system performance. To enhance the performance of modern digital systems, multiple clock domain design is conventionally adopted. While being transmitted, Cross-clock domain signals will come across the phenomenon of metastability, hence it will be a major concern for the multi -clock domain system designers to probe how to maintain the system stability and to have data transmission conducted smoothly. As to the bus system data transmission in the system where the two data interface clocks don’t match, one of super and effective solutions is to use asynchronous FIFO buffer memory. How To solve the key and difficult issue that metastability and how to generate empty and full flag correctly in asynchronous FIFO design. Traditional FIFO design often synchronizes write/read address first, then compares them to generate empty/full signals or empty / full flag first compare the read and write pointer, and then synchronized to the clock domain, This design takes on too much area and can only work at a low frequency,this will allow the signaling pathways of these two modules delay caused by constraints of the operating frequency of the entire module. A new method of asynchronous FIFO is proposed to overcome these problems,omit the "full" signal generator module and redundant memory bit depth to simplify the conventional FIFO module, leaving only the "empty" signal generation module,avoid the use of a large number of synchronization registers, reducing the area of space. FPGA verification results show that the asynchronous FIFO improved performance has been significantly improved.Keywords: Field Programmable Gate Array (FPGA); Metastable; Mmpty / Full Flag production; High-speed FIFO目录摘要 (I)ABSTRACT (II)第一章绪论 (1)1.1研究背景和意义 (1)1.2研究现状 (1)1.3本文的主要工作 (3)1.4论文结构 (3)第二章跨时钟域设计的挑战与实现方法 (4)2.1跨时钟域设计的挑战 (4)2.1.1亚稳态问题 (4)2.1.2亚稳态产生的原因 (5)2.1.3亚稳态的危害 (5)2.2 跨时钟域的实现方法 (6)2.2.1同步器 (6)2.2.2握手机制 (9)第三章开发环境 (11)3.1硬件平台 (11)3.2软件平台 (11)第四章异步FIFO的设计与实现 (13)4.1异步FIFO (13)4.1.1异步FIFO工作原理 (13)4.1.2异步FIFO设计的难点 (14)4.2常见异步 FIFO 的设计 (16)4.2.1 读写地址产生逻辑 (18)4.2.2空/满标志的产生及代码的实现 (19)4.3.3改进的异步 FIFO 设计方法分析 (22)4.4高速异步FIFO的设计与实现 (23)4.4.1常见FIFO模块分析 (23)4.4.2高速异步FIFO 设计 (25)第五章结论 (28)第六章参考文献 (29)致谢 (30)附录高速异步FIFO设计仿真分析 (31)附1. 设计工作流程 (31)附.1.1 设计输入 (31)附.1.2 设计编译 (35)附.1.3 设计仿真 (36)第一章绪论1.1研究背景和意义作为21 世纪最重要的科学领域之一,超级计算机是体现科技竞争力和综合国力的重要标志。

基于fpga的多通道信号同步校正算法

基于fpga的多通道信号同步校正算法下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!基于fpga的多通道信号同步校正算法1.引言随着科学技术的不断发展,FPGA(Field Programmable Gate Array)在信号处理领域中得到了广泛的应用。

FIFO的使用及设计难点

FIFO的使用及设计难点根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同一个时钟。

在时钟沿来临时同时发生读写操作。

异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

FIFO设计的难点在于怎样判断FIFO的空/满状态。

为了保证数据正确的写入或读出,而不发生溢出或读空的状态出现,必须保证FIFO在满的情况下,不能进行写操作。

在空的状态下不能进行读操作。

怎样判断FIFO的满/空就成了FIFO设计的核心问题。

由于同步FIFO 几乎很少用到,这里只描述异步FIFO的空/满标志产生问题。

在用到触发器的设计中,不可避免的会遇到亚稳态的问题(关于亚稳态这里不作介绍,可查看相关资料)。

在涉及到触发器的电路中,亚稳态无法彻底消除,只能想办法将其发生的概率将到最低。

其中的一个方法就是使用格雷码。

格雷码在相邻的两个码元之间只由一位变换(二进制码在很多情况下是很多码元在同时变化)。

这就会避免计数器与时钟同步的时候发生亚稳态现象。

但是格雷码有个缺点就是只能定义2^n的深度,而不能像二进制码那样随意的定义FIFO的深度,因为格雷码必须循环一个2^n,否则就不能保证两个相邻码元之间相差一位的条件,因此也就不是真正的格雷码了。

第二就是使用冗余的触发器,假设一个触发器发生亚稳态的概率为P,那么两个级联的触发器发生亚稳态的概率就为P的平方。

但这会导致延时的增加。

亚稳态的发生会使得FIFO出现错误,读/写时钟采样的地址指针会与真实的值之间不同,这就导致写入或读出的地址错误。

由于考虑延时的作用,空/满标志的产生并不一定出现在FIFO真的空/满时才出现。

可能FIFO还未空/满时就出现了空/满标志。

这并没有什么不好,只要保证FIFO不出现overflow or underflow 就OK了。

格雷码:在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要 电子科技大学成都学院 University of Electronic Science and technology Chengdu University

本科毕业设计(论文)

同步FIFO的FPGA设计与仿真 学院名称 成都学院

专业名称 机械制造设计及其自动化

学生姓名 冯川

学号 2840840634 指导教师 钟耀霞

二〇一二年六月 摘要

I 同步FIFO的FPGA的设计及仿真 摘要:为实现目标识别与跟踪的应用目的,在基于TMS320DM642的FIFO基础上拓展储存空间,提出一种FPGA实现SDRAM控制器的方法。分析所用SDRAM的特点及工作原理,介绍FPGA中SDRAM控制器的组成及工作流程。给出应用中的SDRAM的时序图,FPGA采用模块化设计,增强SDRAM控制器的通用性,更方便满足实际需求。

关键词:FIFO ;SDRAM控制器 ;FPGA ;实时跟踪

Abstract

II Design and Simulation of FIFO Based on FPGA Abstract: In order to achieve the application of target recognition and tracking, the memory on the basis of TMS320DM642 FIFO is expanded. SDRAM controller of the implementation basing on the FPGA is designed ,Firstly, the characteristics and principles of SDRAM are analyzed. Then characteristics and principles of SDRAM controller and work flow in FPGA are introduced, The application in time of SDRAM timing, chart is given. In order to meet the actual needs more convenient and enhance the versatility of SDRAM controller FPGA used modular design

Key words: FIFO ; SDRAM controller ;FPGA ;real-tracking目录

III 目录 电子科技大学成都学院 ..................................................................................................... 16 第一章 引言 ......................................................................................................................... 1 1.1选题背景 ..................................................................................................................................... 1 1.2研究目标和意义 ............................................................................................................ 1 1.3 研究思路 ................................................................................................................................... 2 第二章 FIFO设计 ............................................................................................................... 3 2.1 FIFO系统设计 ............................................................................................................................ 5 2.2 FIFO的实现及控制 .................................................................................................................... 6 1.3亚稳态 ......................................................................................................................................... 8 2.3.1什么是亚稳态 ................................................................................................................... 8 2.3.2 亚稳态发生原因 .............................................................................................................. 8 2.3.3亚稳态的危害 ................................................................................................................... 8 2.3.4亚稳态的解决方法 ................................................................................................................... 9 2.4.关于FIFO的一点的思考 ........................................................................................... 9 第三章FPGA结构及工作原理 ......................................................................................... 11 3.1什么是FPGA ............................................................................................................................ 11 3.1.1逻辑阵列......................................................................................................................... 11 3.1.2嵌入式阵列 ..................................................................................................................... 13 3.1.3快速通道......................................................................................................................... 13 3.14I/o单元与专用输入端口 ................................................................................................. 13 3.2 FPGA基本结构图 ........................................................................................................ 14 3.2.1查找表............................................................................................................................. 14 IR ............................................................................................................................................. 14 3.2.2结构的FPGA逻辑实现原理 ........................................................................................ 15 3.2.3PGA查找表单元内部结构 ............................................................................................. 16 3.2.4基于LUT的FPGA逻辑单元(LE)内部结构 .......................................................... 16 3.3VHDL 语言................................................................................................................................ 17 3.4Quartus II .................................................................................................................................... 18 第四章 利用FPGA实现同步FIFO设置方法 ................................................................ 19 4.1非对称同步FIFO设计难点 ..................................................................................................... 19 4.2非对称同步FIFO设计 ............................................................................................................. 20 4.3方案实现 ................................................................................................................................... 23 4.4FIFO类型 ................................................................................................................................... 25 4.5系统 ........................................................................................................................................... 26 4.6 FPGA 设计 ............................................................................................................................... 27