FIR带通滤波器的FPGA实现

基于FPGA的FIR数字滤波器的实现

G r a p h ) 算法进 一步 简化 C S D编码 . 然后采 用 A l t e r a 公

司的 F P G A芯片来实现信号处理中的 F I R数字滤波器.

实验证 明这是 一种 F I R数 字 滤 波 器 的 较 好 的 设 计 选 择, 具 有 应 用 价值

HUA Z e , ZHAO Xi n g -h a n g , F U Z h a o - y a n g , L U Yo u , Z HANG Ni

( 1 ) 从最低有效位开始 . 用 1 0 …( ) - 1 取 代 所 有 大 于 2的 1 序 列 。此 外 还 需 用 1 1 0 — 1 取代 1 0 1 1 。 ( 2 ) 从最高有效位开始 , 用0 1 1 代替 1 0 - 1 。 例如 :

( 9 1 ) 1 0 = ( 1 0 1 1 0 1 1 ) 2 - ( 1 1 0 旷1 0 - 1 ) 佳c s D

收稿 日期 : 2 01 3 — 0 9 —1 0 修稿 日期 : 2 0 1 3 —1 0 —1 0

作 者 简介 : 陈剑 冰 , 男, 本科 , 研 究 方 向 为信 号 处理

④ 现 代 计算 机 2 0 1 3 . 1 0 中

Ap p l i c a t i o n o f He t e r O g e n e Ou S Sy s t e m I n t e g r a t i o n i n I n t e l l i g en t Tr a n s p or t a t i o n I n t e g r a t e d I n f o r ma t i o n PI a t f Or m

★基 金 项 目: 广 东省 科 技 厅 产 学研 项 目( No _ 2 0 1 2 B 0 9 1 1 0 0 3 4 9 ) 、 广 东省 经 信 委 项 目( No . G DE I D2 0 1 0 I s 0 3 4 ) 、 广 州市 越 秀 区科 技 项 目 ( No . 2 0 1 2 一 G X一 0 0 4 )

32阶FIR滤波器的FPGA实现_范晓东

32阶FIR 滤波器的FPGA 实现范晓东1,蔡德林2,桂 岳1,梁本仁1(1.安徽大学电子科学与技术学院 安徽合肥 230039;2.中国电子科技集团公司第38研究所 安徽合肥 230031)摘 要:阐述了有限冲击响应(FIR )低通滤波器的窗函数设计方法,利用并行分布式算法在现场可编程门阵列上实现了32阶FIR 低通滤波器。

采用Altera 公司中Stratix 系列芯片内部的ROM 实现了一种基于查找表结构的FIR 数字滤波器,从而将卷积运算变换成一种查表后的加法运算,提高了运算速度,节省了逻辑单元。

仿真结果表面,基于并行分布式算法的FIR 滤波器最大处理速度可以达到200M Hz 。

关键词:FIR 滤波器;FP GA ;并行分布式算法;Matlab ;Quartus Ⅱ中图分类号:TN713 文献标识码:A 文章编号:10042373X (2009)212186203Implement of 32Orders FIR Filter on FPG AFAN Xiaodong 1,CAI Delin 2,GU I Yue 1,L IAN G Benren 1(1.Electronic Science and Technology Institute ,Anhui University ,Hefei ,230039,China ;2.No.38Institute ,China Electronics Technology Group Corporation ,Hefei ,230031,China )Abstract :Windows function design method of FIR digital filter is introduced ,and the parallel distributed arithmetic is used to implement a 32orders FIR digital ing the Altera ′s Stratix series FP GA to design a new structure of ing the ROM in FP GA ,this design can convert convolution to summation.Thus ,a high process speed is improved and the Logic Ele 2ments (L E )is saved.The result of simulation shows that the max speed of FIR filter can arrive at 200M Hz based on parallel distributed arithmetic.K eywords :FIR filter ;FP GA ;parallel distributed arithmetic ;Matlab ;Quartus Ⅱ收稿日期:2009204222 随着软件无线电的发展,对于滤波器的处理速度要求越来越高。

基于FPGA的高效FIR滤波器设计与实现

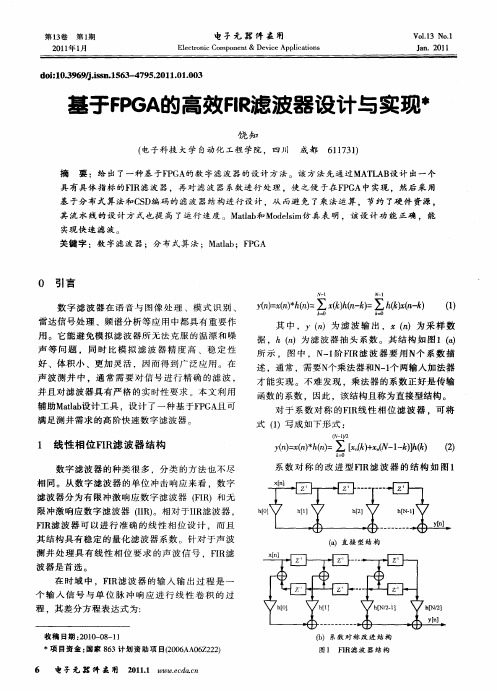

( a )直 接 型 结 构

程 ,其 差分方 程表 达式 为:

收 稿 日期 :0 0 0 — 1 2 1 — 8 1

()系数 对 称 改进 结构 b

图 1 FR滤 渡 器 结 构 I

项 目资 金 : 国家 8 3计 划 资助 项 目(0 6 A 6 22 6 20 A 0 Z 2 )

F A o l Ma a 信 号 处 理 工 具 箱 里 专 用 的 D T o是 tb l 滤 波器 设计 分 析工 具 ,该 工具 的 主要 作 用是 按 照 设 计 指 标 提 取 滤 波器 系数 。用F A 0l 计 数 字 D T o设 滤 波器 的关 键 在 于滤波 器 类 型 、窗 函数 、滤 波 器 阶 数 、截止 频 率等参 数 的选 择 。其 中窗 函数 用 于

占用 大量 资 源 的乘 法单 元 。分 布 式 算法 ( A D )的 提 出可 将乘 法 运算 转换 为 移位 相加 运 算 ,从 而节

滤波 器分 为有 限冲激 响应 数字 滤波 器 fI 1和 无 FR

y =( (=2 [(+ V1. } ( ( ) n 2 一一)( 2 n ) ) i J } ) 】 )

k - - 0

系 数 对 称 的 改 进 型 FR滤 波 器 的结 构 如 图 1 I

限 冲激 响应数 字滤 波器 fR 。相对 于I I ) I I R滤波器 ,

具有 具体指 标 的FR滤 波器 ,再对 滤波 器 系数进 行 处理 ,使之 便 于在 F G I P A中实现 。然后 采 用 基 于分布式算 法和C D编码 的滤波 器结构进 行设 计 ,从 而避免 了乘 法运算 ,节约 了硬件 资源 。 S

其 流 水 线 的 设 计 方 式 也 提 高 了运 行 速 度 。 Ma a 和 Moes tb l d l m仿 真 表 明 ,该 设 计 功 能 正 确 , 能 i

基于FPGA的线性相移FIR滤波器的实现

目 标等空间分布和运行 状况信息 . 进行动态监测 . 分析风险隐患 , 对可 能发生的突发公共事件进行预测预警 。 453 突发公 共事件发生后 . .- 通过汇总分析相关地区和部门的预测结 果, 结合事件进展情况 , 对事件影响 范围 、 影响方式 、 持续 时间和危害 程度等后果进行综合研 判 4 . 根据有关应 急预案 . .4 5 利用对 突发公共事件的研判结果 . 通过应 急平 台对有关法律法 规 、 政策 、 安全 技术 要求以及处理类似事 件的案 例等进行智能检索 和分析 , 并咨 询专 家意见 , 提供应对 突发 公共事件 的指导流程和辅助决策方案 455 记录事件 的应 对过程 . .. 根据有 关评价指标 . 对应 急过程 和能力 进行综合评估 。 同时 . 可在应急平 台上进行应急处 置模拟推演 . 提高相 关人员突发事件处置的能力和效率 。 在应急管理模块 与调度指挥模块联合部署的情况下 . 急管理模 应

[] 4蒋小 燕捌、 晓薇, 阳, 基于 F G 胡恒 等. P A的 FR数 字滤波器 的设计 与实现 . I 常卅I 院学报. 1 . ( : — 6 工学 2 1 4 )3 1. 0 221 [] 5李书华憎 以成 . 基于分布式算法 的高阶 FR滤波 器及其 F G I P A实现Il 计算 J l 机工程与应用, 1. ( ) 3 — 3 . 2 0 61 : 6 19 0 4 21 [] 6 田耘, 文波 .i x P A开发使用教程f ] 徐 Xl G i F n M. 北京: 清华大学 出版社, 0 , . 2 81 0 1

科技信 息

S IN E&T C N L GY F MA I N CE C E H O O 0R T O

21 年 01

第3 5期

fir数字滤波器的设计与实现

FIR数字滤波器的设计与实现介绍在数字信号处理中,滤波器是一种常用的工具,用于改变信号的频率响应。

FIR (Finite Impulse Response)数字滤波器是一种非递归的滤波器,具有线性相位响应和有限脉冲响应。

本文将探讨FIR数字滤波器的设计与实现,包括滤波器的原理、设计方法和实际应用。

原理FIR数字滤波器通过对输入信号的加权平均来实现滤波效果。

其原理可以简单描述为以下步骤: 1. 输入信号经过一个延迟线组成的信号延迟器。

2. 延迟后的信号与一组权重系数进行相乘。

3. 将相乘的结果进行加和得到输出信号。

FIR滤波器的特点是通过改变权重系数来改变滤波器的频率响应。

不同的权重系数可以实现低通滤波、高通滤波、带通滤波等不同的滤波效果。

设计方法FIR滤波器的设计主要有以下几种方法:窗函数法窗函数法是一种常用简单而直观的设计方法。

该方法通过选择一个窗函数,并将其与理想滤波器的频率响应进行卷积,得到FIR滤波器的频率响应。

常用的窗函数包括矩形窗、汉宁窗、哈密顿窗等。

不同的窗函数具有不同的特性,在设计滤波器时需要根据要求来选择合适的窗函数。

频率抽样法频率抽样法是一种基于频率抽样定理的设计方法。

该方法首先将所需的频率响应通过插值得到一个连续的函数,然后对该函数进行逆傅里叶变换,得到离散的权重系数。

频率抽样法的优点是可以设计出具有较小幅频纹波的滤波器,但需要进行频率上和频率下的补偿处理。

最优化方法最优化方法是一种基于优化理论的设计方法。

该方法通过优化某个性能指标来得到最优的滤波器权重系数。

常用的最优化方法包括Least Mean Square(LMS)法、Least Square(LS)法、Parks-McClellan法等。

这些方法可以根据设计要求,如通带波纹、阻带衰减等来得到最优的滤波器设计。

实现与应用FIR数字滤波器的实现可以通过硬件和软件两种方式。

硬件实现在硬件实现中,可以利用专门的FPGA(Field-Programmable Gate Array)等数字集成电路来实现FIR滤波器。

基于FPGA设计的FIR滤波器的实现与对比

从 FR 公 式 出发 , 以得 道 m 滤 波 器 的 输 出 是 输 人 数 I 可

据 和 系 数相 卷 积 得 到 的 , 公 式 ( ) 示 。 如 1所

L I 波器 分 为两类 : R和 F R滤波器 。 数据 通讯 , T滤 I I I 在 语音 信 号处 理 , 图像 处理 , 达信 号处 理 中 , 能有 明显 的相位 失 真 , 雷 不 而 有 限长 单 位 冲 激 相 应 F R具 有 严 格 的 线 性 相 位 的特 点 : I 此 外 ,I F R滤 波器 的单 位抽 样 响 应 序 列是 有 限 长 的 .因此 是 一 个

法) 。在 文 中是 以 一 3 2阶 F R滤 波 器 进 行 比较 的 。 I

^L l

∑s) Ⅳ ∑ ( s ) o ( - = ) ) ( ( + ( ) (= 0 )

i0 - i0 -

s 1 x 1 ( ) h( +…+ ( 1  ̄ N-1 ( ) h( ) 2 x 2) 5 ) h( )

稳 定 的系 统 , FR 滤 波 器 在 上 述 领 域 中 得 到 广 泛 应用 [。 故 I ห้องสมุดไป่ตู้ 1

ysn () 2 si hN i =() n= ( x ( -) )

() 1

具 有 严 格 线 性 相 位 FR滤 波 器 具有 对 称 的性 质 .即 满 足 I

偶 对称 性 或 奇 对 称 , 在这 里 介 绍 下 偶 对 称 的 结构 , 满 足 公 式 即

Re lz to nd c m pa io ft e FI ft r b s d o FPGA aiai n a o rs n o h R le a e n

CUILin a g,ZHANG — in Zhixa

FIR数字滤波器的FPGA设计与实现

数 字滤波器是语 音与 图像处理 、模式识别 、雷达信 号处 理 、频谱分析等应 用中的一种 基本的处理部件 ,它 能满足滤

([]口 [] [x一l+ cOx一0 +c ]口 【 …+ [ l 1 I】 cN一1 1 】 [ 一 Ⅳ一1 2- ] a )

+([] 2 】 [ x 一[ +…+cN 一1 口2N 一1 2 cOx一【 +c1 s21 0 ] ] [ ] 一I x ] )

上 面 对 分 布 式 算 法 做 了 个 概 述 ,但 就 实 现 方 式 来 说 ,分 布 式 算 法 又 分 为 串行 方 式 和 并 行 方 式 。 串行 方 式 规 模 小 但 速

法 实现 。若使用传统的乘累加结构来设计 F R数字滤波器 , I 那么就需要进行 L 1次加 法和 L次乘法 ,硬件 的规模较大 , - 速度也较慢 ,不适用于高速 的处理和运算 。因此,本设计采 用 了速度和 规模 都较理想 的分布式算法 。下面 就对分布式算 法作个概述 。 个线性时不变 网络 的输 出可 以用下式表示 :

20 0 8年第 1 O期 ( 总第 1 0期 ) 1

大 众 科 技

DA ZHo NG l KEJ

No 1 . 0。2 0 0 8

( u lt eyN .1 ) C muai l o1 v 0

F I R数字滤波器 的 F G P A设计 与实现

项 正 山 ,胡 蓉花

( 桂林 长海发展 有限责任 公 司 ,广西 桂林 5 10 ) 40 1

【 摘 要 】提 出了一种基 于现场可编程 门阵列器件 F G P A并利 用窗函数 法 实现一个 1 6阶线性 FR 数 字滤波器的设计方 法。 I.

基于FPGA的MAC FIR滤波器的实现

f as psl f as ps2 ftp s 2 o 在通带两侧 的衰减

3ok z 0 H 4Ok z 5 H 4ok z 8 H 5 B 4d

通带纹波

1

全并行滤波器相 比, A M C结构采用单一乘法器和累加

利用 M tb的信号处理工具箱 (i a p csn aa l s nl r e i g o sg

滤波器 的特性 ( : 滤波器 、 如 低通 带通滤 波器 、 通滤波 高 器) 。该 公式可 以采用 不 同架构 、 利用 不同方法 ( , 如 串

因此 , R滤波器在通信、 F I 图像处理 、 模式识别等领域

都 有着广泛 的应 用 … 。 利用 F G Fe r r al G t Ary 现 场 P A( il P ga be a r , d o mm e a

胡 少轩

( 山西国新能源发展集团有 限公 司, 山西 太原 000 ) 30 6

摘 要

F I R滤波器在通信、 图像处理、 模式识别等领域都有着广泛的应用。本文设计 了基于乘 累

加器( u iyA cm li , A ) M lp cu u tnM C 的有限冲激响应滤波器( i t Ipl e os F t ) 介绍 了其优 tl ao F i u eR s ne i r , nem s p l e

点及详 细的设 计方 法, 给 出 了基 于 F G 的 实现 流程 , 并 PA 最后 进行 了基 于 JA T G的硬 件协 同仿 真验 证 。 仿真与 实验 结果验证 了所提 出 MA I CFR的正确性 与有效性 。

关键 词 FR; A F G 数字信号 处理 I M C;P A;

行、 半并行或并行) 来实现。在采样速度慢、 系数多时,

基于FPGA的FIR低通滤波器的设计与实现

Ab s t r a c t Th e t h e o r y a n d me t h o d t o r e a l i z e FI R l o w- p a s s f i l t e r u s i n g Di s t r i b u t e d Ar i t h mt e t i c b a s e d o n FPGA i s p r e s e nt e d .Th e d e s i gn

要使 用到滤波器 。F I R滤波器 是数字信 号处理 中常用 的一

种 方法 , 它具 有 稳 定 、 能保 证 精 确 的 线性 相 位 的特 性 _ 1 ] 。 F P GA具有灵活 的可编 程特 性 , 突破 了并行 处理 与 流水 级 数 的限制 , 可 以很好地 实现信号处理 的及 时性 , 且它 的开发 程序 可移植 性好 , 开发周 期短 。而采用 F P G A 技术 来设 计 F I R滤波 器正 成为设 计 的趋 势l _ 2 J 。目前 , 用F P GA设 计

丁

( 江苏 科 技 大 学

伟

张 家港 2 1 5 6 0 0 )

摘 要

论文主要研究基 于 F P GA技术 、 采用分布式算法实现 F I R低通滤波器的原理和方法。该设计利用 Ma t l a b工具箱设计 窗函数

计算 F I R滤波器系数 , 并用 Q u a r t u s 1 I 进 行硬件仿真 , 仿真结果表明设计 F I R滤波器的正确性 。最后 以 1 6阶的 F I R低通滤波器 为例 , 给出

s h o ws t h e d e s i g n e d FI R f i l t e r i s c o r r e c t . A 1 6 一 o r d e r FI R 1 O W f i l t e r i s d e s i g n e d a s a n e x a mp l e ,s ho wi n g t h e s i mu l a t e d wa v e s ,h a r d wa r e ve r i i— f

FPGA实现FIR抽取滤波器的设计

FPGA实现FIR抽取滤波器的设计之蔡仲巾千创作FIR(fini te impulse response)滤波器是数字信号处理系统中最基本的元件,它可以在包管任意幅频特性的同时具有严格的线性相频特性,同时其单位冲激响应是有限的,没有输入到输出的反馈,系统稳定。

因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。

在工程实践中,往往要求对信号处理要有实时性和灵活性,而已有的一些软件和硬件实现方式则难以同时达到这两方面的要求。

随着可编程逻辑器件的发展,使用FPGA来实现FIR滤波器,既具有实时性,又兼顾了一定的灵活性,越来越多的电子工程师采取FPGA器件来实现FIR滤波器。

1 FIR滤波器工作原理在进入FIR滤波器前,首先要将信号通过A/D器件进行模数转换,使之成为8bit的数字信号,一般可用速度较高的逐次逼进式A/D转换器,不管采取乘累加方法还是分布式算法设计FIR 滤波器,滤波器输出的数据都是一串序列,要使它能直观地反应出来,还需经过数模转换,因此由FPGA构成的FIR滤波器的输出须外接D/A模块。

FPGA有着规整的内部逻辑阵列和丰富的连线资源,特别适合于数字信号处理任务,相对于串行运算为主导的通用DSP芯片来说,其并行性和可扩展性更好,利用FPGA乘累加的快速算法,可以设计出高速的FIR数字滤波器。

2 16阶滤波器结构在滤波过程中实现抽取,对于抽取率为N的抽取滤波器而言,当进来N个数据时滤波器完成1次滤波运算,输出1次滤波结果。

抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。

在数字系统中采取拙取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。

采样数据与滤波器系数在控制电路的作用下,分别对应相乘并与前一个乘积累加,经过多次(有多少阶就要多少次)反复的乘累加最后输出滤波结果,将相同系数归类,16阶滤波器公式:乘法器的数量减少一半,但加法器的数量增多了,但相对乘法运算来说,加法运算所占用的资源少的多,运算的速度也快得多。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

y(行)=≥:x(n—i)^(i)

(1)

=蜀

式中:z(咒)是输入采样序列;^(,z)是滤波器系数;L是

滤波器阶数;3,(咒)表示滤波器输出序列,为z(以)和

h(竹)的卷积。FIR滤波器基本结构如图1所示。

图1 FIR滤波器基本结构

对于一个4阶滤波器子系统其输出可表示为: y(行)=^(O)z(咒)+h(1)z(,z一1)+ h(2)z(咒一2)+h(3)z(以一3) (2)

中图分类号:TN713+.7

文献标识码:A

文章编号:1004—373X(2009)18—028一03

Design and Implementation of Bandpass Filter SHI Xinghua。WU Guangmin

(Faculty of Science,Kunming University of Science and Technology,Kunming,650093,China)

2

Simulink的模型仿真

在Simulink环境下设计仿真时间等参数,运行仿 真得到滤波输出的幅频相应图和时域图如图2,图3 所示。

图2中纵横坐标分别代表了幅值和频率值显示,

万方数据

Magnitude,Frequency单位分别是dB(幅值单位也称 衰减倍数)和MHz(横坐标每格单位相比kHz被放大 104便于观察)。纵横轴每格量为5 dB和50 MHz。从 该频谱图中可看出,滤波后通带内幅频曲线相对平缓, 带外衰减较大,由滤波前的连续幅频变成了选择通过的 单一幅频曲线,起到了过滤带外频谱的作用。

正弦信号进行滤波,结果下裁到开发板上用示波器观测,达到了预期的滤波效果和目的。基于DSPBuilder完成系统建模,省

去了复杂的VHDL编程,还可针对具体模块进行参数设置从而适应不同的滤波需求。该方法实现简单、可靠,还可类推实现 其他复杂的嵌入式系统设计。

关键词:FIR(有限冲击相应);数字带通滤波器;FPGA;DSPBulider

参考文献

[13任爱峰,初秀琴。常存,等.基于FPGA的嵌入式系统设计 [M].西安:西安电子科技大学出版社,2004.

[23潘松,黄继业,曾毓.SoPC技术使用教程[M].北京:清华大 学出版社,2004.

[3]飞思科技产品研发中心.Matlab 7辅助信号处理技术与应 用[M].北京:电子工业出版社,2005.

蟹重圜臣曩葺圜

互基坐量;兰!垦壹通透邃量鱼里里鱼垒塞婴

FIR带通滤波器的FPGA实现

石兴华,吴光敏

(昆明理工大学理学院 设计一个项目可用的FIR数字带通滤波器,采用Matlab/Simulink软件中DSPBulider强大的算法模块设计工 具,结合Altera公司的FPGA开发板实现FIR数字带通滤波器的系统集成、RTL级仿真、综合编译,下裁等设计流程,并对

Simulink中仅实现了算法级的仿真,而ModelSim 需要对生成的VHDL代码进行功能仿真即RTL级仿 真。如图4的波形。

图4 ModelSim仿真图(模拟显示格式) 29

图4定性表述了6个信号波形。clock为时钟周 期,第二个信号是全局复位。重点观察第三、六个信号。 分别是输入信号(加了数/模转换的)的模拟显示和经滤 波后输出信号的模拟显示。这和Simulink中仿真结果 是一致的。第四个信号是滤波后(加数/模转换)的信 号,第五个是最后一个4阶滤波子系统的输出。同样可 设置ModelSim对应的数字显示,每个时钟周期对应的 数值即为每个时钟周期对正弦信号的一个采样点计算 一次的值。

收稿日期:2009—01—16 基金项目:云南省社会发展应用基金面资助项目

(2007F028M) 28

万方数据

最为常用的模块之一,在此基于上述基础,设计实现了 基于模块的FIR数字带通滤波器。

1基于DSP Builder的滤波系统设计

1.1 FIR滤波器原理

有限冲激响应(Finite Impulse Response,FIR)滤

Abstract:In order tO design an available FIR digital bandpass filter,applying powerful algorithm module design tool of Matlab/Simulink/DSPBulider.Making use of FPGA Development Board of Ahera tO accomplish design flow of FIR digital fil— ter,such as system integration,simulation of RTI。,synthesis and compilation etc.Then,sinwaves are used to filter and results downloaded tO the development board using oscilloscope observation.Results prove to be effective and expected.Not only using DSPBuilder tO appcomlish system modeling and eliminate complex VHDL programming,but also amending parameters of mod— el SO as to be adapted tO different demands of filter.This method is easy and reliable in implementing,can also achieve other complex embedded system design.

r 103 Altera.Altera DSP Builder for DSP 6.1 User Guide.pdf [EB/OI。].http://www.altera.corn,August 2004/Novem—

波器是由有限个采样值组成,实现的方式是非递归、稳 定的,在满足幅频响应要求的同时,可以获得严格的线

性相位特性,因此在高保真的信号处理等领域得到广泛

应用。

对于一个FIR滤波器系统,它的冲击相应总是有

N--I

限长的,其系统函数可记为:H(z)=≥:h(n)z-‘,最基

●=0

本的FIR滤波器可表示为:

L—l

[4]郑亚民,董晓舟.可编程逻辑器件开发软件Quartus II[M]. 北京:国防工业出版社,2006.

[5]杨守良.Matlab/Simulink在FPGA设计中的应用[J].微计 算机信息,2005,21(1 6):98—99.

[6]程佩青.数字信号处理教程[M].北京:清华大学出版 社,2001.

4在Quartus I中实现时序仿真

ModelSim中也仅实现RTL级仿真,并不能精确 反应电路的全部硬件特性。Ahera提供自动和手动两 种综合适配流程,在此选用自动流程在Quartus 11中进 行硬件设计。设定990 ns仿真结果如图5所示与图3 ModelSim的数字显示对应信号和结果均是一致的,只 是QuartusII的时序仿真[41更为精确。

验证了该滤波器达到预期设计要求。

6结语

这里介绍在Altera DSPBuilder环境下基于模型化 设计FIR数字带通滤波器的方法,通过模块化的方法 实现了向VHDL硬件描述语言代码的自动转换、RTL 级功能仿真、综合编译适配和布局布线、时序实时仿真 直至对目标器件的编程配置和硬件实现。验证了滤波 器满足预期设计要求。创新点在于便捷地设计模块或 修改基本参数,完成其他DSP系统设计。综上采用 DSP Builder作FPGA设计,可以更快速、可靠、有效地 实现系统功能。体现了FPGA技术的便捷和发展。

图5 Quartus II时序仿真图

5 FPGA硬件实现

系统仿真通过后,需转到硬件上加以实现,这是整 个DSP Builder设计中最为关键的一步。QuartusⅡ仿 真中生成了.sol编程文件,用于FPGA编程配置,完成 了对开发板StratixⅡEP2S180特定芯片的编译和管 脚的分配。将.sof文件下载到开发板中,编程模式为 USB Blaster相应模式为JTAG,用示波器检测D/A输 出,可观察到实测的输入/输出波形与仿真结果均对应 一致。至此完成了该滤波器完整的FPGA开发设计,并

根据FIR滤波器原理和4阶子系统的输出公式, 在Matlab的Simulink环境下,调用AlteraDSP Builder 库中的4个Delay延迟模块、4个Product乘法模块、 5个9位的Input输入端口、1个20位的Output输出端 口和一个4输入的加法器,使9位的输入序列z(砚)和 FIR滤波器的系数^(o),^(1),^(2)。^(3)作为输入,完 成4阶滤波器子系统。调用4个这样的子系统级联起来 构成16阶的滤波器。其中,滤波器系数,l(o),h(1),…, ^(15)由滤波器设计工具FDATools生成,系数与滤波 器关联,建立出完整的滤波系统模型[2]。

[7]杨春玲,张辉.现代可编程逻辑器件及SoPC应用设计[M]. 哈尔滨:哈尔滨工业大学出版社,2005.

[8]齐鹏飞,刘雄飞,张德恒.基于FPGA的数字滤波器的设计 与实现[J].现代电子技术,2006,29(15):70—71.

[9]赖联友,吴伟力,许伟坚.基于FPGA的FIR滤波器设计 [J].集美大学学报,2006,11(4):348—350.

图2 滤波器的幅频曲线图

图3滤泼前后的时域波形

该图坐标轴的纵横轴分别代表了幅度值和时间轴。 单位分别为十进制数和S。图3(a)是两正弦信号经平 行加法器合成的波形图3(b)滤波后的波形。可见高频 信号衰减很大起到了过滤带外时间离散信号的作用。 综上该带通滤波器在频域和时域都实现了相应的滤波 功能,至此完成了模型仿真。 3在ModelSim中实现RTL级仿真