Synopsys 综合工具Design Compiler(DC)

Design Compiler和Encounter

VLSI EDA实验报告本课程学习了ASIC设计流程中的相关知识,我们组下载了存储器控制器设计代码,应DC和Encounter对其进行了综合及物理设计,以下为本次实践报告。

一、有关综合综合包括转译(Translation),优化(Opitimization),映射(Mapping)三个过程⏹转译是把电路的HDL描述转化为与工艺无关的功能块组成的逻辑电路。

⏹映射是把转译后得到的电路结构用特定目标工艺库中的单元来实现。

这时得到的电路包含了具体的制造工艺参数。

⏹优化则是综合工具根据设计者施加的时序和面积等约束条件对电路进行改进的过程综合流程如下图:二、DC的介绍:SynopsysDesign Compiler,是一个基于UNIX系统,通过命令行进行交互的综合工具,除了综合之外,它还含有一个静态时序分析引擎及FPGA和LTL(links-to-layout)的解决方案。

它的主要功能包括:⏹使用用户指定的门阵列或标准单元库产生速度快、面积小的ASIC设计。

⏹把设计从一种工艺转换为另一种工艺。

⏹在不同的负载温度和电压条件下对时序面积和功耗设计指标作折中处理。

⏹综合和优化有限状态机(FSM) 。

⏹支持网表输入,支持用来与第三方工具交互的网表或原理图输出。

⏹自动创建和划分层次化原理图。

三、存储器控制器的综合1.综合的输入文件TRL 代码:(.v / .hdl)top文件中包含各个子模块的调用。

库文件:(.lib / .db)综合脚本:(.tcl)脚本中包含环境建立、约束条件。

2. 添加I/O在芯片的版图中,信号的引脚需要有相应的焊盘(pad),才能进行封装和生产。

标准单元库都提供了I/O单元,我们选择hjtc18_ff中的I/O单元PLBI16N,其结构如下图所示:PLBI16N原理图在为IO加pad时,就是将pad用线网wire连接到设计的顶层模块的IO接口,通过元件例化设置I/O单元PLBI16N的引脚就可以设置端口的输入和输出,下面是引用的过程:PLBI16N PIN_I_CLK (.D(i_clk),.P(I_CLK), //pad设置为I_CLK.A(1'b0), //数据输入为0.CONOF(1'b1), // CMOS输入使能有效.NEN(1'b0), //低电压输出使能.PD(1'b0), //拉低.PEN(1'b0), //高电压输出使能为低.PU(1'b1), //拉高.SONOF(1'b0) //CMOS施密特使能); // Input Buffer with CMOS Input3. 面积约束我们希望电路的面积越小越好,所以在面积约束时设置最大面积为0,这只是理想值。

synopsys DC

What beh2str leaves out...

Timing!

No clock defined so no target speed No input drive defined so assume infinite drive No output load define so assume something

Type commands to the design compiler shell

Start with syn-dc and start typing

2.

Write a script

Use syn-script.tcl as a starting point

2. Read in your structural Verilog

Usually split into analyze and elaborate

3.

Use the Design Vision GUI

Friendly menus and graphics...

3. Set constraints

timing – define clock, loads, etc.

Design Compiler – Basic Flow

syn-script.tcl

#/* the following control which output files you want. They */ #/* should be set to 1 if you want the file, 0 if not */ set write_v 1 ;# compiled structural Verilog file set write_db 0 ;# compiled file in db format (obsolete) set write_ddc 0 ;# compiled file in ddc format (XG-mode) set write_sdf 0 ;# sdf file for back-annotated timing sim set write_sdc 1 ;# sdc constraint file for place and route set write_rep 1 ;# report file from compilation set write_pow 0 ;# report file for power estimate

synopsys DC10.03图文安装配置详解

喾林原创Synopsys DC10.03安装配置1、需准备安装包:1)、Synopsys DC(design compiler)安装包2)、SCL 安装包(注:此包为synopsys license 管理)。

3)、Synopsys 图像安装工具:installer2.0及以上均可。

(注:图形安装操作简单,不易出错,故采用图形安装界面)4)、Synopsys license 制作工具( EFA LicGen 0.4b 和Synopsys SSS Feature Keygen )。

2、开始安装DC : 1)、启动图形安装界面于linux 系统下解压installer2.0包(在windows 下解压文件易损坏)。

解压后运行setup.sh 得如图(一)所示界面。

图 (一)喾林原创点击“start ”有如图(二)所示界面开始安装。

在“Source ”栏选中DC 安装文件所在上层目录。

“Done ”后“Next ”(此次“Next ”时间较长,耐心等待)。

图 (二) 之后可一直“NEXT ”到如图(三)所示。

图 (三)在该界面勾选linux选项即可,继续下一步到如图(四)所示。

选择安装路径后继续下一步直到结束。

喾林原创图(四)至此DC安装结束。

3、开始安装SCL:此安装与DC安装步骤一直,几乎没有差别,唯一不同的就是安装路径不同。

4、license的制作:License的制作是在windows下制作的。

1)、打开EFA LicGen 0.4b文件夹运行LicGen.exe程序出现如图(五)所示界面。

喾林原创图(五)点击“OPEN”选择Synopsys.lpd文件,“打开”。

回到图(五)所示界面。

勾选上Custon、Use Daemon及最后一个Custon。

喾林原创在两个“Custon ”后输入Linux 系统的MAC 。

注:Linux MAC 获取命令。

A :lmhostid 下图(六)红线处即为 MAC 。

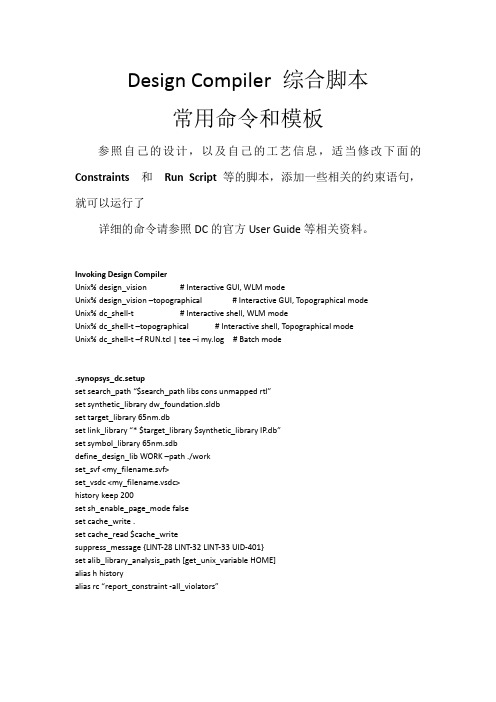

DC Design Compiler 综合脚本命令及参考模板

Design Compiler 综合脚本常用命令和模板参照自己的设计,以及自己的工艺信息,适当修改下面的Constraints和Run Script 等的脚本,添加一些相关的约束语句,就可以运行了详细的命令请参照DC的官方User Guide等相关资料。

Invoking Design CompilerUnix% design_vision # Interactive GUI, WLM modeUnix% design_vision –topographical # Interactive GUI, Topographical modeUnix% dc_shell-t # Interactive shell, WLM modeUnix% dc_shell-t –topographical # Interactive shell, Topographical modeUnix% dc_shell-t –f RUN.tcl | tee –i my.log # Batch mode.synopsys_dc.setupset search_pa th “$search_path libs cons unmapped rtl”set synthetic_library dw_foundation.sldbset target_library 65nm.dbset link_library “* $target_library $synthetic_library IP.db”set symbol_library 65nm.sdbdefine_design_lib WORK –path ./workset_svf <my_filename.svf>set_vsdc <my_filename.vsdc>history keep 200set sh_enable_page_mode falseset cache_write .set cache_read $cache_writesuppress_message {LINT-28 LINT-32 LINT-33 UID-401}set alib_library_analysis_path [get_unix_variable HOME]alias h historyalias rc “report_constraint -all_violators”TCL Commands and Constructsset PER 2.0 # Define a variable and its valueecho $PER # Variable substitution → 2.0set MARG 0.95expr $PER * $MARG # expr: *, /, +, -, >, <, =, <=, >=set pci_ports [get_ports A] # Imbedded commandset pci_ports [get_ports “Y??M Z*”]# Wildcardsecho “Effctv P = \ # Soft quotes → 1.9[expr $PERIOD * $MARGIN]”echo {Effctv P = \ # Hard quotes[expr $PERIOD * $MARGIN]} # → Effctv P = [expr $PER * $MARG] # Comment lineset COMMENT in_line; # In-line commentset MY_DESIGNS {B1.v ... B26.v} # foreach loopforeach DESIGN $MY_DESIGNS {read_verilog $DESIGN}for {set i 1} {$i < 27} {incr i} { # for loopread_verilog BLOCK_$i.v}Helpful UNIX-like DC-shell commandspwdcdlshistory!!!7!reportsh <UNIX_command>printenvget_unix_variable ARCHConstraintsreset_designset_max_area 0create_clock -period 2 –name Main_Clk [get_ports Clk1]create_clock –period 2.5 –waveform {2 3.5} [get_ports Clk2]create_clock –period 3.5 –name V_Clk; # VIRTUAL clockset_clock_uncertainty –setup 0.14 [get_clocks *]set_clock_uncertainty –setup 0.21 –from [get_clocks Main_Clk] –to [get_clocks Clk2]set_clock_latency –max 0.6 [get_clocks Main_Clk]set_clock_latency –source –max 0.3 [get_clocks Main_Clk]set_clock_transition 0.08 [get_clocks Main_Clk]set_input_delay -max 0.6 -clock Main_Clk [all_inputs]set_input_delay –max 0.3 –clock Clk2 –clock_fall –add_delay [get_ports “B E”]set_input_delay -max 0.5 -clock –network_latency_included V_Clk [get_ports “A C F”]set_output_delay -max 0.8 -clock –source_latency_included Main_Clk [all_outputs]set_output_delay -max 1.1 -clock V_Clk [get_ports “OUT2 OUT7]set_max_capacitance 1.2 [all_inputs]set_load 0.080 [all_outputs]set_load [expr [load_of slow_proc/NAND2_3/A] * 4] [get_ports OUT3]set_load 0.12 [all_inputs]set_input_transition 0.12 [remove_from_collection [all_inputs][get_ports B]]set_driving_cell –lib_cell FD1 –pin Q [get_ports B]set_operating_conditions –max WCCOMset auto_wire_load_selection falseset_wire_load_model –name 1.6MGatesset_wire_load_mode enclosedset_wire_load_model –name 200KGates [get_designs “SUB1 SUB2”]set_wire_load_model –name 3.2MGates [get_ports IN_A]set_port_fanout_number 8 [get_ports IN_A]set_false_path -from [get_clocks Asynch_CLKA] -to [get_clocks Asynch_CLKB]set_multicycle_path –setup 4 –from –from A_reg -through U_Mult/Out –to B_regset_multicycle_path –hold 3 –from –from A_reg -through U_Mult/Out –to B_regset_isolate_ports –type inverter [all_outputs]set_ideal_network [get_ports reset* select*]set_ideal_network [get_pins FF_SET_reg/Q]set_ideal_network –no_propagate [get_nets CTRL]set_ideal_latency 1.4 [get_ports reset* select*]set_ideal_transition 0.5 [get_pins FF_SET_reg/Q]set_scan_configuration -style <multiplexed_flip_flop | clocked_scan | lssd | aux_clock_lssd>Checking and Removing Constraints and Directivesreport_clock; report_clock -skewreport_designreport_port –verbosereport_wire_loadreport_path_groupsreport_timing_requirements (–ignored)report_auto_ungroupreport_isolate_portswrite_script –output <constraints.tcl>check_timingreset_path –from FF1_regremove_clockremove_clock_transitionremove_clock_uncertaintyremove_input_delayremove_output_delayremove_driving_cellremove_wire_load_modelSyntax CheckingUnix% dcprocheck constr_file.conPhysical Constraints – Topographical Modeset_aspect_ratioset_utilizationset_placement_areaset_rectilinear_outlineset_port_sideset_port_locationset_cell_locationcreate_placement_keepoutMisc. Reports# Generate A library report fileread_db library_file.dblist_libsredirect –file reports/lib.rpt {report_lib <libname>} report_hierarchy [-noleaf]# Arithmetic implementation and# resource-sharing inforeport_resources# List area for all cells in the designreport_cell [get_cells –hier *]Run Scriptread_verilog {A.v B.v TOP.v} orread_vhdl {A.vhd B.vhd TOP.vhd} orread_ddc MY_TOP.ddc oracs_read_hdl MY_TOP oranalyze –format verilog {A.v B.v TOP.v}elaborate MY_TOP –parameters “A_WIDTH=8, B_WIDTH=16”current_design MY_TOPlinkif {[check_design] ==0} {echo “Check Design Error”exit # Exits DC if a check-design error is encountered} # Continue if NO problems encounteredwrite –f ddc –hier –out unmappedd/TOP.ddcredirect –tee –file reports/precompile.rpt {source –echo -verbose TOP.con}redirect –append –tee –file reports/precompile.rpt {check_timing}source <Physical_Constraints_TCL_file> or # Source tcl constraints, if available, or extract_physical_constraints <DEF_file> # Extract and apply from an existing # DEF floorplan filegroup_path -name CLK1 -critical_range <10% of CLK1 Period> –weight 5group_path -name CLK2 -critical_range <10% of CLK2 Period> –weight 2group_path –name INPUTS –from [all_inputs]group_path –name OUTPUTS –to [all_outputs]group_path –name COMBO –from [all_inputs] –to [all_outputs]set_fix_multiple_port_nets –all –buffer_constants********************************************************** ** Insert Expert, Ultra or ACS compile flow here ** **********************************************************check_designreport_constraint –all_violatorsreport_timing –delay –to –from –through –input_pins –max_paths \–nworst –nets –cap –sig –groupreport_areareport_qorset verilogout_no_tri truechange_names –rule verilog –hierwrite –f verilog –hier –out mapped/TOP.vwrite –f ddc –hier –out mapped/TOP.ddcwrite_sdc TOP.sdcwrite_scan_def –out TOP_scan.defwrite_physical_constraints –output TOP_PhysConstr.tcl exitObject Retrieval and Manipulation (Collection Commands) get_ports, get_pins, get_designsget_cells, get_nets, get_clocksget_nets –of_objects [get_pins FF1_reg/Q]get_libs <lib_name>get_lib_cells <lib_name/cell_names>get_lib_pins <lib_name/cell_name/pin_names>all_inputs, all_outputs, all_clocks, all_registersall_connectedall_fanin, all_fanoutall_ideal_netsset pci_ports [get_ports pci_*]echo $pci_ports # → _sel184 query_objects $pci_ports # → {pci_1 pci_2 ...} get_object_name $pci_ports # → pci_1 pci_2 ... sizeof_collection $pci_ports # → 37set pci_ports [add_to_collection $pci_ports \[get_ports CTRL*]]set all_inputs_except_clk [remove_from_collection \ [all_inputs] [get_ports CLK]]compare_collectionsindex_collectionsort_collectionforeach_in_collection my_cells [get_cells -hier * \ -filter “is_hierarchical == true”] {echo “Instance [get_object_name $cell] is hierarchical”}# Filtering operators: ==, !=, >, <, >=, <=, =~, !~filter_collection [get_cells *] “ref_name =~ AN*”get_cells * -filter “dont_touch == true”get_clocks * -filter “period < 10”# List all cell attributes and redirect output to a fileredirect –file cell_attr \{list_attributes –application –class cell}# Grep the file for cell attributes starting with dont_UNIX% grep dont_ cell_attr | more# List the value of the attribute dont_touchget_attribute <cell_name> dont_touchUltra Compile Flow - Topographical or WLM ModeUltra + DesignWare and DFTC licenses available# In “topo” mode (dc_shell-t –topo) specify Milkyway reference and design libraries create_mw_lib –tech <technology_file> -mw_reference_library <mw_reference_libraries> \<mw_design_library_name>open_mw_lib <mw_design_library_name>set_tlu_plus_files -max_tluplus <max_tluplus_file> -tech2itf_map <mapping_file>set compile_auto_ungroup_delay_num_cells 99999999set compile_auto_ungroup_count_leaf_cells trueset compile_auto_ungroup_override_wlm trueset_ungroup <top_level_and/or_pipelined_blocks> false# OPTIONAL: Disable unconditional auto-ungrouping# of DesignWare hierarchy (not usually recommended)set compile_ultra_ungroup_dw false# If design contains pipelined sub-designs and the pipeline registers# are grouped together at the input or output, relax timingset_multicycle_path –setup <#_stages> -from U_Pipeline/R3_reg* –to U_Pipeline/R7_reg* # In “ topo” mode, if the floorplan is available, apply or extract the physical constraints source <physical_constraints_file> ORextract_physical_constraints <DEF_file># OPTIONAL: Exclude specific cells/design from adaptive retiming (-retime)set_dont_retime <cells_or_designs> true# First compilecompile_ultra –scan –retime –timing|-area# The design hierarchy may have changed due to auto-ungrouping/-uniquifyingreset_path -from U_Pipeline/R3_reg* -to U_Pipeline/R7_reg*# OPTIONAL: Maintain registered pipeline outputs if requiredset_dont_touch [get_cells U_Pipeline/R12_reg*] true# Optimize registers if pipeline violates timing; Skip if no pipeline issues:set_optimize_registers true –design My_Pipeline_Subdesignoptimize_registers –only_attributed_designs# Continue if design is NOT meeting all constraints:# Apply more focus on violating critical paths, as necessarygroup_path –name <group_name> -from <path_start> -to <path_end> \–critical range <10% of max delay goal> -weight 5# Select appropriate second compile# In “topo” mode in DC v2006.06, or any mode in DC v2007.03 or latercompile_ultra –scan –incremental# In “WLM” mode in DC v2006.06set_ultra_optimization truecompile –boundary –scan –map_effort high –incremental (-area_effort medium|low|none) # In “topo” mode prior to DC v2007.03: Write out updated physical constraintswrite_physical_constraints –output PhysConstr.tclDFT Flow – Expert or UltraDFTC license available# Prior to the first compile set the# scan cell styleset_scan_configuration –style ..# Perform the first test-ready compilecompile –boundary –map high –scan # ORcompile_ultra –timing -scan# Continue before the next compile:# Read in the scan specification filesource scan_spec.tcl# Check for DFT rule violationsdft_drc# Preview the scan chainspreview_dft# Insert and optimize scaninsert_dft******************************************************* * * Execute additional Ultra/Expert optimization ** techniques, as needed ** * ******************************************************# After the final compile check the DFT QoR# and write out the scan DEF filedft_drc –coverage_estimatewrite_scan_def -out <my_design.def>Some Scan Specification Commandsset_scan_state test_readyset_dft_configuration ...set_dft_signal ...set_scan_path ...set_scan_configuration ...create_test_protocolExpert Compile FlowNo Ultra license available; DFTC license availablecompile –boundary –scan –map_effort high# Continue if NOT meeting constraints# Note: -scan requires DFTC licensecompile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Continue if NOT meeting constraints:# Increase max-delay priority if OK to postpone DRC fixingset_cost_priority –delay# Note: The design hierarchy may have changed due to auto- # uniquifying# Apply more focus on violating critical paths, as necessary group_path –name <group_name> -from <path_start> \-to <path_end> –critical range <10% of max delay goal> -weight 5 # Repartition if design is poorly partitionedgroup –design <NEW_DESIGN> -cell_name <U_NEW_CELL> \{U2 U7 ...}ungroup –start_level 2 U_NEW_CELLcompile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Or, can ungroup all hierarchy in lieu of group/ungroup# commands with –ungroup_allcompile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none) –ungroup_all“Pseudo Ultra” Compile FlowUltra license available; No DesignWare license availableset compile_auto_ungroup_delay_num_cells 99999999set compile_auto_ungroup_area_num_cells 99999999set compile_auto_ungroup_count_leaf_cells trueset compile_auto_ungroup_override_wlm trueset_ungroup <top_level_and/or_pipelined_blocks> false# OPTIONAL: Disable unconditional auto-ungrouping# of DesignWare hierarchy (not usually recommended)set compile_ultra_ungroup_dw false# If design contains pipelined sub-designs and the pipeline registers# are grouped together at the input or output, relax timingset_multicycle_path –setup <#_stages> \-from U_Pipeline/R3_reg* –to U_Pipeline/R7_reg*# Enable Ultra optimizations available for compileset_ultra_optimization –no_auto_dwlib trueset hlo_disable_datapath_optimization trueset compile_slack_driven_buffering truecompile –boundary –scan –map_effort high –auto_ungroup delay|area \ (-area_effort medium|low|none)# Note: The design hierarchy may have changed due to auto-# ungrouping and auto-uniquifyingreset_path -from U_Pipeline/R3_reg* -to U_Pipeline/R7_reg*# OPTIONAL: Maintain registered pipeline outputs if requiredset_dont_touch [get_cells U_Pipeline/R12_reg*] true# Optimize registers if pipeline violates timing; Skip if no pipeline issues:set_optimize_registers true –design My_Pipeline_Subdesignoptimize_registers –only_attributed_designs# Continue if design is NOT meeting all constraints:compile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)# Continue if NOT meeting all constraints:set_cost_priority –delay# Ungroup DesignWare components amid combinational logicungroup <DesignWare_components># Apply more focus on violating critical paths, as necessarygroup_path –name <group_name> -from <path_start> -to <path_end> \–critical range <10% of max delay goal> -weight 5compile –boundary –scan –map_effort high –incremental \ (-area_effort medium|low|none)。

高级ASIC芯片综合

高级ASIC芯片综合翻译者:阿信使用Synopsys公司的DesignCompilerPhysicalCompiler和PrimeTime第二版名目写在前面前言前言事实证实,相关于集成电路IC设计规模半导体产业是相对??。

作为一个团体,80年代中期,每个芯片集成了大约1000个晶体管,我们称之为大规模集成电路〔LSI〕,仅仅在大约两年后,每个芯片的晶体管集成数量就抵达了1万~10万个,我们所用的术语也迅速的变成了甚大规模集成电路〔VLSI〕。

Preface前言这本书的第二版描述了一些使用Synopsys公司的一套工具在ASIC芯片设计中的高级概念和技术,包括ASIC芯片综合,物理综合,形式验证和静态时序分析等。

另外,对ASIC的整个设计流程和沈亚微米〔Very-Deep-Sub-Micron〕设计技术作了具体的介绍。

这本书的重点是在Synopsys工具的实时使用上,用工具往解决在深亚微米尺寸领域的各种咨询题。

将展示给读者解决在亚微米ASIC设计复杂咨询题的有效设计方法。

重点就在HDL的编码风格,综合和优化,动态仿真,形式验证,可测性设计DFT扫描链的插进,板块设计的连接,物理综合和静态时序分析。

在每一步,确定设计流程中每一段的咨询题,咨询题的解决方法并围绕此咨询题展开具体的论述。

另外,关于板块设计的要害咨询题,好比时钟的综合和最后的集成也作了较长篇幅的讨论。

最后,这本书深进的讨论了根基的Synopsys技术库和编码风格,综合优化技术。

这本书的读者对象是刚刚工作的ASIC设计工程师和学习过ASIC大规模集成电路设计与可测性设计课程的高年级学生。

这本书并不是想取代Synopsys的参考手册,而是为任何参与ASIC设计的人员而写。

同时,这本书对那些没有板块能力或者自己有技术库然而需要其他公司来做后端集成和最终制造器件的计者〔和公设司〕根基上特别有用。

因为到深亚微米技术会碰到各种各样的咨询题,本书提供了可选择的;这本书同时也介绍了设计人员对不同EDA工具商提供的各种工具时所面临常见咨询题的解决方法。

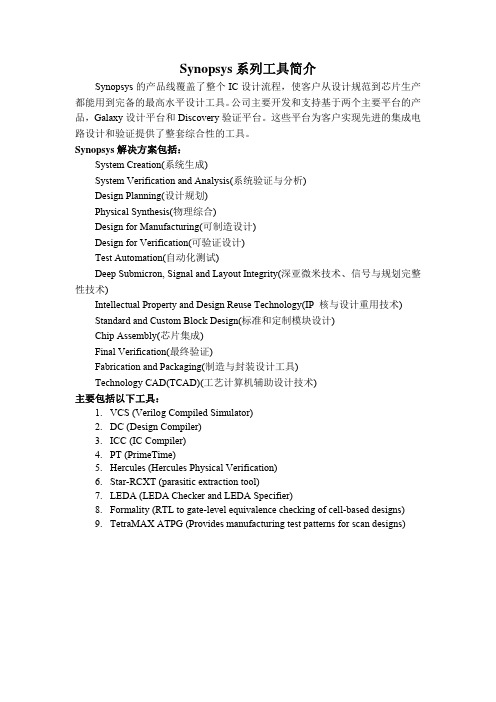

Synopsys系列工具简介

Synopsys系列工具简介Synopsys的产品线覆盖了整个IC设计流程,使客户从设计规范到芯片生产都能用到完备的最高水平设计工具。

公司主要开发和支持基于两个主要平台的产品,Galaxy设计平台和Discovery验证平台。

这些平台为客户实现先进的集成电路设计和验证提供了整套综合性的工具。

Synopsys解决方案包括:System Creation(系统生成)System Verification and Analysis(系统验证与分析)Design Planning(设计规划)Physical Synthesis(物理综合)Design for Manufacturing(可制造设计)Design for Verification(可验证设计)Test Automation(自动化测试)Deep Submicron, Signal and Layout Integrity(深亚微米技术、信号与规划完整性技术)Intellectual Property and Design Reuse Technology(IP 核与设计重用技术)Standard and Custom Block Design(标准和定制模块设计)Chip Assembly(芯片集成)Final Verification(最终验证)Fabrication and Packaging(制造与封装设计工具)Technology CAD(TCAD)(工艺计算机辅助设计技术)主要包括以下工具:1.VCS (Verilog Compiled Simulator)2.DC (Design Compiler)3.ICC (IC Compiler)4.PT (PrimeTime)5.Hercules (Hercules Physical Verification)6.Star-RCXT (parasitic extraction tool)7.LEDA (LEDA Checker and LEDA Specifier)8.Formality (RTL to gate-level equivalence checking of cell-based designs)9.TetraMAX ATPG (Provides manufacturing test patterns for scan designs)1.VCS (Verilog Compiled Simulator)VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

Synopsys工具简介

Synopsys工具简介Synopsys的产品线覆盖了整个 IC设计流程,使客户从设计规范到芯片生产都能用到完备的最高水平设计工具。

公司主要开发和支持基于两个主要平台的产品,Galaxy设计平台和Discovery验证平台。

这些平台为客户实现先进的集成电路设计和验证提供了整套综合性的工具。

Synopsys解决方案包括:· System Creation(系统生成)· System Verification and Analysis(系统验证与分析)· Design Planning(设计规划)· Physical Synthesis(物理综合)· Design for Manufacturing(可制造设计)· Design for Verification(可验证设计)· Test Automation(自动化测试)· Deep Submicron, Signal and Layout Integrity(深亚微米技术、信号与规划完整性技术)· Intellectual Property and Design Reuse Technology(IP 核与设计重用技术)· Standard and Custom Block Design(标准和定制模块设计)· Chip Assembly(芯片集成)· Final Verification(最终验证)· Fabrication and Packaging(制造与封装设计工具)· Technology CAD(TCAD)(工艺计算机辅助设计技术)主要包括以下工具:1.VCS( verilog compiled simulator )VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

DC、DCT、DCG的区别以及Wire_load_mode

DC、DCT、DCG的区别以及Wire_load_mode在dc家族系列中,DC_V,DC_E为基本的DC(Design Compiler)⼯具,具有dc所具备的基本fearture,DC在synopys⼯具系列中位置,举⾜轻重,也是业界使⽤最⼴泛的综合⼯具,相⽐candence的RC(RTL compiler)有更⼤的客户群。

进⼊到亚微⽶⼯艺下,DCT/DCG已逐渐成为优化时序的⼀种选择。

在说明这个问题之前,就我所接触到的DC相关的license问题,简述⼀下synopsys的⽣财之道。

可以说DC是synopsys最挣钱的EDA⼯具,除了基本的fearture需要license以外,⼀些⾼级的fearture,都需要额外收费。

⽐如1、compile_ultra2、set_host_number3、design_ware库(⼜细分为很多种⽐如低功耗,多⽐特寄存器,以及⼀些IP)。

4、DCT5、DCG等等,这些都需要license,⽽且价格不菲。

⼤家可以在synopsys官⽹上看到这些。

那么⾔归正传,DC/DCT/DCG有什么区别和联系呢?1、⾸先简单的讲,DCG包含DCT所有fearture,DCT包含DC所有fearture,当然有⼀些DC的fearture在DCT和DCG中已不再适⽤,⽐如wire_load_model的设置。

2、从库的⾓度来看,DCT/DCG相⽐DC多了physical library的设置。

DCG相⽐DCT⼜多了对layer,congestion相关的设置。

4、 DCT/DCG相⽐DC都需要输⼊物理约束。

通常是通过ICC做floorplan之后的def⽂件中抽取物理约束信息。

⽬前来看通过物理约束命令,编写物理约束已成为鸡肋,主要原因,这个阶段很难通过命令精确的表述block的布局布线信息。

5、低功耗设计中upf/cpf⽂件的编写,是低功耗设计的基本功。

DC/DCT/DCG都⽀持低功耗设计。

Design_compiler经典教程

微电子学实验室实验教程ASIC综合器软件——Design Compiler实验2006-7Design Compiler实验前言Design Compiler(简称DC)是synopsys公司的ASIC综合器产品,它可以完成将硬件描述语言所做的RTL级描述自动转换成优化的门级网表。

DC得到全球60多个半导体厂商、380多个工艺库的支持。

Synopsys的逻辑综合工具DC占据91%的市场份额。

DC是工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库将输入的VHDL或者Verilog的RTL描述自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

本实验对DC软件的使用进行简单的介绍,熟悉和掌握综合器软件使用中的基本概念和术语,了解如何对数字电路施加约束,掌握同步数字电路设计、约束和优化的方法,了解时钟的概念,理解同步电路静态时序分析(STA)的方法和时序报告。

西安交通大学微电子学实验室实验1setup和synthesis流程实验准备有两种界面可以运行Design Compiler:1)命令行界面,dc_shell-xg-t;2)图形用户界面(GUI),Design Vision。

本次实验主要运用GUI模式。

图1.1给出了RTL逻辑综合的直观概念和简要流程。

图1.1 RTL逻辑综合的直观概念和简要流程。

在DC中,总共有8种设计对象:z设计(Design):一种能完成一定逻辑功能的电路。

设计中可以包含下一层的子设计。

z单元(Cell):设计中包含的子设计的实例。

z参考(Reference):单元的参考对象,即单元是参考的实例。

z端口(Port):设计的基本输入输出口。

z管脚(Pin):单元的输入输出口。

z连线(Net):端口间及管脚间的互连线。

DC学习

以DesignCompiler为例子讲解综合2009-03-19 11:09:13来源:转载作者:佚名共有评论(0)条浏览次数:878第一节:什么是综合呢?synthesis,台湾翻译为-合成,其作用就是将硬件描述语言的RTL级代码转变为门级网表。

当然,现在综合技术已经很成熟了,还有推出的行为(behavioral)综合和物理(physical)综合。

我们这里讨论的是逻辑(logic)综合。

综合技术是提高设计产能的一个很重要的技术,没有综合技术的发展,我们就不可能用HDL实现电路的设计,因为HDL开始是用来供电路仿真建模使用的,到了后来才把其中一部分子集作为可综合的语言,也就是我们使用的RTL CODE。

很多人入门都用HDL做设计,就以为HDL就只是用来做设计的,没有看到HDL最初始的一面,所以在验证的时候,就无法用好HDL另外一部分强大的功能。

有时间还是可以看看Writing Testbench这本书,增强对HDL语言在验证方面作用的了解,也是提高对HDL认识很好的补充。

我们以DesignCompiler为例子讲解综合的过程。

首先,综合就要必须要用综合库,这个你可以向厂家要,综合库可以通过.lib这个库文件转变成.db综合库,这个过程可以在DesignCompiler里面用实现,综合库里面有什么内容呢?.db 是无法阅读的,.lib是可以阅读的,里面有库的基本参数的单位,库运行的条件,各种参数,最重要的是两个部分,一个是WLM-Wire Load Model,一个Gate的定义(输入输出,功能,时序参数,面积等等);这只是StandarCell的库,另外还有其他库,如RAM,DSP的综合库,都以.db的形式存在。

综合需要三种输入,一个是代码,一个是综合库,一个是综合脚本script。

综合脚本主要包括了一下内容,对综合工具环境的配置,对综合对象外部环境的设置(operation condiction),对WLD的设置,对综合对象的时序的约束,综合策略,综合优化,综合报告和输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Synopsys 综合工具Design Compiler(DC)简介 一.约束的基本概念: 约束就是对用户的设计中可度量的电路参数(如时序、面积以及电容等)进行声明。没有约束,工具(本文为DC)就不能有效地优化电路,以满足要求。 当DC对设计进行优化时,使用了两类约束: 1) 设计规则约束(Design Rule Constraints, DRC):此类约束是工具固有的,由工艺库(technology library)来定义。此类约束是设计功能正确的必要条件,通过库应用于所有设计上。当然,你可以将它们定义的更紧。 2) 优化约束(Optimization Constraints):它们是由用户定义的,前提是可实现的。 用户在使用DC时,可以通过命令行或编写约束文件(.scr)来定义约束。下图给出DC主要的DRC及优化约束,以及相关的DC命令(dc_shell接口命令)。

DRC: 最大转换时间(Max Transition Time):对于一条连线(net)来说,是其驱动pin逻辑值转化的最长时间。 最大扇出(Max Fanout):对于驱动pin来讲。 最大/最小电容(Max/Min Capacitance):用来控制连线的电容值。 器件退化(Cell Degradation):某些工艺库包括器件退化表,它列举了某一器件可驱动的最大电容,是该器件输入pin最大转换时间的函数。 优化约束: 时序约束:包括 输入/输出延迟(Input/Output Delay):同步路径 最大/最小延迟(Minimum/Maximum Delay):异步路径 最大面积(门数): 最小孔隙度(Min porosity):可布线性 二.约束报告 约束报告提供了设计规则和优化约束的信息。可采用如下命令产生相应报告: report_constraint report_port report_clock report_attribute report_timing_requirements 用户可通过输出相应报告,来分析设计是否满足了约束。如下例使用report_constraint报告一个计数器的设计约束结果。可看到最后若干项不符合约束定义。

Example dc_shell> report_constraint **************************************** Report : constraint Design : counter Version: v1998.02 Date : Wed Jan 14 1998 **************************************** Weighted Group (max_delay/setup) Cost Weight Cost --------------------------------------------------------- CLK 0.001.00 0.00 default 0.001.00 0.00 --------------------------------------------------------- max_delay/setup 0.00 Total Neg Critical Group (critical_range) Slack Endpoints Cost ----------------------------------------------------- CLK 0.00 0 0.00 default 0.00 0 0.00 ----------------------------------------------------- critical_range 0.00 Constraint Cost ----------------------------------------------------- max_transition 0.00 (MET) max_fanout 0.00 (MET) max_delay/setup 0.00 (MET) critical_range 0.00 (MET) min_delay/hold 0.40 (VIOLATED) max_leakage_power 6.00 (VIOLATED) max_dynamic_power 14.03 (VIOLATED) max_area 48.00 (VIOLATED) min_porosity 2.00 (VIOLATED)

三. 基本综合流程 一个基本的综合流程如下图所示,它包括如下步骤: 1) 开发HDL模型 2) 启动DC shell界面 3) 指定相关库 4) 读入设计 5) 定义设计环境 6) 选择编译策略 7) 设置设计约束 8) 优化 9) 分析与调试 10) 保存设计数据 11) 退出shell界面 3.1开发HDL模型 为了达到最佳综合结果,HDL文件编写应注意如下三方面: 1. 设计数据管理:为了简化数据的交换、查找,以及开发数据策划和版本控制方法,设计者应遵循一定的规则,其中包括文件生成、维护及删除规则;文件命名规范;设计的层次化目录管理等。 2. 设计划分(partitioning):对于大的设计来说,设计划分的好坏影响综合结果。划分得当会减少编译时间并简化约束定义。 3. 设计编码(Coding):好的HDL编码可以产生小而快的设计。

3.2启动DC shell界面 如果要进入dc_shell,可在系统提示符下键入 %dc_shell

3.3 指定相关库 DC使用了如下一些库: a) 工艺库:半导体生产厂定义的器件信息,如器件名、器件管脚名、延迟时间以及管脚负载等。采用link_library及target_library变量指定。 b) 符号库:定义了DA(Design Analyzer)的可视符号。采用symbol_library变量指定。 c) 宏单元库(DesignWare):提供很多内建HDL算子的实现模块。

3.4 读入设计 DC既可以读入RTL设计又可以读入门级网表。RTL设计可采用analyze和elaborate命令读入,而网表采用read_file读入。

3.5 定义设计环境 设计环境指围绕将要进行综合的设计的环境,由一套属性(attribute)和约束(constraint)来模拟。主要包括: 操作条件:温度、电压和制造过程。 线负载模型:通过估计连线长度、扇出以及面积等,预估连线延迟。 系统接口:包括驱动设计的器件以及被驱动的负载定义,如下图所示。

3.6 选择编译策略 对一个层次式设计来说,用户可选择的编译策略包括: a) 自顶向下的编译 b) 自底向上的编译 c) 特征化编译(characterize)

3.7 设置设计约束 DC使用两类约束来优化设计: a) DRC:固有约束,包括

b) 优化约束:用户定义的约束,包括

3.8 优化 DC使用目标工艺库、DRC以及优化约束对设计进行综合,并将其变为专门面向工艺的门级实现。 可采用compile命令启动综合过程。

3.9 分析与调试 DC能生成报告帮助用户分析优化结果,并调试出现的问题。 3.10 保存设计数据 使用write命令存储设计的数据(如网表、SDF文件等)。 3.11 退出shell界面 用户可以在任何时候退出dc_shell,但是此时dc_shell并不会自动保存数据。可以采用下面任何一种方法退出 a) 输入quit b) 输入exit c) 按Ctrl+d

四. 设计实例 下面的例子给出一个约束文件,采用自顶向下的编译策略,对Adder16.v进行优化。 /* specify the libraries */ 指定库 target_library = my_lib.db symbol_library = my_lib.sdb link_library = "*" + target_library /* read the design */读入设计 read -format verilog Adder16.v /* define the design environment */定义设计环境 set_operating_conditions WCCOM set_wire_load "10x10" set_load 2.2 sout set_load 1.5 cout set_driving_cell -cell FD1 all_inputs() set_drive 0 clk /* set the optimization constraints */设置优化约束 create_clock clk -period 10 set_input_delay -max 1.35 -clock clk {ain, bin} set_input_delay -max 3.5 -clock clk cin set_output_delay -max 2.4 -clock clk cout set_max_area 0 /* map and optimize the design */映射并优化设计 uniquify compile//执行综合并优化 /* analyze and debug the design */分析并调试设计 report_constraint -all_violators report_area /* save the design database */保存设计数据 write -format db -hierarchy -output Adder16.db

用户可以采用如下几种方法执行命令: a) 进入dc_shell,并逐个键入命令 b) 进入dc_shell,并执行脚本文件,采用include命令(dcsh模式)或source命令(Tcl模式)。如假设上面的脚本文件称作run.scr,则在dcsh模式下运行 dc_shell> include run.scr

c) 在UNIX命令行模式下运行脚本,如 % dc_shell -f run.scr