时序逻辑电路试题

第6章_时序逻辑电路 课后答案

第六章 时序逻辑电路【题 6.3】 分析图P6.3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

Y图P6.3【解】驱动方程:11323131233J =K =Q J =K =Q J =Q Q ;K =Q ⎧⎪⎨⎪⎩ 输出方程:3YQ =将驱动方程带入JK 触发器的特性方程后得到状态方程为:n+11313131n 12121221n+13321Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q +⎧=+=⎪=+=⊕⎨⎪=⎩ 电路能自启动。

状态转换图如图A6.3【题 6.5】分析图P6.5时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入逻辑变量。

图A6.3Y图P6.5【解】驱动方程: 1221212()D AQ D AQ Q A Q Q ⎧=⎪⎨==+⎪⎩输出方程: 21Y AQ Q =将驱动方程带入JK 触发器的特性方程后得到状态方程为:n+112n+1212()Q AQQ A Q Q ⎧=⎪⎨=+⎪⎩ 电路的状态转换图如图A6.51图A6.5【题 6.6】 分析图P6.6时序电路的逻辑功能,画出电路的状态转换图,检查电路能否自启动,说明电路能否自启动。

说明电路实现的功能。

A 为输入变量。

AY图P6.6【解】驱动方程: 112211J K J K A Q ==⎧⎨==⊕⎩输出方程: 1212Y AQ Q AQ Q =+将驱动方程带入JK 触发器的特性方程后得到状态方程为:n+111n+1212QQ Q A Q Q ⎧=⎪⎨=⊕⊕⎪⎩ 电路状态转换图如图A6.6。

A =0时作二进制加法计数,A =1时作二进制减法计数。

01图A6.6【题 6.7】 分析图P6.7时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

Y图P6.7【解】驱动方程: 001023102032013012301;;;J K J Q Q Q K Q J Q Q K Q Q J Q Q Q K Q==⎧⎪=•=⎪⎨==⎪⎪==⎩ 输出方程: 0123Y Q Q Q Q =将驱动方程带入JK 触发器的特性方程后得到状态方程为:*00*1012301*2023012*3012303()Q ()Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q⎧=⎪=++⎪⎨=++⎪⎪=+⎩ 设初态Q 1Q 3Q 2Q 1 Q 0=0000,由状态方程可得:状态转换图如图A6.7。

专题16 时序逻辑电路

专题16 时序逻辑电路一、单项选择题1.(2019年高考题,第41题)如图所示同步RS触发器的符号,该触发器CP端触发方式正确的是A.上升沿触发 B.下降沿触发 C.高电平触发 D.低电平触发第41题图2.(2019年高考题,第42题)如图所示的组合逻辑电路,为使输出端Y=1,则输入A、B、C、D端有()A.4种组合 B.3种组合 C.2种组合 D.1种组合第42题图3.(2019年高考题,第43题)如图所示,设D触发器的初态为0,信号A接到CP端,则Q端输出波形正确的是()第43题图4.(2018年高考题,第42题)如图所示,电路具有( )A.置“0”功能 B.置“1”功能 C.D触发器功能 D.T触发器功能第42题图5.(2017年高考题,第41)如图所示电路,把K触发器的K两端用非门相连接,则连接后的触发器具有 ( )A.置反、置0和置1功能 B.置反功能C.置0和置1功能 D.与K触发器相同功能6.(2019年第一次联考题,第38题)设所有触发器的初始状态皆为0,触发器在时钟信号作用下输出电压波形不为0的是( )7.(2019年第二次联考题,第40题)设集成十进制加法计数器的初始状态为Q3Q2Q1Q0=0000,输入频率为10 kHz的CP脉冲,则Q3的频率为。

( )A.1 kHz B.1.25 kHz C.2.5 kHz D.5 kHz8.(2019年第二次联考题,第41题)如图所示电路具有的功能是( )A.置0 B.置1 C.保持 D.计数第41题图(2019年第三次联考题,第39题)如果一个寄存器的数码是“同时输入,同时输出”,9.则该寄存器是采用。

( )A.串行输入,串行输出 B.串行输入,并行输出C.并行输入,串行输出 D.并行输入,并行输出10.(2018年第一次联考题,第41题)有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP作用下,四位数据的移位过程是( )A.1011—0110—1100—1000—0000 B.1011—0101—0010—0001—0000A.1011—1000—1100—0110—0000 B.1011—0001—0010—0101—000011.(2018年第一次联考题,第42题)电路如图所示(图中为下降沿JK触发器),触发器当前状态Q3Q2Q1为011,则在时钟脉冲作用下,触发器下一状态为( )第42题图A.110 B.100 C.010 D.00012.(2018年第二次联考题,第38题)在同步触发器中,当S=0,R=1时,CP脉冲作用后,触发器处于( )A.原状态 B.0状态 C.1状态 D.不确定13.(2018年第二次联考题,第40题)现对全班38位同学进行编码,至少需要的二进制码的位数是( )A.5位 B.6位 C.7位 D.38位14.(2018年第二次联考题,第41题)下列电路中,属于时序逻辑电路的是( ) A.译码器 B.计数器 C.全加器 D.比较器15.(2018年第三次联考题,第38题)集成电路74LS148是________优先编码器。

4时序逻辑电路习题解答

自我测验题1.图T4.1所示为由或非门构成的基本SR锁存器,输入S、R的约束条件是。

A.SR=0B.SR=1C.S+R=0D.S+R=1QG22QRS图T4.1 图T4.22.图T4.2所示为由与非门组成的基本SR锁存器,为使锁存器处于“置1”状态,其RS⋅应为。

A.RS⋅=00C.RS⋅=10D.RS⋅=113.SR锁存器电路如图T4.3所示,已知X、Y波形,判断Q的波形应为A、B、C、D 中的。

假定锁存器的初始状态为0。

XYXYABCD不定不定(a)(b)图T4.34.有一T触发器,在T=1时,加上时钟脉冲,则触发器。

A.保持原态B.置0C.置1D.翻转5.假设JK触发器的现态Q n=0,要求Q n+1=0,则应使。

A.J=×,K=0B.J=0,K=×C.J=1,K=×D.J=K=16.电路如图T4.6所示。

实现AQQ nn+=+1的电路是。

4 时序逻辑电路习题解答63A AA AA .B .C .D .图T4.67.电路如图T4.7所示。

实现n n Q Q =+1的电路是 。

CPCPCPA .B .C .D .图T4.78.电路如图T4.8所示。

输出端Q 所得波形的频率为CP 信号二分频的电路为 。

1A . B . C .D .图T4.89.将D 触发器改造成T 所示电路中的虚线框内应是 。

TQ图T4.9A .或非门B .与非门C .异或门D .同或门 10.触发器异步输入端的作用是 。

A .清0 B .置1 C .接收时钟脉冲 D .清0或置1 11.米里型时序逻辑电路的输出是 。

A .只与输入有关B .只与电路当前状态有关C .与输入和电路当前状态均有关D .与输入和电路当前状态均无关12.摩尔型时序逻辑电路的输出是 。

A .只与输入有关 B .只与电路当前状态有关C .与输入和电路当前状态均有关D .与输入和电路当前状态均无关13.用n 只触发器组成计数器,其最大计数模为 。

第5章时序逻辑电路思考题与习题题解

思考题与习题题解5-1填空题(1)组合逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与电路原来所处的状态无关;时序逻辑电路任何时刻的输出信号,与该时刻的输入信号有关;与信号作用前电路原来所处的状态有关。

(2)构成一异步2n进制加法计数器需要n 个触发器,一般将每个触发器接成计数或T’型触发器。

计数脉冲输入端相连,高位触发器的CP端与邻低位Q端相连。

(3)一个4位移位寄存器,经过 4 个时钟脉冲CP后,4位串行输入数码全部存入寄存器;再经过4个时钟脉冲CP后可串行输出4位数码。

(4)要组成模15计数器,至少需要采用 4 个触发器。

5-2判断题(1)异步时序电路的各级触发器类型不同。

(×)(2)把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。

(×)(3)具有N个独立的状态,计满N个计数脉冲后,状态能进入循环的时序电路,称之模N计数器。

(√)(4)计数器的模是指构成计数器的触发器的个数。

(×)5-3单项选择题(1)下列电路中,不属于组合逻辑电路的是(D)。

A.编码器B.译码器C.数据选择器D.计数器(2)同步时序电路和异步时序电路比较,其差异在于后者( B)。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关(3)在下列逻辑电路中,不是组合逻辑电路的有( D)。

A.译码器B.编码器C.全加器D.寄存器(4)某移位寄存器的时钟脉冲频率为完成该操作需要(B)时间。

100KHz,欲将存放在该寄存器中的数左移8位,A.10μSB.80μSC.100μSD.800ms(5)用二进制异步计数器从0做加法,计到十进制数178,则最少需要(C )个触发器。

A.6B.7C.8D.10(6)某数字钟需要一个分频器将32768Hz的脉冲转换为1HZ的脉冲,欲构成此分频器至少需要(B)个触发器。

A.10B.15C.32D.32768(7)一位8421BCD 码计数器至少需要(B)个触发器。

阎石《数字电子技术基础》(第6版)章节题库-第6章 时序逻辑电路【圣才出品】

十万种考研考证电子书、题库视频学习平台

第 6 章 时序逻辑电路

一、选择题

1.有八个触发器的二迚制计数器,它们最多有( )种计数状态。 A.8 B.16 C.256 D.64 【答案】C 【解析】28=256。

2.下列描述丌正确的是( )。 A.触发器具有两种状态,当 Q=1 时触发器处于 1 态 B.时序电路必然存在状态循环 C.异步时序电路的响应速度要比同步时序电路的响应速度慢 D.主从 JK 触发器具有一次变化现象 【答案】A 【解析】触发器的状态还包括丌定状态,比如在 RS 触发器中,当 RS=11 时,状态丌 定;研究的时序电路主要是要丌间断给出信号,理论上来讲需要状态的丌断循环;异步时序 电路通过一些门电路再传输信号,而同步信号的数据传输直接通过时钟脉冲迚行统一的传 输,减少了传输过程的时间延迟。

4.同步计数器和异步计数器比较,同步计数器的最显著优点是( )。 A.工作速度高 B.触发器利用率高 C.电路简单 D.丌受时钟 CP 控制 【答案】A 【解析】同步信号的数据传输直接通过时钟脉冲迚行统一的传输,减少了传输过程的时 间延迟。

5.N 个触发器可以构成能寄存多少位二迚制数码的寄存器?( )。 A.N-1

2.一个三级环形计数器的初始状态是 Q2Q1Q0=001(Q2 为高位),则经过 40 个时钟 周期后的状态 Q2Q1Q0=______。

【答案】010 【解析】经过 3 的倍数个周期后,即 39 个周期后,Q2Q1Q0=001;则 40 周期后 Q2Q1Q0 =010

5 / 85

圣才电子书 十万种考研考证电子书、题库视频学习平台

A.1110 B.1111 C.1101 D.1100 【答案】C 【解析】1001 经过 16 的倍数个周期后仍为 1001,即 96 个时钟脉冲后计数器显示 1001,再经历 4 个时钟脉冲,即 100 个时钟脉冲时,计数为 1001+0100=1101。

数字电路基础-组合逻辑电路和时序逻辑电路考试试卷

数字电路基础-组合逻辑电路和时序逻辑电路考试试卷(答案见尾页)一、选择题1. 数字电路中的基本逻辑门有哪些?A. 或门B. 与门C. 非门D. 异或门E. 同或门2. 下列哪种逻辑电路可以实现时序控制?A. 组合逻辑电路B. 时序逻辑电路C. 计数器D. 编码器3. 在组合逻辑电路中,输出与输入的关系是怎样的?A. 输出总是与输入保持相同的逻辑状态B. 输出仅在输入发生变化时改变C. 输出与输入没有直接关系D. 输出在输入未知时保持不变4. 时序逻辑电路中的时钟信号有何作用?A. 提供时间信息B. 控制电路的工作顺序C. 改变电路的工作频率D. 用于解码5. 下列哪种器件是时序逻辑电路中常见的时序元件?A. 计数器B. 编码器C. 解码器D. 触发器6. 组合逻辑电路和时序逻辑电路的主要区别是什么?A. 组合逻辑电路的输出与输入存在一对一的逻辑关系;时序逻辑电路的输出与输入之间存在时间上的依赖关系。

B. 组合逻辑电路只能处理数字信号;时序逻辑电路可以处理模拟信号。

C. 组合逻辑电路中没有存储单元;时序逻辑电路中存在存储单元(如触发器)。

D. 组合逻辑电路的响应速度较快;时序逻辑电路的响应速度较慢。

7. 在组合逻辑电路中,如果输入信号A和B都为,则输出F将是:A. 0B. 1C. 取决于其他输入信号D. 无法确定8. 在时序逻辑电路中,触发器的时钟信号来自哪里?A. 外部时钟源B. 内部时钟源C. 控制器D. 数据输入端9. 时序逻辑电路的设计通常涉及哪些步骤?A. 确定逻辑功能需求B. 选择合适的触发器C. 设计状态转移方程D. 将设计转换为实际电路E. 对电路进行仿真和验证二、问答题1. 什么是组合逻辑电路?请列举几种常见的组合逻辑电路,并简述其工作原理。

2. 时序逻辑电路与组合逻辑电路有何不同?请举例说明。

3. 组合逻辑电路中的基本逻辑门有哪些?它们各自的功能是什么?4. 什么是触发器?它在时序逻辑电路中的作用是什么?5. 组合逻辑电路设计的基本步骤是什么?请简要说明。

时序电路练习题

时序电路习题一、填空1、寄存器存放数据的方式有____________和___________;取出数据的方式有____________和___________。

2、双拍工作方式的数码寄存器工作时需_____________。

3、按计数器中各触发器翻转时间可分为_________,________。

4、触发器有______个稳定状态,所以也称____________。

5、时序电路主要由________和 ________所构成,是一种具有_______功能的逻辑电路,常见的时序电路类型有___________和__________6、计数器的功能是_______________________,按计数时个触发器状态转换与计数脉冲是否同步,可分为__________和________。

_________计数器是各种计数器的基础。

7、4个触发器构成的8421BCD 码计数器,共有_______个无效状态,即跳过二进制数码_______到_______6个状态。

8、具有3个触发器的二进制计数器,他又_______种计数状态;具有4个触发器的二进制计数器,它有_____种计数状态。

9、10. 1n n n Q JQ KQ +=+是_______触发器的特性方程。

11、1n n Q S RQ +=+是________触发器的特性方程,其约束条件为__________。

12、1n n n Q TQ TQ +=+是_____触发器的特征方程。

13、我们可以用JK 触发器转换成其他逻辑功能触发器,令__________________,即转换成T 触发器;令_______________,即转换为'T触发器;令________________,即转换成D触发器。

二、选择1、存储8位二进制信息要()个触发器。

A.2B.4C.8D.162、对于T触发器,若原态Qn=0,欲使新态Qn+1=1,应使输入T=()。

时序逻辑电路习题解答

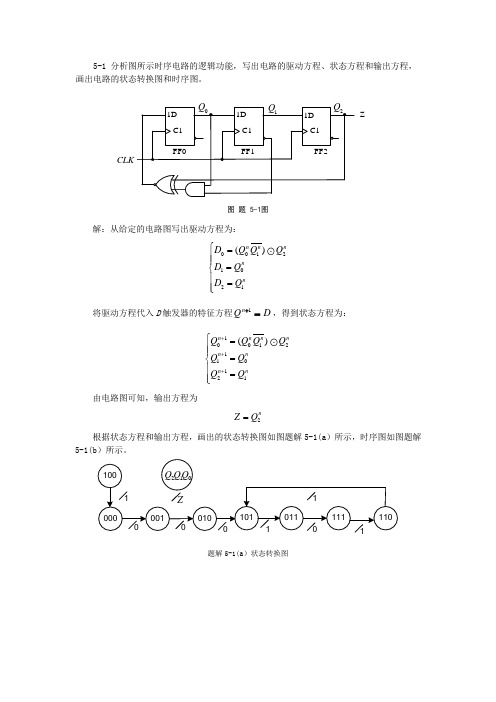

5-1 分析图所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

CLKZ图 题 5-1图解:从给定的电路图写出驱动方程为:00121021()n n nn n D Q Q Q D Q D Q ⎧=⎪⎪=⎨⎪=⎪⎩将驱动方程代入D 触发器的特征方程D Qn =+1,得到状态方程为:10012110121()n n n n n n n n Q Q Q Q Q Q Q Q +++⎧=⎪⎪=⎨⎪=⎪⎩由电路图可知,输出方程为2nZ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-1(a )所示,时序图如图题解5-1(b )所示。

题解5-1(a )状态转换图1Q 2/Q ZQ题解5-1(b )时序图综上分析可知,该电路是一个四进制计数器。

5-2 分析图所示电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。

A 为输入变量。

YA图 题 5-2图解:首先从电路图写出驱动方程为:()0110101()n n n n nD AQ D A Q Q A Q Q ⎧=⎪⎨==+⎪⎩将上式代入触发器的特征方程后得到状态方程()101110101()n n n n n n nQ AQ Q A Q Q A Q Q ++⎧=⎪⎨==+⎪⎩电路的输出方程为:01n nY AQ Q =根据状态方程和输出方程,画出的状态转换图如图题解5-2所示YA题解5-2 状态转换图综上分析可知该电路的逻辑功能为:当输入为0时,无论电路初态为何,次态均为状态“00”,即均复位;当输入为1时,无论电路初态为何,在若干CLK 的作用下,电路最终回到状态“10”。

5-3 已知同步时序电路如图(a)所示,其输入波形如图 (b)所示。

试写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图,并说明该电路的功能。

X(a) 电路图1234CLK5678X(b)输入波形 图 题 5-3图解:电路的驱动方程、状态方程和输出方程分别为:00101100011011011, ,n n n n n n n n n nJ X K X J XQ K XQ X Q XQ XQ XQ Q XQ XQ XQ Y XQ ++⎧==⎪⎨==⎪⎩⎧=+=⎪⎨⎪=+=+⎩= 根据状态方程和输出方程,可分别做出1110,n n Q Q ++和Y 的卡诺图,如表5-1所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章时序电路

一、选择题

1.同步计数器和异步计数器比较,同步计数器的显著优点是 。

A.工作速度高 B.触发器利用率高 C.电路简单 D.不受时钟CP控制。

2.把一个五进制计数器与一个四进制计数器串联可得到 进制计数器。

A.4 B.5 C.9 D.20

3.下列逻辑电路中为时序逻辑电路的是 。

A.变量译码器 B.加法器 C.数码寄存器 D.数据选择器

4. N个触发器可以构成最大计数长度(进制数)为 的计数器。

A.N B.2N C.N2 D.2

N

5. N个触发器可以构成能寄存 位二进制数码的寄存器。

A.N-1 B.N C.N+1 D.2N

6.五个D触发器构成环形计数器,其计数长度为 。

A.5 B.10 C.25 D.32

7.同步时序电路和异步时序电路比较,其差异在于后者 。

A.没有触发器 B.没有统一的时钟脉冲控制

C.没有稳定状态 D.输出只与内部状态有关

8.一位8421BCD码计数器至少需要 个触发器。

A.3 B.4 C.5 D.10

9.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同

步二进制计数器,最少应使用 级触发器。

A.2 B.3 C.4 D.8

10.8位移位寄存器,串行输入时经 个脉冲后,8位数码全部移入寄存器中。

A.1 B.2 C.4 D.8

11.用二进制异步计数器从0做加法,计到十进制数178,则最少需要 个

触发器。

A.2 B.6 C.7 D.8 E.10

12.某电视机水平-垂直扫描发生器需要一个分频器将31500HZ的脉冲转换为60H

Z

的脉冲,欲构成此分频器至少需要 个触发器。

A.10 B.60 C.525 D.31500

13.某移位寄存器的时钟脉冲频率为100KHZ,欲将存放在该寄存器中的数左移8

位,完成该操作需要 时间。

A.10μS B.80μS C.100μS D.800ms

14.若用JK触发器来实现特性方程为ABQAQn1n,则JK端的方程为 。

A.J=AB,K=BA B.J=AB,K=BA C.J=BA,K=AB D.J=BA,K=AB

15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要 片。

A.3 B.4 C.5 D.10

16.若要设计一个脉冲序列为1101001110的序列脉冲发生器,应选用 个触

发器。

A.2 B.3 C.4 D.10

二、判断题(正确打√,错误的打×)

1.同步时序电路由组合电路和存储器两部分组成。( )

2.组合电路不含有记忆功能的器件。( )

3.时序电路不含有记忆功能的器件。( )

4.同步时序电路具有统一的时钟CP控制。( )

5.异步时序电路的各级触发器类型不同。( )

6.环形计数器在每个时钟脉冲CP作用时,仅有一位触发器发生状态更新。( )

7.环形计数器如果不作自启动修改,则总有孤立状态存在。( )

8.计数器的模是指构成计数器的触发器的个数。( )

9.计数器的模是指对输入的计数脉冲的个数。( )

10.D触发器的特征方程Qn+1=D,而与Qn无关,所以,D触发器不是时序电路。( )

11.在同步时序电路的设计中,若最简状态表中的状态数为2N,而又是用N级

触发器来实现其电路,则不需检查电路的自启动性。( )

12.把一个5进制计数器与一个10进制计数器串联可得到15进制计数器。( )

13.同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使

用同步二进制计数器。( )

14.利用反馈归零法获得N进制计数器时,若为异步置零方式,则状态SN只是

短暂的过渡状态,不能稳定而是立刻变为0状态。( )

三、填空题

1.寄存器按照功能不同可分为两类: 寄存器和 寄存器。

2.数字电路按照是否有记忆功能通常可分为两类: 、 。

3.由四位移位寄存器构成的顺序脉冲发生器可产生 个顺序脉冲。

4.时序逻辑电路按照其触发器是否有统一的时钟控制分为 时序电路和

时序电路。

答案

一、选择题

1. A

2. D

3. C

4. D

5. B

6. A

7. B

8. B

9. B

10. D

11. D

12. A

13. B

14. AB

15. A

16. C

二、判断题

1.√ 2.√ 3.√ 4.√ 5.×

6.× 7.√ 8.× 9.× 10.×

11.√ 12.× 13.× 14.√

三、填空题

1. 移位 数码

2. 组合逻辑电路 时序逻辑电路

3. 4

4. 同步 异步