74LVC系列

SN74LVC2G04DBVRE4中文资料

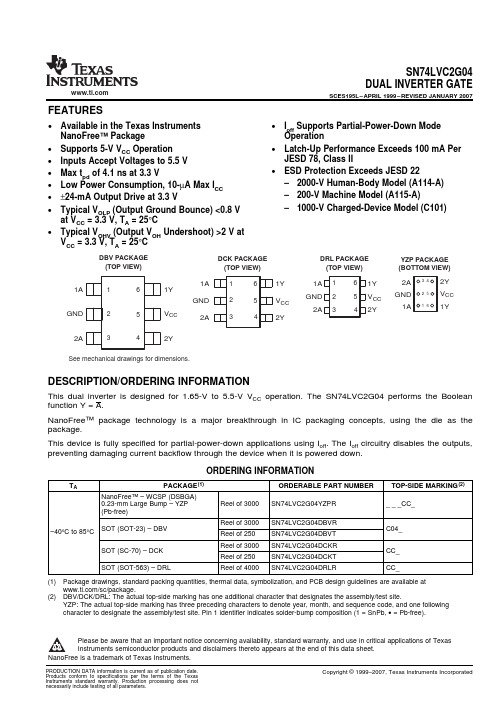

FEATURES1A 1Y2YGND2ADBV PACKAGE (TOP VIEW)YZP PACKAGE (BOTTOM VIEW)DCK PACKAGE (TOP VIEW)1A 1Y 2Y2A1A2A 1Y2Y GND DRL PACKAGE (TOP VIEW)See mechanical drawings for dimensions.V CC V CC CC V CC DESCRIPTION/ORDERING INFORMATIONSN74LVC2G04DUAL INVERTER GATESCES195L–APRIL 1999–REVISED JANUARY 2007•Available in the Texas Instruments •I off Supports Partial-Power-Down Mode NanoFree™PackageOperation•Supports 5-V V CC Operation •Latch-Up Performance Exceeds 100mA Per JESD 78,Class II•Inputs Accept Voltages to 5.5V •ESD Protection Exceeds JESD 22•Max t pd of 4.1ns at 3.3V–2000-V Human-Body Model (A114-A)•Low Power Consumption,10-µA Max I CC –200-V Machine Model (A115-A)•±24-mA Output Drive at 3.3V–1000-V Charged-Device Model (C101)•Typical V OLP (Output Ground Bounce)<0.8V at V CC =3.3V,T A =25°C•Typical V OHV (Output V OH Undershoot)>2V at V CC =3.3V,T A =25°CThis dual inverter is designed for 1.65-V to 5.5-V V CC operation.The SN74LVC2G04performs the Boolean function Y =A.NanoFree™package technology is a major breakthrough in IC packaging concepts,using the die as the package.This device is fully specified for partial-power-down applications using I off .The I off circuitry disables the outputs,preventing damaging current backflow through the device when it is powered down.ORDERING INFORMATIONT APACKAGE (1)ORDERABLE PART NUMBER TOP-SIDE MARKING (2)NanoFree™–WCSP (DSBGA)0.23-mm Large Bump –YZP Reel of 3000SN74LVC2G04YZPR ___CC_(Pb-free)Reel of 3000SN74LVC2G04DBVR SOT (SOT-23)–DBV C04_–40°C to 85°CReel of 250SN74LVC2G04DBVT Reel of 3000SN74LVC2G04DCKR SOT (SC-70)–DCK CC_Reel of 250SN74LVC2G04DCKT SOT (SOT-563)–DRLReel of 4000SN74LVC2G04DRLRCC_(1)Package drawings,standard packing quantities,thermal data,symbolization,and PCB design guidelines are available at /sc/package.(2)DBV/DCK/DRL:The actual top-side marking has one additional character that designates the assembly/test site.YZP:The actual top-side marking has three preceding characters to denote year,month,and sequence code,and one following character to designate the assembly/test site.Pin 1identifier indicates solder-bump composition (1=SnPb,•=Pb-free).Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.1A1Y2A2YAbsolute Maximum Ratings(1)SN74LVC2G04DUAL INVERTER GATESCES195L–APRIL1999–REVISED JANUARY2007FUNCTION TABLE(EACH INVERTER)INPUT OUTPUTA YH LL HLOGIC DIAGRAM(POSITIVE LOGIC)over operating free-air temperature range(unless otherwise noted)MIN MAX UNIT V CC Supply voltage range–0.5 6.5VV I Input voltage range(2)–0.5 6.5VV O Voltage range applied to any output in the high-impedance or power-off state(2)–0.5 6.5VV O Voltage range applied to any output in the high or low state(2)(3)–0.5V CC+0.5VI IK Input clamp current V I<0–50mAI OK Output clamp current V O<0–50mAI O Continuous output current±50mAContinuous current through V CC or GND±100mADBV package165DCK package259θJA Package thermal impedance(4)°C/WDRL package142YZP package123T stg Storage temperature range–65150°C (1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.(3)The value of V CC is provided in the recommended operating conditions table.(4)The package thermal impedance is calculated in accordance with JESD51-7.Recommended Operating Conditions(1)SN74LVC2G04DUAL INVERTER GATESCES195L–APRIL1999–REVISED JANUARY2007MIN MAX UNIT Operating 1.65 5.5V CC Supply voltage VData retention only 1.5V CC=1.65V to1.95V0.65×V CCV CC=2.3V to2.7V 1.7V IH High-level input voltage VV CC=3V to3.6V2V CC=4.5V to5.5V0.7×V CCV CC=1.65V to1.95V0.35×V CCV CC=2.3V to2.7V0.7V IL Low-level input voltage VV CC=3V to3.6V0.8V CC=4.5V to5.5V0.3×V CCV I Input voltage0 5.5V V O Output voltage0V CC VV CC=1.65V–4V CC=2.3V–8I OH High-level output current–16mAV CC=3V–24V CC=4.5V–32V CC=1.65V4V CC=2.3V8I OL Low-level output current16mAV CC=3V24V CC=4.5V32V CC=1.8V±0.15V,2.5V±0.2V20∆t/∆v Input transition rise or fall rate V CC=3.3V±0.3V10ns/VV CC=5V±0.5V5T A Operating free-air temperature–4085°C (1)All unused inputs of the device must be held at V CC or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs,literature number SCBA004.Electrical CharacteristicsSwitching CharacteristicsOperating CharacteristicsSN74LVC2G04DUAL INVERTER GATESCES195L–APRIL 1999–REVISED JANUARY 2007over recommended operating free-air temperature range (unless otherwise noted)PARAMETERTEST CONDITIONSV CC MIN TYP (1)MAX UNIT1.65V to 5.5I OH =–100µA V CC –0.1V I OH =–4mA1.65V 1.2I OH =–8mA2.3V 1.9V OHV I OH =–16mA 2.43V I OH =–24mA 2.3I OH =–32mA 4.5V 3.81.65V to 5.5I OL =100µA 0.1V I OL =4mA1.65V 0.45I OL =8mA2.3V 0.3V OLV I OL =16mA 0.43V I OL =24mA 0.55I OL =32mA4.5V 0.55I I A inputsV I =5.5V or GND 0to 5.5V±5µA I off V I or V O =5.5V 0±10µA 1.65V to 5.5I CC V I =5.5V or GND,I O =010µA V ∆I CC One input at V CC –0.6V,Other inputs at V CC or GND3V to 5.5V 500µA C i V I =V CC or GND3.3V3.5pF (1)All typical values are at V CC =3.3V,T A =25°C.over recommended operating free-air temperature range (unless otherwise noted)(see Figure 1)V CC =1.8V V CC =2.5V V CC =3.3V V CC =5V FROM TO ±0.15V ±0.2V ±0.3V ±0.5V PARAMETERUNIT(INPUT)(OUTPUT)MIN MAXMIN MAX MIN MAX MIN MAX t pdAY3.181.54.41.24.113.2ns T A =25°CV CC =1.8VV CC =2.5VV CC =3.3VV CC =5V PARAMETERTEST CONDITIONSUNIT TYP TYP TYP TYP C pdPower dissipation capacitancef =10MHz14141416pFPARAMETER MEASUREMENT INFORMATIONFrom Output Under TestLOAD CIRCUITOpen Data InputTiming InputV I0 VV I0 V0 VInputVOLTAGE WAVEFORMS SETUP AND HOLD TIMESVOLTAGE WAVEFORMS PROPAGATION DELAY TIMESINVERTING AND NONINVERTING OUTPUTSVOLTAGE WAVEFORMS PULSE DURATIONV OHV OHV OLV OLV I0 V InputOutput Waveform 1S1 at V LOAD (see Note B)Output Waveform 2S1 at GND (see Note B)V OLV OH V LOAD /20 V≈0 VV IVOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES LOW- AND HIGH-LEVEL ENABLINGOutputOutputt PLH /t PHL t PLZ /t PZL t PHZ /t PZHOpen V LOAD GNDTEST S1NOTES: A.C L includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z O = 50 Ω.D.The outputs are measured one at a time, with one transition per measurement.E.t PLZ and t PHZ are the same as t dis .F.t PZL and t PZH are the same as t en .G.t PLH and t PHL are the same as t pd .H.All parameters and waveforms are not applicable to all devices.Output Control V I1.8 V ± 0.15 V2.5 V ± 0.2 V3.3 V ± 0.3 V 5 V ± 0.5 V1 k Ω500 Ω500 Ω500 ΩV CC R L 2 × V CC 2 × V CC 6 V 2 × V CCV LOAD C L 30 pF 30 pF 50 pF 50 pF0.15 V 0.15 V 0.3 V 0.3 VV ∆V CC V CC 3 V V CCV I V CC /2V CC /21.5 V V CC /2V M t r /t f ≤2 ns ≤2 ns ≤2.5 ns ≤2.5 nsINPUTS SN74LVC2G04DUAL INVERTER GATESCES195L–APRIL 1999–REVISED JANUARY 2007Figure 1.Load Circuit and Voltage WaveformsPACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74LVC2G04DBVR ACTIVE SOT-23DBV 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DBVRE4ACTIVE SOT-23DBV 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DBVT ACTIVE SOT-23DBV 6250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DBVTE4ACTIVE SOT-23DBV 6250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DCKR ACTIVE SC70DCK 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DCKRE4ACTIVE SC70DCK 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DCKRG4ACTIVE SC70DCK 63000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DCKT ACTIVE SC70DCK 6250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DCKTE4ACTIVE SC70DCK 6250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DCKTG4ACTIVE SC70DCK 6250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04DRLR ACTIVE SOT-533DRL 64000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LVC2G04YZPRACTIVEWCSPYZP63000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS),Pb-Free (RoHS Exempt),or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt):This component has a RoHS exemption for either 1)lead-based flip-chip solder bumps used between the die and package,or 2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free (RoHS compatible)as defined above.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.4-May-2007In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annualbasis.4-May-2007TAPE AND REELINFORMATION12-May-2007DevicePackage Pins SiteReel Diameter (mm)Reel Width (mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74LVC2G04DBVR DBV 6HNT 1809 3.23 3.17 1.3748Q3SN74LVC2G04DBVR DBV 6NFME 00 3.23 3.17 1.3748Q3SN74LVC2G04DBVT DBV 6HNT 1809 3.23 3.17 1.3748Q3SN74LVC2G04DCKR DCK 6HNC 1809 2.24 2.34 1.2248Q3SN74LVC2G04DCKT DCK 6HNT 1809 2.24 2.34 1.2248Q3SN74LVC2G04DRLR DRL 6HNT 1809 1.78 1.780.6948Q3SN74LVC2G04YZPRYZP6ASEK18081.021.520.6648Q1TAPE AND REEL BOX INFORMATIONDevicePackage Pins Site Length (mm)Width (mm)Height (mm)SN74LVC2G04DBVR DBV 6HNT 200.0200.030.0SN74LVC2G04DBVR DBV 6NFME 185.0185.0220.0SN74LVC2G04DBVT DBV 6HNT 200.0200.030.0SN74LVC2G04DCKR DCK 6HNC 205.0200.033.0SN74LVC2G04DCKT DCK 6HNT 200.0200.030.0SN74LVC2G04DRLR DRL 6HNT 201.0192.026.0SN74LVC2G04YZPRYZP6ASEK220.0220.034.012-May-200712-May-2007IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements, improvements,and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right,or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI. Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use anynon-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power /lpw Telephony /telephonyWirelessVideo&Imaging /videoWireless /wirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2007,Texas Instruments Incorporated。

sn74lvc2t45

FEATURESDCT OR DCU PACKAGE(TOP VIEW)12348765V CCA A1A2GNDV CCB B1B2DIRYZP PACKAGE (BOTTOM VIEW)A1GND B1DIR A2B2V CCAV CCBDESCRIPTION/ORDERING INFORMATION•Available in the Texas Instruments NanoFree™Package•Fully Configurable Dual-Rail Design Allows Each Port to Operate Over the Full 1.65-V to 5.5-V Power-Supply Range•V CC Isolation Feature –If Either V CC Input Is at GND,Both Ports Are in the High-Impedance State•DIR Input Circuit Referenced to V CCA•Low Power Consumption,10-µA Max I CC •±24-mA Output Drive at 3.3V•I off Supports Partial-Power-Down Mode Operation•Max Data Rates–420Mbps (3.3-V to 5-V Translation)–210Mbps (Translate to 3.3V)–140Mbps (Translate to 2.5V)–75Mbps (Translate to 1.8V)•Latch-Up Performance Exceeds 100mA Per JESD 78,Class II•ESD Protection Exceeds JESD 22–4000-V Human-Body Model (A114-A)–200-V Machine Model (A115-A)–1000-V Charged-Device Model (C101)This dual-bit noninverting bus transceiver uses two separate configurable power-supply rails.The A port is designed to track V CCA .V CCA accepts any supply voltage from 1.65V to 5.5V.The B port is designed to track V CCB .V CCB accepts any supply voltage from 1.65V to 5.5V.This allows for universal low-voltage bidirectional translation between any of the 1.8-V,2.5-V,3.3-V,and 5-V voltage nodes.ORDERING INFORMATIONT APACKAGE (1)ORDERABLE PART NUMBER TOP-SIDE MARKING (2)NanoFree –WCSP (DSBGA)Reel of 3000SN74LVC2T45YZPR ___TB_0.23-mm Large Bump –YZP (Pb-free)Reel of 3000SN74LVC2T45DCTR SSOP –DCT CT2___–40°C to 85°CReel of 250SN74LVC2T45DCTT Reel of 3000SN74LVC2T45DCUR VSSOP –DCUCT2_Reel of 250SN74LVC2T45DCUT(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI website at .(2)DCT:The actual top-side marking has three additional characters that designate the year,month,and assembly/test site.DCU:The actual top-side marking has one additional character that designates the assembly/test site.YZP:The actual top-side marking has three preceding characters to denote year,month,and sequence code,and one following character to designate the assembly/test site.Pin 1identifier indicates solder-bump composition (1=SnPb,•=Pb-free).Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.NanoFree is a trademark of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright ©2003–2007,Texas Instruments IncorporatedProducts conform to specifications per the terms of the Texas Instruments standard warranty.Production processing does not necessarily include testing of all parameters.DESCRIPTION/ORDERING INFORMATION (CONTINUED)B1DIRA1V CCA V CCBB2A2DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007The SN74LVC2T45is designed for asynchronous communication between two data buses.The logic levels of the direction-control (DIR)input activate either the B-port outputs or the A-port outputs.The device transmits data from the A bus to the B bus when the B-port outputs are activated,and from the B bus to the A bus when the A-port outputs are activated.The input circuitry on both A and B ports always is active and must have a logic HIGH or LOW level applied to prevent excess I CC and I CCZ .The SN74LVC2T45is designed so that the DIR input circuit is supplied by V CCA .This device is fully specified for partial-power-down applications using I off .The I off circuitry disables the outputs,preventing damaging current backflow through the device when it is powered down.The V CC isolation feature ensures that if either V CC input is at GND,both ports are in the high-impedance state.NanoFree™package technology is a major breakthrough in IC packaging concepts,using the die as the package.FUNCTION TABLE (1)(EACH TRANSCEIVER)INPUT OPERATION DIR L B data to A bus HA data toB bus(1)Input circuits of the data I/Os always are active.LOGIC DIAGRAM (POSITIVE LOGIC)2Submit Documentation FeedbackAbsolute Maximum Ratings(1)over operating free-air temperature range(unless otherwise noted)MIN MAX UNITV CCASupply voltage range–0.5 6.5VV CCBV I Input voltage range(2)–0.5 6.5VV O Voltage range applied to any output in the high-impedance or power-off state(2)–0.5 6.5VA port–0.5V CCA+0.5V O Voltage range applied to any output in the high or low state(2)(3)VB port–0.5V CCB+0.5I IK Input clamp current V I<0–50mAI OK Output clamp current V O<0–50mAI O Continuous output current±50mAContinuous current through V CC or GND±100mADCT package220θJA Package thermal impedance(4)DCU package227°C/WYZP package102T stg Storage temperature range–65150°C (1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.(3)The value of V CC is provided in the recommended operating conditions table.(4)The package thermal impedance is calculated in accordance with JESD51-7.3Submit Documentation FeedbackRecommended Operating Conditions (1)(2)(3)DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007V CCIV CCOMIN MAX UNIT V CCA 1.65 5.5Supply voltageVV CCB1.655.51.65V to 1.95VV CCI ×0.652.3V to 2.7V 1.7High-level V IHData inputs (4)Vinput voltage3V to 3.6V 24.5V to5.5V V CCI ×0.71.65V to 1.95VV CCI ×0.352.3V to 2.7V 0.7Low-level V ILData inputs (4)V input voltage3V to 3.6V 0.84.5V to5.5V V CCI ×0.31.65V to 1.95VV CCA ×0.652.3V to 2.7V 1.7High-level DIRV IHVinput voltage(referenced to V CCA )(5)3V to 3.6V 24.5V to5.5V V CCA ×0.71.65V to 1.95VV CCA ×0.352.3V to 2.7V 0.7Low-level DIRV ILV input voltage (referenced to V CCA )(5)3V to 3.6V 0.84.5V to5.5VV CCA ×0.3V I Input voltage 0 5.5V V OOutput voltageV CCOV 1.65V to 1.95V–42.3V to 2.7V –8I OHHigh-level output currentmA 3V to 3.6V –244.5V to 5.5V –321.65V to 1.95V42.3V to 2.7V 8I OLLow-level output currentmA 3V to 3.6V 244.5V to 5.5V321.65V to 1.95V202.3V to 2.7V 20Data inputsInput transition ∆t/∆v3V to 3.6V 10ns/V rise or fall rate4.5V to5.5V5Control input1.65V to 5.5V5T A Operating free-air temperature–4085°C (1)V CCI is the V CC associated with the input port.(2)V CCO is the V CC associated with the output port.(3)All unused data inputs of the device must be held at V CCI or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs ,literature number SCBA004.(4)For V CCI values not specified in the data sheet,V IH min =V CCI ×0.7V,V IL max =V CCI ×0.3V.(5)For V CCI values not specified in the data sheet,V IH min =V CCA ×0.7V,V IL max =V CCA ×0.3V.4Submit Documentation FeedbackElectrical Characteristics(1)(2)over recommended operating free-air temperature range(unless otherwise noted)(1)V CCO is the V CC associated with the output port.(2)V CCI is the V CC associated with the input port.5Submit Documentation FeedbackSwitching CharacteristicsSwitching CharacteristicsDUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007over recommended operating free-air temperature range,V CCA =1.8V ±0.15V (unless otherwise noted)(see Figure 1)V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =5V FROM TO ±0.15V ±0.2V ±0.3V ±0.5V PARAMETERUNIT(INPUT)(OUTPUT)MIN MAX MIN MAX MIN MAX MIN MAX t PLH 317.7 2.210.3 1.78.3 1.47.2A B ns t PHL 2.814.3 2.28.5 1.87.1 1.77t PLH 317.7 2.316 2.115.5 1.915.1B A ns t PHL 2.814.3 2.112.9212.6 1.812.2t PHZ 10.630.910.330.510.530.510.729.3DIR A ns t PLZ 7.319.77.519.67.519.5719.4t PHZ 1027.98.414.9 6.511.3 4.18.6DIR B ns t PLZ 6.519.57.212.6 4.39.7 2.17.1t PZH (1)37.228.625.222.2DIR A ns t PZL (1)42.227.823.920.8t PZH (1)37.429.927.826.6DIRBns t PZL (1)45.23937.636.3(1)The enable time is a calculated value,derived using the formula shown in the enable times section.over recommended operating free-air temperature range,V CCA =2.5V ±0.2V (unless otherwise noted)(see Figure 1)V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =5V FROM TO ±0.15V ±0.2V ±0.3V ±0.5V PARAMETERUNIT(INPUT)(OUTPUT)MIN MAX MIN MAX MIN MAX MIN MAX t PLH 2.316 1.58.5 1.3 6.4 1.1 5.1A B ns t PHL 2.112.9 1.47.5 1.3 5.40.9 4.6t PLH 2.210.3 1.58.5 1.4817.5B A ns t PHL 2.28.5 1.47.5 1.370.9 6.2t PHZ 6.617.17.116.8 6.816.8 5.216.5DIR A ns t PLZ 5.312.6 5.212.5 4.912.3 4.812.3t PHZ 10.727.98.113.9 5.810.5 3.57.6DIR B ns t PLZ 7.818.9 6.211.2 3.68.9 1.46.2t PZH (1)29.219.716.913.7DIR A ns t PZL (1)36.421.417.513.8t PZH (1)28.62118.717.4DIRBns t PZL (1)3024.322.221.1(1)The enable time is a calculated value,derived using the formula shown in the enable times section.6Submit Documentation FeedbackSwitching CharacteristicsSwitching Characteristicsover recommended operating free-air temperature range,V CCA =3.3V ±0.3V (unless otherwise noted)(see Figure 1)V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =5V FROM TO ±0.15V ±0.2V ±0.3V ±0.5V PARAMETERUNIT(INPUT)(OUTPUT)MIN MAX MIN MAXMIN MAX MIN MAX t PLH 2.115.5 1.480.7 5.60.7 4.4A B ns t PHL 212.6 1.370.850.74t PLH 1.78.3 1.3 6.40.7 5.80.6 5.4B A ns t PHL 1.87.1 1.3 5.40.850.7 4.5t PHZ 510.9 5.110.8510.8510.4DIR A ns t PLZ 3.48.4 3.78.4 3.98.1 3.37.8t PHZ 11.227.3813.7 5.810.4 2.97.4DIR B ns t PLZ 9.417.7 5.611.3 4.38.315.6t PZH (1)2617.714.111DIR A ns t PZL (1)34.419.115.411.9t PZH (1)23.916.413.912.2DIRBns t PZL (1)23.517.815.814.4(1)The enable time is a calculated value,derived using the formula shown in the enable times section.over recommended operating free-air temperature range,V CCA =5V ±0.5V (unless otherwise noted)(see Figure 1)V CCB =1.8V V CCB =2.5V V CCB =3.3V V CCB =5V FROM TO ±0.15V ±0.2V ±0.3V ±0.5V PARAMETERUNIT(INPUT)(OUTPUT)MIN MAX MIN MAX MIN MAX MIN MAX t PLH 1.915.117.50.6 5.40.5 3.9A B ns t PHL 1.812.20.9 6.20.7 4.50.5 3.5t PLH 1.47.21 5.10.7 4.40.5 3.9B A ns t PHL 1.770.9 4.60.740.5 3.5t PHZ 2.98.2 2.97.9 2.87.9 2.27.8DIR A ns t PLZ 1.4 6.9 1.3 6.70.7 6.70.7 6.6t PHZ 11.226.17.213.9 5.810.1 1.37.3DIR B ns t PLZ 8.416.951147.715.6t PZH (1)24.116.112.19.5DIR A ns t PZL (1)33.118.514.110.8t PZH (1)2214.212.110.5DIRBns t PZL (1)20.414.112.411.3(1)The enable time is a calculated value,derived using the formula shown in the enable times section.7Submit Documentation FeedbackOperating CharacteristicsDUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007T A =25°CV CCA =V CCA =V CCA =V CCA =TEST V CCB =1.8VV CCB =2.5VV CCB =3.3VV CCB =5VPARAMETER UNITCONDITIONS TYP TYP TYP TYP A-port input,3444C L =0pF,B-port output C pdA(1)f =10MHz,pFB-port input,t r =t f =1ns 18192021A-port outputA-port input,18192021C L =0pF,B-port output C pdB(1)f =10MHz,pFB-port input,t r =t f =1ns3444A-port output(1)Power dissipation capacitance per transceiver8Submit Documentation FeedbackPower-Up ConsiderationsA proper power-up sequence always should be followed to avoid excessive supply current,bus contention, oscillations,or other anomalies.To guard against such power-up problems,take the following precautions:1.Connect ground before any supply voltage is applied.2.Power up V CCA.3.V CCB can be ramped up along with or after V CCA.Table1.Typical Total Static Power Consumption(I CCA+I CCB)V CCAV CCB UNIT0V 1.8V 2.5V 3.3V5V0V0<1<1<1<11.8V<1<2<2<222.5V<1<2<2<2<2µA3.3V<1<2<2<2<25V<12<2<2<29Submit Documentation FeedbackTYPICAL CHARACTERISTICS5101520253035t P L H− n s C L − pF5101520253035t PH L − n sC L − pFTYPICAL PROPAGATION DELAY (B to A)vs LOADCAPACITANCE5101520253035t P L H − n sC L − pF5101520253035t P H L− n sC L − pFDUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007TYPICAL PROPAGATION DELAY (A to B)vs LOAD CAPACITANCET A =25°C,V CCA =1.8VT A =25°C,V CCA =1.8V10Submit Documentation FeedbackTYPICAL CHARACTERISTICS5t P L H − n s C L − pF5101520253035t P H L − n sC L − pFTYPICAL PROPAGATION DELAY (B to A)vs LOAD CAPACITANCEt P H L− n s C L − pF12345678910t P L H − n sC L − pFSN74LVC2T45DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007TYPICAL PROPAGATION DELAY (A to B)vs LOAD CAPACITANCET A =25°C,V CCA =2.5VT A =25°C,V CCA =2.5VTYPICAL CHARACTERISTICS5101520253035t P L H − n sC L − pFt P H L − n sC L − pFTYPICAL PROPAGATION DELAY (B to A)vs LOAD CAPACITANCEt P L H − n sC L − pFt P H L− n s C L − pF5101520253035SN74LVC2T45DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007TYPICAL PROPAGATION DELAY (A to B)vs LOAD CAPACITANCET A =25°C,V CCA =3.3VT A =25°C,V CCA =3.3VTYPICAL CHARACTERISTICSt P H L − n s C L − pFt P L H − n s C L − pFTYPICAL PROPAGATION DELAY (B to A)vs LOAD CAPACITANCEt P H L − n sC L − pFt P L H − n sC L − pF10SN74LVC2T45DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007TYPICAL PROPAGATION DELAY (A to B)vs LOAD CAPACITANCET A =25°C,V CCA =5VT A =25°C,V CCA =5VPARAMETER MEASUREMENT INFORMATIONV OH V OLLOAD CIRCUIT × V CCOOpenOutput Control (low-level enabling)Output Waveform 1S1 at 2 × V CCO (see Note B)Output Waveform 2S1 at GND (see Note B)0 V0 VV CCI0 VV CCAV CCOVOLTAGE WAVEFORMS PROPAGATION DELAY TIMESVOLTAGE WAVEFORMS PULSE DURATIONVOLTAGE WAVEFORMS ENABLE AND DISABLE TIMESInputt pd t PLZ /t PZL t PHZ /t PZHOpen 2 × V CCO GNDTEST S1NOTES: A.C L includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR v 10 MHz, Z O = 50 Ω, dv/dt ≥ 1 V/ns.D.The outputs are measured one at a time, with one transition per measurement.E.t PLZ and t PHZ are the same as t dis .F.t PZL and t PZH are the same as t en .G.t PLH and t PHL are the same as t pd .H.V CCI is the V CC associated with the input port.I.V CCO is the V CC associated with the output port.J.All parameters and waveforms are not applicable to all devices.1.8 V ± 0.15 V2.5 V ± 0.2 V3.3 V ± 0.3 V 5 V ± 0.5 V2 k Ω2 k Ω2 k Ω2 k ΩV CCO R L 0.15 V 0.15 V 0.3 V 0.3 VV TP C L 15 pF 15 pF 15 pF 15 pFSN74LVC2T45DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007Figure 1.Load Circuit and Voltage WaveformsAPPLICATION INFORMATIONSYSTEM-1SYSTEM-2SN74LVC2T45DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007The following shows an example of the SN74LVC2T45being used in a unidirectional logic level-shifting application.PIN NAME FUNCTION DESCRIPTION1V CCA V CC1SYSTEM-1supply voltage (1.65V to 5.5V)2A1OUT1Output level depends on V CC1voltage.3A2OUT2Output level depends on V CC1voltage.4GND GND Device GND5DIR DIR GND (low level)determines B-port to A-port direction.6B2IN2Input threshold value depends on V CC2voltage.7B1IN1Input threshold value depends on V CC2voltage.8V CCBV CC2SYSTEM-2supply voltage (1.65V to 5.5V)Figure 2.Unidirectional Logic Level-Shifting ApplicationAPPLICATION INFORMATIONSYSTEM-1SYSTEM-2Enable TimesSN74LVC2T45DUAL-BIT DUAL-SUPPLY BUS TRANSCEIVERWITH CONFIGURABLE VOLTAGE TRANSLATION AND 3-STATE OUTPUTSSCES516I–DECEMBER 2003–REVISED MARCH 2007Figure 3shows the SN74LVC2T45being used in a bidirectional logic level-shifting application.Since the SN74LVC2T45does not have an output-enable (OE)pin,the system designer should take precautions to avoid bus contention between SYSTEM-1and SYSTEM-2when changing directions.The following table shows data transmission from SYSTEM-1to SYSTEM-2and then from SYSTEM-2to SYSTEM-1.STATE DIR CTRLI/O-1I/O-2DESCRIPTION1H Out In SYSTEM-1data to SYSTEM-2SYSTEM-2is getting ready to send data to SYSTEM-1.I/O-1and I/O-2are disabled.The 2H Hi-Z Hi-Z bus-line state depends on pullup or pulldown.(1)DIR bit is flipped.I/O-1and I/O-2still are disabled.The bus-line state depends on pullup or 3L Hi-Z Hi-Z pulldown.(1)4LInOutSYSTEM-2data to SYSTEM-1(1)SYSTEM-1and SYSTEM-2must use the same conditions,i.e.,both pullup or both pulldown.Figure 3.Bidirectional Logic Level-Shifting ApplicationCalculate the enable times for the SN74LVC2T45using the following formulas:•t PZH (DIR to A)=t PLZ (DIR to B)+t PLH (B to A)•t PZL (DIR to A)=t PHZ (DIR to B)+t PHL (B to A)•t PZH (DIR to B)=t PLZ (DIR to A)+t PLH (A to B)•t PZL (DIR to B)=t PHZ (DIR to A)+t PHL (A to B)In a bidirectional application,these enable times provide the maximum delay from the time the DIR bit is switched until an output is expected.For example,if the SN74LVC2T45initially is transmitting from A to B,then the DIR bit is switched;the B port of the device must be disabled before presenting it with an input.After the B port has been disabled,an input signal applied to it appears on the corresponding A port after the specified propagation delay.PACKAGING INFORMATIONOrderable Device Status (1)Package Type PackageDrawing Pins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)Samples(Requires Login)SN74LVC2T45DCTR ACTIVE SM8DCT83000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Request Free SamplesSN74LVC2T45DCTRE4ACTIVE SM8DCT83000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Request Free SamplesSN74LVC2T45DCTRG4ACTIVE SM8DCT83000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Request Free SamplesSN74LVC2T45DCTT ACTIVE SM8DCT8250Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Contact TI Distributoror Sales OfficeSN74LVC2T45DCTTE4ACTIVE SM8DCT8250Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Contact TI Distributoror Sales OfficeSN74LVC2T45DCTTG4ACTIVE SM8DCT8250Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Contact TI Distributoror Sales OfficeSN74LVC2T45DCUR ACTIVE US8DCU83000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Request Free SamplesSN74LVC2T45DCURE4ACTIVE US8DCU83000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Request Free SamplesSN74LVC2T45DCURG4ACTIVE US8DCU83000Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Request Free SamplesSN74LVC2T45DCUT ACTIVE US8DCU8250Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Purchase SamplesSN74LVC2T45DCUTE4ACTIVE US8DCU8250Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Purchase SamplesSN74LVC2T45DCUTG4ACTIVE US8DCU8250Green (RoHS& no Sb/Br)CU NIPDAU Level-1-260C-UNLIM Purchase SamplesSN74LVC2T45YZPR ACTIVE DSBGA YZP83000Green (RoHS& no Sb/Br)SNAGCU Level-1-260C-UNLIM Request Free Samples(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.Addendum-Page 1(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.OTHER QUALIFIED VERSIONS OF SN74LVC2T45 :•Enhanced Product: SN74LVC2T45-EPNOTE: Qualified Version Definitions:•Enhanced Product - Supports Defense, Aerospace and Medical ApplicationsAddendum-Page 2TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74LVC2T45YZPR DSBGAYZP83000178.09.21.022.020.634.08.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm)SN74LVC2T45YZPR DSBGA YZP83000220.0220.035.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

74LVC2G53资料

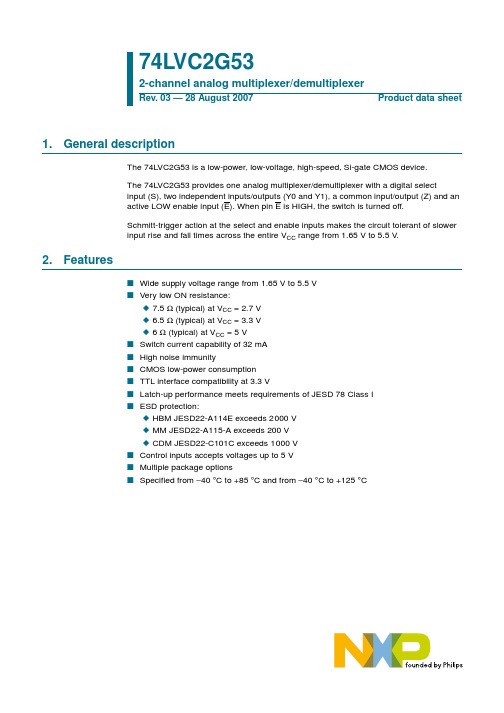

74LVC2G532-channel analog multiplexer/demultiplexerRev. 03 — 28 August 2007Product data sheet1.General descriptionThe 74LVC2G53 is a low-power, low-voltage, high-speed, Si-gate CMOS device.The 74LVC2G53 provides one analog multiplexer/demultiplexer with a digital selectinput(S),two independent inputs/outputs(Y0and Y1),a common input/output(Z)and anactive LOW enable input (E). When pin E is HIGH, the switch is turned off.Schmitt-trigger action at the select and enable inputs makes the circuit tolerant of slowerinput rise and fall times across the entire V CC range from 1.65 V to 5.5 V.2.Featuress Wide supply voltage range from 1.65V to 5.5Vs Very low ON resistance:x7.5Ω (typical) at V CC=2.7Vx6.5Ω (typical) at V CC=3.3Vx6Ω (typical) at V CC=5Vs Switch current capability of 32 mAs High noise immunitys CMOS low-power consumptions TTL interface compatibility at 3.3 Vs Latch-up performance meets requirements of JESD 78 Class Is ESD protection:x HBM JESD22-A114E exceeds 2000Vx MM JESD22-A115-A exceeds 200Vx CDM JESD22-C101C exceeds 1000Vs Control inputs accepts voltages up to 5 Vs Multiple package optionss Specified from−40°C to +85°C and from−40°C to +125°C3.Ordering information4.Marking5.Functional diagramTable 1.Ordering informationType numberPackageTemperature range NameDescriptionVersion 74LVC2G53DP −40°C to +125°C TSSOP8plastic thin shrink small outline package; 8 leads;body width 3 mm; lead length 0.5 mmSOT505-274LVC2G53DC −40°C to +125°C VSSOP8plastic very thin shrink small outline package; 8 leads;body width 2.3 mm SOT765-174LVC2G53GT −40°C to +125°C XSON8plastic extremely thin small outline package; no leads;8terminals; body 1× 1.95× 0.5 mmSOT833-174LVC2G53GM −40°C to +125°CXQFN8plastic extremely thin quad flat package; no leads;8terminals; body 1.6×1.6×0.5mmSOT902-1Table 2.MarkingType number Marking code 74LVC2G53DC V5374LVC2G53DP V5374LVC2G53GT V5374LVC2G53GMV53Fig 1.Logic symbol001aad386S Z EY0Y167251Fig 2.Logic diagram001aad387ZY0SY1E6.Pinning information6.1Pinning6.2Pin descriptionFig 3.Pin configuration SOT505-2 (TSSOP8) andSOT765-1 (VSSOP8)Fig 4.Pin configuration SOT833-1 (XSON8)74LVC2G53Z V CC E Y0GND Y1GNDS001aae7981234658774LVC2G53Y1Y0V CCSGNDE ZGND001aae80036271845Transparent top viewFig 5.Pin configuration SOT902-1 (XQFN8)001aag724EY1ZV C C GNDY0G N DS Transparent top view36415872terminal 1index area74LVC2G53Table 3.Pin description Symbol PinDescriptionSOT505-2, SOT765-1 and SOT833-1SOT902-1Z 17common output or input E 26enable input (active LOW)GND 35ground (0V)GND 44ground (0V)S53select inputTable 3.Pin description …continuedSymbol Pin DescriptionSOT505-2, SOT765-1 and SOT833-1SOT902-1Y162independent input or outputY071independent input or outputV CC88supply voltage7.Functional descriptionTable 4.Function table[1]Input Channel onS EL L Y0 to Z or Z to Y0H L Y1 to Z or Z to Y1X H Z (switch off)[1]H=HIGH voltage level;L=LOW voltage level;X=don’t care;Z=high-impedance OFF-state.8.Limiting valuesTable 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V). Symbol Parameter Conditions Min Max Unit V CC supply voltage−0.5+6.5VV I input voltage[1]−0.5+6.5VI IK input clamping current V I<−0.5V or V I>V CC + 0.5 V−50-mAI SK switch clamping current V I<−0.5V or V I>V CC + 0.5 V-±50mAV SW switch voltage enable and disable mode[2]−0.5V CC + 0.5VI SW switch current V SW>−0.5V or V SW< V CC + 0.5 V-±50mAI CC supply current-100mAI GND ground current−100-mAT stg storage temperature−65+150°CP tot total power dissipation T amb=−40°C to+125°C[3]-250mW[1]The minimum input voltage rating may be exceeded if the input current rating is observed.[2]The minimum and maximum switch voltage ratings may be exceeded if the switch clamping current rating is observed.[3]For the TSSOP8 and VSSOP8 packages: above 110°C the value of P tot derates linearly with 8mW/K.For XSON8 and XQFN8 packages: above 45°C the value of P tot derates linearly with 2.4mW/K.9.Recommended operating conditions[1]To avoid sinking GND current from terminal Z when switch current flows in terminal Yn, the voltage drop across the bidirectional switch must not exceed 0.4V .If the switch current flows into terminal Z,no GND current will flow from terminal Yn.In this case,there is no limit for the voltage drop across the switch.[2]Applies to control signal levels.10.Static characteristicsTable 6.Recommended operating conditions Symbol Parameter Conditions Min Typ Max Unit V CC supply voltage 1.65- 5.5V V I input voltage 0- 5.5V V SW switch voltage enable and disable mode[1]0-V CC V T amb ambient temperature−40-+125°C ∆t/∆Vinput transition rise and fall rateV CC =1.65V to 2.7V [2]--20ns/V V CC =2.7V to 5.5V[2]--10ns/VTable 7.Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground 0V).Symbol Parameter Conditions−40°C to +85°C −40°C to +125°C Min Typ [1]Max Min Max Unit V IHHIGH-level input voltageV CC =1.65V to 1.95V 0.65V CC--0.65V CC-V V CC =2.3V to 2.7V 1.7-- 1.7-V V CC =3V to 3.6V 2.0-- 2.0-V V CC =4.5V to 5.5V0.7V CC--0.7V CC-V V ILLOW-level input voltageV CC =1.65V to 1.95V --0.35V CC-0.35V CC VV CC =2.3V to 2.7V --0.7-0.7V V CC =3V to 3.6V --0.8-0.8V V CC =4.5V to 5.5V--0.3V CC 0.3V CC V I Iinput leakage current pin S and pin E;V I =5.5V or GND;V CC =0V to 5.5V[2]-±0.1±2-±10µAI S(OFF)OFF-state leakage current V I = V IH or V IL ; V CC =5.5V;see Figure 6[2]-±0.1±5-±20µAI S(ON)ON-state leakage currentV I = V IH or V IL ; V CC =5.5V;see Figure 7[2]-±0.1±5-±20µAI CCsupply current V I =5.5 V or GND;V SW =GND or V CC ; I O =0A;V CC =1.65 V to 5.5V [2]-0.110-40µA∆I CCadditional supply current pin S and pin E;V I =V CC −0.6V;I O =0A;V SW =GND or V CC ;V CC =5.5V[2]-5500-5000µA[1]Typical values are measured at T amb =25°C.[2]These typical values are measured at V CC =3.3V10.1Test circuitsC I inputcapacitance - 2.5---pF C S(OFF)OFF-state capacitance - 6.0---pF C S(ON)ON-state capacitance-18---pFTable 7.Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground 0V).Symbol Parameter Conditions−40°C to +85°C −40°C to +125°C MinTyp [1]Max Min Max Unit V I =V CC or GND; V O =GND or V CC .Fig 6.Test circuit for measuring OFF-state leakage currentV OI S001aad390S ZEY0Y1V CCGNDswitch switch1122V ILV IH S V IHV IH E V IV IL or V IHV IHV I =V CC or GND and V O =open circuit.Fig 7.Test circuit for measuring ON-state leakage currentI S001aad391S ZEY0Y1V CCGNDV IV IL or V IHV ILswitch 12V ILV IH S V ILV IL E V Oswitch1210.2ON resistance[1]Typical values are measured at T amb =25°C and nominal V CC .[2]Flatness is defined as the difference between the maximum and minimum value of ON resistance measured at identical V CC and temperature.Table 8.ON resistanceAt recommended operating conditions; voltages are referenced to GND (ground 0V); for graphs see Figure 9 to Figure 14.Symbol ParameterConditions−40°C to +85°C −40°C to +125°C Unit MinTyp [1]Max Min Max R ON(peak)ON resistance (peak)V I =GND to V CC ; see Figure 8I SW =4mA;V CC =1.65V to 1.95V-34.0130-195ΩI SW =8mA; V CC =2.3V to 2.7V -12.030-45ΩI SW =12mA; V CC =2.7V -10.425-38ΩI SW =24mA; V CC =3V to 3.6V -7.820-30ΩI SW =32mA;V CC =4.5V to 5.5V- 6.215-23ΩR ON(rail)ON resistance (rail)V I =GND; see Figure 8I SW =4mA;V CC =1.65V to 1.95V-8.218-27ΩI SW =8mA; V CC =2.3V to 2.7V -7.116-24ΩI SW =12mA; V CC =2.7V - 6.914-21ΩI SW =24mA; V CC =3V to 3.6V - 6.512-18ΩI SW =32mA;V CC =4.5V to 5.5V - 5.810-15ΩV I =V CC ; see Figure 8I SW =4mA;V CC =1.65V to 1.95V-10.430-45ΩI SW =8mA; V CC =2.3V to 2.7V -7.620-30ΩI SW =12mA; V CC =2.7V -7.018-27ΩI SW =24mA; V CC =3V to 3.6V - 6.115-23ΩI SW =32mA;V CC =4.5V to 5.5V- 4.910-15ΩR ON(flat)ON resistance (flatness)V I =GND to V CC[2]I SW =4mA;V CC =1.65V to 1.95V-26.0---ΩI SW =8mA; V CC =2.3V to 2.7V - 5.0---ΩI SW =12mA; V CC =2.7V - 3.5---ΩI SW =24mA; V CC =3V to 3.6V - 2.0---ΩI SW =32mA;V CC =4.5V to 5.5V-1.5---Ω10.3ON resistance test circuit and graphsR ON = V SW / I SW .Fig 8.Test circuit for measuring ON resistanceI SWV SW001aad392S ZEY0Y1V CCGNDswitch switch1122V IHV IL S V ILV IL E V IV IL or V IHV IL(1)V CC = 1.8 V .(2)V CC = 2.5 V .(3)V CC = 2.7 V .(4)V CC = 3.3 V .(5)V CC = 5.0 V .Fig 9.Typical ON resistance as a function of input voltage; T amb = 25°CV I (V)054231mna67320103040R ON (Ω)(1)(2)(3)(4)(5)(1)T amb =125°C.(2)T amb =85°C.(3)T amb =25°C.(4)T amb =−40°C.(1)T amb =125°C.(2)T amb =85°C.(3)T amb =25°C.(4)T amb =−40°C.Fig 10.ON resistance as a function of input voltage;V CC =1.8V Fig 11.ON resistance as a function of input voltage;V CC =2.5VV I (V)0 2.01.60.8 1.20.4001aaa7122535154555R ON (Ω)5(4)(3)(2)(1)V I (V)0 2.52.01.0 1.50.5001aaa70891171315R ON (Ω)5(1)(2)(3)(4)(1)T amb =125°C.(2)T amb =85°C.(3)T amb =25°C.(4)T amb =−40°C.(1)T amb =125°C.(2)T amb =85°C.(3)T amb =25°C.(4)T amb =−40°C.Fig 12.ON resistance as a function of input voltage;V CC =2.7V Fig 13.ON resistance as a function of input voltage;V CC =3.3V001aaa709V I (V)0 3.02.01.02.51.50.5971113R ON (Ω)5(1)(2)(3)(4)V I (V)04312001aaa7106810R ON (Ω)4(1)(2)(3)(4)11.Dynamic characteristics(1)T amb =125°C.(2)T amb =85°C.(3)T amb =25°C.(4)T amb =−40°C.Fig 14.ON resistance as a function of input voltage; V CC =5.0VV I (V)054231001aaa7115467R ON (Ω)3(2)(4)(1)(3)Table 9.Dynamic characteristicsAt recommended operating conditions; voltages are referenced to GND (ground =0V); for load circuit see Figure 17.Symbol Parameter Conditions−40°C to +85°C −40°C to +125°C Unit MinTyp [1]Max Min Max t pdpropagation delay Z to Yn or Yn to Z; see Figure 15[2][3]V CC = 1.65 V to 1.95 V --2- 2.5ns V CC = 2.3 V to 2.7 V -- 1.2- 1.5ns V CC = 2.7 V -- 1.0- 1.25ns V CC = 3.0 V to 3.6 V --0.8- 1.0ns V CC = 4.5 V to 5.5 V--0.6-0.8nsTable 9.Dynamic characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground=0V); for load circuit see Figure17. Symbol Parameter Conditions−40°C to+85°C−40°C to+125°C UnitMin Typ[1]Max Min Maxt en enable time S to Z or Yn; see Figure16[4]V CC = 1.65 V to 1.95 V 2.6 6.710.3 2.612.9nsV CC = 2.3 V to 2.7 V 1.9 4.1 6.4 1.98.0nsV CC = 2.7 V 1.9 4.0 5.5 1.87.0nsV CC = 3.0 V to 3.6 V 1.8 3.4 5.0 1.8 6.3nsV CC = 4.5 V to 5.5 V 1.3 2.6 3.8 1.3 4.8nsE to Z or Yn; see Figure16[4]V CC = 1.65 V to 1.95 V 1.9 4.07.3 1.99.2nsV CC = 2.3 V to 2.7 V 1.4 2.5 4.4 1.4 5.5nsV CC = 2.7 V 1.1 2.6 3.9 1.1 4.9nsV CC = 3.0 V to 3.6 V 1.2 2.2 3.8 1.2 4.8nsV CC = 4.5 V to 5.5 V 1.0 1.7 2.6 1.0 3.3ns t dis disable time S to Z or Yn; see Figure16[5]V CC = 1.65 V to 1.95 V 2.1 6.810.0 2.112.5nsV CC = 2.3 V to 2.7 V 1.4 3.7 6.1 1.47.7nsV CC = 2.7 V 1.4 4.9 6.2 1.47.8nsV CC = 3.0 V to 3.6 V 1.1 4.0 5.4 1.1 6.8nsV CC = 4.5 V to 5.5 V 1.0 2.9 3.8 1.0 4.8nsE to Z or Yn; see Figure16[5]V CC = 1.65 V to 1.95 V 2.3 5.68.6 2.311.0nsV CC = 2.3 V to 2.7 V 1.2 3.2 4.8 1.2 6.0nsV CC = 2.7 V 1.4 4.0 5.2 1.4 6.5nsV CC = 3.0 V to 3.6 V 2.0 3.7 5.0 2.0 6.3nsV CC = 4.5 V to 5.5 V 1.3 2.9 3.8 1.3 4.8ns[1]Typical values are measured at T amb=25°C and nominal V CC.[2]t pd is the same as t PLH and t PHL.[3]propagation delay is the calculated RC time constant of the typical ON resistance of the switch and the specified capacitance whendriven by an ideal voltage source (zero output impedance).[4]t en is the same as t PZH and t PZL[5]t dis is the same as t PLZ and t PHZ11.1Waveforms and test circuitsMeasurement points are given in Table 10.Logic levels: V OL and V OH are typical output voltage levels that occur with the output load.Fig 15.Input (Yn or Z) to output (Z or Yn) propagation delayst PLHt PHLV M V M V MV MGNDV IV OHV OLYn or Z inputZ or Yn output001aac361Measurement points are given in Table 10.Logic levels: V OL and V OH are typical output voltage levels that occur with the output load.Fig 16.Enable and disable times V M V IGNDV CCV OL V OHGNDS, E inputoutputLOW to OFF OFF to LOWoutputHIGH to OFF OFF to HIGHV M001aad393V Mt PZLt PHZt PZHV XV Yswitch disabledswitch enabledswitch enabledZ, YnZ, Ynt PLZTable 10.Measurement pointsSupply voltageInput Output V CCV M V M V XV Y1.65V to2.7V 0.5V CC 0.5V CC V OL +0.15V V OH −0.15V 2.7V to 5.5V0.5V CC0.5V CCV OL +0.3VV OH −0.3V11.2Additional dynamic characteristicsTest data is given in T able 11.Definitions test circuit:R T = Termination resistance (should be equal to output impedance Z o of the pulse generator).C L = Load capacitance (including jig and probe capacitance).R L = Load resistance.V EXT = External voltage for measuring switching times.Fig 17.Load circuit for switching times V EXTV CCV IV Omna616DUTC L R TR LR LGTable 11.Test dataSupply voltageInput Load V EXT V CCV I t r , t f C L R L t PLH , t PHL t PZH , t PHZ t PZL , t PLZ 1.65V to 1.95V V CC ≤2.0ns 30pF 1k Ωopen GND 2V CC 2.3V to 2.7V V CC ≤2.0ns 30pF 500Ωopen GND 2V CC 2.7V V CC ≤2.5ns 50pF 500Ωopen GND 2V CC 3V to 3.6V V CC ≤2.5ns 50pF 500Ωopen GND 2V CC 4.5V to 5.5VV CC≤2.5ns50pF500ΩopenGND2V CCTable 12.Additional dynamic characteristicsAt recommended operating conditions; voltages are referenced to GND (ground =0V); T amb =25°C.Symbol ParameterConditionsMinTypMaxUnitTHDtotal harmonic distortionf i =600 Hz to 20kHz; R L =600Ω;C L =50pF; V I =0.5V (p-p);see Figure 18V CC =1.65V -0.260-%V CC =2.3V -0.078-%V CC =3.0V -0.078-%V CC =4.5V-0.078-%f (-3dB)−3 dB frequency response R L =50Ω; C L =5pF; see Figure 19V CC =1.65V -200-MHz V CC =2.3V -300-MHz V CC =3.0V -300-MHz V CC =4.5V-300-MHz11.3Test circuitsαisoisolation (OFF-state)R L =50Ω; C L =5pF; f i =10MHz;see Figure 20V CC =1.65V -−42-dB V CC =2.3V -−42-dB V CC =3.0V -−40-dB V CC =4.5V-−40-dBQ injcharge injectionC L =0.1 nF; V gen =0V; R gen =0Ω;f i =1MHz; R L =1M Ω; see Figure 21V CC =1.8V - 3.3-pC V CC =2.5V - 4.1-pC V CC =3.3V - 5.0-pC V CC =4.5V - 6.4-pC V CC =5.5V-7.5-pCTable 12.Additional dynamic characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground =0V); T amb =25°C.Symbol ParameterConditionsMinTypMaxUnitFig 18.Test circuit for measuring total harmonic distortionD001aad394600 Ω10 µF0.1 µFSZY0Y1V CC0.5V CCGNDC LR Lswitch switch1122V IHV IL S V ILV IL E f iV IL or V IHEV ILAdjust f i voltage to obtain 0dBm level at output. Increase f i frequency until dB meter reads −3dB.Fig 19.Test circuit for measuring the frequency response when switch is in ON-statedB001aad39550 Ω0.1 µFSZEY0Y1V CC 0.5V CCGNDC LR Lswitch switch1122V IHV IL S V ILV IL E f iV IL or V IHV ILAdjust f i voltage to obtain 0dBm level at input.Fig 20.Test circuit for measuring isolation (OFF-state)dB001aad39650 ΩR L0.1 µFSZEY0Y1V CC0.5V CC0.5V CCGNDC LR Lswitchswitch1122V ILV IH S V IHV IH E f iV IL or V IHV IHa.T est circuitb.Input and output pulse definitionsQ inj =∆V O ×C L .∆V O = output voltage variation.R gen = generator resistance.V gen = generator voltage.Fig 21.Test circuit for measuring charge injection001aad398S ZY0Y1R L C LV CC GNDR genV genswitch12V I V O EV IL G001aac478∆V Ooffon off logicinputV O(S)12.Package outlineFig 22.Package outline SOT505-2 (TSSOP8)UNIT A 1A max.A 2A 3b p L H E L p w y v c e D (1)E (1)Z (1)θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITAmm0.150.000.950.750.380.220.180.083.12.93.12.90.654.13.90.700.358°0°0.130.10.20.5DIMENSIONS (mm are the original dimensions)Note1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.0.470.33SOT505-2- - -02-01-16w Mb pD Ze0.251485θA 2A 1L p (A 3)detail XALH EE cv M AXAy2.5 5 mm0scaleTSSOP8: plastic thin shrink small outline package; 8 leads; body width 3 mm; lead length 0.5 mmSOT505-21.1pin 1 indexFig 23.Package outline SOT765-1 (VSSOP8)UNIT A 1A max.A 2A 3b p L H E L p w y v c e D (1)E (2)Z (1)θ REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITAmm0.150.000.850.600.270.170.230.082.11.92.42.20.53.23.00.40.18°0°0.130.10.20.4DIMENSIONS (mm are the original dimensions)Notes1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.0.400.15Q 0.210.19SOT765-1MO-18702-06-07w Mb pD Ze0.121485θA 2A 1QL p(A 3)detail XALH EE cv M AXAy2.5 5 mm0scaleVSSOP8: plastic very thin shrink small outline package; 8 leads; body width 2.3 mm SOT765-11pin 1 indexFig 24.Package outline SOT833-1 (XSON8)terminal 1index areaREFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IEC JEDEC JEITA SOT833-1- - -MO-252- - -SOT833-104-07-2204-11-09DIMENSIONS (mm are the original dimensions)XSON8: plastic extremely thin small outline package; no leads; 8 terminals; body 1 x 1.95 x 0.5 mm DEe 1eA 1b LL 1e 1e 11 2 mmscaleNotes1. Including plating thickness.2. Can be visible in some manufacturing processes.UNIT mm0.250.172.01.90.350.27A 1max b E 1.050.95D e e 1L 0.400.32L 10.50.6A (1)max 0.50.04182736458×(2)4×(2)AFig 25.Package outline SOT902-1 (XQFN8)REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IEC JEDEC JEITA SOT902-1MO-255- - -- - -SOT902-105-11-1605-11-25UNIT A max mm0.5A 10.250.150.050.001.651.550.350.250.150.05DIMENSIONS (mm are the original dimensions)XQFN8: plastic extremely thin quad flat package; no leads; 8 terminals; body 1.6 x 1.6 x 0.5 mm b D L e 11.651.55e E L 1v 0.10.550.5w 0.05y 0.050.05y 101 2 mmscaleXCyCy 1terminal 1index areaterminal 1index areaB ADE detail XAA 1b8765e 1e 1eeA CB ∅ v M C∅ w M 4123LL 1metal area not for soldering13.Abbreviations14.Revision historyTable 13.AbbreviationsAcronym DescriptionCMOS Complementary Metal Oxide Semiconductor TTL T ransistor-Transistor Logic HBM Human Body Model ESD ElectroStatic Discharge MM Machine Model CDM Charged Device Model DUTDevice Under TestTable 14.Revision historyDocument ID Release date Data sheet status Change notice Supersedes 74LVC2G53_320070828Product data sheet-74LVC2G53_2Modifications:•The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors.•Legal texts have been adapted to the new company name where appropriate.•Added type number 74LVC2G53GM (XQFN8/SOT902-1 package).•Section 2 “Features”:Added: Switch handling capability of 32 mA.•Section 10 “Static characteristics”:Changed: Conditions for input leakage and supply current.•Section 11.2 “Additional dynamic characteristics”:Removed: Crosstalk between switches removed from additional characteristics table.Changed: T ypical values of the charge injection.74LVC2G53_220060331Product data sheet -74LVC2G53_174LVC2G53_120060110Product data sheet--74LVC2G53_3© NXP B.V . 2007. All rights reserved.Product data sheet Rev. 03 — 28 August 200721 of 2215.Legal information15.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s)described in this document may have changed since this document was published and may differ in case of multiple devices.The latest product status information is available on the Internet at URL .15.2DefinitionsDraft —The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet —A short data sheet is an extract from a full data sheet with the same product type number(s)and title.A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.15.3DisclaimersGeneral —Information in this document is believed to be accurate andreliable.However,NXP Semiconductors does not give any representations or warranties,expressed or implied,as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes —NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice.This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use —NXP Semiconductors products are not designed,authorized or warranted to be suitable for use in medical, military, aircraft,space or life support equipment, nor in applications where failure ormalfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage.NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications —Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values —Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134)may cause permanent damage to the device.Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in theCharacteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale —NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale,as published at /profile/terms , including those pertaining to warranty,intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license —Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant,conveyance or implication of any license under any copyrights,patents or other industrial or intellectual property rights.15.4TrademarksNotice:All referenced brands,product names,service names and trademarks are the property of their respective owners.16.Contact informationFor additional information, please visit:For sales office addresses, send an email to:salesaddresses@Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development.Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheetProductionThis document contains the product specification.17.Contents1General description. . . . . . . . . . . . . . . . . . . . . . 12Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Ordering information. . . . . . . . . . . . . . . . . . . . . 24Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Functional diagram . . . . . . . . . . . . . . . . . . . . . . 26Pinning information. . . . . . . . . . . . . . . . . . . . . . 36.1Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 37Functional description . . . . . . . . . . . . . . . . . . . 48Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 49Recommended operating conditions. . . . . . . . 510Static characteristics. . . . . . . . . . . . . . . . . . . . . 510.1T est circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . . 610.2ON resistance. . . . . . . . . . . . . . . . . . . . . . . . . . 710.3ON resistance test circuit and graphs. . . . . . . . 811Dynamic characteristics . . . . . . . . . . . . . . . . . 1011.1Waveforms and test circuits . . . . . . . . . . . . . . 1211.2Additional dynamic characteristics . . . . . . . . . 1311.3T est circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . 1412Package outline . . . . . . . . . . . . . . . . . . . . . . . . 1613Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 2014Revision history. . . . . . . . . . . . . . . . . . . . . . . . 2015Legal information. . . . . . . . . . . . . . . . . . . . . . . 2115.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . 2115.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2115.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 2115.4T rademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 2116Contact information. . . . . . . . . . . . . . . . . . . . . 2117Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2007.All rights reserved.For more information, please visit: For sales office addresses, please send an email to: salesaddresses@Date of release: 28 August 2007Document identifier: 74LVC2G53_3。

74LVC1G32GF中文资料

For XSON6 packages: above 45 °C the value of Ptot derates linearly with 2.4 mW/K.

9. Recommended operating conditions

Table 6. Symbol VCC VI VO

Tamb ∆t/∆V

SOT353-1

SOT753 SOT886

SOT891

Table 2. Marking Type number 74LVC1G32GW 74LVC1G32GV 74LVC1G32GM 74LVC1G32GF

5. Functional diagram

Marking code VG V32 VG VG

1B 2A

元器件交易网

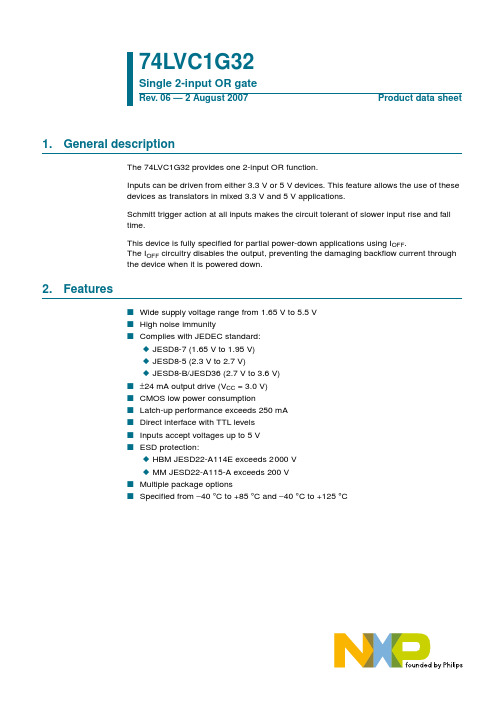

74LVC1G32

Single 2-input OR gate

Rev. 06 — 2 August 2007

Product data sheet

1. General description

The 74LVC1G32 provides one 2-input OR function.

plastic surface-mounted package; 5 leads

plastic extremely thin small outline package; no leads; 6 terminals; body 1 × 1.45 × 0.5 mm

SN74LVC2G04DBVTE4中文资料