verilog顶层模块调用实例

verilog中function用法

verilog中function用法

在Verilog中,`function`是一种用于定义可重用代码块的语法结构。

`function`可以在模块、组合逻辑或时序逻辑中使用,以提供一种更加模块化和可读性更好的代码实现方式。

下面是一个简单的`function`示例,用于计算两个整数的和:

```verilog

function int add(int a, int b);

return a + b;

endfunction

```

在上面的代码中,`function`关键字用于定义一个名为`add`的函数,该函数接受两个整数参数`a`和`b`,并返回它们的和。

在函数体中,我们使用`return`语句将计算结果返回给调用者。

一旦定义了`add`函数,我们就可以在任何地方调用它,如下所示:

```verilog

module top;

int a = 10, b = 20, c;

initial begin

c = add(a, b); // 调用add函数,并将结果赋值给c

$display("The sum of %d and %d is %d", a, b, c);

end

endmodule

```

在上面的代码中,我们在模块的初始化部分调用`add`函数,并将结果赋值给变量`c`。

最后,我们使用`$display`语句将结果打印到控制台上。

除了上述示例中的基本用法外,`function`还可以用于实现更复杂的逻辑,例如递归函数、函数指针等。

在实际应用中,使用`function`可以大大提高代码的可读性和可维护性。

verilog中function用法_verilog中的function用法与例子

verilog中function⽤法_verilog中的function⽤法与例⼦函数的功能和任务的功能类似,但⼆者还存在很⼤的不同。

在 Verilog HDL 语法中也存在函数的定义和调⽤。

1.函数的定义函数通过关键词 function 和 endfunction 定义,不允许输出端⼝声明(包括输出和双向端⼝) ,但可以有多个输⼊端⼝。

函数定义的语法如下:function [range] function_id;input_declarationother_declarationsprocedural_statementendfunction其中,function 语句标志着函数定义结构的开始;[range]参数指定函数返回值的类型或位宽,是⼀个可选项,若没有指定,默认缺省值为 1 ⽐特的寄存器数据;function_id 为所定义函数的名称,对函数的调⽤也是通过函数名完成的,并在函数结构体内部代表⼀个内部变量,函数调⽤的返回值就是通过函数名变量传递给调⽤语句;input_declaration ⽤于对寒暑各个输⼊端⼝的位宽和类型进⾏说明,在函数定义中⾄少要有⼀个输⼊端⼝;endfunction为函数结构体结束标志。

下⾯给出⼀个函数定义实例。

定义函数实例。

function AND;//定义输⼊变量input A, B;//定义函数体beginAND = A && B;endendfunction函数定义在函数内部会隐式定义⼀个寄存器变量, 该寄存器变量和函数同名并且位宽也⼀致。

函数通过在函数定义中对该寄存器的显式赋值来返回函数计算结果。

此外,还有下列⼏点需要注意:(1)函数定义只能在模块中完成,不能出现在过程块中;(2)函数⾄少要有⼀个输⼊端⼝;不能包含输出端⼝和双向端⼝;(3) 在函数结构中, 不能使⽤任何形式的时间控制语句 (#、 wait 等) , 也不能使⽤ disable中⽌语句;(4)函数定义结构体中不能出现过程块语句(always 语句)(这样的话,函数就不能完成时序逻辑,只能做组合逻辑,是这样吗?) ;(5)函数内部可以调⽤函数,但不能调⽤任务。

verilog 传递参数

verilog 传递参数在Verilog中,模块之间传递参数通常通过模块的端口进行。

Verilog中的模块可以有输入端口(input)、输出端口(output)和双向端口(inout)。

通过这些端口,可以在模块之间传递参数和数据。

首先,你需要在模块的定义中声明端口,并指定它们的方向和数据类型。

例如:verilog.module MyModule(。

input wire clk, // 输入时钟信号。

input wire [7:0] data_in, // 8位输入数据。

output reg [7:0] data_out // 8位输出数据。

);// 模块逻辑。

endmodule.在该例子中,MyModule模块有一个输入时钟信号(clk)、一个8位的输入数据(data_in)和一个8位的输出数据(data_out)。

当你实例化这个模块并连接到其他模块时,你需要将参数传递给端口。

例如:verilog.module MyTopModule(。

input wire clk,。

input wire [7:0] input_data,。

output reg [7:0] output_data.);MyModule inst1(。

.clk(clk), // 将顶层模块的时钟信号连接到子模块的时钟信号。

.data_in(input_data), // 将输入数据连接到子模块的输入数据。

.data_out(output_data) // 将子模块的输出数据连接到顶层模块的输出数据。

);// 其他逻辑。

endmodule.在这个例子中,MyTopModule模块实例化了MyModule模块,并通过连接端口将参数传递给子模块。

当顶层模块的输入发生变化时,这些变化将传递到子模块,并子模块的输出也会传递回顶层模块。

总的来说,在Verilog中传递参数是通过模块的端口进行的,你需要在模块定义和实例化时正确地连接端口,以实现参数的传递和数据交换。

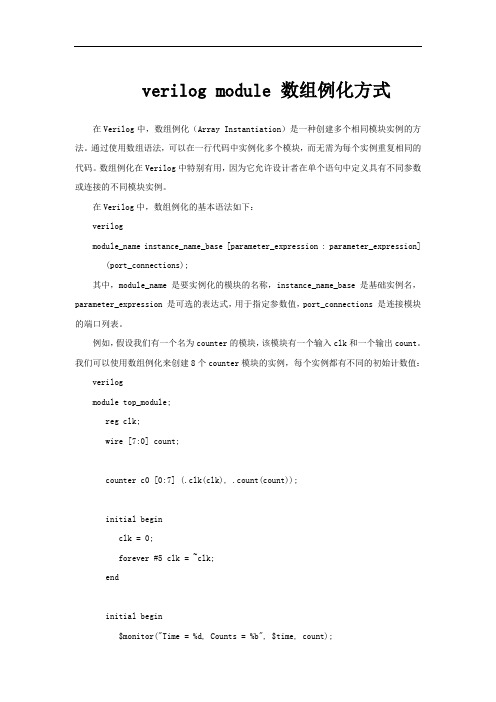

verilog module 数组例化方式

verilog module 数组例化方式在Verilog中,数组例化(Array Instantiation)是一种创建多个相同模块实例的方法。

通过使用数组语法,可以在一行代码中实例化多个模块,而无需为每个实例重复相同的代码。

数组例化在Verilog中特别有用,因为它允许设计者在单个语句中定义具有不同参数或连接的不同模块实例。

在Verilog中,数组例化的基本语法如下:verilogmodule_name instance_name_base [parameter_expression : parameter_expression] (port_connections);其中,module_name 是要实例化的模块的名称,instance_name_base 是基础实例名,parameter_expression 是可选的表达式,用于指定参数值,port_connections 是连接模块的端口列表。

例如,假设我们有一个名为counter的模块,该模块有一个输入clk和一个输出count。

我们可以使用数组例化来创建8个counter模块的实例,每个实例都有不同的初始计数值:verilogmodule top_module;reg clk;wire [7:0] count;counter c0 [0:7] (.clk(clk), .count(count));initial beginclk = 0;forever #5 clk = ~clk;endinitial begin$monitor("Time = %d, Counts = %b", $time, count);endendmodulemodule counter(input clk,output reg [7:0] count);parameter INIT_VAL = 0;always @(posedge clk)count <= (count + 1) % 256;initial count = INIT_VAL;endmodule在上面的示例中,counter模块被例化了8次,从c0[0]到c0[7]。

4.3verilog中的function用法与例子

4.3verilog中的function⽤法与例⼦函数的功能和任务的功能类似,但⼆者还存在很⼤的不同。

在 Verilog HDL 语法中也存在函数的定义和调⽤。

1.函数的定义函数通过关键词 function 和 endfunction 定义,不允许输出端⼝声明(包括输出和双向端⼝),但可以有多个输⼊端⼝。

函数定义的语法如下:function [range] function_id;input_declarationother_declarationsprocedural_statementendfunction其中,function 语句标志着函数定义结构的开始;[range]参数指定函数返回值的类型或位宽,是⼀个可选项,若没有指定,默认缺省值为 1⽐特的寄存器数据;function_id 为所定义函数的名称,对函数的调⽤也是通过函数名完成的,并在函数结构体内部代表⼀个内部变量,函数调⽤的返回值就是通过函数名变量传递给调⽤语句;input_declaration ⽤于对寒暑各个输⼊端⼝的位宽和类型进⾏说明,在函数定义中⾄少要有⼀个输⼊端⼝;endfunction为函数结构体结束标志。

下⾯给出⼀个函数定义实例。

定义函数实例。

function AND; //定义输⼊变量input A, B; //定义函数体beginAND = A && B;endendfunction函数定义在函数内部会隐式定义⼀个寄存器变量,该寄存器变量和函数同名并且位宽也⼀致。

函数通过在函数定义中对该寄存器的显式赋值来返回函数计算结果。

此外,还有下列⼏点需要注意:(1)函数定义只能在模块中完成,不能出现在过程块中;(2)函数⾄少要有⼀个输⼊端⼝;不能包含输出端⼝和双向端⼝;(3)在函数结构中,不能使⽤任何形式的时间控制语句(#、 wait 等),也不能使⽤ disable中⽌语句;(4)函数定义结构体中不能出现过程块语句(always 语句);(5)函数内部可以调⽤函数,但不能调⽤任务。

第2讲 Verilog HDL层次建模

2.1.6 自顶向下的设计实例

例2.3 脉动进位计数器顶层模块

例2.4 触发器T_FF 例ຫໍສະໝຸດ .5 带异步复位的D触发器 D_FF

例2.6 激励模块

激励信号和波形输出

2.1.7 小结

用于数字电路设计的两种方法:自顶向下方法和自底向上

方法。在当今的数字电路设计中,这两种方法经常组合使 用。随着设计复杂性的增加,使用这些结构化的方法来进 行设计管理变得越来越重要。 模块是Verilog中的基本功能单元。模块通过调用(实例引 用)来使用,模块的每个实例都被惟一标识,以区别于同 一模块的其他实例。每个实例都拥有其模板模块的不同副 本。读者需要将模块和模块实例区别开来。 仿真有两个不同的组成部分:设计块和激励块,激励块用 于测试设计块。激励块通常是顶层模块。对设计块施加激 励有两种不同的模式。 以脉动进位计数器为例,一步步地解释了为各个部分创建 仿真的过程。

说明为向量,则默认线网的位宽为1。线网的默认值为 z(trireg类型的线网例外,其默认值为x)。线网的值 由其驱动源确定,如果没有驱动源,则线网的值为z。

2.2.2.3 寄存器(reg,integer,real,time)

寄存器用来表示存储元件,它保持原有的数值,直到被

改写。寄存器数据类型一般通过使用关键字reg来声明, 默认值为x。例3.1给出了如何使用寄存器的例子。 例3.1 寄存器的声明和使用

一个模块的示例

Verilog HDL的四种描述方式

行为或算法级:Verilog所支持的最高抽象层次。设计者只

注重其实现的算法,而不关心其具体的硬件实现细节。在 这个层次上进行的设计与C语言编程非常类似。 数据流级:通过说明数据的流程对模块进行描述。设计者 关心的是数据如何在各个寄存器之间流动,以及如何处理 这些数据。 门级:从组成电路的逻辑门及其相互之间的互连关系的角 度来设计模块。这个层次的设计类似于使用门级逻辑简图 来完成设计。 开关级:Verilog所支持的最低抽象层次。通过使用开关、 存储节点及其互连关系来设计模块。在这个层次进行设计 需要了解开关级的实现细节。

verilog第二章简单的Verilog模块

and #1 u2(sela, a, nsl);

and #1 u3(selb, b, sl);

or #1 u4(out, sela, selb);

endmodule

/*一个名为adder的三位加法器的例子。*/

module adder ( count,sum,a,b,cin ); //模块定义开始

// 选择逻辑组合

2.2.2 模块的概念

一个设计是由一个个模块构成的。一个模块的设计如下:

1 模块内容是嵌套在module和endmodule两个语句之间。每个

模块实现特定的功能,模块是可以进行层次嵌套的。正因为

如此,才可以将大型的数字电路设计分割成不同的小模块来

实现特定的功能,最后通过顶层模块调用子模块来实现整体

endmodule

数据流语句

▪这个例子描述了一个三位的加法器。从例子中可以看出整个

Verilog HDL程序是嵌套在module和endmodule声明语句里

的,只出现了一个assign语句。

例SR触发器模块

S

Q

//SR 触发器

module SR_FF (Q, Q_n,S,R);

R

Q_n

output Q, Q_n; //端口声明

input S,R;

nand n1(Q, S,Q_n);

nand n2(Q_n,R,Q);

nand为verilog

中的与非门门级

原语部件

endmodule

模块中的5个部分并没全部出现,只出现在

低层次模块实例化

D触发器模块

//D 触发器

module D_FF (d, clk,clr,q,qb);

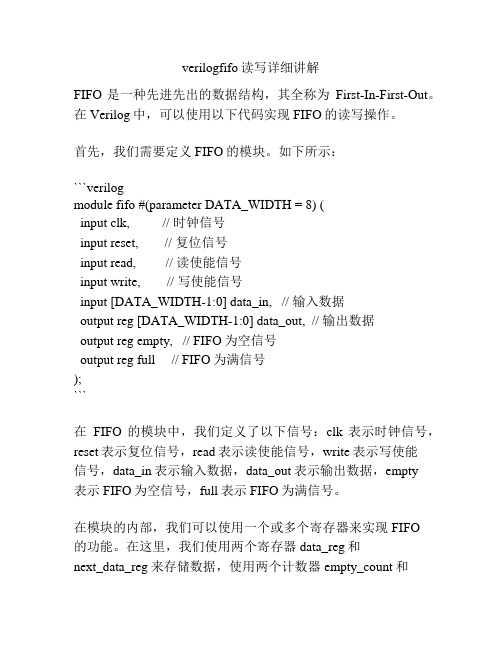

verilogfifo读写详细讲解

verilogfifo读写详细讲解FIFO是一种先进先出的数据结构,其全称为First-In-First-Out。

在Verilog中,可以使用以下代码实现FIFO的读写操作。

首先,我们需要定义FIFO的模块。

如下所示:```verilogmodule fifo #(parameter DATA_WIDTH = 8) (input clk, // 时钟信号input reset, // 复位信号input read, // 读使能信号input write, // 写使能信号input [DATA_WIDTH-1:0] data_in, // 输入数据output reg [DATA_WIDTH-1:0] data_out, // 输出数据output reg empty, // FIFO为空信号output reg full // FIFO为满信号);```在FIFO的模块中,我们定义了以下信号:clk表示时钟信号,reset表示复位信号,read表示读使能信号,write表示写使能信号,data_in表示输入数据,data_out表示输出数据,empty表示FIFO为空信号,full表示FIFO为满信号。

在模块的内部,我们可以使用一个或多个寄存器来实现FIFO的功能。

在这里,我们使用两个寄存器data_reg和next_data_reg来存储数据,使用两个计数器empty_count和full_count来记录FIFO的空和满状态。

```verilogreg [DATA_WIDTH-1:0] data_reg; // 数据寄存器reg [DATA_WIDTH-1:0] next_data_reg; // 下一个数据寄存器reg [DATA_WIDTH-1:0] data_out_reg; // 输出数据寄存器reg empty_count; // 空计数器reg full_count; // 满计数器```接下来,我们定义FIFO的行为。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

verilog顶层模块调用实例

以下是一个简单的Verilog顶层模块调用的示例代码:verilogmodule TopModule( input wire clk, input wire reset, output wire out); 实例化子模块SubModule

submodule( .clk(clk), .in(reset), .out(out) );endmodulemodul e SubModule( input wire clk, input wire in, output wire out); 具体逻辑实现 ...endmodule在上述代码中,`TopModule` 是顶层模块,它实例化了一个名为`SubModule` 的子模块,并通过端口连接起来。

顶层模块有三个端口:`clk`、`reset` 和`out`。

子模块也有三个端口:`clk`、`in` 和`out`。

顶层模块中的`clk` 和`reset` 端口直接连接到子模块的`clk` 和`in` 端口,而`out` 端口通过子模块传递给顶层模块。

这个例子中,顶层模块作为顶层设计的入口,可以将输入信号传递到子模块,并从子模块获取输出信号。

子模块的具体逻辑实现可以根据实际需求进行定义。

请注意,这只是一个简单的示例,你可以根据实际需求进行更复杂的模块调用和连接。