6 折叠式共源共栅运算放大器设计实验.

折叠式共源共栅电路结构

折叠式共源共栅电路结构1. 介绍折叠式共源共栅电路结构是一种常见的电路结构,广泛应用于集成电路设计中。

它具有很多优点,例如低功耗、高增益、高频特性稳定等。

本文将深入研究折叠式共源共栅电路结构的原理、特点及其在集成电路设计中的应用。

2. 折叠式共源共栅电路结构的原理折叠式共源共栅电路结构由两个互相折叠并串联的晶体管组成,其中一个晶体管作为放大器的输入端(即源极),另一个晶体管作为放大器的输出端(即漏极)。

两个晶体管之间通过一个无源负载进行连接。

这种连接方式使得输入和输出之间具有很高的耦合效率,从而提高了整个电路的增益。

3. 折叠式共源共栅电路结构的特点3.1 低功耗:由于折叠式共源共栅电路结构中使用了两个互相串联并通过无源负载连接,使得整个电路在工作时能够充分利用输入信号和输出信号之间的能量传递,从而减少了功耗。

3.2 高增益:折叠式共源共栅电路结构中的两个晶体管之间通过无源负载连接,使得输入信号能够得到充分放大,从而提高了整个电路的增益。

3.3 高频特性稳定:折叠式共源共栅电路结构中的两个晶体管之间通过无源负载连接,在高频信号传输中能够保持稳定的特性,从而提高了整个电路在高频工作时的性能。

4. 折叠式共源共栅电路结构在集成电路设计中的应用4.1 射频放大器:折叠式共源共栅电路结构由于其低功耗、高增益、高频特性稳定等特点,在射频放大器设计中得到了广泛应用。

射频放大器是无线通信系统中重要的组成部分,其主要作用是对输入信号进行放大,使其能够满足系统要求。

折叠式共源共栅电路结构可以有效地满足射频放大器对低功耗、高增益和稳定性能等方面的要求。

4.2 低噪声放大器:在集成电路设计中,低噪声是一个重要指标。

由于折叠式共源共栅电路结构具有高增益和低功耗的特点,因此在低噪声放大器的设计中得到了广泛应用。

低噪声放大器主要用于信号源和接收机之间,其主要作用是将输入信号进行放大,并尽可能地减少噪声的引入。

折叠式共源共栅电路结构能够有效地提高低噪声放大器的增益,并减少噪声的引入。

采样保持电路中全差分运算放大器的设计与仿真

采样保持电路中全差分运算放大器的设计与仿真采样保持电路中全差分运算放大器的设计与仿真1 引言运算放大器是许多模拟系统和混合信号系统的一个完整部分,伴随着每一代CMOS 工艺,由于电源电压和晶体管沟道长度的减小,为运算放大器的设计不断提出新的挑战。

在采样保持电路的设计中,运算放大器是最关键的模块之一,其带宽,摆率,增益,噪声,失调等性能直接决定了采样保持电路模块的速度,精度等性能。

2 折叠共源共栅结构电路结构。

图1 折叠共源共栅运算放大器运算放大器采用折叠共源共栅结构,采用NMOS 输入差分对MN1 和MN2。

MN0 为输入差分对的尾电流源,向MN1 和MN2 提供直流偏置。

MP1 和MP2 为电流源,向输入管和共源共栅管提供直流偏置。

MP3 和MP4 为共源共栅管,用来提高运算放大器的增益。

MN3,MN4,MN5 和MN6 是共源共栅电流镜负载,采用共源共栅结构可以提高输出阻抗。

与套筒式结构相比,折叠共源共栅结构放大器输出摆幅增大了一个过驱动电压,另外较大的共模输入范围是我们选择折叠共源共栅结构的主要原因。

3 开关电容共模反馈(CMFB)电路由于采用全差分结构,而在高增益的全差分运算放大器中,输出共模电平对器件的特性和适配相当敏感,而且不能通过差模反馈来达到稳定,因此设计时增加了共模反馈电路模块,来稳定输出共模电平。

共模反馈电路。

共模反馈电路与主运放的连接。

图 2 共模反馈电路该结构与电阻检测方式,运用MOSFET 作为源级跟随器和可变电阻的检测技术相比有明显优点。

其工作流程如下,时钟信号在Φ1 相位时,为C1 充电,确定C1 两端的电压,在Φ2 相位时,将C1 与C2 并联,根据Vo1 和Vo2 平均值的大小确定输出共模电平。

例如,(Vo1+Vo2)/2>VREF,则输出共模电平cmctl bias v > v ,从而使尾电流减小,最终导致输出(Vo1+Vo2)/2 减小,连续几个周期调整后,将使(Vo1+Vo2)/2≈Vref。

一种折叠共源共栅运算放大器的设计

一种折叠共源共栅运算放大器的设计杨俊;卞兴中;王高峰【摘要】折叠共源共栅运放结构的运算放大器可以使设计者优化二阶性能指标,这一点在传统的两级运算放大器中是不可能的.特别是共源共栅技术对提高增益、增加PSRR值和在输出端允许自补偿是有很用的.这种灵活性允许在CMOS工艺中发展高性能无缓冲运算放大器.目前,这样的放大器已被广泛用于无线电通信的集成电路中.介绍了一种折叠共源共栅的运算放大器,采用TSMC 0.18混合信号双阱CMOS工艺库,用Hspice W-2005.03进行设计仿真,最后与设计指标进行比较.【期刊名称】《现代电子技术》【年(卷),期】2006(029)018【总页数】3页(P28-30)【关键词】CMOS;运算放大器;折叠共源共栅;Hspice W-2005.03【作者】杨俊;卞兴中;王高峰【作者单位】武汉大学,微电子与信息技术研究院,湖北,武汉,430072;武汉大学,物理科学与技术学院,湖北,武汉,430072;武汉大学,微电子与信息技术研究院,湖北,武汉,430072;武汉大学,物理科学与技术学院,湖北,武汉,430072;武汉大学,物理科学与技术学院,湖北,武汉,430072【正文语种】中文【中图分类】TN722.7+71 引言随着集成电路技术的不断发展,高性能运算放大器广泛应用于高速模/数转换器(ADC)、数/模转换器(DAC)、开关电容滤波器、带隙电压基准源和精密比较器等各种电路系统中,成为模拟集成电路和混合信号集成电路设计的核心单元电路,其性能直接影响电路及系统的整体性能。

高性能运算放大器的设计一直是模拟集成电路设计研究的热点之一,以折衷满足各种应用领域的需要。

许多现代集成CMOS运算放大器被设计成只驱动电容负载。

有了这样只有电容的负载,对于运算放大器,就没有必要使用电压缓存器来获得低输出阻抗。

因此,有可能设计出比那些需要驱动电阻负载的运算放大器具有更高速度和更大信号幅度的运算放大器。

折叠式共源共栅电路结构

折叠式共源共栅电路结构折叠式共源共栅电路,是一种常见的电路结构,常用于放大和信号处理的应用中。

该电路结构由共源放大器和共栅放大器组成,通过折叠式的设计,可以在一定程度上提高电路的性能和稳定性。

我们来了解一下共源放大器和共栅放大器的基本原理。

共源放大器是一种常见的场效应管放大器电路,由一个场效应管和负载电阻组成。

当输入信号施加在场效应管的栅极上时,输出信号会经过负载电阻形成输出电压。

共源放大器的特点是增益较高,输入阻抗较低,输出阻抗较高。

而共栅放大器也是一种场效应管放大器电路,由一个场效应管和负载电阻组成。

不同于共源放大器,共栅放大器的输入信号施加在场效应管的源极上,输出信号则取自场效应管的栅极。

共栅放大器的特点是增益较低,输入阻抗较高,输出阻抗较低。

将共源放大器和共栅放大器结合起来,形成折叠式共源共栅电路结构。

这种结构的设计可以在一定程度上克服共源放大器和共栅放大器各自的缺点,提高整体的性能和稳定性。

在折叠式共源共栅电路中,共源放大器和共栅放大器之间通过一个电容连接起来,起到耦合的作用。

这样设计的好处是可以在一定程度上提高电路的增益和带宽,减小相位失真。

同时,通过折叠式的结构,可以有效地降低电路的输入和输出阻抗,提高电路的适配性。

除了以上的基本原理,折叠式共源共栅电路还可以根据具体的应用需求进行进一步的优化和改进。

例如,可以在共源放大器和共栅放大器之间添加一个反馈电路,以提高电路的稳定性和线性度。

另外,可以通过调整电路中的元件参数和工作点,来满足不同的放大要求和特性。

折叠式共源共栅电路是一种常见的电路结构,通过将共源放大器和共栅放大器结合起来,可以在一定程度上提高电路的性能和稳定性。

该电路结构在放大和信号处理的应用中具有广泛的应用前景。

通过不断的优化和改进,可以进一步提高电路的性能和适配性,满足不同的应用需求。

一种两级全差分折叠共源共栅运算放大器的设计

Rcc

=

Cc + CL gm12Cc

=

4.75 gm12

(2.10)

2.确定尾电流大小 由图 2.1 可知当输入差分信号很大时,不妨设 M2 管截止,此时通过 Cc2 的充电电流大

小为 ID6-ID10,由此可计算出压摆率为

SR = ID6 − ID10 > 2V / μs Cc

(2.11)

其中 Cc=8pF,故 ID6-ID10=16μA。在设计中为了留有裕量,取 ID6-ID10=25μA。又

载电容较大,为 30pF。可以预计电路的主极点位于第一级放大器的输出端,而非主极点位 于第二级放大器的输出端,且与主极点的值相差不远。频率补偿的目的就是尽可能使这两个 极点分离开,可以采取的方案有密勒补偿。同时,还可以引入左半平面的零点,以补偿非主

2

极点造成的相频恶化,例如给 CMFB 的共模取样电阻并上电容等。 除了考虑电路差模环的频率稳定性外,还应该考虑共模环的稳定性。因为 CMFB 电路

为了达到 60º相位裕度,应满足

(2.6)

PM = 180 + Ph[T ( jGB)] = 60

(2.7)

由

Ph[T ( jω)] = − tan−1( ω ) − tan−1( ω ) + tan−1( ω )

− p1

− p2

−z

(2.8)

代入(2.7)式,并设 z > 10GB,可以求得|p2|=2.2GB,Cc > 0.22CL=6.6pF。在设计中为

(2.13)

式中 VDS6 < VTP 总能成立,所以输入管 M1、M2 工作于饱和区。实际上,输入共模电压最 小可以低于 0V。输入共模电压最大值至少应为 1.2V,有

运算放大器实验报告---修改版

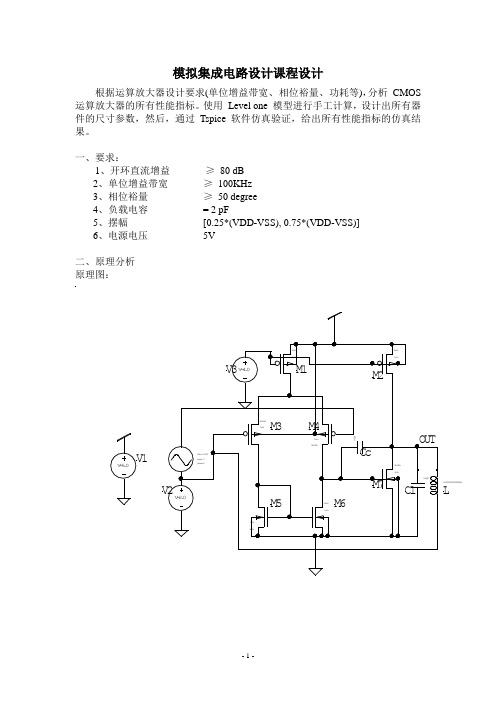

模拟集成电路设计课程设计根据运算放大器设计要求(单位增益带宽、 相位裕量、 功耗等),分析 CMOS 运算放大器的所有性能指标。

使用 Level one 模型进行手工计算,设计出所有器件的尺寸参数,然后,通过 Tspice 软件仿真验证,给出所有性能指标的仿真结果。

一、要求:1、开环直流增益 ≥ 80 dB2、单位增益带宽 ≥ 100KHz3、相位裕量 ≥ 50 degree4、负载电容 = 2 pF5、摆幅 [0.25*(VDD-VSS), 0.75*(VDD-VSS)]6、电源电压 5V二、原理分析 原理图:L1L =100000000000000G uV =5.0实验原理:电路选用二级米勒补偿,其中一级放大主要是放大增益,二级是放大摆幅,将电路分三部分来看左边:用直流电压为m1,m2提供偏置电压中间:m3,m4,m5,m6,m1一路选用差分放大电路作为一级放大 右边:m2,m7一路是提高输出摆幅电路部分 Cc 为补偿电容,而电感L 起稳压作用为达到设计指标,对运算放大器的每个moS 管都要在饱和区工作,通过对原理图的小信号分析得到这种结构的增益为Gain = gm1×gm6/(gds2 + gds4)/(gds6 + gds7)表示,其中gds2 , gds4, gds6 , gds7,分别为M2,M4,M6,M7管的相关电导。

gm1,gm6分别M1、M6的跨导。

而输出电压摆幅为Vincm.max=Vdd-|V GS3|+Vthn ,Vincm.min=V od5-V GS1=V od5+V od1+Vthn1,其中Vod1、Vod5分别为M1和M5的过驱动电压。

21()(1)2D n oxG S TH D S W I C V V V Lμλ=-+2()112()()D m n oxG S TH D S G S THDDD S G S TH on n ox G S TH I W g C V V V LV V I L I V V V R W C V V Lμγλγμ=-==-∝-=- 饱和饱和=时三、设计步骤:1. 由已知的C L 并根据转换速率的要求(或功耗要求)选择I SS (I 9)的范围;2. 计算满足频率要求的R out 范围,否则,改变I SS ;3. 设计W 3/L 3( W 4/L 4)、W 5/L 5( W 6/L 6 )满足上ICMR (或输出摆幅)要求;4. 设计W 2/L 2 、 W 7/L 7满足增益要求;满足下ICMR (或输出摆幅)要求;5. 若达不到设计要求,重复上述过程。

折叠式共源共栅电路

折叠式共源共栅电路

折叠式共源共栅电路是一种常用于低噪音放大器的电路结构,它由共源放大器和共栅放大器连接而成。

整个电路将输入信号分别放大、反向相位放大,最终输出得到高质量的信号。

在折叠式共源共栅电路中,共源放大器负责输出信号的半波放大,而共栅放大器则负责反相的半波放大,使得输出信号带有高增益和低噪声。

具体地,输入信号先被送入共源放大器的源极,然后经过源漏间隙进入共栅放大器进行反相放大,最终输出信号在负载上形成完整波形。

与传统共源共栅电路不同,折叠式共源共栅电路能够实现压控增益,这是因为电路中的共栅放大器可以通过偏置电压的调节改变其阻抗。

此外,通过引入折叠技术,这种电路还可有效地降低电路面积和噪声电压,从而提高其工作效率和性能表现。

总的来说,折叠式共源共栅电路既具有传统共源共栅电路的优点,同时又能够在一定程度上增加电路的灵活性和性能表现。

因此,在低噪音放大器以及信号放大器等领域中,这种电路结构被广泛地应用和研究。

折叠式共源共栅电路结构

折叠式共源共栅电路结构折叠式共源共栅电路是一种常见的电路结构,用于放大和调节电信号。

它由一个共源放大器和一个共栅放大器组成,通过折叠结构的连接方式实现电信号的放大和调节。

在折叠式共源共栅电路中,共源放大器负责放大电信号,而共栅放大器则负责调节电信号。

这两个放大器通过折叠结构的连接方式实现了信号的传递和调节。

让我们来了解一下共源放大器的工作原理。

共源放大器由一个场效应管组成,该管的栅极连接到信号源,漏极连接到负载电阻,源极则通过电源电压相连。

当信号源输入信号时,场效应管的栅极电压发生变化,导致漏极电流的变化,从而实现电信号的放大。

共源放大器具有输入阻抗高、增益大的特点,适用于信号放大的场合。

接下来,我们来讨论一下共栅放大器的工作原理。

共栅放大器也由一个场效应管组成,该管的栅极连接到信号源,漏极连接到负载电阻,源极则通过电源电压相连。

与共源放大器不同的是,共栅放大器的输出信号是从漏极取出的。

当信号源输入信号时,场效应管的栅极电压发生变化,导致源极电流的变化,从而实现电信号的调节。

共栅放大器具有输出阻抗低、电流增益大的特点,适用于信号调节的场合。

在折叠式共源共栅电路中,共源放大器和共栅放大器通过折叠结构连接起来。

折叠结构是一种特殊的电路布局,可以有效地减少信号传输过程中的干扰和损耗。

通过折叠结构的连接方式,共源放大器和共栅放大器可以实现信号的有序传递和调节,从而达到电信号放大和调节的目的。

总结一下,折叠式共源共栅电路是一种常见的电路结构,用于放大和调节电信号。

它由共源放大器和共栅放大器组成,通过折叠结构的连接方式实现信号的有序传递和调节。

折叠式共源共栅电路具有放大器的特点,适用于信号放大和调节的场合。

这种电路结构在电子设备中得到广泛应用,对于提高电路性能和信号质量具有重要意义。

gmid折叠共源共栅运放

GMID折叠共源共栅运放1. 什么是GMID折叠共源共栅运放?GMID折叠共源共栅运放(Folded Cascode Operational Amplifier with Gain Boosting)是一种常用的运算放大器电路,主要用于信号放大和处理。

它采用了折叠式的电路结构,通过共源共栅(Cascode)连接以增加增益和带宽。

2. GMID折叠共源共栅运放的特点GMID折叠共源共栅运放具有以下几个特点:2.1 高增益GMID折叠共源共栅运放通过使用多级级联的结构,可以实现较高的增益。

其中,折叠式结构可以提供更高的输出阻抗,从而减小负载影响;而利用多级级联可以进一步提高整体增益。

2.2 宽带宽GMID折叠共源共栅运放通过采用Cascode连接方式,可以有效地减小输入和输出电容之间的Miller效应,并提高带宽。

此外,通过合理设计电路参数和引入补偿电容等手段,还可以进一步扩展带宽。

2.3 低功耗GMID折叠共源共栅运放可以通过调整电流源和电阻等参数来实现低功耗设计。

合理选择电流源的大小和类型,可以在满足性能要求的前提下降低功耗。

2.4 适用于集成电路GMID折叠共源共栅运放的结构简单紧凑,适合在集成电路中实现。

它可以利用CMOS工艺来制造,并且可以通过调整晶体管尺寸和工作点等参数来满足具体应用需求。

3. GMID折叠共源共栅运放的基本原理GMID折叠共源共栅运放的基本原理是利用多级级联的结构和Cascode连接方式来增加增益和带宽。

下面将详细介绍其基本原理。

3.1 基本结构GMID折叠共源共栅运放由输入级、中间级和输出级组成。

其中,输入级负责将输入信号转换为差分信号,中间级负责增益放大,输出级负责驱动负载。

3.2 输入级输入级由两个差分对组成,每个差分对包括一个PMOS晶体管和一个NMOS晶体管。

其中,PMOS晶体管的栅极连接到VDD电压,NMOS晶体管的栅极连接到接地。

通过控制差分对的栅极电压,可以实现输入信号的差分放大。

改进型折叠式共源共栅运算放大器电路的设计

改进型折叠式共源共栅运算放大器电路的设计殷万君;白天蕊【摘要】In the telescopic cascodeand folded cascode operational amplifier, the folded cascode operational amplifier with high output swing and low bias voltage is widely used. However, these advantages are at the expense of a larger power consumption and lower current utilization rate. In order to improve the current utilization rate, an improved folded cascode operational amplifier was designed. The improved folded cascode operational amplifier can significantly improve transconductance, slew rate and noise performance at the same voltage and load. The simulation results show that under the same power consumption and area condition, the gain bandwidth and slew rate of the improved folded cascode operational amplifier is 3 times as that of the original folded cascode operational amplifier.%在套筒式共源共栅、折叠式共源共栅运放中,折叠式共源共栅运算放大器凭借较大的输出摆幅和偏置电压的较低等优点而得到广泛运用.但是,折叠式的这些优势是以牺牲较大的功耗、较低的电流利用率而换取的.本文以提高电流利用率为着手点设计了一种改进的折叠式共源共栅运算放大器,在相同的电压和负载下改进的折叠式共源共栅运算放大器能显著提升跨导、压摆率和噪声性能.仿真结果表明在相同功耗和面积的条件下,改进的折叠式共源共栅运算放大器的单位增益带宽和压摆率是折叠式共源共栅运放的3倍.【期刊名称】《现代电子技术》【年(卷),期】2012(035)020【总页数】3页(P167-168,172)【关键词】套筒式共源共栅;折叠式共源共栅;电流利用率;偏置电压【作者】殷万君;白天蕊【作者单位】西南交通大学信息科学与技术学院,四川成都 610031;西南交通大学信息科学与技术学院,四川成都 610031【正文语种】中文【中图分类】TN722-34运算放大器(简称运放)是模拟电路的一个最通用的单元。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设置DC参量时,首先,要选择Save DC Operating Point项,此项是为了保存静态工作点的;然后在Sweep Variable区域选择Design Variable项,选取变量名称,可以直接输入你所定义的变量名,也可以从下面的Select Design Variable中选择需要扫描的变量,我们这里扫描差动信号的直流分量vdm1。在Sweep Range中选择扫描变量的范围,定义起始点为0V,终止点为3.3V,而且采取线性扫描方式,扫描的步长设为0.01V。

建立的symbol的图形(可以改变图形形状),如下图所示:

5.加入激励

对于已经生成symbol的图形,需要给输入端加入激励之后才能够进行仿真。需要生成一个新的cell view作仿真,此处起名为sim_pucker-SG,易于统一名称。

Cell view的生成同上所述,在cell view的设计过程中加入刚刚设计的折叠式共源共栅放大器作为仿真模型,对其输入端加激励。

从上面的叙述可知,电容的值是一个根据要求而变化的值,所以我们把电容值设为一个参数cap,在仿真过程中再添加其值。这样只是为了方便更改而已,你也可以直接对负载电容赋值,在仿真时,再根据情况更改电容值。

负载电容的值设为参变量cap,在仿真过程中给定值。

注意:在作仿真图形时,还需要有一个用来规定电源电压值的电路,这是为了防止多个电路中有多个电源电压的情况,这样只需设定一个电源电压来规定电源电压的值,而不会发生冲突。

负载电容值的确定:

对于负载电容值的确定是有要求的,因为题目要求单位增益带宽尽可能的大,所以在满足了增益的情况下,需要主极点越大越好,只有主极点越大才能保证单位增益带宽越大。主极点与输出阻抗和负载电容的乘积的倒数有关,而输出阻抗的值影响增益的大小,如果输出阻抗越大,则增益越大,但是主极点越小,从而使单位增益带宽越小,所以只有在增益一定的情况下改变负载电容的值来增加单位增益带宽。

4.

以上设置完成后,就可以进行仿真了。

仿真的方法有两种,可以通过点击菜单中的Simulation-Netlist and Run进行网表的提取和仿真;第二种方法是通过快捷方式,即图框中右下角的按钮进行仿真。

运行之后会产生网表和运行图形,点击Result-Print-DC Operating Points查看每个mos管的状态,如下图所示:

注意:乘号的意思代表宽度的乘数*倍数,即在multiplier处添加倍数值。

4)分配初始偏置电压值

mos管阈值电压的初始值由工艺库中给定,pmos管的阈值电压为Vth=-0.663V,nmos管的阈值电压为Vth=0.713V,这些值将在仿真过程中修正。

i). pmos管M0,M1的过驱动电压为VOD0=VOD1=0.4V,而|Vth|=0.663V,则偏置电压源电压为V0=3.3V-(0.663V+0.4V)=2.237V。

3.设定仿真类型

i).tran(瞬态)分析设定

Analyses->Choose,选择tran分析,如图所示:设置仿真时间为1ms。

注意:设定的瞬态仿真时间一般是频率倒数的1-10倍即可,过大可能无法看出细微图形,太小根本看不到一个周期的情况。此处设的1ms就是频率的倒数。

ii). DC(直流)分析设定

ii).变量的设置

首先,需要导入要设置的变量名进入Design Variable中,点击Variables->Copy From Cellview导入变量,如下图所示:

注意:此处设定参数时,在Design Variables图形框中双击要设置的参量后,设定其值。

设定负载电容的值时,先假定给cap=1pF,后面还要根据题目要求更改cap的值,以满足单位增益带宽和稳定性的要求。vdm1,vdm2的值是根据输入端的偏置电压值设定的,即初始值vdm1=vdm2=1.413V。

=>(W/L)=(upCOXVOD2) /(2 IDS)

根据公式可得所有mos管的宽长比,分别为:

(W/L)0-1=388.62;(W/L)2-3=253.75;(W/L)4-7=91.3;

(W/L)8=(W/L)10=91.3;(W/L)9=102.7。

根据上面求出的宽长比确定宽度和长度。由于使用工艺库,取L=1.4um(取L的值较大是为了达到大的增益的要求),同样可以得到各种W值W0,1=136*4um,W2,3=88.82*4um,W4,5,6,7=63.92*2um,W8,10=63.92*2um,W9=71.88*2um。

学习差动放大器DC扫描、AC、瞬态分析的方法。

参数给定:COX=(εsiεo)/tox

其中εsi=8.85*10-12,εo=3.9,tox=6.62nm;

un=350cm2,up=92.5cm2。

2.

1.启动cadence工具

在Terminal中输入cds.setup

icfb&

2.电路设计

按照下图进行电路设计,运放采用折叠式共源共栅电路。

iv).nmos管M6,M7的过驱动电压为VOD6=VOD7=0.3V,而Vth=0.713V,则偏置电压源电压为V0=0.713V+0.3V=1.013V。

v).nmos管M8,M10的过驱动电压(输入管的偏置直流电压部分)为VOD8=VOD10=0.3V,而Vth=0.713V,则偏置电压源电压为V0=0.713V+0.3V+0.4V=1.413V。

注意:i).所有的pmos管的衬底都必须接电源;所有nmos管的衬底都必须接地

ii).直接用电压源给出偏置电压。

3.参数计算

完成了电路图的基本结构之后,接下来就是给每个元件加入设计量,这样就需要对各个器件的参数进行分配和计算。从图中的mos管的标号定义:总的尾电流源pmos管为M0,M1;pmos共栅管为M2,M3;nmos共源共栅管从上到下依次为M4,M5,M6,M7;输入管为M8,M10;输入端的尾电流源mos管为M9。pmos管的model name取p33,nmos管为n33。

1)电流的分配

由于VDD=3.3V,功率P=10mW,则总的电流为IDS=10mW/3.3V=3mA。其次两条支路是完全对称的,所以给每条之路分配1.5mA的电流。而对于折叠电路部分和本身的共源共栅电路部分将每条支路的电流再次分割,这里我们全部采用平分的方式,即M0,M1的电流均为1.5mA;其余mos管(除M9外)的电流均为0.75mA,是每条支路的二分之一;而对于M9的电流值为两个输入支路电流之和,即为1.5mA。

vi).nmos管M9ຫໍສະໝຸດ 过驱动电压为VOD9=0.4V,而Vth=0.713V,则偏置电压源电压为

V0=0.7V+0.4V=1.113V。

根据给定的初始的偏置电压给各个偏置电压源加值。

4.生成symbol图形

Symbol的生成过成:我们选择在已经制作好的cell view中建立它的symbol,点击Design->Create Cell View->from Cell View,这样就直接从已经建好的cell view的schematic中建立了它的symbol文件。

注意:a)在调节mos管的宽长比时,只能在原来的宽长比的基础上对宽度作适当调整,不能不考虑原来的值,大幅度调整,这样将会和你的设计完全不符的情况。

b)如果当所有的mos管都已达到饱和,但是对于放大器的增益还是不满足时可以将输出端两端的mos管的宽长同时加大,这样可以使增益大幅度增加。这是由于当宽长同时加大时,电流、跨导等量由于宽长比的值没有变化,所以它们的值也不改变。但是由于长度L增大一倍,使λ值减小,从而使这个mos管的输出电阻增大,输出两端的mos管的宽长同时加大,即M2,M3,M4,M5的宽长同时加大,使输出电阻ro2,ro3,ro4,ro5增大,从而使增益加大。

根据打印出的mos管状态图中的Vth值,通过V0=VOD+Vth+Vs来修正偏置电压的值,再进行仿真。在此过程中,由于M0,M1,M6,M7,M9不存在衬偏效应所以他们的阈值电压值的改变可能会小一些,所以先调整这些管子的偏置电压值比较合适;而对于M2,M3,M4,M5,M8,M10这些mos管而言,都存在衬偏效应,所以他们的值改变的比较大,需要不断的修正仿真,直到这些值都基本不变化即可。这样就完全确定了偏置电压的值。

主极点与输出阻抗和负载电容的乘积的倒数有关而输出阻抗的值影响增益的大小如果输出阻抗越大则增益越大但是主极点越小从而使单位增益带宽越小所以只有在增益一定的情况下改变负载电容的值来增加单位增益带宽

国家集成电路人才培养基地

模拟电路高级实验(6)

折叠式运算放大器

2006-07

1.

设计共源共栅运算放大器,使其满足VDD=3.3V,功率P=10mW,输出摆幅为1.95V,增益AV≥80dB。使用SMIC 0.18um 3.3V CMOS工艺3.3V晶体管模型。

iii).AC(交流)分析设定

Analyses->Choose,选择ac分析,如图所示:

设置AC参数时,只需对频率进行扫描,这里设置扫描范围为10-300MHZ。

4.设定输出波形

点击Output->to be plotted->Select On Schematic后,所作的schematic图形将自动弹出,然后选择需要输出的信号电压或者pin脚电流,这里我们选择两个输出量Vout1,Vout2为需要输出的信号电压。选择输出端作为仿真的输出时,输出端将变为彩色的高亮度线条。

3)宽长比的确定

通过电流与过驱动电压的关系式确定宽长比,由于所有mos管都必须工作在饱和区,所以使用饱和区的电流-过驱动电压的关系:

Nmos管:IDS=1/2unCOX(W/L)(VGS-Vth)2=1/2unCOXVOD2

=>(W/L)=(unCOXVOD2) /(2 IDS)