VHDL And Synthesis Review

eda综合的概念

eda综合的概念

EDA综合(Electronic Design Automation synthesis)是电子设计自动化的一个重要环节,主要涉及到数字电路的综合和优化。

综合是将高级描述语言(如Verilog、VHDL等)表示的电路设计转换为具体的逻辑门级网表的过程。

在这个过程中,综合工具会根据设计约束和优化目标,将抽象的设计转化为可实现的硬件电路。

EDA综合的过程包括以下几个阶段:

1. 高级综合:将高级描述语言(如C/C++/SystemC)描述的功能转化为RTL(Register Transfer Level)级的抽象电路。

高级综合工具能够进行并行化、流水线化、资源共享等优化,以提高电路性能和效率。

2. RTL综合:将RTL级的电路描述转化为逻辑门级的电路网表。

RTL综合包括逻辑综合和寄存器传输级综合,其中逻辑综合用于将逻辑门和寄存器的组合逻辑表示为逻辑门级的网表,而寄存器传输级综合则是将寄存器和时钟相关的逻辑转化为时序逻辑网表。

3. 时序综合:根据时序约束对逻辑网表进行时序优化,以满足电路的时序要求,如时钟频率、时序延迟等。

4. 物理综合:将逻辑网表转换为物理布局,并进行布线和管脚分配,以满足电路的物理约束要求,如芯片面积、功耗、信号完整性等。

5. 验证和优化:对综合后的电路进行功能验证和时序验证,并根据验证结果进行必要的优化,以确保电路的正确性和性能。

EDA综合在电子设计中起着重要的作用,可以提高设计效率和准确性,缩短产品开发周期。

通过综合工具的优化,可以实现更高的性能、更低的功耗和更小的面积,同时也能提高电路的可靠性和可维护性。

EDA-综合

10

X(0) X(1) X(0) X(2) X(1) X(2)

G1

G2 G3

A1 G4 A2 A3 C1

15

Motorola HDC库Synopsys综合工具。边P259VHDL设计电子线路

16

一位加法器

17

RTL (1)—行波进位加法器(Ripple carry adder)

architecture struc of adder is signal C: std_logic_vector(4 downto 0); begin process(a,b,cin,c) begin C(0)<= Cin; for i in 0 to 3 loop Sum(i)<= a(i)xor b(i) xor C(i); C(i+1)<= (a(i) and b(i) ) or (C(i) and (a(i) or b(i))); end loop; Cout<=C(4); end process; end struc ;

26

RTL描述 展 平

综 合 工

未优化布尔式

约束文件 — script

工艺库— — Library

优化(面积、时间)

优化布尔式 映 网 射 表

具 流 程

27

பைடு நூலகம்

• 综合工具

RTL Description Technology Library

EDA与VHDL复习参考题 (1)

选择题1. 综合是EDA设计流程的关键步骤,在下面对综合的描述中,()是错误的。

A. 综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B. 综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C. 为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D. 综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

2. IP核在EDA技术和开发中具有十分重要的地位,IP分软IP、固IP、硬IP,下列所描述的IP核中,对于硬IP的正确描述为__________。

A.提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路;B.提供设计的最总产品----掩膜;C.以网表文件的形式提交用户,完成了综合的功能块;D.都不是。

3提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__________。

A .软IP B.固IP C.硬IP D.都不是4 在VHDL程序存盘过程当中,文件名应该是()A. 结构体名B. 程序包名C. 任意D. 实体名5. 大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是____。

A.FPGA是基于乘积项结构的可编程逻辑器件;B. FPGA是全称为复杂可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

6. 规模可编程器件主要有FPGA、CPLD两类,其中CPLD通过_______实现其逻辑功能。

A. 可编程乘积项逻辑B. 查找表(LUT)C. 输入缓冲D. 输出缓冲7.大规模可编程器件主要有CPLD和FPGA两类,下面对FPGA结构与工作原理描述中,正确的是()A FPGA全称为复杂可编程逻辑器件B FPGA是基于乘积项结构的可编程逻辑器件。

数字电路英文版 第八单元

A logical gate circuit is a fundamental building block of digital circuits that perform a specific logical operation on one or more input signals

It insists of transitions connected together to implement logical functions such as AND, OR, NOT, and

Field effect transformer

A field effect transformer (FET) is a transformer that uses an electric field to control the flow of current through it

FETs are commonly used in analog and digital circuits, such as amplifiers, oscillators, and switching circuits

NAND operation

It is the logical NOT operation of the AND operation If any of the inputs are low, the output is high If all inputs are high, the output is low

Diode

01

Diode is a two terminal electronic component that allows the flow of current in only one direction

ic6-review

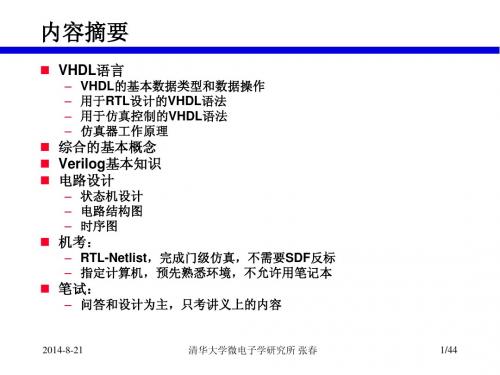

2014-8-21

清华大学微电子学研究所 张春

14/44

事件驱动的仿真

信号操作及事件: Event:对信号的赋值操作,且信号新值与旧值不同。

开始仿真 更新信号值 执行活动进程 更新仿真时钟

仿真周期

当前时间的所有事件都处理完后时间才会递增

2014-8-21

清华大学微电子学研究所 张春

15/44

信号赋值的延时性

信号赋值具有延时性,缺省是Delta X1 <= `1' after 10 ns; SR1 <= 5 after 5 ns; X2 <= `0' after 10 ns, `1' after 20 ns, `0' after 30 ns; X5 <= `1';

t t+5 0 10 5 1 0 t+10 1 t+20 t+30

Y5 <= X; Z <= Y5;

end process;

end FIVE_A;

2014-8-21 清华大学微电子学研究所 张春 19/44

状态S2 10 R 状态S3 11 R R 状态S1 01 R RA 状态S0 00 R+A R R 状态S4 10

End process

2014-8-21

清华大学微电子学研究所 张春

12/44

VHDL程序

Architecture arch of xxx is signal state: std_logic_vector(1 downto 0); Begin Process(rst,clk) Begin if rst=„1‟ then state <=“00”; elsif clk‟event and clk=„1‟ then case state is when “00” => result <= „0‟; if key_in=9 then state <= “01”; when “10” => state <= “00”; if key_in=1 then result <=„1‟; else result <= „0‟; end if; when others => end case; End if; End process; End arch; state <= “00”; result <= „0‟; else state <= “00”; end if; when “01” => result <= „0‟; if key_in=3 then state <= “10”;

quartusII.9安装及使用

一、安装 解压,打开90_quartus_windows.exe,选择 安装路径,点击Install自动安装

选择 I accept· · · ,以后就是一路的Next

选Complete完整版

安装完成,Finish后,此时在桌面可见软件图标

二、破解 破解前关闭杀毒软件,保证电脑联网在线。 找到并记下你电脑的网卡物理地址。 打开CRACK文件夹,将“Quaruts_II_9.0破解器.exe” 文件拷到安装目录下的quartus文件夹的bin文件夹中, 然后再双击打开。

architecture art of nanda is begin c <= not(a and b); end art;

注意:保存的文件名必须与实体名相同。

三、编译 VHDL 文件。 点击工具栏按钮( start Analysis & synthesis

等待编译结果,不能出现error错误

如出现error,则会给出相应的错误提示,

编译通过后,对管脚进行分配,点击工具栏按钮 (pin planner)

双击location (蓝条)为输入输出配置引脚。

管脚分配后再对整体进行编译,点击工具栏按钮

start Complilation

等待,忽视warning

四、仿真:

建立波形文件。以观察信号输入、输出波形 File-> New->Vector Waveform File

进入波形编辑窗口。

• 双击此空白处,弹出对话框

• 创建输入、输出向量。单击Node Finder,出现选择节 点窗口

• 单击list,显示所有管脚,可选择。如全选,单击输入波形。 • 单击要编辑的输入波形,出现蓝色,用按钮 对波形进行设置。

EDA软件应用与开发

7

3.4.2.1 基本编码实践--命名规则

E D A 软 件 应 用 与 开 发

Rule - Develop a naming convention for the design

Use lowercase letters for signal names, variable names, and port names Use uppercase letters for constants and user-defined types In hierarchy design keep the top module or sub top module’s entity name same as its file name. Use meaningful names Keep parameter names short, but descriptive

结构类型

综合模型

举例

ARCHITECTURE rtl OF my_syn_model IS OR ARCHITECTURE str OF my_syn_model IS

模拟模型

ARCHITECTURE sim OF my_syn_model IS OR ARCHITECTURE tb OF my_syn_model IS

Declare one port per line Declare the ports in the following order: Input Input Output Output

Clocks Clocks Resets Resets Enables Enables Other Control signals Other Control signals Data and address lines Data and address lines

可编程逻辑器件编程技术_b

电信学院 电子系 信号与信息处理研究所

powered by dlut ee 1

本课程参考资料

一、MAXPLUSEII 入门 马群生 二、VHDL程序设计 曾繁泰 清华大学 三、VHDL 语言100例详解 北京理工大学 四、 VHDL语言程序设计 姜立东 北京邮电 五、 六、

原理图/VHDL文本输入设计流程

STEP1:建立 工作库文件夹

STEP2:输入设计项目 原理图/VHDL文本代码

STEP3:存盘,注意 原理图/文本取名

STEP4:将设计项 目设置成Project

STEP5:选 择目标器件

STEP11: 硬件测试

STEP10:编程 下载/配置

STEP9:引脚 锁定并编译

• “ tell me what hardware you want and I will give it to you”

– VHDL is what you write is what functional you get

• “ tell me how your circuit should behave and the VHDL compiler will give you the hardware that does the job” • but the designer can not control how the circuit implement

………..

逻辑综合器

FPGA/CPLD 器件和电路系统

FPGA/CPLD 编程下载

时序与功能 门级仿真

第三方提供

powered by dlut ee

12

VHDL 设计流程 : V-S-F-P

VHDL

synplify与Xilinx ISE 的使用

Synplify and Synplify Pro synthesis and OptionsSynplify is a synthesis tool that can effectively synthesize VHDL, Verilog and Mixed language designs to create EDIF netlists. For detailed information about using Synplify tool to get best results, please refer to the Synplify and Synplify Pro user guide or Synplify On Line HelpISE works with Synplify / Synplify Pro 6.1 and onward. When Synplify is installed, it sets proper values in the windows registry. ISE makes use of these values in the registry to invoke the latest version of Synplify. Also ISE needs Synplify to have a floating license in order to make use of Synplify’s batch mode capability.Following Xilinx device families are supported by Synplify and ISE package - Spartan, Spartan-II, SpartanXL, Virtex, Virtex-E, Virtex2, XC4000E, XC4000EX, XC4000L, XC4000XL, XC4000XLAA. Setting Synplify/Synplify Pro as your synthesis tool1.Create an ISE project using File->New menu button or open an existing ISE project.2.Select your project in the source window of project navigator.3.Right click and choose "Properties…" option to set Synplify/Synplify Pro as your synthesis tool.4.Also choose the family and the device to be used for implementation in this option.B. Setting Synplify and Synplify Pro optionsBefore you synthesize your design, you can set a variety of options for Synplify/Synplify Pro.For complete description of these options, please refer to the design constraints section in the Synplify / Synplify Pro user guide or Synplify On Line Help.1.Select your top-level design in the source window of project navigator.2.To set the options, right click on "Synthesize" in the process window of Project Navigator.3.Select "Properties…" to display synthesis options in the process properties dialog box.4.Set the desired synthesis, VHDL specific, Device and Constraint file options.Following is a list of options:Synthesis Options•Symbolic FSM compiler - Default value is ON.The Symbolic FSM Compiler is an advanced state machine optimizer, which automatically recognizes state machines in your design and optimizes them. Unlike other synthesis tools that treat state machines as regular logic, the FSM Compiler extracts the state machines as symbolic graphs, and then optimizes them by re-encoding the state representations and generating a better logic optimization starting point for the state machines. The FSM Explorer uses the state machines extracted by the FSM Compiler when it explores different encoding styles.•Resource sharing - Default value is ON.Check the resource sharing option when you set implementation options. With this option checked, the software shares hardware resources like adders, multipliers, and counters wherever possible, and minimizes area.•Frequency - Default value is 0 indicating area optimization.For timing-driven synthesis, explicitly define the clock frequency. The software will use the global clock frequency for timing-driven synthesis.•Implementation NameAn implementation is one version of a project, run with a certain set of options. You can synthesize again with another set of options to get another implementation. Synplify allows you to display multiple implementations in the same Project view.•Top Level ModuleThis is the name of the top-level module being synthesized.•Write Mapped Verilog Netlist - Default value is OFF.Set this option to create a verilog netlist for the mapped design.•Write Mapped VHDL Netlist - Default value is OFF.Set this option to create a VHDL netlist for the mapped design.•Write Vendor Constraint File - Default value is ON.Synplify/Synplify Pro forward annotates user specified design constraints through a vendor constraint file. Set this option to enable/disable creation of this (NCF) file.VHDL Specific Options•Default Enum Encoding Goal - Default value is ’Default’.You can set the default enumeration encoding. This is only for enumerated types; state-machine encoding is selected by the FSM compiler or specified using the syn_encoding attribute. Synplify selects the encoding style based on the number of values of the enumerated type. It can be onehot, gray or sequential encoding. Setting a value of ’default’ for this option will enable Synplify to choose this automatically. Otherwise the specified value is used.•Set LibraryYou can specify the VHDL library name. This command is used primarily for compatibility with VHDL simulators.Device Options•Modular flow (Synplify Pro Only) - Default value is OFF.Synplify Pro supports the Xilinx modular design through different attributes. You can enable this capability by setting the "Modular flow" option.•Use FSM Explorer data (Synplify Pro Only) - Default value is OFF.Synplify Pro provides a powerful capability called FSM explorer. It explores various state encodings for the state machines in your design and then chooses the best encoding based on the design constraints. You can enable this capability by setting the "Use FSM explorer data" option.•Pipelining (Synplify Pro Only) - Default value is OFF.Synplify Pro can perform pipelining for multipliers and ROMs. It can move registers in to the logic for these blocks to reduce the critical path delay. This can improve results significantly for your designs.•Disable I/O insertion - Default value is OFF.You can enable/disable insertion of IO pads in your design through this option.•Fanout Guide - Default value is 100.You can specify a global fanout constraint on all the nets in your design. This is useful in keeping net fanout from becoming too large and causing any problems in the routing.•Result File NameYou can specify the name of the file in which Synplify/Synplify Pro will write the design netlist to be used for implementation.•Result Format - Default is edif.You can specify the design netlist format. It can be either edif or xnf.Constraint Files Options•Constraints File NameSynplify/Synplify Pro provides a very easy to use and powerful constraint editor. You can specify a constraint file name to be used for saving the design constraints. If a file with the specified name exists then it will be opened when ’Edit Constraints’ option is chosen.C. Editing a Constraint FileYou can make use of powerful constraint editor (SCOPE) provided with Synplify/Synplify Pro to edit or add constraints for your design. Double click on "Edit Constraints…" option in the process window to bring up the Constraint Editor.D. Synthesizing a DesignWhen a design is ready to synthesize, you can invoke Synplify or Synplify Pro within the Project Navigatorby choosing "Launch Synplify" option under the Synthesis Folder.To synthesize a design:1.Select a source file in the source window.2.Double click "Synthesize" in the process window.E. Viewing a Schematic representation of your designHDL Analyst is a high quality schematic viewer option provided with Synplify/Synplify Pro. You can view the RTL representation created after compilation and Technology representation created after mapping process using this. Double click on the "Launch RTL viewer" or "Launch Technology Viewer" options to achieve this.F. Viewing a Synthesis ReportWhen synthesis is complete, you can view the results by double clicking "View Compile Report" or "View Map Report" in the Process window.G. Known issues/problems1.In Synplify’s case view compile report and view rtl view both depends on the compile process. The same way viewmap report and view tech view depends on map process. Due to which when the compile/map process fails the user has to manually open the *.srr file outside of projnav.2.The constraint file "module_name".sdc gets included if it is present in the project directory. This can sometimesmake the frquency value specified in the properties section to be not used by Synplify.3.Presently compile and mapping in the batch mode is not separate. So when the user tries to compile in Projnav, itgoes through compile and mapping process. That is why when you try to run mapping, it finds all the files up-to-date and puts just the checkmark.。

VHDL_Verilog_mixed_simulation

1.VHDL调用Verilog模块VHDL调用Verilog模块的时候,要在实例化模块前,加上“verilogmodelGM:”VHDL调用verlogverilog module:module m(a,b,c);input a,b;output c;...endmodule调用如下:compoent mport(a: in std_logic;b: in std_logic;c: out std_logic);end compoentbeginverilogmodelGE: mport map(...)...end在VHDL里调用Verilog的话:例化+映射在Verilog里调用VHDL的话:只要映射2.一个VHDL testbench的实例以下为文件名为testbench.vhd的文件,library IEEE;use IEEE.std_logic_1164.all;entity testbench isend entity testbench;architecture test_reg of testbench iscomponent dff isPORT (d,clk,rst:IN STD_LOGIC;q: OUT STD_LOGIC);end component;signal clock: std_logic:='0';signal d,rst:STD_LOGIC;signal q:STD_LOGIC;constant ClockPeriod : TIME := 50 ns;beginUUT : dff port map (d=>d, clk=>clock, rst=>rst,q=>q);generate_clock : PROCESS (clock)BEGIN -- processclock <= NOT clock AFTER ClockPeriod/2;END PROCESS;process begind<='0';rst<='1';wait for 100 ns;d<= '1';wait for 50 ns;rst<='0';wait for 50 ns;d<='0';wait for 100 ns;d<='1';wait for 50 ns;rst<='1';wait;end process;end architecture test_reg;以下为文件为的异步dff.vhd文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY dff ISPORT (d,clk,rst:IN STD_LOGIC;q: OUT STD_LOGIC);END dff;ARCHITECTURE behavior OF dff ISBEGINPROCESS(rst,clk)BEGINIF(rst='1') THENq<='0';ELSIF(clk'EVENT AND clk='1') THENq<=d;END IF;END PROCESS;END behavior;以上两个文件放在同一个project下,仿真结果如下图所示:以下为文件为的同步dff.vhd文件:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY dff ISPORT (d,clk,rst:IN STD_LOGIC;q: OUT STD_LOGIC);END dff;ARCHITECTURE behavior OF dff ISBEGINPROCESS(rst,clk)BEGINIF(clk'EVENT AND clk='1'') THENIf(rst=‟1‟) q<='0';Else q<=d; end if;END IF;END PROCESS;END behavior;3.VHDL描述D-latchlibrary IEEE;use ieee.numeric_bit.all;entity D_latch isport(D, CLK : in bit;Q, : out bit);end D_latch;architecture D_latch_inside of D_latch isbeginprocess(D, CLK)beginif CLK = …1‟ thenQ <= D;end if;end process;end D_latch_inside;4.在时钟上升分支中存在选择语句的情况:LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY dff ISPORT (d,clk,rst,cs:IN STD_LOGIC;q: OUT STD_LOGIC);END dff;ARCHITECTURE behavior OF dff ISsignal temp: STD_LOGIC;BEGINPROCESS(rst,clk)BEGINIF(rst='1') THENtemp<='0';ELSIF(clk'EVENT AND clk='1') THENif(cs='1') then temp<=d;else temp<=temp; end if;END IF;q<=temp;END PROCESS;END behavior;原理图如下:实现的器件图如下:由上面两图可见,在时钟上升沿中出现的选择分支的选择条件cs成为触发器的使能端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

– in:

• signal values are read-only

– out:

• signal values are write-only • Possible to have multiple drivers <- Depends on type of port, will discuss later

– buffer:

• comparable to out • signal values may be read, as well • only 1 driver

– inout:

• bidirectional port

Types of VHDL Ports / Signals

• VHDL a strongly typed language, so all types assigned between signals and ports have to match • Standard VHDL Types:

• How does design translate during synthesis?

– Sensitivity list is usually ignored during synthesis (It is NOT ignored during simulation) – A bad sensitivity list could give you a design that looks like it works during simulation, but could synthesize to something that doesn’t!

Arithmetic Operations

• Arithmetic operators you will want to use are included in the NUMERIC_STD package

– Include its libraries with this command

• use ieee.numeric_std.all;

• Gives you error messages in cases of multiple concurrent signal assignments • More work to do arithmetic as type conversions are needed, some libraries predefined for std_logic

Understanding Synthesis

• Latches

– Happen when you have incomplete assignment statements, synthesizer then infers that you want to have memory (this is in an un-clocked process) – Example: architecture WRONG of MUX is begin process (A, B, SEL) begin if SEL = `1` then Z <= A; end if; end process; end WRONG; – Why is a latch generated for Z instead of a logic path?

VHDL And Synthesis Review

VHDL In Detail

• Things that we pes – Arithmetic Operators – Design styles for Synthesis

VHDL Ports

Understanding Synthesis

• Example of Register

– process(CLK, RST) begin if (CLK`event and CLK=`1`) then -- combinatorics end if; end process;

OR

– Here can use function to check for rising edge of clock, synthesizer may or may not support this – process(CLK, RST) begin if (rising_edge(CLK) then -- combinatorics end if; end process;

•

**Cant have any other elsif, else in main outer if block!! Nested if blocks ok!!

Understanding Synthesis

• Example of asynchronous reset FlipFlop process(CLK, RST) begin if (RST = `1`) then -- asynchronous register reset elsif (CLK`event and CLK=`1`) then -- combinatorics --Signals assigned here inferred as FF’s, reg end if; end process;

– STD_LOGIC AND STD_LOGIC_VECTOR

• When multiple signal assignments present uses resolution function to decide which signal ‘wins’ over the other signal and is assigned, or whether an unknown signal is assigned • Can use the port mode “buffer” to overcome the resolution function being used (buffer allows only a single signal driver)

Understanding Synthesis

• Clocked Processes

– In synthesis all assignments to signals inside a clocked process will make those signals stored as memory (flip-flop, registers) – Have to follow a certain format for this to happen

• NOTE: Can use Logical and Comparison operators directly on std_logic and std_logic_vector types without type conversion!

– i.e. – not, and, <, =, /=

Understanding Synthesis

• Need to have a clock event in the sensitivity list (or wait on clk’event statements) • For single edge triggered need to check for specified edge (can do dual edge triggered by checking for both edges)

Understanding Synthesis

• Correct way to do assignment statements with “if statements” architecture OK_1 of MUX is begin process (A, B, SEL) begin Z <= B; if SEL = `1` then Z <= A; end if; end process; end OK_1; • For CASE statements, can use the default case (“when others”), and assign signals there to avoid latches

• Might have to convert std_logic_vector to signed or unsigned type if compiler complains • Typecasting to unsigned

– someSignalUnsignedType <= 6 + unsigned(someSignal)

• Have two basic modes of operation

– Signed : 2-complement (sign+absolute value) – Unsigned : binary representation of positive integers

Arithmetic Operators

VHDL Types

• However instead of using bits, or bit vectors better to use the Std_Logic_1164 types:

– Instead of a simple 0 or 1 have more states that you can use during simulation to get more information on what is going on with design – TYPE STD_ULOGIC IS ( `U`, -- uninitialized `X`, -- Forcing Unknown `0`, -- Forcing 0 `1`, -- Forcing 1 `Z`, -- High Impedance `W`, -- Weak Unknown `L`, -- Weak 0 `H`, -- Weak 1 `-`, -- don`t care); – To use Std_Logic_1164 need to include its library with command