AD布线方法汇总

AltiumDesigner PCB布局布线过程与技巧

AltiumDesigner PCB布局布线过程与技巧首先是原理图设计。

原理图设计是前期准备工作,对简单的板子,如果熟练流程,不妨可以跳过。

但是对于初学者一定要按流程来,这样一方面可以养成良好的习惯,另一方面对复杂的电路也只有这样才能避免出错。

在画原理图时,层次设计时要注意各个文件最后要连接为一个整体,这同样对以后的工作有重要意义。

由于,软件的差别有些软件会出现看似相连实际未连(电气性能上)的情况。

如果不用相关检测工具检测,万一出了问题,等板子做好了才发现就晚了,这也显示出按顺序来做的重要性了接下来重点讨论具体制板的过程与技巧1.制作物理边框place>line,然后画框并选取框,最后design>board shape>define from selected objects,完成!主要是要注意精确,否则以后出现安装问题麻烦可就大了。

还有就是拐角地方最好用圆弧,一方面可以避免被尖角划伤,同时又可以减轻应力作用。

2.元件和网络的引入打开原理图,选择Design>Update PCB Document...常见问题:元件的封装形式找不到,元件网络问题,有未使用的元件或管脚,对照提示这些问题可以很快搞定的。

3.元件的布局元件的布局与走线对产品的寿命、稳定性、电磁兼容都有很大的影响,是应该特别注意的地方。

一般来说应该有以下一些原则:(1)放置顺序先放置与结构有关的固定位置的元器件,如电源插座、指示灯、开关、连接件之类,这些器件放置好后用软件的LOCK功能将其锁定,使之以后不会被误移动。

再放置线路上的特殊元件和大的元器件,如发热元件、变压器、IC等。

最后放置小器件。

(2)注意散热元件布局还要特别注意散热问题。

对于大功率电路,应该将那些发热元件如功率管、变压器等尽量靠边分散布局放置,便于热量散发,不要集中在一个地方,也不要高电容太近以免使电解液过早老化。

4.布线通行的布线原则。

◆高频数字电路走线细一些、短一些好◆大电流信号、高电压信号与小信号之间应该注意隔离(隔离距离与要承受的耐压有关,许多情况下为避免爬电,还在印制线路板上的高低压之间开槽。

Altium_Designer教程交互式布线篇

Altium Designer 交互式布线8月14日2008SEED Altium Designer 教程以Altium公司的2008新版EDA集成开发系统Altium Summer 08为模板进行讲解,Altium Summer 是Altium Designer 6.9的升级版,大家可以叫他AD7,本教程绝大部分可以在Altium Designer V6 上通用。

我写这篇教程的目的在于交流学习,没有什么版权问题,大家如果觉得好,可以随便转载。

SEED 菜鸟级教程第一篇之Interactive Routing启动Altium Summer 08 启动画面如下图:大家在左上角可以看到Bulid 7.0.0.13815 这就是版本号即7.0版本,细分就是7.0.0.13815右边中间有Licensed to SEED 表示证书授权于SEED,就是我咯^_^,盗版的……同时启动时会加载很多组件,大家在屏幕上可以看到其中一个Starting Project Manager…下面就进入Interactive Routing 的讲解把Altium Summer 08 启动完毕后请选择一个PCB 文件打开,具体步骤如下:File>Open选择打开文件的路径,选择一个PCB文件打开大家可以进入Examples里选择一个PCB 文件3现在打开了一个PCB文件,如下图:点击左上方的DXP>Preferences4接下来出现Preferences框,如下图,大家可以看到有System Schematic FPGA等12个大类我们选择PCB Editor> Interactive Routing 进入交互式布线设置,下图就是交互式布线设置对话框从上图我们可以看到PCB Editor-Interactive Routing 里的7个相关设置Routing Conflict ResolutionDragingInteractive Routing OptionsSmart Connection Pad ExitsInteractive Routing Width/Via Size SourcesFacorite Interactive Routing WidthsFacorite Interactive Routing Via SizesⅠ、Routing Conflict Resolution 篇下面对上面几个设置选项进行说明Routing Conflict Resolution 篇从上面可以看到Routing Conflict Resolution 对应有None,Push Conflicting Object ,Walk Around Conflicting Object,Hug And Push Conflicting Objec 4个布线方式Routing Conflict Resolution 篇之None7回到PCB环境中进行None下的布线,这种方式布线就是常规式布线,你想连哪里就可以拖动鼠标移动到哪里,等介绍玩下面3种布线方式大家就会知道None与其他布线方式的区别了,在其它3种布线模式下将不能连接不同的网络,比如VCC连接到GND,光标始终停留在GND外围。

AD布线规则(自己整理)

一、PCB板的元素1、工作层面对于印制电路板来说,工作层面可以分为6大类,信号层(signal layer)内部电源/接地层(internal plane layer)机械层(mechanical layer)主要用来放置物理鸿沟和放置尺寸标注等信息,起到相应的提示作用。

EDA软件可以提供16层的机械层。

防护层(mask layer)包含锡膏层和阻焊层两大类。

锡膏层主要用于将概况贴元器件粘贴在PCB上,阻焊层用于防止焊锡镀在不该该焊接的地方。

丝印层(silkscreen layer)在PCB板的TOP和BOTTOM层概况绘制元器件的外观轮廓和放置字符串等。

例如元器件的标识、标称值等以及放置厂家标记,生产日期等。

同时也是印制电路板上用来焊接元器件位置的依据,作用是使PCB板具有可读性,便于电路的装置和维修。

其他工作层(other layer)禁止布线层 Keep Out Layer钻孔导引层 drill guide layer钻孔图层 drill drawing layer复合层 multi-layer2、元器件封装是实际元器件焊接到PCB板时的焊接位置与焊接形状,包含了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。

元器件封装是一个空间的功能,对于分歧的元器件可以有相同的封装,同样相同功能的元器件可以有分歧的封装。

因此在制作PCB板时必须同时知道元器件的名称和封装形式。

(1)元器件封装分类通孔式元器件封装(THT,through hole technology)概况贴元件封装(SMT Surface mounted technology )另一种经常使用的分类方法是从封装外形分类: SIP单列直插封装DIP双列直插封装PLCC塑料引线芯片载体封装PQFP塑料四方扁平封装SOP 小尺寸封装TSOP薄型小尺寸封装PPGA 塑料针状栅格阵列封装PBGA 塑料球栅阵列封装CSP 芯片级封装(2) 元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸例如 AXIAL-0.3 DIP14 RAD0.1 RB7.6-15 等。

AD布线规则(自己整理)之欧阳索引创编

一、PCB板的元素欧阳家百(2021.03.07)1、工作层面对于印制电路板来说,工作层面可以分为6大类,信号层(signal layer)内部电源/接地层(internal plane layer)机械层(mechanical layer)主要用来放置物理边界和放置尺寸标注等信息,起到相应的提示作用。

EDA软件可以提供16层的机械层。

防护层(mask layer)包括锡膏层和阻焊层两大类。

锡膏层主要用于将表面贴元器件粘贴在PCB上,阻焊层用于防止焊锡镀在不应该焊接的地方。

丝印层(silkscreen layer)在PCB板的TOP和BOTTOM层表面绘制元器件的外观轮廓和放置字符串等。

例如元器件的标识、标称值等以及放置厂家标志,生产日期等。

同时也是印制电路板上用来焊接元器件位置的依据,作用是使PCB板具有可读性,便于电路的安装和维修。

其他工作层(other layer)禁止布线层 Keep Out Layer钻孔导引层 drill guide layer钻孔图层 drill drawing layer复合层 multi-layer2、元器件封装是实际元器件焊接到PCB板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。

元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。

因此在制作PCB板时必须同时知道元器件的名称和封装形式。

(1)元器件封装分类通孔式元器件封装(THT,through hole technology)表面贴元件封装(SMT Surface mounted technology )另一种常用的分类方法是从封装外形分类: SIP单列直插封装DIP双列直插封装PLCC塑料引线芯片载体封装PQFP塑料四方扁平封装SOP 小尺寸封装TSOP薄型小尺寸封装PPGA 塑料针状栅格阵列封装PBGA 塑料球栅阵列封装CSP 芯片级封装(2) 元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸例如 AXIAL-0.3 DIP14 RAD0.1 RB7.6-15 等。

AD实用技巧分享

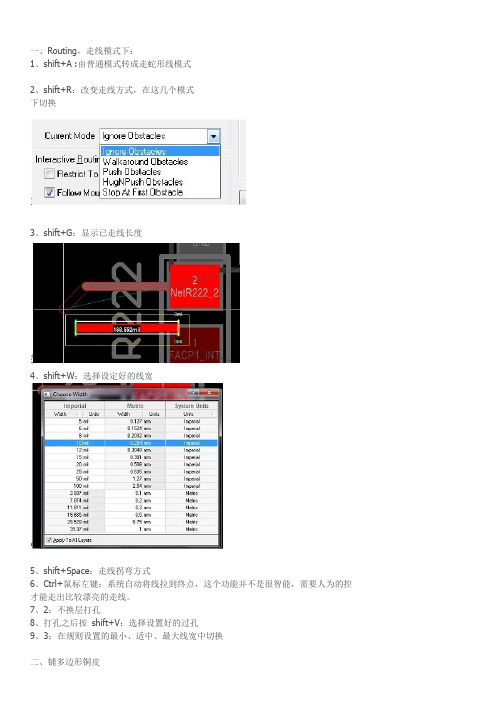

一、Routing,走线模式下:1、shift+A :由普通模式转成走蛇形线模式2、shift+R:改变走线方式,在这几个模式下切换3、shift+G:显示已走线长度4、shift+W:选择设定好的线宽5、shift+Space:走线拐弯方式6、Ctrl+鼠标左键:系统自动将线拉到终点,这个功能并不是很智能,需要人为的控才能走出比较漂亮的走线。

7、2:不换层打孔8、打孔之后按shift+V:选择设置好的过孔9、3:在规则设置的最小、适中、最大线宽中切换二、铺多边形铜皮Tools》Polygon Pours》Define From Selected Objects:在选定的闭合多边形中铺铜框框中间是铜皮。

铜皮离框框的距离是受铺铜规则约束的。

接着双击中间的铜皮修改属性。

这种方法可用于整板灌铜,只需要SY选中外框或者keepout 就行了。

三、内层挖空该技巧出自彭工之手,再次感谢彭工!彭工的无私奉献和钉子精神值得我们学习。

AD挖空是通过用fill 或者polygon 来实现的。

对于简单的方方正正的区域挖空,只需放个fill就搞掂了,可是对于那些奇形怪状的挖空,单单用fill就已经无法得到令我们满意的结果。

这时,就需要用到polygon 了。

下面通过例子来说明这个技巧的实用之处。

现在我们需要对中间部分进行挖空,首先,把所有线都改到keepout 层,并把线宽改成0.01mil。

接着在需要挖空区域打一个地过孔,并把规则里面的铺铜间距改成0.01mil。

接着就在顶层铺地铜,将整个区域都填满,得到下图效果。

接着去掉过孔,并选择Tools》Convert》Explode Polygon to free primitives,将铜皮打碎就可以得出下面效果接下来我想大家都已经不需要我再啰嗦了吧…四、FPGA的Bank设颜色我想做过FPGA的同事都知道,在调FPGA管脚的时候特别麻烦,需要将每个Bank都圈出来。

这是个非常繁琐的事情。

AD9.0布线注意事项及常用快捷键

Ctrl+shift+滚轮放过孔同时切换上下层,同时shift+V可以切换过孔大小。

1、利用原理图设计工具绘制原理图,并且生成对应的网络表。

当然,有些特殊情况下,如电路版比较简单,已经有了网络表等情况下也可以不进行原理图的设计,直接进入PCB设计系统,在PCB设计系统中,可以直接取用零件封装,人工生成网络表。

2、手工更改网络表将一些元件的固定用脚等原理图上没有的焊盘定义到与它相通的网络上,没任何物理连接的可定义到地或保护地等。

将一些原理图和PCB封装库中引脚名称不一致的器件引脚名称改成和PCB 封装库中的一致,特别是二、三极管等。

二、画出自己定义的非标准器件的封装库建议将自己所画的器件都放入一个自己建立的PCB 库专用设计文件。

三、设置PCB设计环境和绘制印刷电路的版框含中间的镂空等1、进入PCB系统后的第一步就是设置PCB设计环境,包括设置格点大小和类型,光标类型,版层参数,布线参数等等。

大多数参数都可以用系统默认值,而且这些参数经过设置之后,符合个人的习惯,以后无须再去修改。

2、规划电路版,主要是确定电路版的边框,包括电路版的尺寸大小等等。

在需要放置固定孔的地方放上适当大小的焊盘。

对于3mm 的螺丝可用6.5~8mm 的外径和3.2~3.5mm 内径的焊盘对于标准板可从其它板或PCB izard 中调入。

注意:在绘制电路版地边框前,一定要将当前层设置成Keep Out层,即禁止布线层。

四、打开所有要用到的PCB 库文件后,调入网络表文件和修改零件封装这一步是非常重要的一个环节,网络表是PCB自动布线的灵魂,也是原理图设计与印象电路版设计的接口,只有将网络表装入后,才能进行电路版的布线。

在原理图设计的过程中,ERC检查不会涉及到零件的封装问题。

因此,原理图设计时,零件的封装可能被遗忘,在引进网络表时可以根据设计情况来修改或补充零件的封装。

当然,可以直接在PCB内人工生成网络表,并且指定零件封装。

ad布线规则自己整理

一、PCB板的元素1、工作层面对于印制电路板来说,工作层面可以分为6大类,信号层(signal layer)内部电源/接地层(internal plane layer)机械层(mechanical layer)主要用来放置物理边界和放置尺寸标注等信息,起到相应的提示作用。

EDA软件可以提供16层的机械层。

防护层(mask layer)包括锡膏层和阻焊层两大类。

锡膏层主要用于将表面贴元器件粘贴在PCB上,阻焊层用于防止焊锡镀在不应该焊接的地方。

丝印层(silkscreen layer)在PCB板的TOP和BOTTOM层表面绘制元器件的外观轮廓和放置字符串等。

例如元器件的标识、标称值等以及放置厂家标志,生产日期等。

同时也是印制电路板上用来焊接元器件位置的依据,作用是使PCB板具有可读性,便于电路的安装和维修。

其他工作层(other layer)禁止布线层Keep Out Layer钻孔导引层 drill guide layer钻孔图层 drill drawing layer复合层 multi-layer2、元器件封装是实际元器件焊接到PCB板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。

元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。

因此在制作PCB板时必须同时知道元器件的名称和封装形式。

(1)元器件封装分类通孔式元器件封装(THT,through hole technology)表面贴元件封装(SMT Surface mounted technology)另一种常用的分类方法是从封装外形分类:SIP单列直插封装DIP双列直插封装PLCC塑料引线芯片载体封装PQFP塑料四方扁平封装SOP 小尺寸封装TSOP薄型小尺寸封装PPGA塑料针状栅格阵列封装PBGA塑料球栅阵列封装CSP 芯片级封装(2)元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸例如AXIAL-0.3 DIP14 RAD0.1 RB7.6-15 等。

altium designer如何布蛇形线

蛇行等长线布线方法Altium Designer 6.x 软件更新速度很快,现在都有AD7了,以前一直用99SE,没想到AD6的功能越来越强大了,在操作方面做了很大改进,特别是在布等长线时,蛇行线的布线那是太容易了。

一.设置需要等长的网络组点击主菜单DesignàClasses,在弹出的窗口中单击Net Classes,并右键,点AddClass会增加一个New Class,在该网络组上右键,修改一个你想要的名字,如:SDRAM 等。

单击打开它,将需要等长的网络,从左边选取并添加到右边的窗口中。

然后再点击close 关闭设置。

二. 布线在布蛇行线时,只能在已经布好的线上修改,不能直接拉蛇线,所以得先布线,把所有SDRAM Class 的网络用手工(不推荐用自动)的方式布完线,走线尽量的短,尽量的宽松,也就是说间距留大一点。

应该把最长的那一根做为基准,把它尽量的布短一点。

三. 走蛇行线等长按T ,R键,单击一根走线,再按TAB键,设置一下先1.选中Form NET 在右边的网络中,选中一根你想要长度的网络,一般选最长的那根2.也就是说,以后的自动等长中,将会以些为基准,所有需等长的线将会跟它一样长。

2.蛇行设置这里为蛇行线的样式,可以根据自己的需要选择.2. 布蛇行线的快捷键控制:在布蛇行线时,按快捷键“1”“2”“3”“4”“,”“。

”可以在走线时随时控制蛇行线的形状。

快捷键: 1 与2,改变蛇行线的拐角与弧度。

快捷键: 3 与4 改变蛇行线的宽度。

快捷键:,与。

改变蛇行线的幅度。

了解了这些,就可以开始布蛇行线了,单击OK 退出设置,在刚才那条线上,按装走线的方向,拉动鼠标,一串漂亮的蛇行线就出来了。

蛇行线幅度步长幅度递增量步长递增量规定了蛇线的长度,在拉蛇线时,就不用在乎到底走了多长,总之,拉到蛇线不再出现为止,在有些空隙大的地方,就可以按“逗号”与“句号”键来控制幅度的大小。

四. 检查网络长度布完线后,按R ,L 输出报告,查看网络是否是等长的。

最新AD布线规则(自己整理)

一、PCB板的元素1、工作层面对于印制电路板来说,工作层面可以分为6大类,信号层(signal layer)内部电源/接地层(internal plane layer)机械层(mechanical layer)主要用来放置物理边界和放置尺寸标注等信息,起到相应的提示作用。

EDA软件可以提供16层的机械层。

防护层(mask layer)包括锡膏层和阻焊层两大类。

锡膏层主要用于将表面贴元器件粘贴在PCB上,阻焊层用于防止焊锡镀在不应该焊接的地方。

丝印层(silkscreen layer)在PCB板的TOP和BOTTOM层表面绘制元器件的外观轮廓和放置字符串等。

例如元器件的标识、标称值等以及放置厂家标志,生产日期等。

同时也是印制电路板上用来焊接元器件位置的依据,作用是使PCB板具有可读性,便于电路的安装和维修。

其他工作层(other layer)禁止布线层Keep Out Layer钻孔导引层 drill guide layer钻孔图层 drill drawing layer复合层 multi-layer2、元器件封装是实际元器件焊接到PCB板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。

元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。

因此在制作PCB板时必须同时知道元器件的名称和封装形式。

(1)元器件封装分类通孔式元器件封装(THT,through hole technology)表面贴元件封装(SMT Surface mounted technology)另一种常用的分类方法是从封装外形分类:SIP单列直插封装DIP双列直插封装PLCC塑料引线芯片载体封装PQFP塑料四方扁平封装SOP 小尺寸封装TSOP薄型小尺寸封装PPGA塑料针状栅格阵列封装PBGA塑料球栅阵列封装CSP 芯片级封装(2)元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸例如AXIAL-0.3 DIP14 RAD0.1 RB7.6-15 等。

高速ADC PCB的布局布线技巧

高速ADC PCB 的布局布线技巧在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。

最终的答案各不相同,但在所有情况下,设计工程师都应尽量消除最佳做法的误差,而不要过分计较布局布线的每一个细节。

今天为各位推荐的这篇文章,将从裸露焊盘开始,依次讲述去耦和层电容、层耦合、分离接地四部分讲述。

裸露焊盘裸露焊盘(EPAD)有时会被忽视,但它对充分发挥信号链的性能以及器件充分散热非常重要。

裸露焊盘,ADI 公司称之为引脚0,是目前大多数器件下方的焊盘。

它是一个重要的连接,芯片的所有内部接地都是通过它连接到器件下方的中心点。

不知您是否注意到,目前许多转换器和放大器中缺少接地引脚,原因就在于裸露焊盘。

关键是将此引脚妥善固定(即焊接)至PCB,实现牢靠的电气和热连接。

如果此连接不牢固,就会发生混乱,换言之,设计可能无效。

实现最佳连接利用裸露焊盘实现最佳电气和热连接有三个步骤第一、在可能的情况下,应在各PCB 层上复制裸露焊盘,这样做的目的是为了与所有接地和接地层形成密集的热连接,从而快速散热。

此步骤与高功耗器件及具有高通道数的应用相关。

在电气方面,这将为所有接地层提供良好的等电位连接。

甚至可以在底层复制裸露焊盘,它可以用作去耦散热接地点和安装底侧散热器的地方。

第二、将裸露焊盘分割成多个相同的部分,如同棋盘。

在打开的裸露焊盘上使用丝网交叉格栅,或使用阻焊层。

此步骤可以确保器件与PCB 之间的稳固连接。

在回流焊组装过程中,无法决定焊膏如何流动并最终连接器件与PCB。

连接可能存在,但分布不均。

可能只得到一个连接,并且连接很小,或者更糟糕,位于拐角处。

将裸露焊盘分割为较小的部分可以确保各个区域都有一个连接点,实现更牢靠、均匀连接的裸露焊盘。

第三、应当确保各部分都有过孔连接到地。

各区域通常都很大,足以放置多个过孔。

组装之前,务必用焊膏或环氧树脂填充每个过孔,这一步非常重要,可以确保裸露焊盘焊膏不会回流到这些过孔空洞中,影响正确连接。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD15布线方法汇总

1.常规布线:最基本的交互式布线,快捷键P+T。需要说明的是在布线过程中,可按小键盘的*键或大键盘的数字2

键添加一个过孔;按L键可以切换布线层;按数字3可设定最小线宽、典型线宽、最大线宽的值进行切换。

2.总线式布线:通俗的讲就是多条网络同事布线的问题。具体方法是,按住SHIFT,然后依次用光标移到要布线的

网络,点击鼠标左键即可选中一条网络,选中所需的所有网络以后,单击工具栏汇的总线布线图标(P+M),在被选

网络中任意单击即可开始多条网络同时布线。布线过程中可以按键盘上左右尖括号<>调节线间距。

3.差分对布线:差分网络是两条存在耦合的传输线,一条携带信号,另一条则携带它的互补信号。使用差分对布线

前要对设定差分对网络进行设置。设置可以在原理图中设置,也可以在PCB中进行设置。

a 原理图中添加差分对规则: 在命名差分对网络时,必须保证网络名的前缀是一样的,后缀中用下划线带一个

N和一个P字母即可。命名好之后点击菜单Place-Directives-DifferntialPair命令,在差分对上放置两个差分对

图标。单击菜单Design-Update PCB Document ****在打开的对话框中重新传差一次修改规则即可在PCB中进行差

分对布线。

b.在PCB中添加差分对布线规则(较快捷):选择右下角的快捷菜单PCB打开左侧PCB面板,从面板第一栏中

选择Differential Pairs Editor,单击add,在打开的差分对设置对话框中选定要定义成差分对的网络,然后在

Name栏内输入一个差分对名称单击OK退出设置,之后就可以进行差分布线了。

单击工具栏中的差分对布线图标(P+I),软件自动将网络高亮显示,在差分对网络上单击开始布线,布线过

程中可以通过按住Ctrl+Shift,同时转动鼠标滚轮添加过孔和换层操作。

4.蛇形走线:蛇形线主要用于匹配高速信号延时,通常采用等长调节实现,数字电路中有时需要使用独立的蛇形

走线,比如增加写信号的延时,以增加数据总线的建立时间。单击工具栏中的交互式布线图标进入交互布线

(P+T),在布线过程中按键盘SHIFT+A即可切换到蛇形布线模式,按数字1、2键可调整蛇形线倒角,按3、4键

可调节间距,按<>键可调节蛇形线幅度。

5.交互布线等长调节:先将线路布完,需要提前留出蛇形走线空间。单击工具栏中交互式布线长度调节(T+R),

单击一根走线,再按TAB键,弹出等长线设置对话框,等长线的约束类型选择“手动”,设置的长度需要按照最

长的线长度作为基准,然后设置好目标长度和蛇形走线布线规则后即可进行长度调节。所有的线长完全调整完

后,按R、L输出报告,查看网络是否是等长。该工具还可以检查其他已布好线的网络长度。注意蛇形走线布线规

则决定了每个蛇形弯的长度,调整网线时增加的长度只能是蛇形弯的长度的整倍数。

6.差分对等长调节。先将线路布完,需要提前留出蛇形走线空间。单击工具栏中交差分线长度调节(T+I),选中差

分线中一根走线,再按TAB键,弹出等长线设置对话框,约束类型选择“手动”,设置好目标长度和蛇形走线布线

规则后即可进行长度调节,其余同5。

7.网络等长调节。该操作属于批处理,需要先定义批处理对象-网络类,和每一个类对应的等长调节规则。

单击菜单“设计”->“类”,在Net Classes选项中添加新类并命名,在新类中添加需要等长布线的网络名称,

然后关闭菜单。可以一次添加多个类,类与类之间采用不同的等长调节规则。

单击菜单“设计->规则”,在High Speed->Matched Length中添加等长约束,名称最好和添加的网络类名称相

对应。新的等长约束的匹配范围选择“网络类”,在右侧下拉选项中选择对应的网络类名称,全部建好后关闭菜单。

所有待调整长度的线应该已经布好并留有足够的蛇形线空间,单击菜单“工具->网络等长”(T+Z),这时每个网

络类中的成员-单个网线,会自动根据所属网络类的等长调节规则进行长度匹配,长度标准自动参考该类中走线最

长的成员,完成后会报告匹配结果。网络等长调整的自动布线一般都比较丑!

如果只想对网络类中一部分成员进行长度调整,需要先将其它已经等长匹配好的走线进行“锁定”,从而不再参

与后续的长度调整。锁定操作:双击网线->勾选“锁定”。如果锁定的网线长度并不符合等长匹配的长度,则该走

线仍然会被重新调整。

** 注意如果存在某个等长约束的匹配范围选择了“所有”,则该规则成为全局约束,可能会报错无法满足所有

网线等长。

8.单键自动布线(几乎没用):主要用于短距离的布线。点击工具栏中交互式布线图标(P+T),然后按住CTRL键,

单击鼠标左键即自动完成布线。

补充一个添加过孔的知识点:快捷键是小键盘的*键。但是对于笔记本来说就要麻烦了呢,按数字2键,再按L键

换层。