wet 半导体工艺

半导体名词解释

1. 何谓PIE PIE的主要工作是什幺答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2. 200mm,300mm Wafer 代表何意义答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋.3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺未来北京的Fab4(四厂)采用多少mm的wafer工艺答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达工艺。

未来北京厂工艺wafer将使用300mm(12英寸)。

4. 我们为何需要300mm答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加倍,芯片数目约增加倍5. 所谓的um 的工艺能力(technology)代表的是什幺意义答:是指工厂的工艺能力可以达到um的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6. 从>>>> 的technology改变又代表的是什幺意义答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从-> -> -> -> 代表着每一个阶段工艺能力的提升。

7. 一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓N, P-type wafer答:N-type wafer 是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3价电荷元素, 例如:B、In)的硅片。

8. 工厂中硅片(wafer)的制造过程可分哪几个工艺过程(module)答:主要有四个部分:DIFF(扩散)、TF(薄膜)、PHOTO(光刻)、ETCH(刻蚀)。

半导体制造工艺流程图

外延层淀积

1.VPE〔Vaporous phase epitaxy> 气相外延生长硅

SiCl4+H2→Si+HCl 2.氧化

Tepi>Xjc+Xmc+TBL-up+tepi-ox SiO2

N-epi

N+-BL

N+-BL

P-SUB

第二次光刻—P+隔离扩散孔

• 在衬底上形成孤立的外延层岛,实现元件的隔离.

• 2.阱区注入及推进,形成阱区

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 3.去除SiO2,长薄氧,长Si3N4

Si3N4

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 4.光II---有源区光刻

Si3N4

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

Wafer Fab、 • 晶圆针测制程〔Wafer Probe; • 後段〔Back End • 构装〔Packaging、 • 测试制程〔Initial Test and Final Test

一、晶圆处理制程

• 晶圆处理制程之主要工作为在矽晶圆上制作电路与 电子元件〔如电晶体、电容体、逻辑闸等,为上述各 制程中所需技术最复杂且资金投入最多的过程 ,以 微处理器〔Microprocessor为例,其所需处理步骤可 达数百道,而其所需加工机台先进且昂贵,动辄数千 万一台,其所需制造环境为为一温度、湿度与 含尘 〔Particle均需控制的无尘室〔Clean-Room,虽然详 细的处理程序是随著产品种类与所使用的技术有关; 不过其基本处理步骤通常是晶圆先经过适 当的清洗 〔Cleaning之後,接著进行氧化〔Oxidation及沈积, 最後进行微影、蚀刻及离子植入等反覆步骤,以完成 晶圆上电路的加工与制作.

半导体器件半导体工艺氧化

氧化率的影响

3、晶向

因为不同晶向其原子密度不同,所以在相同的温度、氧化气压等条件下,原子密度大的晶面,氧化生长速率要大,而且在低温时的线性阶段更为明显。

4、掺杂物

氧化率:高掺杂 > 低掺杂 n型掺杂物:P、As、Sb p型掺杂物:B

5、多晶硅 与单晶硅相比氧化率更快

实际工艺中由于各个部分材料不同,造成氧化层厚度不均匀,出现台阶。

超大规模集成电路生产车间

10

0.3

封装区域

1000~10000

0.5

住房

100 000

室外

>500 000Fra bibliotek章节一

硅——热氧化

CHAPTER ONE

1

列出硅器件中,二氧化硅膜层的基本用途。

2

描述热氧化的机制。

3

列出热氧化反应中的氧化剂及用途。

4

解释氧化条件及基底条件对氧化的影响。

目的

二氧化硅层的用途

干氧 < 湿氧(发泡、干法) < Cl参入氧化

干氧氧化 优点:结构致密、均匀性和重复性好、与光 刻胶黏附好且应力小。 缺点:生长温度高、生长速度慢。

氧化率的影响

2、高压氧化

在实际的工艺过程中增加氧化剂分压来提高氧化速率,或者降低氧化温度而保持同样的氧化速率都是经常采用方法。 优点:有利于降低材料中的位错缺陷。 缺点:在利用高压氧化时要注意安全问题和高压系统带来的污染问题。

集成度(数字MOS集成电路)

小规模集成电路(SSI)

<100

中规模集成电路(MSI)

102~103

大规模集成电路(LSI)

103~105

超大规模集成电路(VLSI)

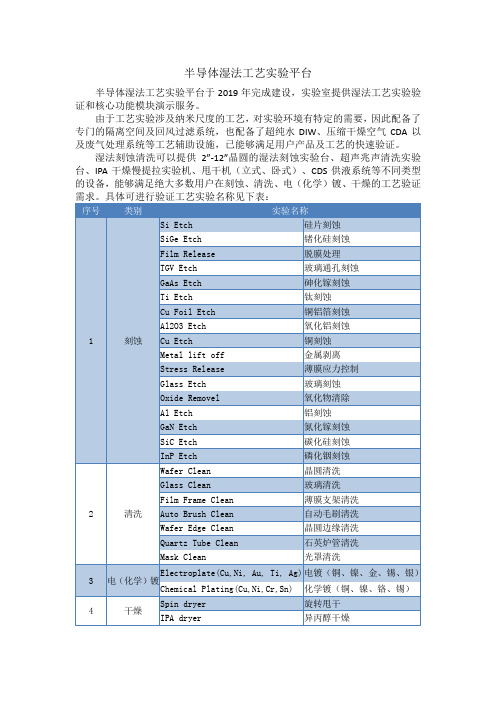

半导体湿法工艺实验平台

半导体湿法工艺实验平台半导体湿法工艺实验平台于2019年完成建设,实验室提供湿法工艺实验验证和核心功能模块演示服务。

由于工艺实验涉及纳米尺度的工艺,对实验环境有特定的需要,因此配备了专门的隔离空间及回风过滤系统,也配备了超纯水DIW、压缩干燥空气CDA以及废气处理系统等工艺辅助设施,已能够满足用户产品及工艺的快速验证。

湿法刻蚀清洗可以提供2”-12”晶圆的湿法刻蚀实验台、超声兆声清洗实验台、IPA干燥慢提拉实验机、甩干机(立式、卧式)、CDS供液系统等不同类型的设备,能够满足绝大多数用户在刻蚀、清洗、电(化学)镀、干燥的工艺验证核心功能模块演示包括超声兆声功能、自动配液功能、循环功能、过滤功能、加热功能、制冷功能、恒温功能、抛动晃动功能等。

➢自动配液:主要用于湿法腐蚀清洗等工序需要使用的腐蚀液集中进行配送,经管道配送至使用端;具有自动化程度高、配比精确(达到2‰)、操作简便等特点,具有耐腐蚀性,可适用于:HF、HNO3、KOH、NH4OH、NaOH、H2SO4、HCL、H2O2、IPA等。

CDS自动配液机➢恒温控温:采用电子冷热交换器,当设定好制程药液所需温度,由控制单元精准控制,则无需别的操作。

通过外接循环水的温度,将药液温度控制精度达到±0.5℃,电子冷热器内部温度控制精度达到±0.1℃,保证多批次清洗、刻蚀效果一致。

电子冷热交换器工作原理示意图电子冷热交换器➢IPA干燥:IPA干燥是利用IPA的低表面张力和易挥发的特性,取代硅片表面的具有较高表面张力的水分,然后用热N2吹干,达到彻底干燥硅片水膜的目的。

➢离心甩干:离心甩干通过外力使晶片短时间内达到高速旋转的状态,晶片表面的水受到离心力作用而从表面消失的干燥技术。

这种干燥方式由于简单可靠,在晶片清洗领域得到了广泛应用。

根据晶片运动方式的不同,离心甩干又分为立式离心甩干(0~3000转)和水平式离心甩干(0~1200转),虽然二者的脱水原理相似,但是由于运动方式的不同,在工艺上有很大的差异。

半导体名词解释(精)

半导体名词解释(精)1. 何谓PIE? PIE的主要工作是什幺?答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2. 200mm,300mm Wafer 代表何意义?答:8吋硅片(wafer)直径为 200mm , 直径为 300mm硅片即12吋.3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm的wafer工艺?答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达0.13um工艺。

未来北京厂工艺wafer将使用300mm(12英寸)。

4. 我们为何需要300mm?答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5倍5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义?答:是指工厂的工艺能力可以达到0.13 um的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6. 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义?答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。

7. 一般的硅片(wafer)基材(substrate)可区分为N,P 两种类型(type),何谓 N, P-type wafer?答:N-type wafer 是指掺杂 negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂 positive 元素(3价电荷元素, 例如:B、In)的硅片。

半导体名词解释

1. 何谓PIE? PIE的主要工作是什幺?答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2. 200mm,300mm Wafer 代表何意义?答:8吋硅片(wafer)直径为 200mm , 直径为 300mm硅片即12吋.3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm的wafer工艺?答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达0.13um工艺。

未来北京厂工艺wafer将使用300mm(12英寸)。

4. 我们为何需要300mm?答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5倍5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义?答:是指工厂的工艺能力可以达到0.13 um的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6. 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义?答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。

7. 一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓 N, P-type wafer?答:N-type wafer 是指掺杂 negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂 positive 元素(3价电荷元素, 例如:B、In)的硅片。

半导体工艺实验报告 【交大】

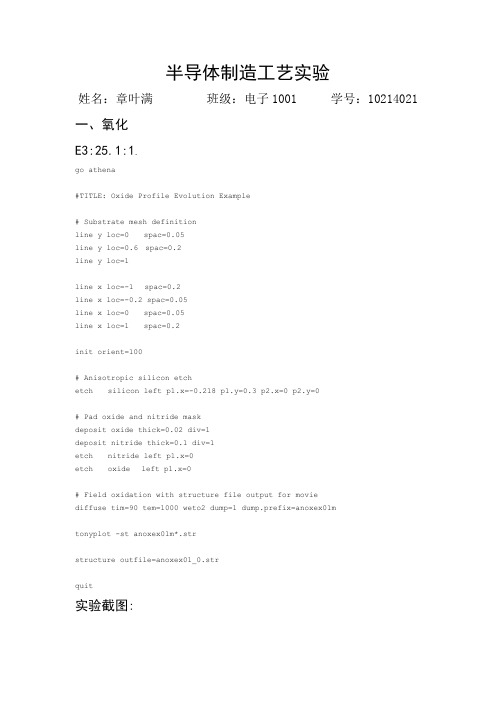

半导体制造工艺实验姓名:章叶满班级:电子1001学号:10214021一、氧化E3:25.1:1.go athena#TITLE: Oxide Profile Evolution Example# Substrate mesh definitionline y loc=0 spac=0.05line y loc=0.6 spac=0.2line y loc=1line x loc=-1 spac=0.2line x loc=-0.2 spac=0.05line x loc=0 spac=0.05line x loc=1 spac=0.2init orient=100# Anisotropic silicon etchetch silicon left p1.x=-0.218 p1.y=0.3 p2.x=0 p2.y=0# Pad oxide and nitride maskdeposit oxide thick=0.02 div=1deposit nitride thick=0.1 div=1etch nitride left p1.x=0etch oxide left p1.x=0# Field oxidation with structure file output for moviediffuse tim=90 tem=1000 weto2 dump=1 dump.prefix=anoxex01mtonyplot -st anoxex01m*.strstructure outfile=anoxex01_0.strquit实验截图:实验分析:当氧扩散穿越已生长的氧化剂时,它是在各个方向上扩散的。

一些氧原子纵向扩散进入硅,另一些氧原子横向扩散。

这意味着在氮化硅掩膜下有着轻微的侧面氧化生长。

由于氧化层比消耗的硅更厚,所以在氮化物掩膜下的氧化生长将抬高氮化物的边缘。

这就是LOCOS 氧化工艺中的“鸟嘴效应”。

半导体名词解释

1.何谓PIE?PIE的主要工作是什幺?答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。

2.200mm,300mm Wafer 代表何意义?答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋.3.目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm的wafer工艺?答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达0.13um 工艺。

未来北京厂工艺wafer将使用300mm(12英寸)。

4.我们为何需要300mm?答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5倍5.所谓的0.13 um 的工艺能力(technology)代表的是什幺意义?答:是指工厂的工艺能力可以达到0.13 um的栅极线宽。

当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。

6.从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义?答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。

从0.35um -> 0.25um -> 0.18um-> 0.15um-> 0.13um 代表着每一个阶段工艺能力的提升。

7.一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓N, P-type wafer?答:N-type wafer 是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3价电荷元素, 例如:B、In)的硅片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

wet 半导体工艺

Wet半导体工艺是半导体制造过程中的重要环节之一。

在半导体工艺中,wet半导体工艺主要用于清洗、去除杂质和形成特定的薄膜。

本文将介绍wet半导体工艺的基本原理、应用和发展趋势。

一、wet半导体工艺的基本原理

wet半导体工艺是利用液体(通常是化学溶液)对半导体材料进行处理的工艺。

其基本原理是通过液体中的化学物质与半导体表面发生反应,改变表面性质或溶解掉不需要的物质。

常见的wet半导体工艺包括清洗、蚀刻和沉积等。

清洗是wet半导体工艺中最基本的一步。

在半导体制造过程中,各种杂质会附着在半导体表面,影响器件性能。

通过将半导体芯片浸泡在适当的化学溶液中,可以去除这些杂质,提高器件的可靠性和性能。

蚀刻是wet半导体工艺中的另一个重要步骤。

蚀刻是指利用化学溶液对半导体表面进行局部溶解,从而形成特定的结构或减少器件尺寸。

蚀刻可以通过控制溶液中的化学物质和蚀刻时间来实现。

常见的蚀刻方法包括湿法蚀刻和干法蚀刻。

湿法蚀刻是利用液体溶液进行蚀刻,而干法蚀刻则是利用气体或等离子体进行蚀刻。

沉积是wet半导体工艺中的另一个重要步骤。

沉积是指将特定材料沉积在半导体表面,形成薄膜或填充孔隙。

常见的沉积方法包括化

学气相沉积(CVD)和物理气相沉积(PVD)。

化学气相沉积是通过化学反应将气体中的化学物质沉积在半导体表面,而物理气相沉积则是通过物理过程将固体材料蒸发或溅射到半导体表面。

二、wet半导体工艺的应用

wet半导体工艺广泛应用于半导体制造的各个环节。

在芯片制造过程中,wet半导体工艺用于清洗半导体表面,去除杂质,确保芯片质量。

在器件制造过程中,wet半导体工艺用于蚀刻半导体表面,形成特定的结构。

此外,wet半导体工艺还用于沉积薄膜,保护半导体表面或改变器件性能。

三、wet半导体工艺的发展趋势

随着半导体技术的发展,wet半导体工艺也在不断演进。

一方面,随着芯片制造工艺的不断精细化,对清洗和蚀刻工艺的要求也越来越高。

因此,新型的清洗剂和蚀刻剂不断涌现,以满足对半导体表面处理的需求。

另一方面,随着半导体器件尺寸的不断缩小,传统的wet半导体工艺面临着挑战。

传统的湿法蚀刻和沉积方法在处理小尺寸结构时存在难以控制的问题。

因此,研究人员正在开发新型的wet半导体工艺,以实现更精确的蚀刻和沉积。

wet半导体工艺还面临着环境污染和资源浪费的问题。

传统的wet 半导体工艺通常需要大量的化学溶液和能源,对环境造成一定的影

响。

因此,研究人员也在探索绿色和可持续的wet半导体工艺,以减少对环境的影响。

wet半导体工艺是半导体制造过程中不可或缺的一部分。

通过清洗、蚀刻和沉积等步骤,wet半导体工艺可以对半导体材料进行处理,使其具有所需的性质和结构。

随着半导体技术的不断发展,wet半导体工艺也在不断演进,以适应新的制造需求和环境要求。