latch up测试标准

ic半导体测试基础(中文版)

i c半导体测试基础(中文版)-CAL-FENGHAI.-(YICAI)-Company One1本章节我们来说说最基本的测试——开短路测试(Open-Short Test),说说测试的目的和方法。

一.测试目的?Open-Short Test也称为ContinuityTest或Contact Test,用以确认在器件测试时所有的信号引脚都与测试系统相应的通道在电性能上完成了连接,并且没有信号引脚与其他信号引脚、电源或地发生短路。

?测试时间的长短直接影响测试成本的高低,而减少平均测试时间的一个最好方法就是尽可能早地发现并剔除坏的芯片。

Open-Short测试能快速检测出DUT是否存在电性物理缺陷,如引脚短路、bond wire缺失、引脚的静电损坏、以及制造缺陷等。

?另外,在测试开始阶段,Open-Short测试能及时告知测试机一些与测试配件有关的问题,如ProbeCard或器件的Socket没有正确的连接。

二.测试方法?Open-Short测试的条件在器件的规格数或测试计划书里通常不会提及,但是对大多数器件而言,它的测试方法及参数都是标准的,这些标准值会在稍后给出。

?基于PMU的Open-Short测试是一种串行(Serial)静态的DC测试。

首先将器件包括电源和地的所有管脚拉低至“地”(即我们常说的清0),接着连接PMU到单个的DUT管脚,并驱动电流顺着偏置方向经过管脚的保护二极管——一个负向的电流会流经连接到地的二极管(图3-1),一个正向的电流会流经连接到电源的二极管(图3-2),电流的大小在100uA到500uA之间就足够了。

大家知道,当电流流经二极管时,会在其P-N结上引起大约的压降,我们接下来去检测连接点的电压就可以知道结果了。

?既然程序控制PMU去驱动电流,那么我们必须设置电压钳制,去限制Open 管脚引起的电压。

Open-Short测试的钳制电压一般设置为3V——当一个Open 的管脚被测试到,它的测试结果将会是3V。

海思消费类芯片可靠性测试技术总体规范V2

海思消费类芯片可靠性测试技术总体规范V2.0海思消费类芯片可靠性测试技术总体规范V2.0是针对芯片可靠性测试的总体规范要求,包括电路可靠性和封装可靠性。

该规范适用于量产芯片验证测试阶段的通用测试需求,并能够覆盖芯片绝大多数的可靠性验证需求。

本规范描述的测试组合可能不涵盖特定芯片的所有使用环境,但可以满足绝大多数芯片的通用验证需求。

该规范规定了芯片研发或新工艺升级时,芯片规模量产前对可靠性相关测试需求的通用验收基准。

这些测试或测试组合能够激发半导体器件电路、封装相关的薄弱环节或问题,通过失效率判断是否满足量产出口标准。

在芯片可靠性测试中,可靠性是一个含义广泛的概念。

以塑封芯片为例,狭义的“可靠性”一般指芯片级可靠性,包括电路相关的可靠性(如ESD、Latch-up、HTOL)和封装相关的可靠性(如PC、TCT、HTSL、HAST等)。

但是芯片在应用场景中往往不是“独立作战”,而是以产品方案(如PCB板上的一个元器件)作为最终应用。

因此广义的“可靠性”还包括产品级的可靠性,例如上电温循试验就是用来评估芯片各内部模块及其软件在极端温度条件下运行的稳定性。

产品级的可靠性根据特定产品的应用场景来确定测试项和测试组合,并没有一个通用的规范。

本规范重点讲述芯片级可靠性要求。

本规范引用了JESD47I标准,该标准是可靠性测试总体标准。

在芯片可靠性测试中,测试组合通常以特定的温度、湿度、电压加速的方式来激发问题。

本规范还新增了封装可靠性测试总体流程图和测试前后的要求,并将《可靠性测试总体执行标准(工业级)》.xlsx作为本规范的附件。

海思消费类芯片可靠性测试技术总体规范V2.0本规范旨在规范海思消费类芯片的可靠性测试技术,确保其性能和质量符合要求。

以下是通用芯片级可靠性测试要求的详细介绍。

2.通用芯片级可靠性测试要求2.1电路可靠性测试电路可靠性测试是对芯片在不同应力条件下的可靠性进行评估的过程。

在测试过程中,需要按照以下要求进行测试:HTOL:在高温条件下进行测试,温度不低于125℃,Vcc不低于Vccmax。

DS_AW8155FCR_CN_V1.0_防破音、超强TDD抑制、超低EMI第二代音乐功放

应用

手机 便携式音频设备 MP3/PMP GPS

版权所有© 2012 上海艾为电子技术有限公司 第 1 页 共 25 页

AW8155 产品手册 2012 年 9 月 V1.0

引脚分布图

AW8155FCR TOP VIEW (俯视图)

3 VOP PGND VON 3

AW8155FCR MARKING (器件标识图)

spec Max. 3℃/sec 60-120sec 60-150sec >260℃ 20-40sec. Max. 6℃/sec Max. 8min.

Setting value Zone 1: 220℃ Zone 2: 197℃ Zone 3: 204℃ Zone 4: 212℃ Zone 5: 257℃ Zone 6: 271℃ Zone 7: 252℃

版权所有© 2012 上海艾为电子技术有限公司 第 2 页 共 25 页

AW8155 产品手册 2012 年 9 月 V1.0

典型应用图

Cs 1μ F Cin 33nF VDD INP INN VOP

Cin

33nF

GPIO

10k

AW8155

CTRL VON

AGND

PGND

图2

AW8155 单端输入方式应用图

概要

AW8155 是一款带防破音、超强 TDD 抑制、 带有 AB 类/D 类输出切换技术和超低 EMI 的第二 代音乐功放。超低失真度,独特的防破音技术消 除播放过程中产生的破音, 带来曼妙的音乐享受。 AW8155 采用艾为专有的 RNS 技术和净音 技术,有效抑制 TDD 噪声的产生。 AW8155 有 0.65W 和 0.85W 两个功率等级, 适用于不同喇叭规格,严格控制功率输出,有效 保护喇叭。 AW8155 内置优异的 Pop-Click 杂音抑制电 路,有效避免了芯片在开启和关断操作时的 Pop-Click 杂音。 AW8155 内置过流保护、过热保护及欠压保 护功能,有效地保护芯片在异常工作状况下不被 损坏。 AW8155 提供纤小 1.5mm×1.5mm FC9 封 装,额定的工作温度范围为-40℃至 85℃。

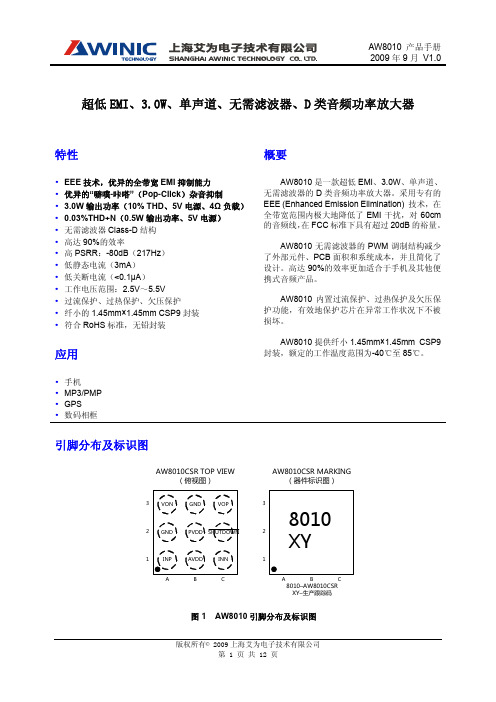

D类功放AW8010相关说明

典型应用图

差分输入

AW8010 产品手册 2009 年 9 月 V1.0

Cs

1µF

Cin Rin 3.3nF 150KΩ 3.3nF 150KΩ Cin Rin

Off On

AVDD PVDD INN

VOP

INP

AW8010

SHUTDOWN

VON

GND

图 2 AW8010 差分输入方式应用图

单端输入

1.20

W

THD+N=1%,f=1kHz,RL=8Ω,VDD=4.2V

1.00

W

THD+N=10%,f=1kHz,RL=4Ω,VDD=3.6V

1.55

W

THD+N=1%,f=1kHz,RL=4Ω,VDD=3.6V

1.25

W

THD+N=10%,f=1kHz,RL=8Ω,VDD=3.6V

0.90

W

THD+N=1%,f=1kHz,RL=8Ω,VDD=3.6V

10

VDD=4.2V Av=2 RL=4Ω+33μH 1

PO=600mW 0.1 PO=300mW

PO=1W

0.01 20

100

1K

FREQUENCY ( Hz )

10K 20K

THD+N (%)

THD+N vs FREQUENCY

10

VDD=3.6V Av=2 RL=8Ω+33μH 1

THD+N vs FREQUENCY

10K 20K

THD+N (%)

THD+N vs FREQUENCY

10

VDD=4.2V Av=2 RL=8Ω+33μH 1

latch up原理

latch up原理Latch-Up原理。

Latch-Up是指在CMOS电路中由于PNP和NPN晶体管的基极和集电极之间的相互耦合而导致的一种电路失效现象。

当CMOS电路中的某些条件满足时,会导致PNP和NPN晶体管同时导通,形成一个正反馈回路,导致电路失效。

在本文中,我们将详细介绍Latch-Up原理及其防护措施。

Latch-Up的原理是由于CMOS电路中的PNP和NPN晶体管之间的相互耦合。

当CMOS电路中的两个晶体管之间的电压差超过一定阈值时,会导致PNP晶体管和NPN晶体管同时导通,形成一个正反馈回路。

由于这个正反馈回路的存在,一旦触发Latch-Up现象,电路将失去控制,导致电路失效。

Latch-Up现象会导致CMOS电路的性能下降甚至损坏,因此需要采取一定的防护措施。

首先,可以通过合理设计电路结构来减小PNP和NPN晶体管之间的耦合,减小Latch-Up的可能性。

其次,可以在电路中引入Latch-Up保护电路,如在电路中加入Latch-Up保护二极管来限制PNP和NPN晶体管之间的电压差,从而防止Latch-Up现象的发生。

此外,合理选择工艺和材料也可以减小Latch-Up的发生概率,如采用深亚微米工艺和抗辐射材料。

总之,Latch-Up是CMOS电路中常见的一种失效现象,其原理是由于PNP和NPN晶体管之间的相互耦合导致的。

为了防止Latch-Up现象的发生,我们可以通过合理设计电路结构、引入Latch-Up保护电路以及选择合适的工艺和材料来减小Latch-Up的可能性。

希望本文能够对Latch-Up原理有所了解,并为电路设计和应用提供一定的参考价值。

latch-up版图

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+

R w ell N w ell P- e p i

R su b P+s u b

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q1 Q2 OUT R su b P+s u b R su b Q2 OUT N+ N+ P+ R w ell

R su b

Q2

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+ R w ell N w ell P- e p i R su b P+s u b

Latch up的具体原因5 5 产生Latch up

OUT Q1

R w ell

R su b

Q2

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up原理分析

I n Out N+ P+ P+ Q1 Q2 N+ N+ P+ R w ell N w ell P- e p i R su b P+ s u b

华侨大学厦门专用集成电路系统重点实验室

Copyright by Huang Weiwei

latch-up保护方法

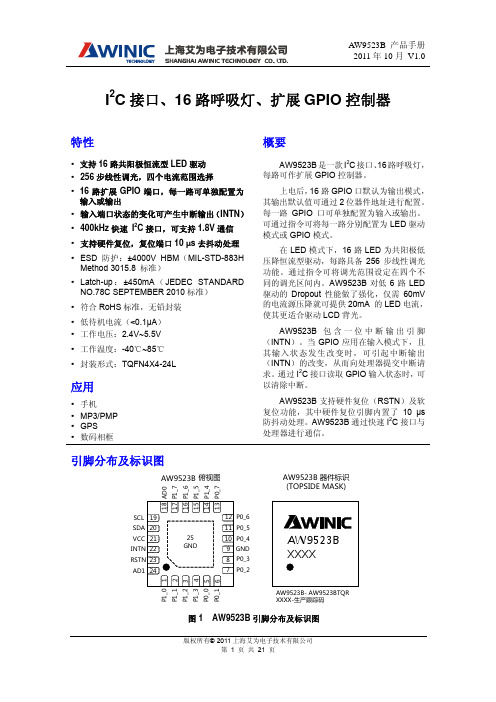

DS_AW9523B_CN_V1.0_IIC接口_16路呼吸灯_扩展GPIO控制器

P0_7~P0_0,

P1_7~P1_0)

tSP_RSTN

RSTN 引脚能滤除的低 毛刺脉宽

LED 驱动

ILED Vdrop1

每路 LED 电流大小

低 6 路(P1-0~P1_3, P0_0~P0_1)输出压降

VCC=2.5V,ISOURCE=10mA VCC=3.6V,ISOURCE=20mA VCC=5V,ISOURCE=20mA VCC=2.5V,ISINK=20mA VCC=3.6V,ISINK=20mA VCC=5V,ISINK=20mA VCC=2.5V,ISINK=6mA VCC=3.6V,ISINK=6mA VCC=5V,ISINK=6mA

逻辑低电平(SCL,

SDA,RSTN,AD0,

VIL

AD1,P0_7~P0_0,

P1_7~P1_0)

IIH,IIL

输入电流(SCL,SDA, AD0,AD1, P0_7~P0_0, P1_7~P1_0)

R_RSTN

RSTN 引脚的内置下拉 电阻

输入电容(SCL,SDA,

RSTN,AD0,AD1,

CI

VCCMCU

VBAT

VCCMCU

VCC INTN

MCU GPO1 GPIO GPO2

4.7kΩ (x3)

INTN

SCL SDA RSTN

1μF

VCC

2

P1_0 P1_1

P0_0

100kΩ (x7)

子系统 EN

AW9523B P1_2

GND

P1_3

P1_4

P1_5

VBAT

1

P1_6 P1_7 P0_1

+IT:+450mA -IT:-450mA

ESD模型和测试标准

1、ESD模型分类

2、HBM和MM测试方法标准

3、 CDM模型和测试方法标准

4、 EIC模型和测试方法标准

5、 TLP及其测试方法

6、拴锁测试

7、 I-V测试

8、标准介绍

1、ESD模型分类

因ESD产生的原因及其对集成电路放电的方式不同

,经过统计,ESD放电模型分下列四类:

(1) 人体放电模式 (Human-ቤተ መጻሕፍቲ ባይዱody Model, HBM)

(2) 机器放电模式 (Machine Model, MM)

(3) 组件充电模式 (Charged-Device Model, CDM)

(4) 电场感应模式 (Field-Induced Model, FIM)

另外还有两个测试模型:

(5)对于系统级产品测试的IEC电子枪空气放电模式

(6)对于研究设计用的TLP模型

引脚,将其作为参考节点连接到B端。其他

所有引脚依次连接到A端,并且在AB间接

入短接线。使用正负1000V的脉冲电压在

AB端,观察波形,经过所有引脚对的电流

波形必须符合如图波形

2、HBM和MM测试方法标准

HBM测试方法及标准

1.ANSI-STM5.1-2001

JESD22-A114D -2005

(2)ESD敏感度(sensitivity):引起器件失效的ESD等

级(level)

(3)ESD耐受电压(withstand voltage):在不引起器

件失效前提下的最大ESD等级

(4)步进耐压增强(Step stress test hardening):在步

进增加的测试电压下,器件的耐受电压的现象

4、 EIC模型和测试方法标准

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

latch up测试标准

Latchup测试是电路设计中非常重要的一部分,用于确保电路在各种情况下都能正常工作。

本测试标准旨在为电路设计人员提供一套清晰、准确、可操作的测试方法,以确保Latchup现象不会对电路性能产生不良影响。

一、测试目的

1.确保Latchup不会在电路中发生;

2.验证Latchup防护措施的有效性;

3.确保电路在不同工作条件下都能正常工作。

二、测试范围

1.电源电路;

2.信号传输线路;

3.数字和模拟电路;

4.芯片接口电路;

5.其他可能发生Latchup的区域。

三、测试方法

1.静态测试:

a.使用示波器、电压表和电流表测量电路各部分的工作电压、电流及信号波形;

b.检查电路中的电感和电容元件,确保其性能正常;

c.对比设计图纸和实际电路,确保元件布局、布线符合设计要求。

2.动态测试:

a.模拟不同的工作环境,如电压波动、温度变化等;

b.引入干扰信号,模拟Latchup条件;

c.使用测试仪器观察电路各部分的工作状态,如电压、电流、信号质量等;

d.观察Latchup发生时的现象,如电压下降、电流增大、信号畸变等。

3.防护措施测试:

a.对电路中的Latchup防护措施(如箝位二极管、磁珠等)进行测试;

b.验证这些防护措施在Latchup发生时的反应时间、抑制效果等性能指标;

c.检查防护措施对电路其他部分的影响。

四、测试标准

tchup现象未在电路中发生;

2.电路在各种工作条件下都能正常工作,无异常现象;

3.保护措施在Latchup发生时能迅速起作用,抑制效果良好;

4.干扰信号对其他电路部分的影响在可接受范围内。

五、测试周期与记录

1.每次设计变更后都应进行Latchup测试;

2.测试结果应记录在案,便于日后查阅;

3.对于多次出现问题的区域,应进行深入分析,找出根本原因。

通过遵循本测试标准,电路设计人员可以更准确地评估电路的安全性和可靠性,为产品的质量和性能提供有力保障。