基于FPGA的DDR3六通道读写防冲突设计

DDR3测试读写

DDR3测试读写(1)今天是重阳节,所以提前祝福重阳节快乐。

因为DDR3讲解内容比较多,所以分解成3节进行讲解。

一个做FPGA的人如果不懂DDR3,Serdes,那基本等于没学习fpga。

所以必须掌握ddr控制器才能深入fpga具体功能。

注意以后基本工具都是用的vivado2014.02版本。

用ise导致不一样,不要问我。

该工程参考的xilinx的文档xtp225。

首先是打开vivado,建完工程以后,然后点击IP catalog,打开ip库。

找到Memory Interface Generator IP核。

然后会出现图1.2页面图1.1图1.2的显示信息是当前工程设置的器件信息。

vivado不像以前的ISE,分离IP工程。

现在都是一个工程。

所以要注意观察该页面显示的器件是否正确。

经常有人选错速度等级而导致无法通过后期时序仿真。

图1.2图1.3是选择创建一个设计。

图1.3图1.4选择ddr3芯片。

图1.4图1.5显示的是兼容引脚。

选择next。

图1.5图1.6是选择选择DDR的时钟,记住,DDR是双边沿。

所以上面写的400MHz,也就是DDR 800M。

选额内存类型是SODIMMs。

内存类型是MT6JTF12864HZ-1G6类型。

Data Mask 数据掩码,可以选择或者不选择,类似于sdram的dqm信号。

有人问这有啥作用。

就等于内存中,你要改变其中几个bit而不是改变全部bit。

所以用掩码方式更好的。

否则你要读出来,然后再写入,这种方法太消耗时间。

图1.6图1.7是表示选择整个IP输入时钟多少,基本DDR3寄存器控制。

基本IP输入时钟在SPARTAN6的MIG核是没有选择,需要手动修改时钟文件。

这里有提供输入时钟选择。

读写burst的方式,一个顺序读取还有个strict 跳跃式读取。

除非你有特殊的要求,一般都是顺序读取。

输出驱动电阻控制RZQ/7和RTT电阻,这个电阻是从datasheet手册得到的。

基于FPGA的DDR SDRAM控制器的设计

普通本科毕业设计题目:基于FPGA的DDR SDRAM控制器的设计摘要随着半导体技术的发展,A/D采样的速率越来越高,相应需要越来越大容量的存储器。

存储器是目前数字系统中的关键部件之一,DDR SDRAM(Double Data Rate SDRAM,双倍数据率同步动态随机存储器)以其大容量、高速率和良好的兼容性以及低成本在计算机、消费类电子、通信等领域得到了相当广泛的应用。

DDR控制器实际上就是用户端与DDR存储器之间进行数据传输的一个桥梁,通过DDR控制器,用户端命令被转化成DDR 存储器所支持的命令格式,从而实现用户端对DDR的访问。

本文对DDR SDRAM及其控制器的结构、接口和时序进行了深入研究与分析,得出一些DDR SDRAM控制器的关键技术特性,然后基于Altera公司Cyclone II系列的FPGA芯片EP2C8Q208C8平台,利用Verilog硬件描述语言设计实现了DDR SDRAM存储控制器。

编写自动生成自加数据的模块,将自加数据写入到SDRAM中,再从SDRAM中读回,从UART 发送出去并在串口调试工具上显示。

【关键词】可编程逻辑门阵列DDR SDRAM 存储控制器通用异步收发器AbstractAlong with the development of semiconductor technology, A/D sampling rate is higher and higher, requiring more capacity of corresponding. Storage of memory is one of the crucial devices in the digital system at present, the DDR (Double Data Rate) SDRAM has many advantages for it's large capacity, high speed and the low cost, it has been used in quite a number of fields, such as the Server, the WorkStation, the Personal computer and the consumer electronics, the communication and other areas. DDR controller actually is a bridge between client and DDR memory for data transmission, through the DDR controller, client command was converted into the DDR memory which support command format, so as to realize the visit of DDR clients.The pivotal technologies of DDR SDRAM and memory controller, such as Structure, Interface and Timing are explored in this article, after a research on the main feature inside the DDR controller, several functional modules of the controller are designed out, and then based on FPGA chip Cyclone II Altera company EP2C8Q208C8 platform series used Verilog hardware description language. Write automatic generation and add data modules, with data from the data written to add SDRAM, and again read back from SDRAM, send it out from UART and display on serial port debugging tools.【Key words】FPGA; DDR SDRAM; Memory Controller; UART目录1 绪论 (2)1.1 DDR SDRAM的现状及发展趋势 (2)1.1.1 DDR内存的现状 (2)1.1.2 DDR内存的发展趋势 (3)1.2 课题研究的意义 (3)1.3 课题研究的要求 (2)1.4 本文的安排 (2)2 DDR SDRAM技术介绍 (4)2.1 DDR SDRAM的分类 (4)2.2 DDR SDRAM的基本概念 (4)2.2.1 DRAM存储原理 (5)2.2.2 DDR SDRAM的逻辑BANK与芯片位宽 (5)2.2.3 DDR SDRAM芯片容量 (5)2.2.4 DDR SDRAM内存刷新 (6)2.3 DDR SDRAM的命令 (6)2.3.1 初始化 (6)2.3.2 DDR SDRAM指令 (7)2.4 DDR SDRAM读写操作时序 (8)2.4.1 读操作时序 (8)2.4.2 写操作时序 (8)3 FPGA和Quartus II简介 (10)3.1 FPGA技术简介 (10)3.1.1 FPGA基本结构 (10)3.1.2 FPGA的基本特点 (10)3.1.3 FPGA芯片的选择 (11)3.2 Quartus Ⅱ简介 (11)3.3 Quartus II的设计流程 (11)4 系统硬件设计 (13)4.1 系统整体框架 (13)4.2 自动累加数据产生模块 (13)4.3 DDR SDRAM控制器模块 (14)4.3.1 DDR SDRAM控制器整体状态分析 (14)4.3.2 DDR SDRAM控制器总体架构 (15)4.3.3 输入/输出FIFO模块 (16)4.3.4 控制接口模块设计 (17)4.3.5 控制接口模块设计 (19)4.3.6 数据通路模块设计 (21)4.4 串口读数据模块 (23)5 系统控制器的功能验证 (26)5.1 系统控制器的功能仿真 (26)5.1.1 系统控制器Testbench设计 (26)5.1.2 系统控制器Testbench总体架构 (26)5.1.3 DDR SDRAM Controller Testbench顶层模块设计 (26)5.1.4 DDR SDRAM Controller Testbench仿真波形 (27)5.2 串口读取数据验证 (28)6 总结 (29)参考文献 (30)致谢 (31)1 绪论1.1 DDR SDRAM的现状及发展趋势1.1.1 DDR内存的现状目前DDR内存市场占有量非常大,尤其是近些年随着市场需求的高速增长使得加入该行业和研究该技术的人员也越来越多,DDR控制技术处于高速发展阶段。

基于FPGA的DDR3 SDRAM控制器设计及实现

基于FPGA的DDR3 SDRAM控制器设计及实现韩进;张览;刘锴【摘要】文章基于Verilog语言设计并实现了一款基于高云FPGA芯片的DDR3 SDRAM控制器系统.本设计以GW2A55作为核心,参照JESD79-3F工业标准定义的DDR3 SDRAM时序操作、状态转换、接口定义等规范,实现了控制器的设计.设计主要分为控制层和物理传输层两个逻辑层级.通过综合验证本设计数据传输接口的速率可达到800Mhz,高负载运行下错误数据校准率为100%,芯片逻辑资源占用率低于6.5%,因此能够满足用户对高速数据传输以及可靠性和低资源占用的要求,同时具备同家族芯片可移植性强的优势,并给出了系统功能仿真的验证结果.【期刊名称】《大众科技》【年(卷),期】2016(018)010【总页数】4页(P1-4)【关键词】FPGA;高云GW2A55;DDR3SDRAM控制器;JESD79-3F【作者】韩进;张览;刘锴【作者单位】山东科技大学计算机科学与工程学院,山东青岛 266590;山东科技大学计算机科学与工程学院,山东青岛 266590;山东高云半导体科技有限公司,山东济南 250000【正文语种】中文【中图分类】TP399DDR3 SDRAM是由JEDEC在DDR SDRAM 的基础上进行开发的内存技术标准,相对于 DDR SDRAM,其优势非常明显,使用SSTL 1.5作为核心电压具有更低的功耗,采用“Fly-by”拓扑结构提高了信号完整性,具有8n-bit预取结构且在时钟的上下沿均传输数据,从而大大提高了传输速率。

但是由于DDR3 SDRAM操作时序繁多,模式寄存器参数众多,工作状态转换复杂,需要有专门的控制器对它的读取、写入、刷新、预充电等进行控制。

本设计目的就是充分利用FPGA逻辑资源,设计一种合理、可靠、符合实际应用且成本低的DDR3 SDRAM 控制器。

论文给出整个控制器的系统设计方案,并搭建了testbench用于验证设计的有效性,同时给出读写数据的RTL级仿真测试结果。

基于FPGA的DDR SDRAM控制器的设计

普通本科毕业设计题目:基于FPGA的DDR SDRAM控制器的设计摘要随着半导体技术的发展,A/D采样的速率越来越高,相应需要越来越大容量的存储器。

存储器是目前数字系统中的关键部件之一,DDR SDRAM(Double Data Rate SDRAM,双倍数据率同步动态随机存储器)以其大容量、高速率和良好的兼容性以及低成本在计算机、消费类电子、通信等领域得到了相当广泛的应用。

DDR控制器实际上就是用户端与DDR存储器之间进行数据传输的一个桥梁,通过DDR控制器,用户端命令被转化成DDR 存储器所支持的命令格式,从而实现用户端对DDR的访问。

本文对DDR SDRAM及其控制器的结构、接口和时序进行了深入研究与分析,得出一些DDR SDRAM控制器的关键技术特性,然后基于Altera公司Cyclone II系列的FPGA芯片EP2C8Q208C8平台,利用Verilog硬件描述语言设计实现了DDR SDRAM存储控制器。

编写自动生成自加数据的模块,将自加数据写入到SDRAM中,再从SDRAM中读回,从UART 发送出去并在串口调试工具上显示。

【关键词】可编程逻辑门阵列DDR SDRAM 存储控制器通用异步收发器AbstractAlong with the development of semiconductor technology, A/D sampling rate is higher and higher, requiring more capacity of corresponding. Storage of memory is one of the crucial devices in the digital system at present, the DDR (Double Data Rate) SDRAM has many advantages for it's large capacity, high speed and the low cost, it has been used in quite a number of fields, such as the Server, the WorkStation, the Personal computer and the consumer electronics, the communication and other areas. DDR controller actually is a bridge between client and DDR memory for data transmission, through the DDR controller, client command was converted into the DDR memory which support command format, so as to realize the visit of DDR clients.The pivotal technologies of DDR SDRAM and memory controller, such as Structure, Interface and Timing are explored in this article, after a research on the main feature inside the DDR controller, several functional modules of the controller are designed out, and then based on FPGA chip Cyclone II Altera company EP2C8Q208C8 platform series used Verilog hardware description language. Write automatic generation and add data modules, with data from the data written to add SDRAM, and again read back from SDRAM, send it out from UART and display on serial port debugging tools.【Key words】FPGA; DDR SDRAM; Memory Controller; UART目录1 绪论 (2)1.1 DDR SDRAM的现状及发展趋势 (2)1.1.1 DDR内存的现状 (2)1.1.2 DDR内存的发展趋势 (3)1.2 课题研究的意义 (3)1.3 课题研究的要求 (2)1.4 本文的安排 (2)2 DDR SDRAM技术介绍 (4)2.1 DDR SDRAM的分类 (4)2.2 DDR SDRAM的基本概念 (4)2.2.1 DRAM存储原理 (5)2.2.2 DDR SDRAM的逻辑BANK与芯片位宽 (5)2.2.3 DDR SDRAM芯片容量 (5)2.2.4 DDR SDRAM内存刷新 (6)2.3 DDR SDRAM的命令 (6)2.3.1 初始化 (6)2.3.2 DDR SDRAM指令 (7)2.4 DDR SDRAM读写操作时序 (8)2.4.1 读操作时序 (8)2.4.2 写操作时序 (8)3 FPGA和Quartus II简介 (10)3.1 FPGA技术简介 (10)3.1.1 FPGA基本结构 (10)3.1.2 FPGA的基本特点 (10)3.1.3 FPGA芯片的选择 (11)3.2 Quartus Ⅱ简介 (11)3.3 Quartus II的设计流程 (11)4 系统硬件设计 (13)4.1 系统整体框架 (13)4.2 自动累加数据产生模块 (13)4.3 DDR SDRAM控制器模块 (14)4.3.1 DDR SDRAM控制器整体状态分析 (14)4.3.2 DDR SDRAM控制器总体架构 (15)4.3.3 输入/输出FIFO模块 (16)4.3.4 控制接口模块设计 (17)4.3.5 控制接口模块设计 (19)4.3.6 数据通路模块设计 (21)4.4 串口读数据模块 (23)5 系统控制器的功能验证 (26)5.1 系统控制器的功能仿真 (26)5.1.1 系统控制器Testbench设计 (26)5.1.2 系统控制器Testbench总体架构 (26)5.1.3 DDR SDRAM Controller Testbench顶层模块设计 (26)5.1.4 DDR SDRAM Controller Testbench仿真波形 (27)5.2 串口读取数据验证 (28)6 总结 (29)参考文献 (30)致谢 (31)1 绪论1.1 DDR SDRAM的现状及发展趋势1.1.1 DDR内存的现状目前DDR内存市场占有量非常大,尤其是近些年随着市场需求的高速增长使得加入该行业和研究该技术的人员也越来越多,DDR控制技术处于高速发展阶段。

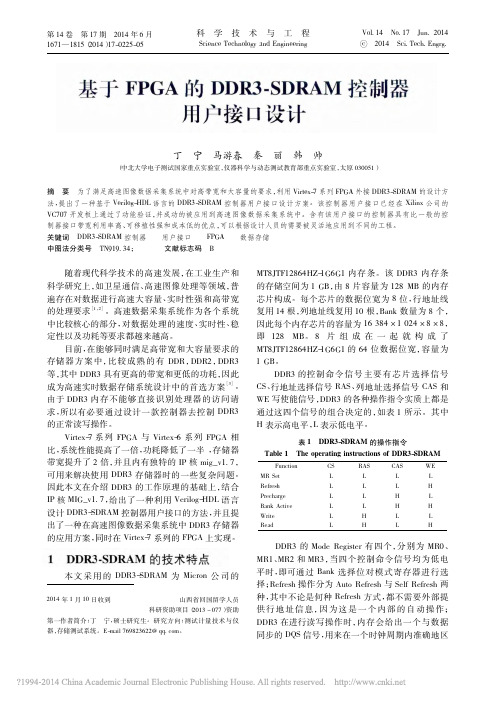

基于FPGA的DDR3-SDRAM控制器用户接口设计

基于FPGA的DDR3-SDRAM控制器用户接口设计丁宁;马游春;秦丽;韩帅【期刊名称】《科学技术与工程》【年(卷),期】2014(014)017【摘要】为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7系列FPGA外接DDR3-SDRAM的设计方法,提出了一种基于Verilog-HDL语言的DDR3-SDRAM控制器用户接口设计方案.该控制器用户接口已经在Xilinx公司的VC707开发板上通过了功能验证,并成功的被应用到高速图像数据采集系统中.含有该用户接口的控制器具有比一般的控制器接口带宽利用率高、可移植性强和成本低的优点,可以根据设计人员的需要被灵活地应用到不同的工程.【总页数】5页(P225-229)【作者】丁宁;马游春;秦丽;韩帅【作者单位】中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原030051;中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原030051;中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原030051;中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原030051【正文语种】中文【中图分类】TN919.34【相关文献】1.基于FPGA和SPICAN控制器的通讯接口设计 [J], 周霞;姜鑫;蓝彦;彭文才;2.基于FPGA的ARM与CAN控制器的接口设计与实现 [J], 贾建峰;崔培玲3.基于FPGA的电脑横机控制器PC104总线接口设计 [J], 潘启勇;卢达4.基于FPGA的DDR2_SDRAM控制器用户接口设计 [J], 韩笑;闫永立;李勇彬;马嘉莉;吴斌5.基于Spartan-6 FPGA的DDR2控制器接口设计 [J], 徐文超;于意仲;柴耀龙;邢卫华因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的DDR3_SDRAM控制器用户接口设计_丁宁

226科学技术与工程14 卷分出每个 传 输 周 期,提 高 了 接 收 方 接 收 数 据 的 准 确度。

与上一代存储器件相比,DDR3 的内存模式有 了很大的改进: 逻辑 Bank 数量由 DDR2 的 4 个增加 为 8 个; 突发长度增加为 8 bit,任何突发中断操作都 将在 DDR3 内存中予以禁止,且不予支持; 取而代之 的是更为灵活的突发传输控制; 其核心工作电压由 DDR2 的 1. 8 V 降至 1. 5 V[4],能够在达到高带宽的 同时,大幅度的降低其功耗; DDR3 采用 FLY_BY 总 线,参考电压分离,增加了 ZQ 校准功能,从而大大 的提高了存储信号的完整性; 并且 DDR3 为绿色封 装,不含任何有害物质,减少了对空气的污染。

图 4 DDR3 存储器的状态机 Fig. 4 The state machine of DDR3 memory

3. 1 用户接口设计模块的 Chipscope 仿真结果分析 在本次设计中,硬件仿真采用将含有此用户接

口模块的控制器下载到 Virtex-7 系列 FPGA 上,通 过 Chipscope 在线实时地观察用户接口内部的信号。 和图 6 中 addr 每隔一个时钟周期加 1 的现象。 3. 2 用 户 接 口 设 计 模 块 的 Modelsim 仿 真 结 果

2. 1 用户接口模块的设计 用户接口模块为整个 DDR3 控制器系统的核心

模块,其中主要包括写数据通路和读数据通路两个 部分,图 2 为 DDR3 控制器的用户接口设计的实现 方案。

在写数据 通 路 的 输 入 端,addr _ rdy、wr _ rdy 和 init_done 为 DDR3 IP 核反馈给写数据控制模块的 信号,init_done 为高电平时指 DDR3 已经完成初始 化操作,addr_rdy 为高电平时表示 DDR3 准备好接 收写数据地址和写数据命令,wr_rdy 为高电平时表 示 DDR3 准备好接收写数据; wr_cmd 为写数据命令 信号。在写数据通路的输出端,cmd _ en 为输入到 DDR3 IP 核的命令和地址的使能信号,wr_en 和 wr_ end 为输入到 DDR3 IP 核的写数据控制信号,跟有 效写数据信号对齐。

基于FPGA的SDRAM控制器的设计与实现

基于FPGA的SDRAM控制器的设计与实现引言:随着技术的发展,FPGA在数字电路设计领域得到了广泛的应用。

而SDRAM是一种常见的存储器设备,具有容量大、速度快等特点,被广泛应用于各种计算机系统中。

本文将介绍基于FPGA的SDRAM控制器的设计与实现。

设计目标:本次设计的目标是实现一个能够控制SDRAM读写操作的FPGA控制器。

通过该控制器,可以实现对SDRAM的读写操作,从而实现数据的存储与获取。

设计方案:本次设计采用Verilog语言进行RTL级的设计。

设计方案包括以下几个模块:初始化模块、控制模块、读写模块和时序控制模块。

1.初始化模块:初始化模块用于对SDRAM进行初始化配置,包括设置时钟频率、设置SDRAM的工作模式等。

在该模块中,需要配置SDRAM的控制寄存器,以便于后续的读写操作。

2.控制模块:控制模块用于接收外部的读写指令,并将其转化为SDRAM的控制信号。

该模块包括读写指令的解析、地址生成、数据缓存等功能。

通过该模块,可以实现对SDRAM的读写操作。

3.读写模块:读写模块用于控制SDRAM的读写操作。

读操作包括向SDRAM发送读指令、读地址和读请求信号,并接收SDRAM返回的读数据;写操作包括向SDRAM发送写指令、写地址和写数据,并接收SDRAM的写完成信号。

4.时序控制模块:时序控制模块用于控制SDRAM的时序,包括时钟信号的生成、读写时序的控制等。

通过该模块,可以确保SDRAM的读写操作按照正确的时序进行。

实现步骤:1.根据SDRAM的规格书,了解SDRAM的控制信号和时序要求。

2.设计并实现初始化模块,完成对SDRAM的初始化配置。

3.设计并实现控制模块,包括读写指令解析、地址生成、数据缓存等功能。

4.设计并实现读写模块,完成对SDRAM的读写操作。

5.设计并实现时序控制模块,确保SDRAM的读写操作按照正确的时序进行。

6.进行功能仿真,验证设计的正确性。

总结:通过本次设计与实现,我们成功实现了基于FPGA的SDRAM控制器。

基于FPGA的DDR3SDRAM控制器设计及实现_张刚

2014年第27卷第1期Electronic Sci.&Tech./Jan.15,2014收稿日期:2013-07-06作者简介:张刚(1989—),男,硕士研究生。

研究方向:电子系统设计与仿真。

E-mail :jiachao2007@ 。

贾建超(1988—),男,硕士研究生。

研究方向:高速并行信号处理。

赵龙(1989—),男,硕士研究生。

研究方向:雷达信号处理与仿真。

基于FPGA 的DDR3SDRAM 控制器设计及实现张刚,贾建超,赵龙(西安电子科技大学电子工程学院,陕西西安710071)摘要DDR3SDRAM 是第三代双倍数据传输速率同步动态随机存储器,以其大容量、高速率和良好的兼容性得到了广泛应用。

文中介绍了DDR3的特点和操作原理,以及利用MIG 软件工具在Virtex -6系列FPGA 中实现DDR3SDRAM 控制器的设计方法,并进行硬件测试。

验证了DDS3控制器的可行性,其工作稳定、占用资源少、可植性强等。

关键词FPGA ;DDR3SDRAM 控制器;MIG中图分类号TN79文献标识码A文章编号1007-7820(2014)01-070-04Design and Realization of DDR3SDRAM Controller Based on FPGAZHANG Gang ,JIA Jianchao ,ZHAO Long(School of Electronic Engineering ,Xidian University ,Xi'an 710071,China )AbstractThe DDR3SDRAM is the third-generation double data rate synchronous dynamic random accessmemory ,which has been widely used in many fields because of its large capacity ,high speed and good compatibili-ty.This paper briefly introduces the characteristics and operating principles of DDR3,and the realization of DDR3SDRAM controller in the Virtex-6FPGA series with MIG software tools ,and gives the hardware test results.The feasibility of the controller is verified.It has the advantages of stable operation ,small requirement on resources and good portability.KeywordsFPGA ;DDR3SDRAM controller ;MIGDDR3SDRAM 是从DDR、DDR2发展而来的一种高速同步动态随机访问存储器。

fpga读写ddr3流程

fpga读写ddr3流程## English Answer:FPGA DDR3 Read/Write Process.The process of reading and writing data to DDR3 memory from an FPGA involves several steps:1. Initialization: The first step is to initialize the DDR3 controller on the FPGA. This involves configuring the controller's registers to define the memory timing parameters and other settings.2. Refresh: The DDR3 memory requires periodic refresh operations to maintain the integrity of the stored data. The FPGA controller typically performs these refreshes automatically in the background.3. Write Operation: To write data to DDR3 memory, the FPGA controller must first issue a write command to thememory controller. The command specifies the address of the memory location to be written to, as well as the data to be written.4. Read Operation: To read data from DDR3 memory, the FPGA controller must first issue a read command to the memory controller. The command specifies the address of the memory location to be read from. The memory controller will then return the data to the FPGA controller.5. Error Handling: The DDR3 memory controller can handle various types of errors that can occur during read and write operations. Common errors include parity errors and address errors. The FPGA controller can detect and correct these errors, or it can report the errors to the system for further handling.DDR3 Timing Parameters.The timing parameters of the DDR3 memory controller are critical for ensuring reliable and high-performance operation. The most important timing parameters include:CAS Latency (CL): The CAS latency is the number of clock cycles that must pass between the time that a read command is issued and the time that the data is returned.Row Address to Column Address Delay (tRCD): The tRCD is the number of clock cycles that must pass between the time that a row address is issued and the time that a column address is issued.Write Recovery Time (tWR): The tWR is the number of clock cycles that must pass between the time that a write command is issued and the time that the memory is ready to accept another write command.Optimization Techniques.There are several techniques that can be used to optimize the performance of DDR3 read/write operations:Burst Mode: DDR3 memory can perform read and write operations in burst mode, which allows for multiple datatransfers to occur in a single operation.Caching: Data that is frequently accessed can be cached in the FPGA's on-chip memory, reducing the number of accesses to the DDR3 memory.Error Correction: Using error correction codes (ECC) can protect data from errors that occur during read and write operations.## 中文回答:FPGA 读写 DDR3 流程。

基于FPGA的DDR控制器的设计

基于FPGA的DDR控制器的设计作者:陈秀英董玉华张亚楠来源:《智能计算机与应用》2016年第06期摘要: DDR SDRAM使用双倍数据速率结构,凭借其大容量,高数据传输速率和低成本优势,正在被越来越多地应用于高速数据采集系统中[1]。

使用Altera公司的Cyclone FPGA芯片设计实现了DDR控制器的功能,叙述了其设计思想,具有一定的实用价值。

关键词: DDR SDRAM;控制器; FPGA;数据采集中图分类号: TP311文献标志码: A文章编号: 2095-2163(2016)06-0118-030引言随着电子技术的快速发展,人们对DDR(全称DDR SDRAM)[2]的需求越来越紧迫。

DDR(Double Data Rate Synchronous Dynamic Random Access Memory,双倍速率随机存储器)在设计上采用的是2.5 V的工作电压,而且允许在时钟的上升沿和下降沿进行数据的存取,整体速度已可达到同频率的2倍,同时还在容量方面也呈现了更佳性能。

因而,在诸多对于数据量和带宽具有较高要求的重要系统中,DDR已然成为获得广泛应用的一种功能强大、可拓展的高端存储器。

基于此,为了充分发挥DDR容量和速度的执行优势,本次研究主要针对DDR 读写的特点,开发实现了一种基于FPGA读写的DDR控制器[3]。

[BT4]1DDR SDRAM控制器的工作解析[BT5]1.1DDR SDRAM的工作原理DDR SDRAM是由若干个基本的单管DRAM单元所构成的。

内存控制器的主要功能是对DDR3 SDRAM的读写进行控制,在内存芯片完成初始化之后,DDR内存处于就绪状态。

DRAM利用MOS管的栅电容上的电荷来实现信息储存,一个单元储存的是0还是1取决于电容是否有电荷,有电荷代表1,无电荷代表0。

但时间一长,由于栅极漏电,代表1的电容会放电,代表0的电容会吸收电荷,这样会造成数据流失。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0引言基于FPGA的期货行情数据加速处理过程中,不同的消息类型采用并行处理的方式,并且每一次的处理结果需要使用内存来缓存一次行情数据信息。

行情数据信息容量巨大,片上存储难以满足需求,采用DDR3SDRAM 成为首选方法[1]。

但由于DDR3只有一套数据访问通道,不能满足多个通道同时访问的需求[2]。

此前的对于SDRAM的多通道解决方案中,比如曹一江[3]等设计的基于NPI总线的片外存储器,最大带宽可达743Mb/s;樊博[4]等使用UI接口,DDR3通信的最大带宽可达3.8Gb/s;张宇嘉[5]等设计的基于AXI4的DDR3多端口方案虽然传输速率有所提高,但由于AXI4协议本身的复杂性增加了开发使用的难度。

本文实现并验证了期货行情数据加速处理中基于FPGA的DDR3六通道UI接口读写防冲突设计,简化了DDR3多通道读写的复杂度,随着有效数据周期的提升,最高端口速率可达5.0GB/s以上,带宽利用率可达80%以上。

1总体设计架构本文所设计的六通道读写防冲突总体架构如图1所示,主要包括通道判优仲裁模块、读写逻辑控制模块和DDR3存储器控制模块。

DDR3存储控制器模块采用Xilinx公司的MIG核,用户只需要通过IP核的GUI选择内存芯片并进行相关参数设置,即可完成DDR3的配置工作[6]。

基于FPGA的DDR3六通道读写防冲突设计张凤麒,张延彬,王忠勇(郑州大学产业技术研究院,河南郑州450000)摘要:为了解决期货行情数据加速处理中多个通道同时访问DDR3时出现的数据读写冲突问题,实现了一种基于FPGA的DDR3六通道读写防冲突设计,完成了对单片DDR3内存条的多通道实时访问控制需求。

通过ChipScope工具采样结果证明了设计的可行性,提高了并行处理的速度,极大程度地降低了期货行情数据处理中行情计算的时间开销,最高通道速率可达5.0GB/s以上,带宽利用率可达80%以上,在多通道数据读写应用中具有很高的实用价值。

关键词:多通道;防冲突;DDR3;FPGA中图分类号:TP334.4文献标识码:A DOI:10.16157/j.issn.0258-7998.175167中文引用格式:张凤麒,张延彬,王忠勇.基于FPGA的DDR3六通道读写防冲突设计[J].电子技术应用,2018,44 (7):68-71,80.英文引用格式:Zhang Fengqi,Zhang Yanbin,Wang Zhongyong.Anti-conflict design for reading and writing of DDR3six channels based on FPGA[J].Application of Electronic Technique,2018,44(7):68-71,80.Anti-conflict design for reading and writing of DDR3six channels based on FPGAZhang Fengqi,Zhang Yanbin,Wang Zhongyong(Industrial Technology Research Institute,Zhengzhou University,Zhengzhou450000,China)Abstract:In order to solve the problem of data conflict of reading and writing when multiple channels access DDR3at the same time in the acceleration processing of futures market data,an anti-conflict design for reading and writing of DDR3six channels based on FPGA is implemented and the requirement of multiple channels′real-time access control for monolithic DDR3memory bar is completed.The result of ChipScope sampling proves the feasibility of the design,it improves the parallel processing speed and reduces the prices of time overhead in the calculation of futures market data processing.The highest channel rate can reach more than5.0GB/s and the bandwidth utilization rate can reach more than80%.The design has a very high practical value in the application of multiple channels′reading and writing.Key words:multiple channels;anti-conflict;DDR3;FPGA图1总体设计架构接口名称app_cmdapp_addr app_en app_rdy app_wdf_data app_wdf_mask app_wdf_rdy app_wdf_wren app_wdf_end位宽3281151264111方向输入输入输入输出输入输入输出输入输入功能描述3'b000写输入写地址输入使能信号是否接收命令输入写数据输入掩码是否接收数据写数据有效指示写数据最后部分表1DDR3写接口信号通道判优仲裁模块将对六路通道进行仲裁,对于同一时刻有读写请求的不同通道,该模块按照优先级的高低判定访问DDR3的顺序,利用中断思想解决多通道读写的冲突问题。

读写逻辑控制模块控制DDR3的接口生成,根据不同操作完成对应接口的时序控制[7],进而实现对DDR3的正确读写访问。

2DDR3存储器控制模块设计DDR3IP 核生成的控制器逻辑框图如图2所示,采用UI 接口的方式相比于AXI4接口,不需要自己组织数据,容易操作,大大简化了DDR3的使用复杂度,为DDR3的扩展使用带来了方便[8]。

2.1存储控制模块写操作DDR3写操作接口信号如表1所示。

写操作过程:当app_rdy 和app_wdf_rdy 同时为高的情况下,写入DDR3的地址app_addr 与app_cmd 绑定对齐,写入DDR3的数据app_wdf_data 与数据掩码app_wdf_mask 绑定对齐,app_cmd 置为3′b000,与此同时app_en 、app_址中。

因为DDR3的写时序不只一种,为了简化系统设计,本文设计的用户接口写操作时序为地址和数据完全对齐,便于理解和操作[9]。

2.2存储控制模块读操作DDR3的读操作接口信号如表2所示。

读操作过程:在app_rdy 为高时,用户发送读命令并同时将app_en 置高,则读命令和读地址会写到DDR3中,DDR3会返回数据和有效指示信号,两者共同决定返回的数据是否有效。

通常情况下,DDR3的读请求结束之后不会马上返回数据,需要延迟一定的时钟周期。

3通道判优仲裁模块设计通常情况下,由于DDR3只有一组控制、地址和数据总线,因此同一时刻只能有一个通道在访问。

根据期货交易的处理规则,优先级由高到低的顺序依次为合约信息消息、市场状态消息、品种交易状态消息、成交统计行情消息、多档定单簿行情消息、多档成交量统计行情消息。

在通道判优的过程中,首先将6种不同的消息经封装后分别寄存到相应的消息缓存中,每一通道写入消息缓存中的数据格式,从高到低位依次为写使能、读使能、写数据、写地址、读地址;然后首先判断合约信息消息缓存是否为空,如果不为空,则证明当前有合约信息消息的请求发生,此时状态机会跳转到合约信息消息处理状态;待合约信息消息的缓存全部读取完毕之后,再次按优先级顺序判断其他消息缓存是否为空,状态机随即做相应的跳转,完成不同通道之间的切换,如图3所示。

对于不同的消息类型,对应着不同的消息处理单元,目的是增加系统的并行处理操作,降低处理延迟。

4读写逻辑控制模块读写逻辑控制模块主要对不同类型消息做并行化处理,生成DDR3的接口信号,每个消息的处理流程如图4所示。

对于期货交易中的各种合约行情,种类多,但占用空间小,通常DDR3中一个地址就可完成一个行情的存储,在行情的还原、计算、发布中,需要读取多个行情。

由于DDR3的突发长度为8,为了便于对行情的准确存图2DDR3IP 核控制器逻辑框图接口名称app_cmdapp_addr app_en app_rdy app_rd_data app_rd_data_valid位宽328115121方向输入输入输入输出输出输出功能描述3'b001读输入读地址输入使能信号是否接收命令DDR3读出数据读数据有效表2DDR3读接口信号图5写操作流程取,6个通道的数据位宽均设定为DDR3位宽的1/8,即一次只存取一个地址的数据。

对于通道判优仲裁模块输出的数据,写使能与读使能均为1bit 位宽,高电平表示请求发生;写数据为64bit 位宽;写地址和读地址为28bit 位宽,DDR3的数据位宽在IP 核中配置为512bit ,地址位宽为28bit 。

因写数据位宽与DDR3数据位宽不匹配,所以DDR3的写操作需要掩码配合共同完成。

处理过程如下:首先进行读写判断,若写使能置高,则跳转到写操作状态;若读使能置高,则跳转到读操作状态,若无读写操作,处于等待状态。

(期货行情消息处理中不会出现同一通道读写同时进行的情况,因此同一通道读写使能同为高电平的情况不会出现。

)如果是写操作,一方面生成写入DDR3的地址和命令,另一方面将写数据封装成512bit 位宽。

其中写入DDR3的地址app_addr 为{写地址[27:3],3′d0},写入的数据app_wdf_data 和掩码app_wdf_mask 由写地址[2:0]确定。

数据地址命令控制模块也会相应的产生app_en 、app_wdf_wren 、app_wdf_end 控制信号,这些信号共同作用关于DDR3SDRAM 存储器,配合完成DDR3的写入操作,如图5所示。

如果是读操作,地址命令选择模块将读地址[27:3]赋值给app_addr 作为写入DDR3的基地址,同时将读地址[2:0]作为写入DDR3的偏移地址存入对应通道的偏移地址缓存中,在数据地址命令控制模块生成其他的控制信号传送给DDR3SDRAM 存储器。