实验3 电子电路OC门与TS门

实验三 门电路功能测试

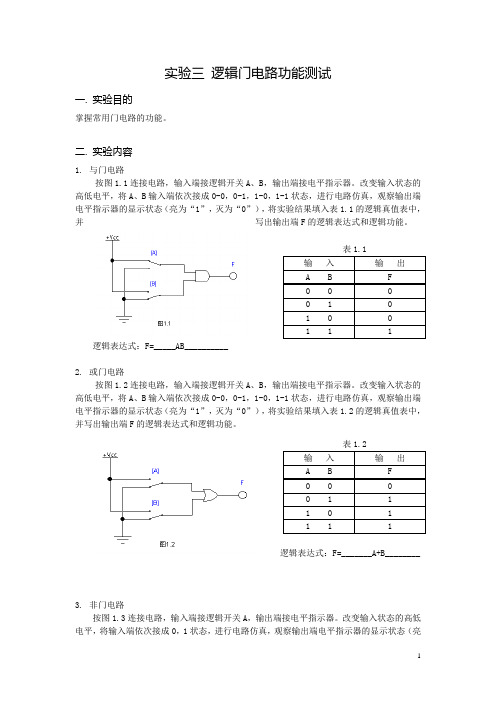

实验三 逻辑门电路功能测试一. 实验目的掌握常用门电路的功能。

二. 实验内容1. 与门电路按图1.1连接电路,输入端接逻辑开关A 、B ,输出端接电平指示器。

改变输入状态的高低电平,将A 、B 输入端依次接成0-0,0-1,1-0,1-1状态,进行电路仿真,观察输出端电平指示器的显示状态(亮为“1”,灭为“0”),将实验结果填入表1.1的逻辑真值表中,并写出输出端F 的逻辑表达式和逻辑功能。

逻辑表达式:F=_____AB__________2. 或门电路按图1.2连接电路,输入端接逻辑开关A 、B ,输出端接电平指示器。

改变输入状态的高低电平,将A 、B 输入端依次接成0-0,0-1,1-0,1-1状态,进行电路仿真,观察输出端电平指示器的显示状态(亮为“1”,灭为“0”),将实验结果填入表1.2的逻辑真值表中,并写出输出端F 的逻辑表达式和逻辑功能。

逻辑表达式:F=_______A+B________3. 非门电路按图1.3连接电路,输入端接逻辑开关A ,输出端接电平指示器。

改变输入状态的高低电平,将输入端依次接成0,1状态,进行电路仿真,观察输出端电平指示器的显示状态(亮为“1”,灭为“0”),将实验结果填入表1.3的逻辑真值表中,并写出输出端F 的逻辑表达式。

表1.1表1.2逻辑表达式:F=______A _____4. 与非门电路按图1.4连接电路,输入端接逻辑开关A 、B ,输出端接电平指示器。

改变输入状态的高低电平,将A 、B 输入端依次接成0-0,0-1,1-0,1-1状态,进行电路仿真,观察输出端电平指示器的显示状态(亮为“1”,灭为“0”),将实验结果填入表1.4的逻辑真值表中,并写出输出端F 的逻辑表达式和逻辑功能。

逻辑表达式:F=______B A _________5. 或非门电路按图1.5连接电路,输入端接逻辑开关A 、B ,输出端接电平指示器。

改变输入状态的高低电平,将A 、B 输入端依次接成0-0,0-1,1-0,1-1状态,进行电路仿真,观察输出端电平指示器的显示状态(亮为“1”,灭为“0”),将实验结果填入表1.5的逻辑真值表中,并写出输出端F 的逻辑表达式和逻辑功能。

数字模拟电路---第三章 逻辑门电路(1)

路。

简称门电路。

5V一、TTL 与非门图3-1 典型TTL 与非门电路3.2 TTL 集成门电路•数字集成电路中应用最广的为TTL 电路(Transister-Transister-Logic 的缩写)•由若干晶体三极管、二极管和电阻组成,TTL 集成电路有54/74系列 ①输出高电平UOH 和输出低电平UOL 。

•输出高电平U OH:至少有一个输入端接低电平时的输出电平。

•输出低电平U OL:输入全为高电平时的输出电平。

• 电压传输特性的截止区的输出电压UOH=3.6V,饱和区的输出电压UOL=0.3V。

一般产品规定U OH≥2.4V、U OL<0.4V时即为合格。

二、TTL与非门的特性参数③开门电平U ON 和关门电平U OFF 。

开门电平U ON 是保证输出电平达到额定低电平(0.3V )时,所允许输入高电平的最低值,表示使与非门开通的最小输入电平。

通常U ON =1.4V ,一般产品规定U ON ≤1.8V 。

关门电平U OFF 是保证输出电平为额定高电平(2.7V 左右)时,允许输入低电平的最大值,表示与非门关断所允许的最大输入电平。

通常U OFF ≈1V ,一般产品要求U OFF ≥0.8V 。

5). 扇入系数Ni和扇出系数N O 是指与非门的输入端数目。

扇入系数Ni是指与非门输出端连接同类门的个数。

反扇出系数NO映了与非门的带负载能力。

6)输入短路电流I IS 。

当与非门的一个输入端接地而其余输入端悬空时,流过接地输入端的电流称为输入短路电流。

7)8)平均功耗P 指在空载条件下工作时所消耗的电功率。

三、TTL门电路的改进 74LS系列 性能比较好的门电路应该是工作速度既快,功耗又小的门电路。

因此,通常用功耗和传输延迟时间的乘积(简称功耗—延迟积或pd积)来评价门电路性能的优劣。

74LS系列又称低功耗肖特基系列。

74LS系列是功耗延迟积较小的系列(一般t pd<5 ns,功耗仅有2 mW) 并得到广泛应用。

三态输出门电路TSL门

17

(2)逻辑符号

低电平有效

控制端低电平有效的三态门

用“▽” 表示输出 为三态。

高电平有效

控制端高电平有效的三态门

2019/7/20

18

2.三态门的主要应用-实现总线传输

要求各门的控制 端EN轮流为高电平, 且在任何时刻只有一 个门的控制端为高电 平。

如有8个门,则8 个EN端的波形应依 次为高电平,如下页 所示。

2019/7/20

8

很大的电流

1 不高不低的 电平:1/0?

0

图2-18 推拉式输出级并联的情况

2019/7/20

9

其次,在采用推拉式输出级的门电路中,电 源一经确定(通常规定为5V),输出的高电平也 就固定了(不可能高于电源电压5V),因而无法 满足对不同输出高电平的需要。

集电极开路门(简称OC门)就是为克服以上 局限性而设计的一种TTL门电路。

为何要采用集电极开路门呢?

推拉式输出电路结构存在局限性。 首先,输出端不能并联使用。若两个门的输出 一高一低,当两个门的输出端并联以后,必然有很 大的电流同时流过这两个门的输出级,而且电流的 数值远远超过正常的工作电流,可能使门电路损坏。 而且,输出端也呈现不高不低的电平,不能实现应 有的逻辑功能。

15

1.三态门的电路结构

(1)电E路N结= 0构时:,增电加路了为控正制常输的入与端非(工E作na状bl态e),。 (所2)以工称作控原制理端:低电平有效。

0

2019/7/20

1 截止

Y=AB

16

1.0V

1.0V 截止

悬空

1

0

导通

截止

当EN = 1时,门电路输出端处于悬空的高阻状态。

OC门

注意:连线完成再通电!!!

实验过程中常见典型故障

• 设计错误 • 器件与底板故障 • 布线错误(漏线和错线)

实验故障检查方法

• 加电前:

1)检查集成电路安装方向; 2)检查包括电源线和地线在内的连线是否有漏线 和错线; 3)用万用表测量电路的电源端和地线端之间的阻 值,排除电源和地线间的短路现象; 4)调整稳压电源输出电压值并用万用表测量。

数字逻辑设计实践

---三态门和OC门的应用

本次内容

• 电路连接基本技术回顾 • 三态门和OC门的数据总线传输

电路连接基本技术

1、集成电路安装

封装形式:双列直插封装(DIP) 安装位置:跨插在宽条面包板的凹槽上 安装方向:保证芯片缺口一律向左

布线示范

电路连接基本技术

2、布线

布线次序:先布电源线和地线,再布固定电平的 规则线,最后按照信号流程逐级连接各逻辑控制 线。 走线原则:

实验故障检查方法

• 加电后:

1)观察稳压电源短路指示灯; 2)检查各集成电路是否已加上电源; 3)未接地和未接电源; 4)检查是否有不允许悬空的输入端未接入电路; 5)静态检查:使电路处在某一故障的工作状态; 6)动态检查:在某一规律信号作用下检查各级工作 波形; 7)器件替换法。

举例说明

三态门和OC门的数据传输实验

普通门、OC门和三态门

• 多个普通门的输出端不允许连接在一起

普通门、OC门和三态门

• 多个OC门、ห้องสมุดไป่ตู้态门的输出端可以连接在一起

oc门的逻辑符号

oc门的逻辑符号OC门,也称作异或门,是数字逻辑电路中最基本的门电路之一,常常被用于电脑的处理器和通信电路等领域,因其操作简单而备受青睐。

OC门的逻辑符号是一个有两个输入端和一个输出端的符号,下面分几个步骤详细介绍OC门的逻辑符号。

1. OC门的基本原理OC门的基本原理是当两个输入端的信号为不同状态(即一个为1,另一个为0)时,输出端的电位为高电位(即为1),而当两个输入端的信号为相同状态(即两个都为0或都为1)时,输出端的电位为低电位(即为0)。

2. OC门的逻辑符号构成OC门的逻辑符号一般由一个黑色框框起来,里面有两条输入线和一条输出线。

输入线的左边有一个反映输入信号状态的点(通常为圆点),而输出线的右边则有一个反映输出信号状态的箭头。

通常在OC门的输入线和输出线上方都有字母“OC”来表明这是一个OC门。

3. OC门的逻辑符号意义OC门的逻辑符号意义简明易懂,通过不同状态的输入信号,输出一个预定的状态。

OC门的逻辑符号是数字逻辑电路设计和运算中最基本的单位之一,因此在电子电路设计、自动控制,以及通信电路等领域都有广泛的应用。

4. OC门在电子设备中的应用OC门在电子设备中有许多应用,比如在电路频分两用器中,可以通过OC门实现两个方向的通信;在计算机内存芯片中,可以使用OC门来存储和操作二进制数据;在音响设备如喇叭控制电路中,OC门可用来控制音量大小等。

5. OC门的优势OC门是数字逻辑电路中最基本的门电路之一,具有简单、容易实现和低成本等优势。

此外,OC门还具有可靠性高、适用于高速和大功率等特点,因此被广泛应用于各种数字逻辑电路中。

总之,OC门的逻辑符号是数字电路中最基本也是最重要的组成部分之一。

其简单性和高可靠性是其得到广泛应用的主要原因。

随着技术的不断发展,OC门逻辑符号的应用领域也会不断地扩大和优化。

OC与OD门

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector (Open Drain)。

为什么引入OC门?实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。

因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:1、实现与或非逻辑,用做电平转换,用做驱动器。

由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC 门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。

在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

在硬件上,可用OC门或三态门(ST门)来实现。

用OC门实现线与,应同时在输出端口应加一个上拉电阻。

3、三态门(ST门)主要用在应用于多个门输出共享数据总线,为避免多个门输出同时占用数据总线,这些门的使能信号(EN)中只允许有一个为有效电平(如高电平),由于三态门的输出是推拉式的低阻输出,且不需接上拉(负载)电阻,所以开关速度比OC门快,常用三态门作为输出缓冲器。

一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。

因此,需要一种新的与非门电路来实现线与逻辑,这种门电路就是集电极开路与非门电路,简称OC 门(open collector)。

OC门电路及逻辑符号见图T1119,该电路的特点是输出管T5的集电极悬空,使用时需外接一个负载电阻R和电源Ec。

POC门的主要用途有以下3个方面:(1)实现与或非逻辑用n个OC门实现与或非逻辑的电路如图T1120所示.因为任何一个门输入全为1时,其输出为零,而n个门的输出端又并接在一起(线与),故输出Y=0,即Y=A1B1+A2B2+……+A nB n,是与或非的逻辑功能。

2.4 TTL特殊门电路

Y

A B

&

EN

Y

低电平有效 0有效

EN

4) 低电平有效的三态门电路结构

5) 三态门应用1-总线结构

1 0

0

5) 三态门应用2-双向传输 0 1

*3. TTL集成逻辑门电路系列简介 1.74系列——为TTL集成电路的早期产品,属中速TTL器件。 2.74L系列——为低功耗TTL系列,又称LTTL系列。 3.74H系列——为高速TTL系列。

2) 三态门电路结构与工作原理

2) 三态门电路结构与工作原理

影响 Vc1 不影响 V =0 V c1c1

D导通 VC2=0

Y悬空 Y=A B 高阻态 0 1 0 1

3) 三态门逻辑符号(三态与非门)

A B EN &

EN

Y

A B

&

EN EN

Y

高电平有效 1有效

3) 三态门逻辑符号

A B EN EN &

2.4 TTL特殊门电路

1. 集电极开路门( OC门) 1) OC 门电路结构

在工程实践中,有时需要将几个门的输出端并联使用。普通的 TTL门电路输出端不能并联使用。为此,生产了集电极开路门。

当输入有低电平 使T5截止时,只 有很小的漏电流 流入门里的T5的 集电极。可认为 此时门的输出端 处于高阻状态。

4.74S系列——为肖特基TTL系列,进一步提高了速度。 5.74LS系列——为低功耗肖特基系列。 6.74AS系列——为先进肖特基系列,它是74S系列的后继产品。 7.74ALS系列——为先进低功耗肖特基系列,是74LS系列的后 继产品。

小结 pOC门工作原理及其应用 pTS门工作原理及其应用 pTTL系产品

OC门和三态门的应用

三态门和 OC 门的应用一、实验目的:通过对三态门和 OC门测试,一方面巩固万用表和示波器的操作,另一方面加深对门电路的逻辑功能认识和探索它们的实际应用。

二、实验内容:1.静态测试三态门的逻辑功能与参数的关系2.动态测试三态门的逻辑功能。

完整记录波形图。

3.静态测试OC 门的逻辑功能,总结电阻的 R 作用。

4.用多个三态门构造一个传输门。

5.用两个 OC 门构造一个门控器,正半周输出 100KHz 的脉冲,负半周输出 500KHz 的脉冲。

三、实验步骤:1.三态门 74LS125 的静态测试:用万用表测量三态门的输入输出电压。

列表记录测量结果。

G A Ylogic V(V) logic V(V) logic V(V)0 0 1 3.99 1 3.590 0 0 0 0 0.0831 3.99 1 3.99 高阻 2.471 3.99 0 0 高阻 2.472.测试两输入 OC 与非门 74LS03 的逻辑功能。

说明 OC 门输出端接上拉电阻 R 的作用。

分析 R 值过大或过小,对输出产生的影响。

(1)A logicBlogicYlogic V(V)0 0 高阻 2.470 1 0 0.141 0 高阻 2.471 1 0 0.15(2)上拉电阻:2.5kΩ到7.03kΩ3.三态门 74LS125 的动态测试:给三态门输入端加脉冲信号,用示波器观测输入输出波形。

完整记录波形。

测试电路:周期(us)峰峰值(V)占空比(%)输入400 4 50输出400 4 75 李萨如合成(X-Y)结果:7.用两个 OC 门组成一个门控开关,控制信号用 100KHz 脉冲信号,控制信号的正半周显示 500KHz,负半周显示 1MHz 的脉冲信号。

设计电路的原理图:(因为软件中没有74125元件,所以用7400代替其逻辑)利用QUARTUSⅡ功能模拟电路:波形模拟:实际外部电路连接:实验得到的波形图:信号源:实验箱上的200KHz和1MHz,信号发生器100KHz波形数据:周期(us)峰峰值(v)占空比(%)输入10.4 4 50输出10.4 2.8 50四、实验中遇到的问题1、第一次做出第7题时,遇到很多麻烦,首先是自己给自己找了麻烦,把原理图画成了这个样子:后来发现下面的或门被上面的非门屏蔽掉了(或者说写出方程后,这一项就可以约掉)。

oc门芯片

oc门芯片OC门芯片是一种逻辑门芯片,用于实现逻辑功能。

它是由电子元件(如二极管、晶体管等)组成的集成电路,被广泛应用于数字电子技术和计算机科学领域。

OC门芯片可以实现与非门、与门、或非门等逻辑操作。

首先,OC门芯片的原理是基于晶体管的工作原理。

晶体管是一种具有放大和控制作用的电子器件,由P型半导体和N型半导体组成,中间隔着一个绝缘层。

当输入电压作用于绝缘层时,可以控制晶体管的导通和截止。

不同的输入电压组合,可以实现不同的电路逻辑功能。

与非门(NOT Gate)是OC门芯片中最简单的一种。

“与”(AND)和“非”(NOT)是逻辑运算中基本的操作。

与非门的输入只有一个,并且产生与输入相反的输出。

当输入为低电平时,输出为高电平;当输入为高电平时,输出为低电平。

与非门可以用一个三极管和几个电阻电容等元器件实现。

与门(AND Gate)是OC门芯片的另一种常见逻辑门。

它有两个或多个输入端和一个输出端。

只有当所有输入信号都是高电平时,输出才为高电平;否则,输出为低电平。

与门一般由多个晶体管和电阻器组成,可以实现多个输入的逻辑与运算。

与门的输出信号可以连接到其他逻辑门芯片的输入端,从而实现复杂的逻辑功能。

或非门(NOR Gate)是OC门芯片中的一种逻辑门。

它有两个或多个输入端和一个输出端。

当所有的输入信号都是低电平时,输出为高电平;否则,输出为低电平。

或非门的实现方法比较复杂,通常由多个晶体管和电阻器组成。

除了与非门、与门和或非门,OC门芯片还包括其他一些逻辑门,如或门(OR Gate)、异或门(XOR Gate)、反异或门(XNOR Gate)等等。

这些逻辑门芯片通过不同的输入电压组合,可以实现各种逻辑运算。

在数字电子电路中,OC门芯片经常用于实现逻辑电路、计算器、存储器等。

总之,OC门芯片是一种非常重要的集成电路,可以实现不同的逻辑功能。

它由晶体管和其他电子元件组成,可以在数字电子技术和计算机科学领域有广泛的应用。

数电实验之三态输出门与集电极开路门

三态输出门与集电极开路门一、实验目的1.学习中规模集成门电路的使用。

2.掌握三态输出门的逻辑功能。

3.学会三态输出门的应用。

二 实验原理三态门是一种特殊的门电路,它与普通的门电路有所不同,它的输出端除了通常为高、低电平两种状态外,还有第三种输出状态—高阻状态,处于高阻状态时,电路与负载之间相当于开路。

它有一个控制端(禁止端或使能端)。

三态门按逻辑功能及控制方式来分有各种不同类型,本实验所采用的型号是74LS125为三态输出四总线缓冲器。

三态门主要用途之一是分时实现总线传输,即用一个传输通道(总线),以选通方式传送多路信息。

电路中将若干个三态门输出端直接接在一总线上,使用时,要求只有一个传输信息的TS 三态输出门控制端处于使能,而其余各TS 门的控制端均处于禁止态。

因为由理论课学习我们知道TS 门输出端不允许并联使用。

所以显然不能同时有两个或两个以上的TS 门的控制端处于使能。

2. 本实验所用OC 与非门(集电极开路门)型号为74LS03(2输入四与非门)。

OC 与非门的输出管的集电极是悬空的,工作时输出端必须通过一只外接电阻R L 和电源V CC ’相连接,以保证输出电平符合电路要求。

OC 门的应用主要有以下三个方面1、 利用电路的“线与”特性,可方便的完成某些特定的逻辑功能。

如下图13.2(A )所示,将两个OC 与非门输出端直接并联在一起,则它们的输出Y = F A +F B = 21A A ·21B B =2121B B A A即把两个或两个以上OC 与非门“线与”后,可完成“与或非”的逻辑功能。

2、实现多路信息采集,使两路以上的信息共用一个传输通道(总线)。

3、实现逻辑电平的转换,以推动荧光数码管、继电器、MOS 器件等多种数字集成电路。

图13.1 OC 与非门内部逻辑图(A)(B )图13.2OC 门输出并联运用时负载电阻R L 的选择:图13.1(B )中由n 个OC 与非门“线与”驱动有m 个输入端的N 个TTL 与非门,为保证OC 与非门输出电平符合逻辑要求,负载电阻R L 阻值的选择范围为;R L (max ) =IHH H CCmInI V V --'00R L (min ) =ILLML CC I m I V V '--'0式中:I 0H :OC 门输出管截止时(输出高电平)的漏电流(约50uA ) I LM :OC 门输出低电平时允许最大灌入负载电流(约20mA ) I IH :负载门高电平输入电流(<50uA)I IL:负载门低电平输入电流(<1.6m A=V CC’:R L外接电源电压n:OC门个数N:负载门个数m:接入电路的负载门输入端总个数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 6 单向总线传输

表 2 图 6 功能测试表

1A 方波

2A 0

3A 1

1������������ 1 0 1 1

2������������ 1 1 0 1

3������������ 1 1 1 0

Y

附:1HZ 脉冲信号的添加方法

6实验报告要求 (1) 画出实验电路图或测试图,设计相关表格。 (2) 记录测试所得数据,并对结果进行分析。 7思考题 (1) 门电路的输出结构有几种形式,哪些结构的输出可以并联使用? (2) 在OC 门应用电路中,若输出不接电源与电阻,将会产生什么结果? (3) 在实验5中,若出现两个以上控制端同时有效,将会产生什么后果?

0

4.选通电路 如图5所示,1A、2A、1������������分别接数据开关,Y 接电平指示器logicprobe。按表2 中的不同状 态输入,同时观察Y 的状态并填入表中,根据结果分析选通电路的工作原理。 表 2 图 5 功能测试表 1A 2A Y 1������������

0

0

0 0 1 1 0 0 1 1

因此与非型OC 门线与后可号

图2 OC门线与功能的实现

2.三态门(TS 门) 三态门也是一种输出端能并联使用的门电路。它除了通常的高电平和低电平两种输出状态 外,还有第三种输出状态高阻态。处于高阻态时,电路与负载间相当于开路。图3 为与非型TS 门的内部电路和逻辑符号。 图3 表示控制端������������=0 时,三态门处于正常工作状态,实现Y= AB 的功能;当������������=1时为 禁止工作状态,Y 输出呈高阻状态。这种在控制端低电平时电路才能正常工作的工作方式称控 制端低电平有效。对应还有控制端高电平有效的器件。 三态电路最重要的用途是实现多路信息的采集,即用一个传输通道(或称总线)以选通的 方式传送多路信号。这种总线结构工作时特别要注意控制端不能同时有效,即一个时刻只允许 一个控制端有效,否则会损坏器件。

图 3 带 3 态控制端的与非门 四实验内容与步骤 1. 测试74LS03(2 输入4 与非OC 门)的逻辑功能

图4 74LS03与74LS125逻辑引脚图 要求画出测试图,自拟表格,验证其与非功能。 2.用OC 门实现线与功能 按图2 接线,取RL=5.1kΩ。将1A、1B、2A、2B分别接数据开关,Y接电平指示器,测试并将 测试结果填入自设计真值表中,归纳输出Y的表达式。 3.测试74LS125(4同相三态门,也称4总线缓冲器)的逻辑功能,逻辑引脚见图4。 要求画出测试图,测试并将测试数据填入表1 中。 表1 74LS125测试真值表 输出 Y 控制端������������ 输入 A 电压(V) 1 x 0 1 逻辑状态

实验3OC门与TS门

一实验目的 (1) 掌握集电极开路门的使用方法。 (2) 掌握三态门的逻辑功能及使用方法。 二实验仪器与器件 实验器件:74LS03、74LS125 各一片,电阻5.1kΩ一个。 虚拟仪器:信号发生器(1 赫兹方波),电平指示器(logicProbe),电平输入器(logicState) 三实验原理 1.集电极开路门(OC 门) 在数字系统中,有时需要把两个或两个以上门电路的输出端连接起来,去完成一定的逻辑 功能。 但普通TTL 门电路的输出是不容许直接连接的, 因为它们的输出部分是推拉式电路结构。 集电极开路门就是将推拉式输出改为三极管集电极开路输出的特殊TTL电路。图1是与非型OC 门的内部电路和逻辑符号。OC门在使用中必须外接集电极负载电阻RL和电源VCC,才能获得正 常的逻辑功能,且输出可以并联使用,如图2 所示。输出相连点Y具有线与功能,即只要其中 有一个OC门的输出为“0”,Y就为“0”。只有所有OC门的输出为“1”时,Y才为“1”,其 表达式为:

0 1 0 1 0 1 0 1

图 5 选通电路

5.单向总线传输 如图6所示,1A接1HZ脉冲信号,2A接“0”,3A接“1”,1������������、2������������、3������������分别接数据开关 并均置“1”。然后按表3 状态设置(分别将一个控制端置“0”),同时观察Y的状态并填入 表中。