DDR+SDRAM控制器的设计与验证

DDRSDRAM基本原理详细介绍

DDRSDRAM基本原理详细介绍DDRSDRAM是一种双倍速率同步动态随机存取存储器,广泛应用于计算机内存和其他高速嵌入式系统中。

DDR代表双倍数据率,SDRAM代表同步动态随机存储器。

DDRSDRAM通过提供更高的带宽和更低的延迟来提高系统性能。

1.双倍数据率:DDRSDRAM采用了双倍数据率技术,可以在每个时钟脉冲周期内传输两个数据,即在上升沿和下降沿都进行数据传输。

这使DDRSDRAM的数据传输速度是传统SDRAM的两倍。

2.同步动态随机存取存储器:DDRSDRAM是一种动态存储器,与静态存储器相比,它的存储单元更小,容量更大。

DDRSDRAM是同步存储器,意味着所有数据传输都需要与系统时钟同步。

3.预充电:DDRSDRAM在读写操作之前需要进行预充电操作。

预充电操作是将存储单元的电荷置为预定的电平,以便于下一次读写操作。

预充电操作在时钟信号的上升沿进行。

4.时序:DDRSDRAM的时序包括预充电时间、平均访问周期、行切换延迟、列切换延迟、CAS延迟等。

这些时序都是根据具体DDRSDRAM芯片的规格进行设置的,用于保证数据的正确传输和存取。

5.控制信号:DDRSDRAM有许多控制信号,其中包括时钟信号、写使能信号、读使能信号、行地址线、列地址线等。

时钟信号用于同步操作,写使能信号和读使能信号用于控制存取操作,行地址线和列地址线用于指定存储单元的位置。

6.数据通路:DDRSDRAM的数据通路分为前端数据总线和背面数据总线。

前端数据总线用于数据的输入和输出,而背面数据总线用于数据在存储芯片内部的传输。

前端数据总线和背面数据总线的宽度决定了DDRSDRAM的带宽。

7.控制器:DDRSDRAM的控制器位于存储芯片的内部,负责管理存储芯片的读写操作。

控制器与计算机系统的主控制器进行通信,接收来自主控制器的指令并执行相应的操作。

8.刷新:DDRSDRAM是一种动态存储器,需要定期刷新以保持数据的稳定性。

DDR区别

SDRAMSDRAM是Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,是前几年普遍使用的内存形式。

SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与EDO内存相比速度能提高50%。

SDRAM基于双存储体结构,内含两个交错的存储阵列,当CPU从一个存储体或阵列访问数据时,另一个就已为读写数据做好了准备,通过这两个存储阵列的紧密切换,读取效率就能得到成倍的提高。

DDR严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,部分初学者也常看到DDR SDRAM,就认为是SDRAM。

DDR SDRAM是Double Data Rate SDRAM的缩写,是双倍速率同步动态随机存储器的意思。

DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。

SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而DDR 内存则是一个时钟周期内传输两次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。

DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

与SDRAM相比:DDR运用了更先进的同步电路,使指定地址、数据的输送和输出主要步骤既独立执行,又保持与CPU完全同步;DDR使用了DLL(Delay Locked Loop,延时锁定回路提供一个数据滤波信号)技术,当数据有效时,存储控制器可使用这个数据滤波信号来精确定位数据,每16次输出一次,并重新同步来自不同存储器模块的数据。

DDR本质上不需要提高时钟频率就能加倍提高SDRAM的速度,它允许在时钟脉冲的上升沿和下降沿读出数据,因而其速度是标准SDRAM的两倍。

基于FPGA的DDR2 SDRAM存储器用户接口设计

基于FPGA 的DDR2SDRAM 存储器用户接口设计杨斌,段哲民,高峰(西北工业大学电子信息学院,陕西西安710129)摘要:使用功能强大的FPGA 来实现一种DDR2SDRAM 存储器的用户接口。

该用户接口是基于XILINX 公司出产的DDR2SDRAM 的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,可知本设计具有很大的使用前景。

本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速率很高,基本可以满足所有设计需要。

关键词:DDR2SDRAM ;FPGA ;用户接口;DDR2SDRAM 存储控制器中图分类号:TN919.8文献标识码:A文章编号:1674-6236(2012)23-0147-03Design of DDR2SDRAM memory user interface based on FPGAYANG Bin ,DUAN Zhe -min ,GAO Feng(School of Electronic Information ,Northwestern Polytechnical University ,Xi ’an 710129,China )Abstract:The user interface of a DDR2SDRAM memory is implemented by using the powerful FPGA .The user interface is based on DDR2SDRAM memory controller produced by the XILINX company .The company produced such memory controllers with high efficiency and used widely .So that this design has great prospects .Through the simulation of multi -channel high -speed data read and write operations we can know that it can fully meet the timing requirements .Through the synthesis results we can know that the use of logic resources is very little ,run rate is high .It can basically meet all design needs.Key words:DDR2SDRAM ;FPGA ;user interface ;DDR2SDRAM memory controller收稿日期:2012-08-06稿件编号:201208014作者简介:杨斌(1981—),男,陕西佳县人,硕士研究生。

DDR SDRAM基本原理详细介绍

DDR SDRAM基本原理详细介绍DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据流SDRAM”。

DDR SDRAM在原有的SDRAM的基础上改进而来。

也正因为如此,DDR能够凭借着转产成本优势来打败昔日的对手RDRAM,成为当今的主流。

由于SDRAM的结构与操作在上文已有详细阐述,所以本文只着重讲讲DDR 的原理和DDR SDRAM相对于传统SDRAM(又称SDR SDRAM)的不同。

一、DDR的基本原理有很多文章都在探讨DDR的原理,但似乎也不得要领,甚至还带出一些错误的观点。

这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片I/O总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。

二、DDR SDRAM与SDRAM的不同DDR SDRAM与SDRAM的不同主要体现在以下几个方面。

DDR SDRAM与SDRAM一样,在开机时也要进行MRS,不过由于操作功能的增多,DDR SDRAM 在MRS之前还多了一EMRS阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着DLL的有效/禁止、输出驱动强度、QFC 有效/无效等。

由于EMRS与MRS的操作方法与SDRAM的MRS大同小异,在此就不再列出具体的模式表了,有兴趣的话可查看相关的DDR内存资料。

下面我们就着重说说DDR SDRAM的新设计与新功能。

差分时钟(参见上文“DDR SDRAM读操作时序图”)是DDR的一个必要设计,但CK#的作用,并不能理解为第二个触发时钟(你可以在讲述DDR原理时简单地这么比喻),而是起到触发时钟校准的作用。

由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。

DDR PCB设计

1 引言DDR2(Double Data Rate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用时钟的上升/下降沿同时传输数据的基本方式,但DDR2却拥有2倍的DDR预读取能力(即4位预存取技术)。

此外,DDR2还增加ODT(内建核心终结电阻器)功能,内建合适的端接电阻,避免了以往因片外连接大片终结电阻带来的制板成本增加。

基于FPGA的SDRAM控制器,以高可靠性、强可移植性、易于集成的特点,逐渐取代以往的专用控制器而成为主流解决方案。

本文采用Xilinx公司的Spartan-3A系列FPGA和Hynix公司的DDR2 SDRAM器件HY5PS121621实现DDR2控制器的设计。

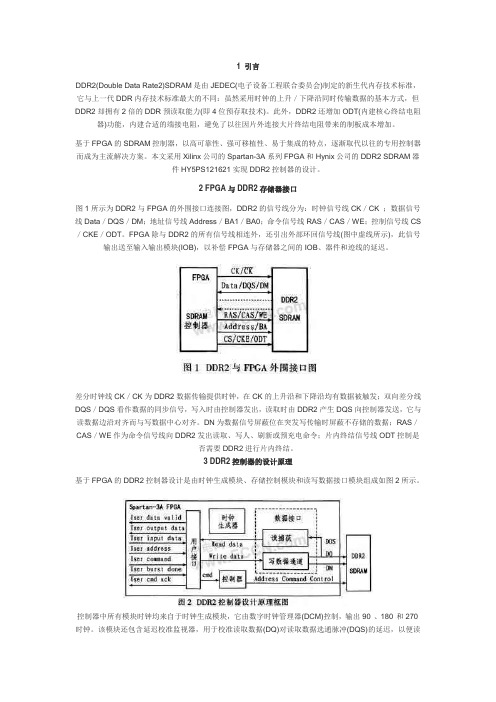

2 FPGA与DDR2存储器接口图1所示为DDR2与FPGA的外围接口连接图,DDR2的信号线分为:时钟信号线CK/CK ;数据信号线Data/DQS/DM;地址信号线Address/BA1/BA0;命令信号线RAS/CAS/WE;控制信号线CS /CKE/ODT。

FPGA除与DDR2的所有信号线相连外,还引出外部环回信号线(图中虚线所示),此信号输出送至输入输出模块(IOB),以补偿FPGA与存储器之间的IOB、器件和迹线的延迟。

差分时钟线CK/CK为DDR2数据传输提供时钟,在CK的上升沿和下降沿均有数据被触发;双向差分线DQS/DQS看作数据的同步信号,写入时由控制器发出,读取时由DDR2产生DQS向控制器发送,它与读数据边沿对齐而与写数据中心对齐。

DN为数据信号屏蔽位在突发写传输时屏蔽不存储的数据;RAS/CAS/WE作为命令信号线向DDR2发出读取、写人、刷新或预充电命令;片内终结信号线ODT控制是否需要DDR2进行片内终结。

3 DDR2控制器的设计原理基于FPGA的DDR2控制器设计是由时钟生成模块、存储控制模块和读写数据接口模块组成如图2所示。

基于FPGA的DDR2存储器控制器设计_河北科技大学.

毕业设计学生姓名:洪雷学号: 09xxxxxxxx 专业:电子科学与技术题目:基于FPGA的DDR2存储器控制器设计指导教师:安国臣(讲师评阅教师:武瑞红(副教授2013年6月毕业设计中文摘要随着消费电类电子产品以及便携式通讯产品向多功能、高性能和低功耗方向的飞快发展,而随之带来的是对大量的数据处理,而产品的系统对其主要的存储设备的要求也越来越高。

目前,DDR2凭着其及其高的数据传输速率和低廉的成本则越来越多的被用到一些高档类的消费类电子和便携式产品中。

对DDR2 SDRAM的控制器处理的设计变得也就非常有必要。

使用FPGA技术设计数字电路,不仅可以简化设计过程,而且还可以减低整个系统的体积和成本,增加系统的可靠性。

本次设计则使用Altear公司的Cyclone V 代器件,经行开发的最小系统。

本次设计使用的是Mircon公司的MT47系列的芯片,借助Altera公司提供的IP 核所自动生成PHY接口。

由于DDR2的读写驱动的要求,多次设计了电压的要求。

本文对DDR2 SDRAM基本结构和原理进行了简单的介绍。

并且阐述基于FIFO和PHY接口的DDR2设计方法。

关键词DDR2 FPGA 存储器控制器 FIFO毕业设计外文摘要Title DDR2 Memory Controller Design based on FPGAAbstractAs consumer electric class electronic products and portable communication products to multi-functional, high performance and low power consumption direction of rapid development, and then brings about a lot of data processing, the product of the system to the main storage device requirements more and more higher. At present, the DDR2 with its and high data transfer rate and low cost are more and more used in some high-end consumer electronics and portable products. Processing of DDR2 SDRAM controller design becomes and is very necessary.Digital circuit design using FPGA technology, not only can simplify the design process, but also can reduce the size and cost of the whole system, increase the reliability of the system. This design USES Altear company Cyclone V generation device, the smallest system development. This design USES the Mircon MT47 series chips, and IP core provided by Altera corporation how can automatically generate the PHY interface. Driven requirements due to DDR2, speaking, reading and writing, and design the voltage requirements for many times.in this paper, the basic structure and principle of DDR2 SDRAM has carried on the simple introduction. And in this paper, the DDR2 design method based on FIFO and PHY interfaceKey Words DDR2 FPGA memory controlle FIFO目录1 绪论 (12 动态随机存储器 (32.1 同步动态随机存储器原理与结构 (32.2 双倍动态随机存储器原理与特点 (32.3 DDR2随机存储器的简介 (43 可编程逻辑器件原理 (73.1 FPGA原理 (73.2 FPGA结构 (73.3 FPGA器件开发的优点 (94 外围电路设计 (114.1芯片的选择和介绍 (114.2 FPGA电源设计 (154.3 FPGA时钟和复位设计 (164.4 FPGA的配置设计 (175 软件设计与仿真 (185.1 FPGA的设计开发流程 (18 5.2 系统设计软件介绍 (195.3 VHDL语言的介绍 (195.4 系统设计 (20结论 (29致谢 (30参考文献 (311 绪论随着大规模、甚大规模的集成电路的设计技术的飞速发展,科技的日益更新,跟随而来的是各种的芯片的弄能不段的变复杂,而同时,数字产品例如掌上电脑、网络设备、音频设备、高清电视等,对高性能的内存的需求也越来越高。

ddr3 sdram-原理图设计

DDR3 SDRAM 篇

DDR3 SDRAM SODIMM

——MT8KTF51264HZ – 4GB

Features:

• • • •Biblioteka • • •204-pin,SODIMM 4GB (512Meg x 64) VDD = 1.35V (1.283–1.45V) VDD = 1.5V (1.425–1.575V) VDDSPD = 3.0–3.6V Single rank Fixed burst chop (BC) of 4 and burst length (BL) of 8

数据信号:DQ[63:0]、DM[7:0] 地址信号:BA[2:0]、A[15:0]、SA[1:0] 命令信号:RAS#、CAS#、WE#、CKE

DDR3涉及4种电源:

• • • • VDD :DDR3内核工作电压,为1.5V VREF:SSTL_15参考电压,为VDD/2 VTT :SSTL_15终结电压,为VDD/2 VDDSPD :SPD芯片及温度传感器的工作电压,为3.3V

Serial data: Used to transfer addresses and data into and out of the temperature sensor/SPD EEPROM on the I2C bus.

SDA

I/O

EVENT#

Output ( open drain)

Temperature event: The EVENT# pin is asserted by the temperature sensor when critical temperature thresholds have been exceeded.

FPGA引脚设置

ddr3控制器

ddr3控制器ddr3理论带宽计算:若最⼤时钟频率400MHZ,数据位宽是16位,也就是16根数据线,ddr是双沿传输,则理论带宽为2*400MHZ*16 = 12800Mbit/s =1600Mbyte/s = 1.5625Gbyte/s1:在IP核列表⾥的Memory interface generator可调⽤ddr控制器并对参数进⾏设置2:对IP核进⾏初始化在调取 DDR3 SDRAM 控制器之后,并不可以⽴即使⽤该 IP 核完成 DDR3SDRAM 的读和写的,⽽是要在该 IP 核初始化成功之后,才可以进⾏读和写(1)例化IP核 ⾸先建⽴⼀个顶层⽂件,复制IP核的实例化模板到顶层,观察实例化模板会发现有⼀部分信号是以 ddr3 开头的,此类的信号均为DDR3 SDRAM 芯⽚的引脚变量,因此在顶层模块需要将其设置为端⼝变量,我们需要将此类信号写⼊到顶层模块名后⾯的⼩括号内,并设定好输⼊/输出类型,以及变量的位宽。

在我们调取 IP 核之后,会在 Vivado ⼯程⽬录下⽣成⼀个 .\project_1.srcs\sources_1\ip\ddr3_ctrl(ddr3_ctrl 为调取 IP 核的名称)的路径,该路径下⽂件夹内会有三个⼦⽂件夹。

其中,docs 中为该 IP 核相关的⽂档⽂件,⽐如该 IP 核的使⽤⽅法等⽂档都在该⽂件夹中涉及;example_design ⽂件夹中为 Xilinx 官⽅提供的该 IP 核参考⽂件,假如不知道如何使⽤该 IP 核,可以参考该⽂件夹内提供的相关例程(2)仿真测试IP核 在调取 IP 核时,我们已经⽣成了 DDR3 SDRAM 控制器 IP 核的仿真模型⽂件。

打开 example_design ⽂件夹中的sim⽂件夹。

会看到⼀个 ddr3_model.sv ⽂件,该⽂件即为我们的仿真模型⽂件,将该⽂件添加到 Vivado ⼯程的 simulation sources 内,然后将仿真模型ddr3_model.sv 实例化到 tb ⽂件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

东南大学硕士学位论文DDR SDRAM控制器的设计与验证姓名:朱炜申请学位级别:硕士专业:微电子学与固体电子学指导教师:胡晨20090515摘要摘要随着移动通信、多媒体技术的发展,嵌入式SoC的应用范围越来越广泛,性能要求也越来越高。嵌入式SoC的性能主要取决于嵌入式SoC内核的处理能力和存储器的带宽,而在SoC内核性能越来越高的情况下,存储器带宽成为了SoC整体性能提升的瓶颈。综合考虑性能、成本、功耗等因素,DDR(DoubleDataRate)SDRAM存储器对于高速嵌入式系统是一个很好的选择,研究设计DDR

SDRAM控制器有着重要的意义。本文在“Garfield”系列SoC芯片架构下设计了一款高性能DDRSDRAM控制器。介绍了DDRSDRAM存储器的基本工作原理,给出了DDRSDRAM支持的指令和典型的操作时序:按照JEDECDDRSDRAM规范制定了详细的DDRSDRAM控制器设计方案,并重点介绍了主要模块的设计方

法;参考典型的SDRAM存储器优化策略,在现有的SoC芯片架构下优化了控制器,尽可能在DDRSDRAM处于空闲状态时进行刷新操作,并通过改进映射策略来充分利用SDRAM的行缓冲区,提高了控制器的效率;将本设计集成到SoC仿真平台中,使用Synopsys公司的VCS对该控制器进行了功能仿真,并建立了相应FPGA原型。仿真和FPGA验证的结果表明:控制器达到了预定的设计指标,能够兼容多种规格的DDRSDRAM。基于基准程序Dhrystone和STREAM的评估结果表明:DDRSDRAM控制器优化后,系统存储器带宽提高了17.8%、性能指标DMlPS提高了30.6%。

关键词:DDRSDRAM;刷新控制;地址映射AbstractAbstractWiththequickdevelopmentofmobilecommunicationandmultimediatechnology,theembeddedSoC

hasbeenwidelyused.Andtheperformancerequirementsofithavebecomemorestringent.Performanceof

embeddedSoCmainlydependsonthegOrespeedandthememory

bandwidth.However,withthe

increasingspeedofcore,thememory

bandwidthhasbecomethebouleneckofSoCperformance.Onthe

basisofconsideringperformance,cost,powerconsumptionandotherfactors,DDR(DoubledataRate)SDRAMisagoodselectionforhi}ghspeedembeddedsystems.Therefore,theresearchanddesignofDDR

SDRAMcontroller

areof

great

significance.

TheDDRSDRAMcontrollerwithhi【ghefficiencyandstabilityisimplementedundertheframework

of“Garfield'’sedesSoC.Firstly,basic

principlesofDDRSDRAMareintroduced,aswellassupported

instructionsandtypicaloperationtiming.Sengondly,theschemeofthedetaileddesign,whichisin

accordancewiththeJEDECDDRSDRAMspecification,ispresented.Thedesignmethodsof

important

modulesarealsogiven.Thirdly,asa

referenceofthe

general-purposememorycontrollingstrategy,the

DDRSDRAMcontrollerisoptimizedundertheframeworkofcurrentSoC.TherefreshoperationisexcutedassoonastheDDRSDRAMisidle.AndtheaddressmappingstrategyisalsoimprovedtotakefulladvantageofSDRAM’Srowbuffer.Theefficiency

ofthecontroller

hasbeenhighlyenhanced

by

optimization.Finally,thedesignisintegratedintothesimulationplatformofSoC,and

functional

verificationismadeusingSynopsys’SVCS.TheassociatedFPGAprototypeisalsobuilt.TheresultofsimulationandFPGAverificationdemonstratesthatthedesignreachesthe

expected

designobjective,andthecontrolleriscompatiblewithmultipletypesofDDR

SDRAM.Theperformance

evaluationbasedonDhrystoneandSTREAMbenchmarkdemonstratesthatbyusingtheoptimizedDDRSDRAMcontrollerthememorybandwidthhasbeenincreasedby17.8%andthesystem’SDMIPSindicatorhasbeenincreasedby30.6%.

Keywords:DDRSDRAM;refreshcontrolling;addressmapping

Ⅱ图表目录图表目录图1.1DRAM芯片的发展………………………………………………………………………………….2图1.2“Garfield”系列SoC芯片构架图……………………………………………………………………4图2.1DRAM存储单元结构图……………………………………………………………………………6

图2.2SDRAM存储结构图……………………………………………………………………………….7图2.3SDRAM芯片结构图…………………………………………………………………………………8图2_4DDRSDRAM与SDRSDRAM数据传输特性对比………………………………………………9

图2.5DDR读操作时序图……………………………………………………………………………….12图2-6DDR写操作时序图……………………………………………………………………………….13图2.7DDR刷新时序图………………………………………………………………………………….13图2.8DDR

SDRAM上电操作……………………………………………………………………………14

图2.9DDR初始化时序图…………………………………………………………………………………14图3.1外部存储器接口结构图…………………………………………………………………………。16图3-2DDRSDRAM控制器主要模块结构图……………………………………………………………17

图3.3DDR

SDRAM标准状态机…………………………………………………………………………1

8

图3_4操作状态机………………………………………………………………………………………~20图3.5读写状态机…………………………………………………………………………………………21图3石读数据通道原理图………………………………………………………………………………一22图3.7写数据通道原理图…………………………………………………………………………………22图3.8DQS延时模块…………………………………………………………………………………….23

图3-9刷新控制模块状态机……………………………………………………………………………一24图3.10Self-Refresh模式波形图…………………………………………………………………………24图3.11Power-Down模式波形图………………………………………………………………………..25图3.12低功耗模式状态切换图………………………………………………………………………….26图4.1ClosePage策略……………………………………………………………………………………28

图4.2OpenPage策略……………………………………………………………………………………~29

图4.3优化前的刷新策略………………………………………………………………………………。3l

图4—4优化后的刷新策略…………………………………………………………………………………32图4.5优化前后的地址映射策略…………………………………………………………………………33图4_6各种策略下系统时钟数与SDRAM命令总数对比……………………………………………..34

图4.7各种策略下Activate和Precharge命令数对比………………………………………………….35图5.1仿真平台结构图……………………………………………………………………………………36图5.2读写测试流程图…………………………………………………………………………………。37图5.3DDRSDRAM控制器初始化波形图……………………………………………………………..38图5-4DDRSDRAM控制器突发写数据波形图………………………………………………………。38图5.5DDR

SDRAM控制器突发读波形图………………………………………………………………39

图5.6Self-Refresh波形图……………………………………………………………………………….39

图5.7Power-Down波形图……………………………………………………………………………….39

图5.8后仿真波形图……………………………………………………………………………………。40图5-9FPGA开发板………………………………………………………………………………………4l图5-10FPGA内部时钟结构图………………………………………………………………………….4lIV