基于SOC的SDRAM控制器的分析与设计

一种基于SOC的FLASH替换设计

一种基于SOC的FLASH替换设计1 引言FLASH存储器具有成本低、密度大、掉电不丢失的特点,在存储器市场中所占的比例越来越大,作为主流SOC重要组成部分,FLASH对SOC作用与影响也越来越大。

由于SOC设计升级或者原有SOC产品存储容量提升等原因,随之会带来其嵌入式FLASH的替换问题,SOC系统设计规模一般较大,设计更改难度和风险都比较大。

除此之外,大部分情况下还需要考虑更改后的设计对原产品的兼容性。

通过在原SOC FLASH控制接口之外增加控制接口转换逻辑实现对新的FLASH IP的连接,可以避免对已成功设计的修改,在达到对FLASH存储器替换的同时降低了设计的风险。

而且由于原FLASH控制逻辑完全固化,只要接口转换逻辑正确,替换后的设计将对原产品完全兼容。

通过对FLASH IP接口与参数的分析,结合对已有SOC中Flash接口时序的要求,设计给出了FLASH控制接口与新FLASH IP之间的接口与时序转换逻辑,并通过仿真,对设计的正确性进行验证。

2 FLASH IP分析2.1 整体介绍设计所选用的Flash存储器是一款CMOS页擦除、16位编程的嵌入式存储器,包含主存储块和信息存储块。

主存储块大小为16k×64,是由128个存储页组成,每个页内有8个行存储单元,每个行又分为16个存储单元,每个存储单元为64位。

信息模块大小为320×64,可用来存储固定信息。

其擦除操作分为页擦除和块擦除两种,页擦除操作擦除一页内的所有字节,块擦除操作擦除整个主存储块。

分立的门单元设计和厚氧化层沟道注入相比于传统的方法获得了更好的可靠性和可制造性。

Flash执行擦除和编程操作只需要1.8 V供电,室温下能够长期保存数据。

2.2 接口分析图1 FLASH接口模块图整体Flash IP的接口如图1所示。

根据功能,可以将接口引脚分为三类:XE、YE、SE、ERASE、PROG、NVSTR、IFREN、MAS1为控制信号线;YADR[3:0]、XADR[9:0]为地址信号;DIN[63:0]、DOUT[63:0]为数据信号。

SOC基础教程5-2 芯片规划与设计(1学时)

逻辑分析系统

server× HP server×20

网络分析仪 频谱分析仪 可编程电源

6GHZ混合信号测试 6GHZ混合信号测试

3

SoC芯片的组成 芯片的组成

SoC芯片应包括哪些模块? 系统总线 存储器/存储器控制器 DMA控制器 电源管理模块 RTC 通用GPIO 嵌入式微处理器内核 中断控制器 锁相环 定时器 watchdog 通信控制 …

SoC芯片 SoC芯片

LCDC

GPS_B

32bit SRAM ROM FLASH

高性能嵌入式SoC微处理器 高性能嵌入式SoC微处理器 SoC 以多媒体信息终端为主要应用产品 特点: 特点: ARM926EJ 32位RISC内核 32位RISC内核 工艺,300MHz主频 0.13uM 工艺,300MHz主频 低功耗设计 特色外设 片上媒体解码模块 片上GPS基带 片上GPS基带 GPS

4

SEP3203

5

SEP0718

6

高性能编解码芯片-多媒体通信终端类SEP5010 高性能编解码芯片-多媒体通信终端类SEP5010

RTC/WD TIMER*1 0 INTC G P I O SSI B UART*3 SD/MMC AC97 DPLL1 USBD DPLL2 ARM926EJ U S PMC A P B Bridge & DMA AHB BUS SDRAM NAND FLASH

9

功能需求( 功能需求(续)

根据用户提出的要求,研发包含两部分内 容,

–一部分是芯片设计, –一部分是桌面视频播放软件设计.

10

功能需求( 功能需求(续)

芯片设计功能

–可接驳标准的嵌入式CMOS Sensor摄像头(标 准手机内嵌的摄像头模块); –压缩图像能够支持 QCIF等MPEG4格式; –最大播放帧数 15帧/S ,用户可以通过桌面 软件配置播放帧数; –拍摄的视频图像以数据流形式直接存入SD卡 –对视频数据流进行简单的加密 –电池供电,片内集成1.8V LDO –低功耗,预计可支持不低于4个小时的视频采 集和存储

【优秀毕业论文】基于soc系统的12位saradc的设计

上海交通大学硕士学位论文基于S O C系统的12位SARADC 的设计DESIGN OF A 12 BIT SUCCESSIVE APPROXIMATION REGISTER ADC IN SOC SYSTEM硕士姓名:沈奇臻专业:电路与系统学号: 1060349010指导教师:戎蒙恬上海交通大学二零零八年十二月DESIGN OF A 12 BIT SUCCESSIVE APPROXIMATION REGISTER ADC IN SOC SYSTEMByShen QizhenADVISOR: Prof. Rong MengtianA THESIS SUBMITTED TOSHANGHAI JIAO TONG UNIVERSITYIN PARTIAL FULFILLMENT OF THE REQUIREMENTSFOR THE DEGREEOF MASTER OF SCIENCEDepartment of Electrical Engineering ofShanghai Jiao Tong UniverisityDecember 2008II基于S O C系统的12位SARADC 的设计摘 要在现在的各种应用SoC系统中,由于系统的高性能、低功耗、低成本要求,一定会把数模转换器(ADC)模块作为一个必不可少的组成部分和其他的模拟模块以及数字模块一起集成于一块芯片上,这已经是种必然的趋势。

正是由于这个原因,一种能够与数字工艺兼容的ADC的设计就变得很必要。

SARADC是一种常见的ADC的结构,由于其本身的小尺寸低功耗的特点,非常适合应用于SoC系统。

本文设计的就是这样一个应用于SoC系统的,能够面向触摸屏应用的ADC模块。

它基于TSMC 0.18um 的1P5M工艺,总共包括了模拟电路中的比较器电路、DAC电路、触摸屏驱动电路,输入通道选择电路以及数字电路的移位逻辑控制电路和时钟频率转换电路。

针对高速低功耗抖动要求,本文给出一种电流按比例缩放结构的DAC结构,并采用温度码和二进制码的分段组合,在明显提高DAC的精度,降低电路的失配和毛刺现象的同时减小芯片的面积和功耗。

基于Nios_II的LCD控制器IP核设计

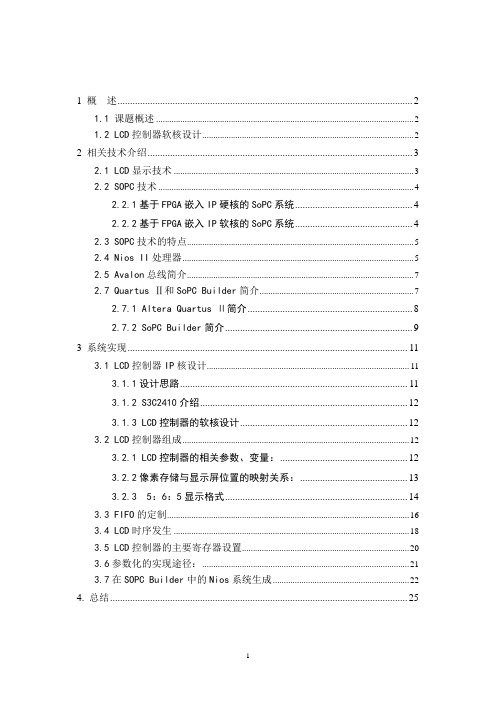

1 概述 (2)1.1 课题概述 (2)1.2 LCD控制器软核设计 (2)2 相关技术介绍 (3)2.1 LCD显示技术 (3)2.2 SOPC技术 (4)2.2.1基于FPGA嵌入IP硬核的SoPC系统 (4)2.2.2基于FPGA嵌入IP软核的SoPC系统 (4)2.3 SOPC技术的特点 (5)2.4 Nios II处理器 (5)2.5 Avalon总线简介 (7)2.7 Quartus Ⅱ和SoPC Builder简介 (7)2.7.1 Altera Quartus Ⅱ简介 (8)2.7.2 SoPC Builder简介 (9)3 系统实现 (11)3.1 LCD控制器IP核设计 (11)3.1.1设计思路 (11)3.1.2 S3C2410介绍 (12)3.1.3 LCD控制器的软核设计 (12)3.2 LCD控制器组成 (12)3.2.1 LCD控制器的相关参数、变量: (12)3.2.2像素存储与显示屏位置的映射关系: (13)3.2.3 5:6:5显示格式 (14)3.3 FIFO的定制 (16)3.4 LCD时序发生 (18)3.5 LCD控制器的主要寄存器设置 (20)3.6参数化的实现途径: (21)3.7在SOPC Builder中的Nios系统生成 (22)4. 总结 (25)1 概述1.1 课题概述本文所要进行描述的设计是运用VHDL语言和Verilog HDL语言,通过分析LCD 控制器的硬件结构和控制时序,使用SoPC技术,把Nios CPU和LCD控制器放在同一个FPGA中。

并通过对相应变量的参数化,实现有一定通用性的LCD IP 核设计。

目的是解决在利用Quartus Ⅱ进行Nios系统开发时,由于内部没有可用LCD的IP,影响产品开发的问题。

1.2 LCD控制器软核设计所要设计的LCD控制器是要求符合Avalon总线规范的。

FPGA中集合了Nios Ⅱ CPU、DMA和LCD控制器模块,以及三态桥(连接Flash)、SDRAM控制器。

SOC中MBIST结构的设计与实现

SOC中MBIST结构的设计与实现作者:黄玮来源:《科技传播》2015年第12期摘要现代SOC电路中,嵌入式存储器所占规模与数量趋于变大,使得测试也越之复杂,目前常用的测试方法是通过eda软件自动生成MBIST电路进行自测试。

该设计基于一个实际的项目,对电路中存储器进行了完整的MBIST结构设计,同时加入了一个标志位移位电路,从而能够准确诊断出故障存储器,最后通过NC_verilog软件完成MBIST结构电路的仿真。

关键词存储器;MBIST;测试;SOC中图分类号TP39 文献标识码 A 文章编号 1674-6708(2015)141-0130-020 引言随着集成电路的规模越来越大,嵌入的存储器也随着变多,传统的测试方法受测试难度和测试成本所制约,已不为芯片设计厂商所接受。

目前存储器最常用的测试方法是通过内建自测试存储器电路[1](MBIST:存储器内建自测试)来实现,其通过eda软件,自动生成存储器的测试电路,根据相应的算法对存储器地址进行读写,完成存储器的测试。

该种测试方法虽然会在电路中加入一些控制逻辑,从而增加芯片的面积,但是对于大规模测试电路,其能够实现测试自动化,减小测试时间,提高测试覆盖率,很大程度上节约测试成本。

本文采用MBIST测试方法,完成对电路中存储器的测试,同时加入了标志位移位电路,能够准确判断错误存储器的位置,从而减少测试诊断时间。

1 MBIST结构介绍MBIST是以存储器为目标,通过采用特定的算法,来检测存储器中存在的某些缺陷的一种测试方法,其主要由bist控制电路,测试向量生成电路,测试响应比较电路三部分组成[2-3],其常用的结构图如图1所示。

图1 MBIST电路结构图1中bist控制电路其内部为一个状态机电路,控制bist电路对存储器进行读写操作;测试向量生成电路根据所选的算法生成不同的测试向量,不同的算法可以得到不同的存储器测试覆盖率;测试响应比较电路是通过对实际存储器输出值与控制电路生成的理想值做对比,来判断存储器是否有问题。

Synopsys SoC 架构设计指南说明书

IP加速DesignWare IP,针对您的SoC进行调整从一开始就保证正确的 SoC 架构每一个复杂的 SoC 设计都是在巨大的上市时间压力下创建出来的。

随着软件内容的增加以及更多IP (以及更复杂IP)被集成,设计人员面临着在不过度设计 SoC 的情况下性能、功耗和面积目标等诸多挑战。

作为您的设计团队的一员,Synopsys 的 SoC 架构设计顾问将帮助您的 SoC 在正确的起点开始。

顾问们已经准备好将他们多年的设计手机、汽车、网络和物联网 SoC 的专业技能应用到您独特的设计中。

这些顾问将在以下方面应用并分享他们的深厚知识:• CPU、DSP和 ASIP 功能• 制定低功耗策略• 关键模块的设计(RTL,ASIP)• PPA 估算• 内存架构,总线带宽/延迟• 验证和基于 FPGA 的原型设计与您的 SoC 一样独特的 IP在为您的快节奏的市场打造 SoC 时,如果能够把针对您的设计调整的 IP 整合到一起,这将会为您带来竞争力上的优势。

然而现成的 IP 已经不足以应对您的设计挑战。

我们期待 IP 供应商能提供更多解决方案,包括简化 IP 配置和集成以及加速软件开发等。

Synopsys的“ IP 加速”计划将重新定义您对 IP 供应商的期望,它能帮助您以更少的功夫、更低的风险和更快的上市速度成功地将IP集成到您的 SoC 中。

“Synopsys团队提出了详细的建议来测试并构建我们 AI SoC的复杂接口,帮助确保我们按时启动项目。

”〜 一家领先的人工智能计算公司的研发总监预先验证的 IP 子系统,可由您或我们的团队 进行定制随着硬件和软件复杂性的增加,您需要更先进的集成 IP 解决方案来满足您快速的项目进度,同时还不能影响质量。

无论您需要单个控制器和 PHY 集成、多种协议的组合或者是需要具有处理器及软件堆栈的完整子系统,Synopsys 专家都能够交付针对您的 SoC 进行优化的 IP 子系统。

soc设计知识点总结

soc设计知识点总结SOC(System on Chip)指的是在一个芯片上集成了一系列功能模块,包括处理器、存储器、I/O接口等,使得整个系统可以在一个单一的芯片上完成。

SOC设计是现代集成电路设计的重要领域,本文将对SOC设计的关键知识点进行总结。

一、SOC设计概述SOC设计是一项综合性工程,涉及到多个学科和技术领域。

在SOC设计过程中,需要考虑以下几个核心要素:1. 系统架构设计:确定系统的功能需求和整体结构,包括处理器的选择、总线结构、存储器层次结构等。

2. IP核集成:选择合适的IP核并进行集成,对SOC的功能和性能起到关键作用。

IP核可以是自己设计的,也可以是从第三方获取的。

3. 性能优化:通过对系统进行优化,提升其性能表现。

优化可能涉及到处理器架构、存储器等方面。

4. 功耗管理:SOC设计中功耗管理是一个重要的问题,需要采取适当的手段减少功耗,以实现低能耗的设计。

5. 验证和调试:验证设计的正确性和性能是否满足需求,并进行调试修复问题。

二、SOC设计中的关键技术1. 处理器架构:SOC设计中处理器的选择和架构设计是一个重要的决策。

常见的处理器架构有ARM、MIPS等,选择适合应用场景的处理器架构可以提高系统性能。

2. 存储器层次结构:SOC设计中存储器的选择和层次结构的设计对系统性能有着重要影响。

常见的存储器包括寄存器、高速缓存、SDRAM等,通过合理的存储器层次结构设计可以提高系统的存取速度。

3. 总线设计:SOC中各个模块之间的通信需要通过总线来实现。

总线设计需要关注带宽、延迟、支持的传输协议等方面,合理的总线设计可以提高系统的性能。

4. 通信接口设计:SOC设计中的I/O接口设计对于系统的外部通信起到重要作用。

常见的接口包括UART、SPI、I2C等,通过设计高效的接口可以提高系统的数据传输速率。

5. 时钟和时序设计:SOC设计中需要考虑各个模块之间的时钟同步和时序关系。

合理的时钟和时序设计可以确保系统正常工作,避免由于时序问题而引起的故障。

ddr3 sdram-原理图设计

DDR3 SDRAM 篇

DDR3 SDRAM SODIMM

——MT8KTF51264HZ – 4GB

Features:

• • • •Biblioteka • • •204-pin,SODIMM 4GB (512Meg x 64) VDD = 1.35V (1.283–1.45V) VDD = 1.5V (1.425–1.575V) VDDSPD = 3.0–3.6V Single rank Fixed burst chop (BC) of 4 and burst length (BL) of 8

数据信号:DQ[63:0]、DM[7:0] 地址信号:BA[2:0]、A[15:0]、SA[1:0] 命令信号:RAS#、CAS#、WE#、CKE

DDR3涉及4种电源:

• • • • VDD :DDR3内核工作电压,为1.5V VREF:SSTL_15参考电压,为VDD/2 VTT :SSTL_15终结电压,为VDD/2 VDDSPD :SPD芯片及温度传感器的工作电压,为3.3V

Serial data: Used to transfer addresses and data into and out of the temperature sensor/SPD EEPROM on the I2C bus.

SDA

I/O

EVENT#

Output ( open drain)

Temperature event: The EVENT# pin is asserted by the temperature sensor when critical temperature thresholds have been exceeded.

FPGA引脚设置

重庆大学SoC设计第2章

• 模块设计及IP复用(Module Design & IP

Reuse)

硬件设计定义说明描述芯片总体结构、规格参数、模块 划分、使用的总线,以及各个模块的详细定义等。

对于需要重新设计的模块进行设计;对于可复用的IP核 ,通常由于总线接口标准不一致需要做一定的修改。

基于标准单元的SoC芯片设计流程

Motion Estimation Accelerator IP External Memory External Memory Controller

ARM920T

DSP CHIP

AHB

On chip memory controller and memory

Direct Memory Access (DMA)

基于标准单元的SoC芯片设计流程

• 形式验证(Formal Verification)

• 可测性电路插入(DFT,Design for Test)

形式验证也是一种静态验证方法。 在整个设计流程中会多次引入形式验证用于比较RTL代 码之间、门级网表与RTL代码之间,以及门级网表之间 在修改之前与修改之后功能的一致性。 可测性设计是SoC设计中的重要一步。通常,对于逻辑 电路采用扫描链的可测试结构,对于芯片的输入/输出端 口采用边界扫描的可测试结构。基本思想是通过插入扫 描链,增加电路内部节点的可控性和可观测性,以达到 提高测试效率的目的。一般在逻辑综合或物理综合后进 行扫描电路的插入和优化。

Slide 18

硬件顶层设计-例子

确定软硬件划分

• • •

软件 灵活性好 性能有待提高 充分利用硬件资源,如处理器 硬件 不够灵活 达到较好的功耗/性能折中 软硬件划分 把系统功能划分为软件部分和硬件部分 定义和明确软硬件接口和通信协议 需要经验丰富的人员依靠人工完成 一个包含可重用核和可重用软件的库,有助于软硬件评估和划分

soc设计知识点总结

soc设计知识点总结一、芯片架构设计1. 总线结构设计总线是芯片内各个功能模块间进行数据传输和通信的基础设施,是整个系统的“血管”系统。

在设计SOC时,需要考虑总线的带宽、延迟、复用性等因素,以满足各个功能模块之间的数据传输需求。

2. 存储器系统设计存储器系统包括内存子系统、缓存子系统和存储控制器等部分。

在SOC设计中,需要考虑存储器系统的容量、访问速度、数据一致性、功耗等因素,确保系统具有良好的性能和低功耗。

3. 电源管理电源管理是SOC设计中非常重要的一个方面,它涉及到芯片的功耗控制、电源分配和管理、时钟管理等。

在SOC设计中,需要考虑如何设计有效的电源管理方案,以降低芯片的功耗,并提高系统的稳定性和可靠性。

4. 硬件安全硬件安全是SOC设计中一个非常重要的方面,它涉及到如何设计安全的硬件结构,如何保护系统不受恶意攻击和非法访问。

在SOC设计中,需要考虑如何设计安全的存储器结构、综合电路结构、加密解密和安全存储等功能,以提高SOC系统的安全性。

5. 集成测试在SOC设计中,集成测试是非常重要的一个环节,它涉及到如何验证各个功能模块的正确性和功能完整性,以及各个功能模块之间的协同工作。

在SOC设计中,需要设计有效的集成测试方案,包括逻辑仿真、时序仿真、功能仿真、硬件验证和验证等环节,以确保SOC系统具有良好的稳定性和可靠性。

二、处理器设计1. CPU核心设计CPU核心是SOC设计中的核心部分,它负责控制整个系统的运行和数据处理。

在SOC设计中,需要考虑如何设计高性能的CPU核心,包括指令集架构、流水线结构、指令级并行执行、分支预测等技术,以提高CPU核心的性能和效率。

2. 浮点运算单元设计浮点运算单元是处理器设计中的另一个重要部分,它负责处理浮点运算指令。

在SOC设计中,需要考虑如何设计高性能的浮点运算单元,包括浮点运算指令集、寄存器文件、乘法器、除法器等功能部件,以提高浮点运算单元的运算速度和精度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2007耳第12期 中图分类号:TP331 文献标识码:A 文章编号:1009—2552(20Or7)12—0081—03

基于SOC的SDRAM控制器的分析与设计

李 瑞,赵建明,冀力强 (电子科技大学微电子与固体电子学院,成都610054) 摘 要:介绍了SDRAM的内部结构和工作原理,根据时序参数对存取速度的影响,利用优化的状 态机对核心控制模块进行设计,减小了存取延时。并通过对波形的仿真,验证了设计的正确性。 关键词:SDRAM;状态机;内存控制器

Analysis and design of SDRAM controller based on SOC LI Rui,ZHA0 Jian—ming,JI Li—qiang (School of Microdectronic and Solid State Electronics,University of Electronic Science and Technology of China,Chengdu 610054,China) Abstract:This paper introduces the principle and internal structure of SDRAM.According to the timing paramerer’S influence on the access rate,it use optimized FSM to design the core of memory controller.The experiments confilTIl the tme of the design by wave emulator. Key words:SDRAM;FSM;memo ̄controller

0 引言 随着半导体工艺和集成电路技术的不断进步,处 理器和缓存技术也得到了长足的发展。一个系统中 集成两个甚至多个处理器已经成为可能,计算机系统 的性能日益受到存储系统的制约,设计实现高效的存 储控制器已成为改善系统性能的关键。面对SDRAM 存储设备复杂的控制逻辑,本文首先对SDRAM的内 部结构和工作原理进行了分析,在此基础上从其内部 时序参数对系统性能制约的角度出发,着重对控制器 内部结构进行优化,以避开传统控制器复杂的状态设 置,采用优化后的状态机对核心控制模块进行设计, 最后给出仿真结果,验证了设计的正确性。 1 SDRAM的内部结构和工作机制 同步动态随机存储器(Synchi'onous Dynamic Random Access Memo ̄)是一种目前被广泛采用的数 据存储器,它在外部同步时钟信号控制下完成数据 的读出和写入。具有容量大、速度快但控制相对复 杂¨J的特点。其内部结构图 如图1所示。 DRAM单元的逻辑状态取决于存储电容的状 态,由于电容不能持久地存储电荷,这就决定了内存 不但要定时刷新,而且每次读操作之后也要刷新一 次,执行一次回写操作。有多个DRAM单元组成的 存储阵列bank结构如图2所示。

列 缓 冲 器

行地址线 列 地 土Ⅱ: 线

存储电容

图1 DRAM的基本单元 行缓冲器

图2 bank的内部结卡句 在实际的SDRAM器件里,由于工艺和封装技 术的制约,最多可以包含4块这样的bank结构,因

收稿日期:2oo7—07—10 作者简介:李瑞(1982一),女,硕士研究生,主要研究方向为深亚微 米高速集成电路的分析与设计。

一8l一

维普资讯 http://www.cqvip.com 此寻址操作中在确定 叶选信号之后要进_步对 bank进行选择(通过bank选择信号ba1,ba0),然后 再在这个选定的bank中根据外部的控制信号RAS (行地址选通脉冲)和cAs(列地址选通脉冲)来触发 相应的行列选通电路。 为了使SDRAM在外部时钟控制下正确工作, 其控制命令必须满足内部参数的约束,全部技术要 涉及到20多个时序参数,其中有三个参数对 SDRAM的性能影响至关重要,即Trcd,CL, 。 Trcd决定了行寻址(有效)至列寻址(读/写命令)之 间的时间间隔;CL决定了列寻址到数据真正被读取 所花费的时间; 则决定了bank中不同工作行转 换的速度。下面将通过对不同情况下的分析,来设 计优化的SDRAM控制器以减少其对读/写时延的影 响,提高其响应速度。 ’ 访问SDRAM存储器主要有以下几种情况: (1)页面命中。如果SDRAM内部行锁存器中已 经保存一部分行地址,与当前需要访问的数据在同 一行中,那么读/写数据不需要等待传感器进行变换 称为页面击中,RAS到CAS延迟时间Trcd为零。只 需要经过cL延迟就能在内存缓冲中调入正确数 据。这是最理想的情况,所需的延时最小。 (2)页面失效。如果SDRAM内部行锁存器中未 保存任何行地址,请求的bank的行地址不是处于打 开的状态,这就叫做页面失效。需要经过Trcd的时 间延迟才能激活要访问的行,图3为页面失效时的 时序图,Trcd=2。读/写数据(与页面击中相比)将增 加Trcd的延时。 \,_厂一\/一 _厂] 厂]厂— /—— 丛一 L一 L—— L一 L—一 L…/t…一 r—矗-一————————————、,———、 ———]r——一 ‘ lAcl lRe L 一/L——一——一 L L— L— A ■~Row一—— _一百一~ 卜}_‘一 × 、、 ..,.一一—— …——.——————.—— — .. . . —./、、..一———— 3 1 1 总幽 (3)页面重新转换。如果SDRAM内部已经保存 某bank的某一行地址,而当前请求的数据位于不同 的行地址称为页面重新转换。这种情况下,灵敏放 大器需要首先回写旧的行地址,然后再激活新的行 地址。回写旧的行地址所占用的时间即 ,如图4 所示。再激活新的行地址所占用的时间为Trcd。读 /写数据延时(与页面击中相比)增加Trcd+Trp,这 是最坏的情况。 在以上三种最常见情况的分析中,为使延时最 一R 一 。 二: X二 【1ll 二 二 )(、 .... 、 .. ..—— . .. . .... ..一 ...—。/、 ...— ,、 .—. /\_-一 : < A 、!:=_ ——_< !: 1 8 0.n, ——一 盼 —弋 一…一…一 、 ! I ...L /I{.r ..... .. ......... ...一 -.■..... ... ... .—— ——一]rI… 4 不蒽图 小,达到最理想的情况,即尽量避免Trcd和1 造成 的影响。Trcd的延时在连续读/写操作中可以减小 为零,为了减小 的影响,可以在对控制器的状态 机设计中进行优化,即每当完成一次读,写操作后都 执行一次PRECHARGE命令,然后再回到空闲状态。 这样页面重新转换的延时1 在一次具体的存取访 问中将减少为零。 2 SDRAM控制器的设计 控制器的主要作用是屏蔽掉SDRAM严格的状 态机管理和刷新操作,以提供一个快速简单且使用 灵活的连续存储器接口,通过对CMD[2:0]的命令 字和ADDR端的地址进行解析,产生相应的SDRAM 的控制时序’,完成初始化、自动定时刷新、存储单元 地址管理、数据读写访问等操作。 由于传统SDRAM控制器的设计多存在结构划 分紊乱,功能模块之间接口信号纷繁芜杂等原因,导 致后续设计的工作量和难度加大。在深刻分析 SDRAM工作原理的基础上,本项目着重对SDRAM 控制器进行结构重组,形成功能清晰,结构明了的三 大模块:控制接口模块、命令模块和数据通道模块。 同时采用优化后的状态机对其进行设计,提高了其 访问速度。图5为SDRAM控制器的结构框图。

5 SDIL ̄M控制器结构框图 控制接口模块由命令接口模块和刷新控制模块 组成。命令接口模块主要负责对系统发出的命令 CMDE2:01进行译码产生相应的请求信号,刷新请求模 块主要产生定期的刷新请求信号,通过[DAD—MODE

维普资讯 http://www.cqvip.com 中的寄存器置人计数初值,由减法计数器产生周期 性的刷新请求信号。 命令模块由仲裁器和命令产生模块组成。仲裁 器通过优先级仲裁对命令接口模块和刷新控制模块 的请求信号进行仲裁,在同一时间内刷新控制模块 的请求信号优先级最高。命令生成模块接受仲裁器 的仲裁结果来触发内部状态机的状态转换,同时根 据SDtLa,M的时序参数和工作模式产生相应的时序 控制信号到SDRAM。命令生成模块由内部包含一 个有限状态机的控制命令产生模块、移位寄存器时 序命令产生模块和地址复用模块三部分构成。结构 框图如图6所示,其中对控制命令产生模块的有限 状态机 按照图7所示流程图进行设计。采用 读/写后自动预充电技术,与传统的控制器状态机设 置相比,在返回空闲状态之前插入了预充电操作,消 除了页面重新转换情况的出现,因此在一次具体的 访问操作中Trp为零。

罔6命令模块的结构框图 SDRAM的时序参数CL,Trcd等时序参数,以及 突发传输长度BL和刷新周期的设置都通过初始化 装载到相应的寄存器中,下文将简单介绍SDRAM 控制器的初始化过程。SDRAM控制器在上电复位 后其初始化过程如下: (1)设定刷新定时器(refresh timer)的预分频参 数,它决定刷新定时器的输入频率(input clock)。 (2)设定刷新定时器的计时时问的长度(或刷新速 度)。亦即设定刷新SDRAM暂存内容的时间间隔。当 此时问终了时,内存控制器自动发出刷新请求。 (3)设定基准地址(base address),大多数的SOC 都是采用多任务式的架构,使用不同种类的内存,不 同的数据端口大小共享使用相同的总线,内存控制 器必须根据基准地址,来和目前所要存取的地址作 比较,确定目前要和那一种内存进行存取操作。 (4)设定存取模式。设定SDRAM的大小、单一一 SDR XM bank的数目、行起始地址位、行地址线的数 目,分页模式等参数。

图7优化后的状态机流程 (5)执行SDRAM的初始化程序。①对所有的 bank执行一次precharge命令一次。②执行CBR refresh命令一次。③执行模式寄存器写命令一次。 ④启动刷新服务,让SDRAM进入正常作业状态。 其初始化过程的仿真波形如图8所示:

图8 SDRAM控制器初始化仿真波形 采用8M的SDRAM的存储器的行为模型,对其 读写操作进行仿真,验证其结果符合设计的预期结 果。图9为其进行突发写的仿真波形,图10为 SDRAM控制器实发读仿真波形。

图9 SD【认M控制器突发写仿真波形 (下转第89页) 一83—