VHDL实验新与答案

四个VHDL实验答案

共6个尾灯,汽车正常行驶时,6个灯全灭;左转时,左边3个灯从右到左依次亮灭;右转时,右边3个灯从左到右依次亮灭;刹车时,车灯全亮;故障时,全部闪烁。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity yu isport(xhd:in std_logic_vector(2downto0);clk:in std_logic;led1,led2,led3,led4,led5,led6:out std_logic);end yu;architecture one of yu issignal l1,l2,l3,l4,l5,l6:std_logic;signal n:std_logic_vector(2downto0);beginprocess(clk,xhd,n)beginif clk'event and clk='1'then n<=n+1;if(xhd>="110")thenl1<='1';l2<='1';l3<='1';l4<='1';l5<='1';l6<='1';elsif(xhd="100")thenif(n="001")or(n="010")then l3<='1';else l3<='0';end if;if(n="011")or(n="100")then l2<='1';else l2<='0';end if;if(n="101")or(n="110")then l1<='1';else l1<='0';end if;elsif(xhd="001")then(l1,l2,l3)<=null;if(n="001")or(n="010")then l4<='1';else l4<='0';end if;if(n="011")or(n="100")then l5<='1';else l5<='0';end if;if(n="101")or(n="110")then l6<='1';else l6<='0';end if;elsif(xhd="010")then l1<='0';l2<='0';l3<='0';l4<='0';l5<='0';l6<='0';elsif(xhd="000")thenif(n="000")or(n="010")or(n="100")or(n="110")thenl1<='1';l2<='1';l3<='1';l4<='1';l5<='1';l6<='1';else l1<='0';l2<='0';l3<='0';l4<='0';l5<='0';l6<='0';end if;end if;end if;led1<=l1;led2<=l2;led3<=l3;led4<=l4;led5<=l5;led6<=l6;end process;end one;设计一个2人抢答器。

VHDL作业及答案1分析

第4节PPT课件作业1.VHDL程序一般包含几个组成部分?各部分的作用是什么?实体,结构体,库,程序包,配置实体:用于描述所设计系统的外部接口特性;即该设计实体对外的输入、输出端口数量和端口特性。

结构体:用于描述实体所代表的系统内部的结构和行为;它描述设计实体的结构、行为、元件及内部连接关系。

库:存放已经编译的实体、构造体、程序包集合和配置。

程序包:存放各设计模块都能共享的数据类型、常数和子程序库;配置:实体对应多个结构体时,从与某个实体对应的多个结构体中选定一个作为具体实现。

2.端口模式有哪几种?buffer类型与inout类型的端口有什么区别?Out, in, inout, bufferout (输出):只能被赋值,用于不能反馈的输出;in (输入):只能读,用于时钟输入、控制输入单向数据输入;inout(输入输出) :既可读又可被赋值,被读的值是端口输入值而不是被赋值,作为双向端口。

buffer(缓冲):类似于输出,但可以读,读的值是被赋值,用做内部反馈用,不能作为双向端口使用。

3.下列标识符中,哪些是非法的?Led3coder_ _1 end port std_machine2adder decoder*8and_2_ _decoder_1 and2 and_2and_ _2 and-24.指出下面的实体描述中存在的四处语法错误并改正LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux21a ISPORT( a, b, s : IN BIT ;y : OUT BIT ;) ; (1.删除括号内的分号)END ENTITY mux; (2.改为mux21a)ARCHITECTURE one OF mux21a ISBEGINPROCESS(a,b,s)Beginif s=‘0’then y<=a ;else y<=b ;end if ;end process (结束少了一个分号)END ARCHITECTURE none ; (none改为one)5.写出下图所示的设计实体mux41的实体声明。

05 第五章 VHDL语言的顺序描述语句 习题答案

填空题1、从执行顺序上划分,VHDL语言可以分为顺序描述语句(Sequential Statements)和并行描述语句(Concurrent Statements)两大类,前者在执行过程中是按照书写顺序依次执行的,而后者则是在同一时间同步执行的,2、顺序描述语句是相对于并行语句而言的,其只出现在进程或者子程序中。

3、标识符赋值目标是以简单的标识符作为被赋值的信号或变量名4、流程控制语句又称为转向控制语句,其特点是通过条件控制开关,决定是否执行或者重复执行或者跳过一条或几条语句。

5、VHDL语言的IF语句是选择分支语句。

6、CASE语句根据满足的条件直接选择多项顺序描述语句中的一项执行,可以用来描述总线或编码、译码的行为。

7、LOOP语句是循环语句的一种,可以使所包含的一组顺序描述语句被循环执行,其执行次数由设定的循环参数决定。

8、由于进程的执行是由敏感信号列表来触发的,因此VHDL语言规定在已列出敏感表的进程中不能使用任何形式的WAIT语句。

9、REPORT语句用于程序运行过程中向用编程人员报告程序的运行状态。

10、REPORT语句提供了4级出错等级,包括FAILURE(失败)、ERROR(错误)、WARNING(警告)、NOTE(注意)。

综述题1、简述赋值语句和代入语句的主要区别。

答案:●对于变量的赋值是立即发生的(假设进程已启动),是一种时间延迟为零的赋值行为。

●对于信号的赋值并不是立即发生的,它发生在一个进程结束时。

●当在同一进程中,同一信号目标有多个赋值源时,信号赋值对象只能被最后一个赋值源赋值,前面的任何赋值都不会改变赋值对象的值。

2、VHDL语言的流程控制语句包括哪几种?答案:●IF语句。

•2 •●CASE语句。

●LOOP语句。

●NEXT语句。

●EXIT语句。

3、使用CASE语句的时候有那些注意事项?答案:●条件句中的选择值必在表达式的取值范围内。

●除非所有条件句中的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句中的选择必须用关键字OTHERS表示,它代表已给的所有条件句中未能列出的其它可能的取值。

VHDL电子琴实验报告

VHDL电子琴实验报告

实验目的:

本实验的目的是设计一个VHDL电子琴,通过FPGA实现,实现按键发出不同的音调,并通过扬声器输出对应的音频信号,达到模拟真实电子琴的效果。

实验原理:

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路的行为和结构。

在本实验中,我们将使用VHDL语言描述电子琴的按键和音调的对应关系,通过FPGA实现电子琴的功能。

电子琴实验主要包含两个部分:输入部分和输出部分。

输入部分是按键,按下不同的按键会发出不同的音调。

输出部分是扬声器,通过扬声器输出对应的音频信号。

实验步骤:

1.确定电子琴的按键数量和对应的音调。

2.使用VHDL语言描述电子琴的按键和音调的对应关系。

3.将VHDL代码综合成逻辑电路网表。

4.将逻辑电路网表烧录到FPGA中。

5.连接扬声器到FPGA输出引脚。

6.按下不同的按键,测试扬声器输出的音频信号是否正确。

实验结果:

经过实验测试,我们成功实现了一个简单的VHDL电子琴。

按下不同的按键,扬声器输出对应的音调。

通过调整VHDL代码中的音频频率,可以改变电子琴的音调高低。

实验总结:

通过本实验,我们深入理解了VHDL语言的应用和FPGA的原理。

电子琴作为一个实际应用案例,充分展示了数字电路设计的魅力。

在今后的学习和工作中,我们将能更加熟练地应用VHDL语言和FPGA技术,设计更加复杂的数字电路系统。

VHDL作业及解答

VHDL作业1、读例6.3、6.7、6.9代码。

2、什么是桶形移位寄存器?桶形移位器用来有效地实现移位、循环移位和位操作,被广泛地用于乘法及其他操作中。

桶形移位器可以实现逻辑左移、右移,算术左移、右移等,它可以在一个时钟周期内实现64位同时移位,也可对任何一种数据类型移任意位数。

桶形移位器与ALU并行操作,可加速乘法、除法、位操作,移位和循环移位操作。

3、什么是寄存器和锁存器?三态门实例:entity Buffer ISport(enable,datain: in std_logic;dataout: out std_logic);end Buffer;atchitecture Buffer1 of Buffer ISbeginprocess(datain,enable)beginif (enable= ‘1’) thendataout <= datain;elsedataout <= ‘Z’;end if;end process;end Buffer1;总线缓冲器entity oeseqbus isport(enable: in std_logic;datain: in std_logic_vector(7 downto 0);dataout: out std_logic_vector(7 downto 0));end oeseqbus;atchitecture sequential of oeseqbus isbeginprocess(datain,enable)beginif (enable= ‘1’) thendataout <= datain;elsedataout <= (others => ‘Z’);end if;end process;end sequential;锁存器实例:library ieee;use ieee.std_logic_1164.all;entity latch isport(datain: in std_lagic;enable: in std_logic;dataout: out std_logic);end latch;atchitecture behav of latch isbeginprocess(datain,enable)beginif(enable = ‘1’) thendataout <= datain;end if;end process;end behav;寄存器:寄存器一般由多位触发器连接而成,通常有锁存寄存器和移位寄存器等。

VHDL参考答案这是我们这学期考的大题都是

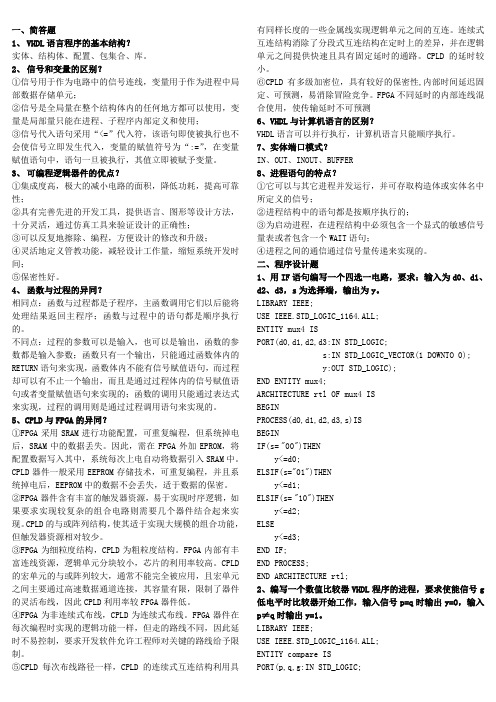

一、简答题1、VHDL语言程序的基本结构?实体、结构体、配置、包集合、库。

2、信号和变量的区别?①信号用于作为电路中的信号连线,变量用于作为进程中局部数据存储单元;②信号是全局量在整个结构体内的任何地方都可以使用,变量是局部量只能在进程、子程序内部定义和使用;③信号代入语句采用“<=”代入符,该语句即使被执行也不会使信号立即发生代入,变量的赋值符号为“:=”,在变量赋值语句中,语句一旦被执行,其值立即被赋予变量。

3、可编程逻辑器件的优点?①集成度高,极大的减小电路的面积,降低功耗,提高可靠性;②具有完善先进的开发工具,提供语言、图形等设计方法,十分灵活,通过仿真工具来验证设计的正确性;③可以反复地擦除、编程,方便设计的修改和升级;④灵活地定义管教功能,减轻设计工作量,缩短系统开发时间;⑤保密性好。

4、函数与过程的异同?相同点:函数与过程都是子程序,主函数调用它们以后能将处理结果返回主程序;函数与过程中的语句都是顺序执行的。

不同点:过程的参数可以是输入,也可以是输出,函数的参数都是输入参数;函数只有一个输出,只能通过函数体内的RETURN语句来实现,函数体内不能有信号赋值语句,而过程却可以有不止一个输出,而且是通过过程体内的信号赋值语句或者变量赋值语句来实现的;函数的调用只能通过表达式来实现,过程的调用则是通过过程调用语句来实现的。

5、CPLD与FPGA的异同?①FPGA采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加EPROM,将配置数据写入其中,系统每次上电自动将数据引入SRAM中。

CPLD器件一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

②FPGA器件含有丰富的触发器资源,易于实现时序逻辑,如果要求实现较复杂的组合电路则需要几个器件结合起来实现。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少。

VHDL实验报告(1)

VHDL 实验报告******班级:电子0701学号:************实验一组合逻辑电路设计一实验目的:1. 熟悉mux+pluxII软件,可以进行新文件的编辑和文件的修改。

2. 掌握门电路VHDL语言程序设计方法。

3. 掌握选择器VHDL语言程序设计方法。

4. 掌握加法器VHDL语言程序设计方法。

5. 熟悉VHDL编程的基本方法。

二实验设备:1.计算机2.Max+PlusII软件三实验原理及内容:1 二输入与门(1)实验原理二输入与门是我们数字电路中的一个基础逻辑门电路,是最基本的逻辑门电路之一,也是最简单的逻辑门之一。

它能实现两个输入端的相与,一般有三个端口。

二输入与门的表达式是:Y=ab二输入与门的逻辑符号如图(1)所示,真值表如表(1)所示。

图(1)与门逻辑符号表(1)与门真值表(2)实验内容a.在mux+pluxII文本编辑环境下,打开新文本,编写两输入与门VHDL语言源程序,程序设计如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY and2 ISPORT(a,b: IN STD_LOGIC;Y: OUT STD_LOGIC);END and2;ARCHITECTURE behave OF and2 ISBEGINY <= a and b;END behave;b.对源程序进行编译,按照提示进行修改,直至编译通过。

c.对编译程序进行仿真,分析并记录仿真波形,其仿真波形图如图(2)所示。

图(2)二输入与门仿真图d.在自己的目录下保存相应的源文件、波形文件。

2 四选一选择器(1)实验原理四选一选择器如图(3)所示,真值表如表(2)所示。

图(3)mux4管脚图表(2)mux4真值表(2)实验内容a.在mux+plusII文本编辑环境下,打开新文件,编辑四选一VHDL源程序文件,其程序设计如下:LIBRARY IEEEUSE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT(A: IN STD_LOGIC_VECTOR (1 DOWNTO 0);D0,D1,D2,D3:IN STD_LOGIC;G:IN STD_LOGIC;Y: OUT STD_LOGIC);END mux4;ARCHITECTURE dataflow OF mux4 ISBEGINPROCESS (A,D0,D1,D2,D3,G)BEGINIF (G ='0') THENIF (A="00")THEN Y <= D0;ELSIF(A="01")THEN Y <= D1;ELSIF(A="10")THEN Y <= D2;ELSE Y <= D3;END IF;ELSE Y <='0';END IF;END PROCESS;END dataflow;b.对源程序进行编译,按照提示进行修改,直到编译通过。

vhdl课后习题答案

vhdl课后习题答案VHDL课后习题答案在学习VHDL(VHSIC Hardware Description Language)这门课程时,课后习题是巩固知识、提高能力的重要方式。

通过认真完成课后习题并查看答案,我们可以更好地理解和掌握VHDL的相关知识,提高自己的编程能力。

下面我们将通过几个典型的VHDL课后习题答案来展示VHDL的魅力和应用。

1. 课后习题一题目:使用VHDL编写一个简单的门电路,包括AND门、OR门和NOT门,并进行仿真验证。

答案:首先,我们定义AND门、OR门和NOT门的输入输出信号。

然后,使用VHDL语言编写各个门电路的逻辑实现,并进行仿真验证。

最后,我们可以观察仿真波形图,验证门电路的功能是否符合预期。

2. 课后习题二题目:使用VHDL编写一个4位全加器,并进行综合、布线和时序分析。

答案:首先,我们定义全加器的输入输出信号。

然后,使用VHDL语言编写4位全加器的逻辑实现,并进行综合、布线和时序分析。

最后,我们可以观察综合和布线报告,分析全加器的资源利用情况和时序性能。

3. 课后习题三题目:使用VHDL编写一个有限状态机(FSM),实现一个简单的计数器,并进行状态转移图和状态转移表的分析。

答案:首先,我们定义有限状态机的状态和状态转移条件。

然后,使用VHDL 语言编写有限状态机的逻辑实现,并进行状态转移图和状态转移表的分析。

最后,我们可以观察状态转移图和状态转移表,验证有限状态机的状态转移是否符合预期。

通过以上几个VHDL课后习题答案的展示,我们可以看到VHDL在数字电路设计和硬件描述方面的强大应用。

通过学习VHDL并完成课后习题,我们可以提高自己的编程能力,掌握数字电路设计的基本原理和方法。

希望大家在学习VHDL的过程中能够认真完成课后习题,并不断提高自己的编程水平。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• library ieee;

• use ieee.std_logic_1164.all;

• entity jk is

• port( pset,clr,clk,j,k:in std_logic;

•

q,qb:out std_logic);

• end entity;

• architecture behav of jk is

•

elsif(s1='0')and(s0='1')then

•

if(r='1')then qs(3)<='1';

•

qs(2 downto 0)<=qs(3 downto 1);

•

elsif(r='0')then qs(3)<='0';

•

qs(2 downto 0)<=qs(3 downto 1);

•

end if;

• end decode3to8;

• architecture behav of decode3to8 is

• signal sel:std_logic_vector(3 downto 0);

• begin

• sel<=a&en;

• with sel select

• Y<= "00000001" when "0001",

输入值

A

B

0

0

0

1

1

0

1

1

半 加 法 器(A+B)

ห้องสมุดไป่ตู้Sum

Car

0

0

1

0

1

0

0

1

半 减 法 器(A-B)

Difference 0 1 1

Borrow 0 1 0

0

0

提示信息:将加法与减法区分成两个功能模块, 使用BLOCK语句将构造体分为两大部分。

2-1代码

• library ieee;

• use ieee.std_logic_1164.all;

• signal q_s,qb_s:std_logic;

• begin

• process(pset,clr,clk,j,k)

• begin

• if(pset='0')and(clr='1')then

• q_s<='1';qb_s<='0';

• elsif(pset='1')and(clr='0')then

• when"1101"=>dout<="0111101";

• when"1110"=>dout<="1001111";

• when"1111"=>dout<="1000111";

• when others=>dout<="0000000";

• end case;

• end process;

• end behav;

• q_s<='0';qb_s<='1';

• elsif(clk 'event and clk='1')then

• if(j='0')and(k='1')then

• q_s<='0';qb_s<='1';

• elsif(j='1')and(k='0')then

• q_s<='1';qb_s<='0';

• architecture behav of d_chufa is

• begin

• process(clk)is

• begin

• if(clk 'event and clk='1')then

• q<=d;

• end if;

• end process;

• end behav;

• 异步清零、异步置位功能的边沿JK触发器

• begin

• g1:block

• begin

• sum<=a xor b;

• car<=a xor b;

• end block g1;

• g2:block

• begin

• dif<=a xor b;

• bor<=(not a) and b;

• end block g2;

• end behav;

实验2-2

实验内容:设计一个4位加减法器. 要求:a,b:数据输入;

sub: 控制端,高电平实现加法功能, 低电平实现减法功能;

s:和与差的输出; co:进位与借位的输出。

2-2代码

• library ieee;

• use ieee.std_logic_1164.all;

• use ieee.std_logic_unsigned.all;

• elsif(j='1')and(k='1')then

• q_s<=not q_s;

• qb_s<=not qb_s;

• end if;

• end if;

• q<=q_s;

• qb<=qb_s;

• end process;

• end behav;

1-3代码

实验2-1

实验内容:完成下述模块的设计,实现真值表中 的半加与半减的功能。

•

• END ARCHITECTURE ART;

1-2代码

• D触发器的设计

• library ieee;

• use ieee.std_logic_1164.all;

• entity d_chufa is

• port ( clk,d:in std_logic;

•

q:out std_logic);

• end d_chufa;

•

signal qs:std_logic_vector(3 downto 0);

•

begin

•

process(clr,s0,s1,clk,l,r)is

•

begin

•

if(clr='0')then

•

qs<="0000";

•

elsif(clk 'event and clk='1')then

•

if(s1='1')and(s0='1')then qs<=p;

• when"0011"=>dout<="1111001";

• when"0100"=>dout<="0110011";

• when"0101"=>dout<="1011011";

• when"0110"=>dout<="1011111";

• when"0111"=>dout<="1110000";

• entity subadd is

• port(sub:in std_logic;

•

a,b:in std_logic_vector(3 downto 0);

•

s:out std_logic_vector(3 downto 0);

•

co:out std_logic);

• end entity subadd;

•

"XXXXXXXX" when others;

• end behav;

实验4-1

功能要求:4位数据输入,可表示0——F十六个数值。 将其译码为共阴极7段LED的显示码。LED的每段和 dout的连接关系见下图。 模块名:LEDDECODER 输入端口:i——数据输入(4位) 输出端口:dout——译码输出(7位)

•

"00000010" when "0011",

•

"00000100" when "0101",

•

"00001000" when "0111",

•

"00010000" when "1001",

•

"00100000" when "1011",

•

"01000000" when "1101",

•

"10000000" when "1111",

• architecture behav of leddecoder is

• begin

• process(i)

• begin

• case i is

• when "0000"=>dout<="1111110";

• when "0001"=>dout<="0110000";

• when"0010"=>dout<="1101101";