EDA-24进制计数器实验报告

eda实验报告最终版.

实验一实验二1、24进制加法计数器的程序:LIBRARY Ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY count24 ISPORT(en,clk: IN STD_LOGIC;qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);--个位数计数qb: out STD_LOGIC_VECTOR(1 DOWNTO 0));--十位数计数END count24;ARCHITECTURE a1 OF count24 ISBEGINprocess(clk)variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);variable tmb: STD_LOGIC_VECTOR(1 DOWNTO 0);beginif clk'event and clk='1' thenif en='1' thenif tma="1001" then tma:="0000";tmb:=tmb+1;Elsif tmb="10" and tma="0011" then tma:="0000";tmb:="00";else tma:=tma+1;end if;end if;end if;qa<=tma;qb<=tmb;end process;END a1;2,60进制的加法器的实验程序LIBRARY Ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;ENTITY count60 ISPORT(en,clk: IN STD_LOGIC;qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);--个位数计数qb: out STD_LOGIC_VECTOR(2 DOWNTO 0));--十位数计数END count60;ARCHITECTURE a1 OF count60 ISBEGINprocess(clk)variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);variable tmb: STD_LOGIC_VECTOR(2 DOWNTO 0);beginif clk'event and clk='1' thenif en='1' thenif tma="1001" and tmb="101"then tmb:="000";tma:="0000" ;Elsif tma="1001" then tma:="0000";tmb:=tmb+1;else tma:=tma+1;end if;end if;end if;qa<=tma;qb<=tmb;end process;END a1;实验三9、采用VHDL语言描述以上3-8译码器LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY s3_8 ISPORT ( A : IN STD_LOGIC_VECTOR(2 DOWNTO 0);D : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ) ;END ;ARCHITECTURE one OF s3_8 ISBEGINPROCESS( A )BEGINCASE A ISWHEN "000" => D <= "00000001" ;WHEN "001" => D <= "00000010" ;WHEN "010" => D <= "00000100" ;WHEN "011" => D <= "00001000" ;WHEN "100" => D <= "00010000" ;WHEN "101" => D <= "00100000" ;WHEN "110" => D <= "01000000" ;WHEN "111" => D <= "10000000" ;WHEN OTHERS => NULL ;END CASE ;END PROCESS ;END ;实验四1、用VHDL语言设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1,反之为0。

24进制计数器设计报告

..1. 设计任务1.1设计目的1. 了解计数器的组成及工作原理。

2. 进一步掌握计数器的设计方法和计数器相互级联的方法。

3. 进一步掌握各芯片的逻辑功能及使用方法。

4. 进一步掌握数字系统的制作和布线方法。

5. 熟悉集成电路的引脚安排。

1.2 设计指标1. 以24为一个周期,且具有自动清零功能。

2. 能显示当前计数状态。

1.3 设计要求1. 画出总体设计框图,以说明计数器由哪些相对独立的功能模块组成,标出各个模块之间互相联系,时钟信号传输路径、方向。

并以文字对原理作辅助说明。

2. 设计各个功能模块的电路图,加上原理说明。

3. 选择合适的元器件,利用multisim 仿真软件验证、调试各个功能模块的电路,在接线验证时设计、选择合适的输入信号和输出方式,在确定电路充分正确性同时,输入信号和输出方式要便于电路的测试和故障排除。

4. 在验证各个功能模块基础上,对整个电路的元器件和布线进行合理布局。

5.打印PCB 板,腐蚀,钻孔,插元器件,焊接再就对整个计数器电路进行调试。

2.设计思路与总体框图.计数器由计数器、译码器、显示器三部分电路组成,再由555定时器组成的多谐振荡器来产生方波,充当计数脉冲来作为计数器的时钟信号,计数结果通过译码器显示。

图1所示为计数器的一般结构框图。

2CRCR CR▲图 1 计数器结构框图3.系统硬件电路的设计3.1 555多谐荡电路555多谐振荡电路由NE555P 芯片、电阻和电容组成。

由NE555P 的3脚输 出方波。

▲图 2 555电路计数脉冲(由555电路产生)异步清零计数器个位位数码示像译码驱动CP CP强制清零3.2 计数器电路集成计数芯片一般都设置有清零输入端和置数输入端,而且无论是清零还是置数都有同步和异步之分。

有的集成计数器采用同步方式,即当CP触发沿到来时才能完成清零或置数任务;有的集成计数器则采用异步方式,即通过触发器的异步输入端来直接实现清零或置数,与CP信号无关。

EDA 24进制计数器的设计

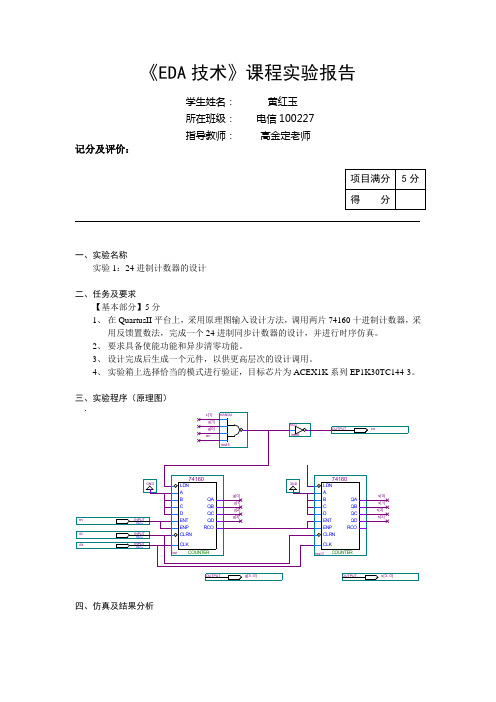

《EDA技术》课程实验报告学生姓名:黄红玉所在班级:电信100227指导教师:高金定老师记分及评价:一、实验名称实验1:24进制计数器的设计二、任务及要求【基本部分】5分1、在QuartusII平台上,采用原理图输入设计方法,调用两片74160十进制计数器,采用反馈置数法,完成一个24进制同步计数器的设计,并进行时序仿真。

2、要求具备使能功能和异步清零功能。

3、设计完成后生成一个元件,以供更高层次的设计调用。

4、实验箱上选择恰当的模式进行验证,目标芯片为ACEX1K系列EP1K30TC144-3。

三、实验程序(原理图)四、仿真及结果分析在QuartusII平台上,采用原理图输入设计方法,调用两片74160十进制计数器,采用反馈置数法,设计一个24进制同步计数器的思路是,一片74160计数器作为个位计数,一片用来十位计数,要实现同步24进制,则个位接成0011,十位接成0010,再用一个四输入(一段接一个使能信号EN)的与非门接到两片74160计数器上的置数端LDN。

把原理图在QuartusII上画成后,进行编译,编译无误后,在新建一个波形文件,添加所有引脚,设置输入引脚的波形,最后在进行波形编译,无误后即可达到想要的24进制。

然后再根据EPF10K30E144芯片引脚对照,输入各个输入输出引脚的引脚号,再链接到试验箱检验,观察数码管的显示结果。

五、硬件验证1、选择模式:模式72、引脚锁定情况表:六、小结经过这次的实验工作,让我知道了许多的东西,也对QuartusII这个软件的一个初步认识及应用,也让我了解了许多在书本上所学不到的知识和技能,这为我们在以后的工作起了非常重要的作用。

计数器eda实验报告

计数器eda实验报告计数器EDA实验报告引言:计数器是数字电路中常见的基本模块之一,用于计算和记录输入脉冲信号的数量。

在本次实验中,我们将使用EDA工具对计数器进行设计和分析。

通过对计数器的EDA实验,我们旨在深入了解计数器的工作原理和性能特点。

一、实验目的本次实验的目的是通过EDA工具对计数器进行设计和分析,具体包括以下几个方面:1. 了解计数器的基本原理和工作方式;2. 学习使用EDA工具进行电路设计和仿真;3. 分析计数器的性能指标,如最大计数值、计数速度等。

二、实验步骤1. 设计计数器的电路原理图;2. 使用EDA工具进行电路仿真;3. 分析仿真结果,包括计数器的计数规律、计数速度等;4. 调整计数器的参数,观察对计数结果的影响;5. 总结实验结果并提出改进意见。

三、计数器的设计原理计数器是由触发器和逻辑门组成的电路,可以实现对输入脉冲信号的计数功能。

常见的计数器包括二进制计数器、十进制计数器等。

在本次实验中,我们将设计一个4位二进制计数器。

四、EDA工具的使用我们选择使用Xilinx ISE Design Suite进行电路设计和仿真。

该工具具有强大的功能和易于使用的界面,方便我们进行计数器的设计和分析。

五、仿真结果分析通过对计数器的仿真结果进行分析,我们可以得到以下结论:1. 计数器的计数规律:根据计数器的设计原理,我们可以观察到计数器的计数规律为二进制递增。

2. 计数器的计数速度:计数器的计数速度取决于输入脉冲信号的频率和计数器的时钟频率。

通过适当调整时钟频率,我们可以实现不同速度的计数。

六、参数调整与性能改进在实验过程中,我们可以通过调整计数器的参数来改进其性能。

例如,我们可以增加计数器的位数,以提高其计数范围;或者调整计数器的时钟频率,以改变其计数速度。

通过不断优化和改进,我们可以得到更加高效和灵活的计数器设计。

七、实验总结通过本次计数器EDA实验,我们深入了解了计数器的工作原理和性能特点,并学会了使用EDA工具进行电路设计和仿真。

EDA实验报告——计数器

EDA实验报告——计数器一、实验目的本实验主要是通过搭建计数器,了解计数器的基本原理和使用方法,掌握数字电路的设计方法及仿真分析方法。

二、实验原理计数器是数字电路的重要组成部分,在数字电路的多个应用中都有着广泛的应用。

计数器可以实现多种数字处理功能,如二进制计数、定量计数、计时、频率分频等。

三、实验材料1. Protues软件2. 74LS90集成电路3. 7段数码管4. 4位拨动开关5. 4个LED灯6. 电路板、杜邦线等。

四、实验内容1. 给定 74LS90 计数器数据手册,分析本实验使用到的 74LS90 芯片的接口及特性。

2. 根据实验需求,用 Protues 软件搭建计数器电路图。

3. 在计数器电路图中连通 74LS90 芯片的译码器输出端口,设置与四个拨动开关相连的输入端口以及 LED 显示器输出端口,实现计数器的计数。

4. 在计数器的输出端口增加 7 段数码管,通过数码管显示计数值。

5. 根据实验需求搭建模电流源电路,对实验电路进行仿真分析,并对仿真结果进行评估。

五、实验步骤2. 从库中拖动 74LS90 芯片、7 段数码管、拨动开关、LED 灯等元件到设计图中。

4. 在 74LS90 芯片工作模式的选择端口接上拨动开关,选择计数器的计数方式。

5. 配置模电流源电路,并设置仿真参数。

6. 进行仿真并记录仿真结果。

七、实验结果本实验搭建的计数器能够正确地进行计数,并且将计数结果通过数码管和 LED 灯显示出来。

在进行仿真分析时,根据仿真数据评估实验电路的合理性。

本实验通过搭建计数器,了解计数器的基本原理和使用方法,掌握数字电路的设计方法及仿真分析方法。

实验中主要学习了数字计数器的结构、性能和工作原理,在搭建计数器电路时主要包括了 74LS90 芯片的接口和设置以及输入输出端口的设置。

通过本实验,我进一步了解了计数器的基本知识和原理,也学习了如何使用 Protues 软件进行电路的搭建和仿真。

eda计数器的实验报告

eda计数器的实验报告EDA计数器的实验报告引言:计数器是数字电路中常用的组合逻辑电路,用于实现对输入信号的计数功能。

EDA计数器是一种基于EDA(Electronic Design Automation,电子设计自动化)技术的计数器,利用EDA工具进行设计和仿真,能够更加高效地完成计数任务。

本实验旨在通过设计和实现EDA计数器,探索其原理和应用。

一、实验目的本实验的目的是通过设计和实现EDA计数器,深入理解计数器的工作原理,并掌握EDA技术在数字电路设计中的应用。

通过实验,我们将学习以下内容:1. 计数器的基本原理和分类;2. EDA工具的使用方法;3. 数字电路的设计与仿真。

二、实验步骤1. 确定计数器的功能要求:根据实验要求,我们需要设计一个4位二进制计数器,能够实现从0000到1111的计数功能。

2. 使用EDA工具进行设计:选择合适的EDA工具(如Verilog、VHDL等),根据计数器的功能要求,编写相应的代码。

3. 进行仿真:利用EDA工具提供的仿真功能,对设计的计数器进行仿真,验证其正确性和稳定性。

4. 进行综合和布局布线:将设计的计数器进行综合和布局布线,生成对应的逻辑网表和物理布局。

5. 进行时序分析和时序优化:对设计的计数器进行时序分析,优化其时序性能,确保其能够满足实际应用需求。

6. 进行静态和动态功耗分析:对设计的计数器进行静态和动态功耗分析,评估其功耗性能,并进行相应的优化。

三、实验结果与分析经过以上步骤的设计和优化,我们成功实现了一个4位二进制计数器。

通过EDA工具的仿真功能,我们验证了计数器的正确性和稳定性。

在时序分析和时序优化过程中,我们发现了一些潜在的时序问题,并进行了相应的优化,确保了计数器的正常工作。

在静态和动态功耗分析中,我们评估了计数器的功耗性能,并进行了一些优化措施,减少了功耗。

四、实验总结通过本次实验,我们深入学习了计数器的原理和分类,并掌握了EDA技术在数字电路设计中的应用。

24进制计数器proteus实验报告

24进制计数器proteus实验报告24进制计数器是在电子系统的设计中经常使用的计数器,具有高速、稳定、精度高等特点,因此在各种计数相关的操作和应用中被广泛使用。

本次实验的目的是在Proteus软件中实现24进制计数器,并验证其计数功能和参数的准确性。

实验器材:- Proteus软件-一块PIC16F877A单片机-一个24进制数码管实验原理:24进制计数器是指计数器的基数为24,即每一次计数器加1所表示的是24进制数中的1。

在本次实验中,我们将采用PIC16F877A单片机来实现24进制计数器,通过单片机来对计数器的计数值进行控制和显示。

具体实现需要根据PIC16F877A的编程和控制的特点,针对24进制计数器设计适当的算法与操作。

实验过程:1.根据24进制计数器的原理,确定计数器所采用的基数为24,编写程序,对PIC16F877A进行初始化和IO口配置。

2.在Proteus软件中,添加PIC16F877A单片机和24进制数码管,并连接需要的电路。

3.编写程序,设置计数范围,并实现对计数值的加1和显示。

4.进行仿真测试,查看计数器的正确性和稳定性。

5.通过调整程序和电路参数,优化计数器的性能和准确性。

实验结果:经过一系列的设计和测试,实验结果表明,本次24进制计数器的实验操作成功,可以实现稳定的计数功能。

在计数器运行的过程中,可以正确显示当前的计数值,并能够正常进行加1操作。

同时,在根据实际需要调整计数范围和显示参数的过程中,可以使用该计数器进行更加精确和高效率的计数操作。

实验结论:通过本次实验的操作和测试,可以有效地理解和应用24进制计数器的原理和实现方法,掌握PIC16F877A单片机作为控制器的实现技术。

该计数器具有高速、稳定和精度高等特点,在各种计数相关的操作和应用中具有广泛的实用价值。

eda24进制计数器设计

EDA24进制计数器设计1. 任务背景计数器是计算机系统中常见的一种电路,用来实现对数字进行计数的功能。

传统的计数器一般是采用二进制表示数字,然而在某些特定的应用场景中,使用其他进制的计数器能够更方便和高效。

EDA24进制计数器是指使用24进制来表示数字的计数器。

24进制是一种特殊的进制,它由24个数字符号(0-23)组成,分别对应于十进制的0-9、字母A-J、字母K-T和字母U-Y。

使用24进制计数器可以更精确地表示某些特定范围内的数字,而且减少了数字的位数和转换过程中的计算复杂度。

本文将介绍如何设计一个EDA24进制计数器,包括计数器的原理、硬件设计和功能实现等方面的内容。

2. 原理介绍EDA24进制计数器的工作原理与传统的计数器类似,主要分为三个部分:计数器状态存储、计数器状态更新和计数器输出。

2.1 计数器状态存储EDA24进制计数器需要使用存储器来保存当前的计数器状态。

由于EDA24进制有24个数字符号,每个符号对应一个存储单元,因此需要一个24位的存储器来存储计数器的状态。

存储器的结构可以采用RAM或者寄存器等形式。

当计数器进行更新时,计数器状态存储器会读取新的计数器状态。

2.2 计数器状态更新EDA24进制计数器的计数逻辑与二进制计数器类似,但需要对进位的处理进行特殊处理。

在24进制下,当某一位达到23时,需要进行进位操作,并将低位的符号进行进位。

例如,当计数器达到23时,进位得到的数字为10(对应K),并将低位的数字进行滚动。

以一个4位的EDA24进制计数器为例,计数范围为0000~2323。

初始状态为0000,当计数值增加时,每一位的变化规律如下:•当个位(最低位)从0~2变化时,直接递增;•当个位达到3时,个位变为0,十位(倒数第二位)递增;•当十位从0~2变化时,直接递增;•当十位达到3时,十位变为0,百位(倒数第三位)递增;•当百位从0~2变化时,直接递增;•当百位达到3时,百位变为0,千位(最高位)递增;•当千位从0~2变化时,直接递增;•当千位达到3时,计数器归零。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《EDA技术》课程实验报告

学生姓名:

所在班级:电信1001班

指导教师:

记分及评价:

一、实验名称

实验1:24进制计数器的设计

二、任务及要求

【基本部分】5分

1、在QuartusII平台上,采用原理图输入设计方法,调用两片74160十进制计数器,采

用反馈置数法,完成一个24进制同步计数器的设计,并进行时序仿真。

2、要求具备使能功能和异步清零功能。

3、设计完成后生成一个元件,以供更高层次的设计调用。

4、实验箱上选择恰当的模式进行验证,目标芯片为ACEX1K系列EP1K30TC144-3。

三、实验程序(原理图)

四、仿真及结果分析

五、硬件验证

1、选择模式:

模式7

2、引脚锁定情况表:

六、小结

初次接触EDA让自己学到了很多的知识,实验中让自己的思维更加的开阔,对这门课程有了一定的了解,也很感兴趣。

总之的收获了不少的知识。