The gem5 simulator

MSI Trident S 5M 游戏桌面说明书

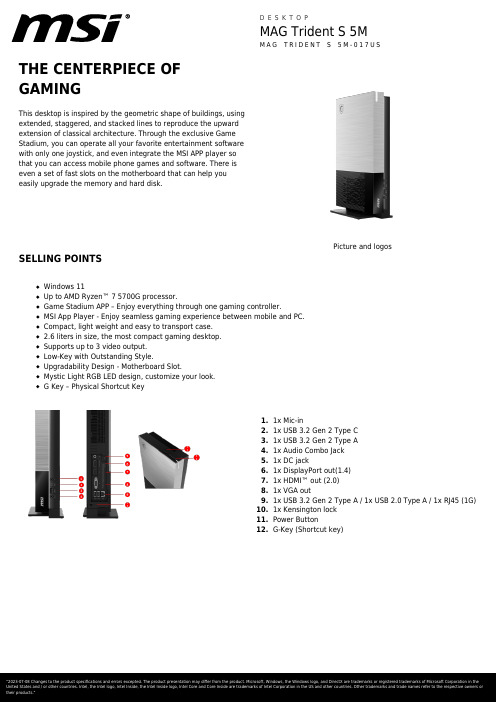

THE CENTERPIECE OFGAMINGThis desktop is inspired by the geometric shape of buildings, usingextended, staggered, and stacked lines to reproduce the upwardextension of classical architecture. Through the exclusive GameStadium, you can operate all your favorite entertainment softwarewith only one joystick, and even integrate the MSI APP player sothat you can access mobile phone games and software. There iseven a set of fast slots on the motherboard that can help youeasily upgrade the memory and hard disk.Picture and logosSELLING POINTSWindows 11Up to AMD Ryzen™ 7 5700G processor.Game Stadium APP – Enjoy everything through one gaming controller.MSI App Player - Enjoy seamless gaming experience between mobile and PC.Compact, light weight and easy to transport case.2.6 liters in size, the most compact gaming desktop.Supports up to 3 video output.Low-Key with Outstanding Style.Upgradability Design - Motherboard Slot.Mystic Light RGB LED design, customize your look.G Key – Physical Shortcut Key1.1x Mic-in2.1x USB 3.2 Gen 2 Type C3.1x USB 3.2 Gen 2 Type A4.1x Audio Combo Jack1x DC jack5.6.1x DisplayPort out(1.4)7.1x HDMI™ out (2.0)1x VGA out8.9.1x USB 3.2 Gen 2 Type A / 1x USB 2.0 Type A / 1x RJ45 (1G)10.1x Kensington lockPower Button11.12.G-Key (Shortcut key)SPECIFICATIONOperating Systems Operating Systems Windows 11 HomeBarcode Info UPC824142286050 UCC1410824142286057Model Part No9S6-B93611-017MKT Name MAG Trident S 5MMKT Spec MAG Trident S 5M-017US Color ID1/Black-Black-BlackProcessor CPU Number AMD Ryzen 5 5600G CPU Clock 3.9GHzCPU Cores6TDP65WCache3MBThreads12CPU Cooler Air cooling 3HPChipset Chipsets N/AGraphics VGA I/O Port N/A VGA MKT Name N/AMemory Memory Size16GB(8GB*2) Memory Type DDR4 SDRAM Memory Speed1600(3200)MHz Module Type SO-DIMM Memory Slot (Total/Free)2/0Max Capacity Max 64GBStorage SSD Size512GBHDD1 Size N/ASSD Config512GB*1SSD Interface PCIe GEN3x4 w/o DRAM NVMe SSD Form Factor M.2-2280 M-KEYM.2 slots (Total/Free)2/1HDD1 RPM N/AHDD1 Form Factor N/AHDD1 Interface N/A3.5" Drive Bays (Total/Free)0/2.5" Drive Bays (Total/Free)1/1ODD(Type)N/AODD Height N/AODD Type N/ACommunications LAN Realtek RTL8111HWLAN INTEL/AX210.NGWG.NV WLAN Version802.11a/b/g/n/ac/ax 2x2+BT BT Version 5.2Audio Audio Chipset Realtek ALC233 Audio Type 2.1 Channel HD AudioI/O Ports (Front)USB 3.2 Gen 1 Type A1 USB 3.2 Gen 2 Type A1 USB 3.2 Gen 2 Type C1 Audio Mic-in1 Mic-in/Headphone-out combo1I/O Ports (Rear)USB 3.2 Gen 2 Type A (R)1USB 2.0 Type A (R)1RJ451WiFi Antenna1VGA out1HDMI™1x (v2.0) DP out1x (v1.4)Power Power120W Power Certification N/A Formfactor N/A Type ADAPTORAccessories Keyboard Interface USBMouse Interface USBPower Cord1AC Adaptor1Warranty Card N/AQuick Guide3User Manual N/AVESA Mount kit N/A Keyboard Vigor GK30 US Mouse CLUTCH GM11Mechanical and Environmental Operating, Storage Temperature0° C ~ 35° C ; -20° C ~ 60° C Operating, Storage Humidity N/ARegulatory ComplianceFCC(Class B)CB/CEUL(CUL)BSMIVCCIRCM(C-Tick)Dimension&Weight Product Dimension (WxDxH) (mm)185.4 x 93 x 334.7 Product Dimension (WxDxH) (inch)7.3 x 3.66 x 13.18 Inside Carton Dimension (WxDxH) (mm)N/AInside Carton Dimension (WxDxH) (inch)N/AOuter Carton Dimension Standard (WxDxH) (mm)482 x 144 x 325 Outer Carton Dimension Standard (WxDxH) (inch)18.98 x 5.67 x 12.8 Weight (Net kg)N/AWeight (Gross kg)N/ALiter2LWarranty Warranty12months。

基于Gem5模拟器的缓存存储体系实验方法

实 验 技 术 与 管 理 第37卷 第1期 2020年1月Experimental Technology and Management Vol.37 No.1 Jan. 2020ISSN 1002-4956 CN11-2034/TDOI: 10.16791/ki.sjg.2020.01.020基于Gem5模拟器的缓存存储体系实验方法沈凡凡1,徐 超1,张 军2,何炎祥3(1. 南京审计大学 信息工程学院,江苏 南京 211815;2. 东华理工大学 软件学院,江西 南昌 330013;3. 武汉大学 计算机学院,湖北 武汉 430072)摘 要:设计了一种简单、高效的基于Gem5模拟器的缓存存储体系实验方法。

分析了Gem5模拟器的源代码结构、函数调用序列以及缓存存储体系源码;设计了4种Gem5模拟器使用和缓存体系结构修改的实验方法,并对这些方法进行了分析;在此基础上,设计了基于Gem5的性能评价实验。

该实验能加深学生对缓存存储体系的理解,为计算机存储体系结构的理论和实验教学提供了新途径。

关键词:模拟器;高速缓冲存储器;存储体系;实验方法;Gem5中图分类号:TP303;TP333 文献标识码:A 文章编号:1002-4956(2020)01-0075-03Experimental method of cache memory architecturebased on Gem5 simulatorSHEN Fanfan 1, XU Chao 1, ZHANG Jun 2, HE Yanxiang 3(1. School of Information Engineering, Nanjing Audit University, Nanjing 211815, China; 2. School of Software, East China University of Technology, Nanchang 330013, China;3. Computer School, Wuhan University, Wuhan 430072, China)Abstract: A simple and efficient experiment method of cache memory system based on the Gem5 simulator is designed. The source code structure, function call sequence and cache memory system source code of the Gem5 simulator are analyzed. Four experimental methods of using the Gem5 simulator and modifying the cache architecture are designed and these methods are analyzed. On this basis, a performance evaluation experiment based on Gem5 is designed. This experiment can deepen students’ understanding of cache memory system and provide a new way for the theory and experiment teaching of computer storage system structure. Key words: simulator; cache memory; memory architecture; experimental method; Gem5在计算机体系结构课程实验教学中,缓存体系结构设计采用计算机硬件实验平台、实验箱、开发板,通过简单的模拟实验完成。

艾默生空调CM+ 用户手册

4.3.2 状态指示灯.................................................................................................................41 4.3.3 告警指示灯.................................................................................................................41 4.3.4 控制按键.....................................................................................................................41 4.4 控制板....................................................................................................................................41 4.5 设定值....................................................................................................................................41 4.5.1 温度设定值.................................................................................................................41 4.5.2 温度偏差.....................................................................................................................42 4.5.3 湿度设定值.................................................................................................................42 4.5.4 湿度偏差.....................................................................................................................42 4.6 运行........................................................................................................................................42 4.6.1 制冷.............................................................................................................................42 4.6.2 加湿.............................................................................................................................43 4.7 告警系统................................................................................................................................45 4.7.1 告警指示.....................................................................................................................45 4.7.2 压缩机低压告警.........................................................................................................46 4.8 主/备机切换...........................................................................................................................47 4.9 控制计时器............................................................................................................................47

啤酒馆MOD1.5光荣与梦想-beta版说明

啤酒馆MOD1.5-光荣与梦想beta版游戏说明啤酒馆MOD小组荣誉出品主创:天问/lialia地图制作:凯文AI调试:qiner事件、科技制作:天问\lialia\镜子叔叔兵模包制作:linsteven兵牌包制作:foolleon技术顾问:hhyy 美工支持: /kiupc8前言 (4)第一章模块科技系统 (5)一、“模块化”概述 (5)二、科技前提介绍 (5)三、特殊科技说明 (6)第二章复合兵种系统 (8)一、常备步兵师(原摩步师模板) (8)二、标准步兵师(原步兵师模板) (9)三、动员步兵师(原民兵师模板) (9)四、机动师(原骑兵模板) (10)五、装甲师 (11)六、山地师 (11)七、空降师 (11)八、陆战师 (12)第三章动员系统 (13)一、人力征召动员系统 (13)二、动员部队快速组建系统 (13)第四章国家工业系统 (14)一、工业体系作用 (14)二、工业体系升级条件 (14)三、选择合适的时机-工业体系升级代价 (15)四、军火交易 (15)第五章常见问题Q&A (16)前言本MOD适用相关软、硬件配置:最低配置:内存1G以上,CPU 2G以上推荐配置:内存2G以上,CPU 2.4G以上推荐操作系统: Windows 7(XP下可能出现无故跳出的bug)从一个事件包的小修小补,到今天基本形成了一个完整的MOD,啤酒馆已经走过了近三年的历程。

这三年,对于庞大的MOD制作,有过有心无力,有过彷徨放弃,但支持我们走到今天的是大家不变的热情,希望这个测试版能够回馈大家对啤酒馆的厚爱,希望大家能够给我们提出更多宝贵的建议,希望每一个HOI 的战友能够从游戏中得到快乐,从现实中收获成功!HOI2随着AOD的完善也步入了一个新的阶段,我们希望让新的啤酒馆带给大家更多的快乐、挑战、历史的激情,因此1.5版的啤酒馆基于全新的地图、科技、兵种设计,希望能通过更复杂和更细腻的设计能够让大家更深的体会那个血与火的年代,体会一寸河山一寸血的壮烈。

【亲测成功杂牌手柄模拟合金装备5】x360ce-[64位]【已修改好ini文件】

![【亲测成功杂牌手柄模拟合金装备5】x360ce-[64位]【已修改好ini文件】](https://img.taocdn.com/s3/m/35bc28a5d1f34693daef3e64.png)

【亲测成功杂牌手柄模拟合金装备5】x360ce-[64位]【已修改好ini文件】这游戏如果想用杂牌手柄玩的话,一定要用64位的x360ce,操作方法见图如下重点是最后要手动修改一下x360ce.ini文件。

以下是我修改好的ini配置文件,亲测成功[Options]UseInitBeep=1Log=0Console=0DebugMode=0InternetDatabaseUrl=/webservices/x360ce.asmxInternetFeatures=1InternetAutoload=1AllowOnlyOneCopy=1Version=1[InputHook]HookMode=1HookLL=0HookCOM=1HookSA=0HookWT=0HookDI=1HookPIDVID=1HookName=0[Mappings]PAD1=IG_c659efa02a9611e28001444553540000PAD2=PAD3=PAD4=[PAD1][PAD2][PAD3][PAD4][IG_3c2f6880b59511e18002444553540000] ProductName=Twin USB JoystickInstanceGuid=3c2f6880-b595-11e1-8002-444553540000 AxisToDPadDeadZone=256AxisToDPadOffset=0A=3B=2Back=9Start=10X=4Y=1D-pad POV=1D-pad Down=DOWND-pad Left=LEFTD-pad Right=RIGHTD-pad Up=UPUseForceFeedback=1ForcePercent=100SwapMotor=0FFBType=0ControllerType=1LeftMotorPeriod=60Left Shoulder=7Left Analog X AntiDeadZone=0Left Analog Y AntiDeadZone=0Left Analog X=1Left Analog Y=-2Left Thumb=11Left Analog X DeadZone=0Left Analog Y DeadZone=0Left Analog Y- Button=0Left Analog X+ Button=0Left Analog Y+ Button=0Left Trigger=5TriggerDeadzone=0PassThrough=0RightMotorPeriod=120Right Shoulder=8Right Analog X AntiDeadZone=0Right Analog Y AntiDeadZone=0Right Analog X=6Right Analog Y=-3Right Thumb=12Right Analog X DeadZone=0Right Analog Y DeadZone=0Right Analog Y- Button=0Right Analog X- Button=0Right Analog X+ Button=0Right Analog Y+ Button=0Right Trigger=6RightTriggerDeadZone=0ProductGuid=00010810-0000-0000-0000-504944564944 AxisToDPad=0[IG_3c32eaf0b59511e18003444553540000] ProductName=Twin USB JoystickProductGuid=00010810-0000-0000-0000-504944564944 InstanceGuid=3c32eaf0-b595-11e1-8003-444553540000 ControllerType=0PassThrough=0RightTriggerDeadZone=0TriggerDeadzone=0D-pad Up=UPD-pad Down=DOWND-pad Left=LEFTD-pad Right=RIGHTAxisToDPad=0AxisToDPadDeadZone=256AxisToDPadOffset=0Left Analog X+ Button=0Left Analog X- Button=0Left Analog Y+ Button=0Left Analog Y- Button=0Left Thumb=0Left Analog X DeadZone=0Left Analog X AntiDeadZone=0Left Analog Y AntiDeadZone=0Right Analog X+ Button=0Right Analog X- Button=0Right Analog Y+ Button=0Right Analog Y- Button=0Right Thumb=0Right Analog X DeadZone=0Right Analog Y DeadZone=0Right Analog X AntiDeadZone=0Right Analog Y AntiDeadZone=0 UseForceFeedback=0FFBType=0SwapMotor=0ForcePercent=0LeftMotorPeriod=0RightMotorPeriod=0Left Analog X=-1[IG_01d51120cbb711e18001444553540000] ProductName=Generic USB Joystick InstanceGuid=01d51120-cbb7-11e1-8001-444553540000 AxisToDPadDeadZone=256AxisToDPadOffset=0A=3B=2Back=9Start=10X=4Y=1D-pad POV=1D-pad Down=DOWND-pad Left=LEFTD-pad Right=RIGHTD-pad Up=UPUseForceFeedback=1ForcePercent=0SwapMotor=0FFBType=0ControllerType=0LeftMotorPeriod=0Left Shoulder=5Left Analog X AntiDeadZone=0Left Analog Y AntiDeadZone=0Left Analog X=1Left Analog Y=-2Left Thumb=11Left Analog X DeadZone=0Left Analog Y DeadZone=0Left Analog Y- Button=0Left Analog X- Button=0Left Analog X+ Button=0Left Analog Y+ Button=0Left Trigger=7TriggerDeadzone=0PassThrough=0RightMotorPeriod=0Right Shoulder=6Right Analog X AntiDeadZone=0Right Analog Y AntiDeadZone=0Right Analog X=3Right Analog Y=-6Right Thumb=12Right Analog X DeadZone=0Right Analog Y DeadZone=0Right Analog Y- Button=0Right Analog X- Button=0Right Analog X+ Button=0Right Analog Y+ Button=0Right Trigger=8RightTriggerDeadZone=0ProductGuid=00060079-0000-0000-0000-504944564944 AxisToDPad=0[IG_a5190fe0b21411e38001444553540000] ProductName=Twin USB Vibration Gamepad ProductGuid=00010810-0000-0000-0000-504944564944 InstanceGuid=a5190fe0-b214-11e3-8001-444553540000 AxisToDPadDeadZone=256AxisToDPad=0AxisToDPadOffset=0A=3B=2GuideButton=Back=9Start=10X=4Y=1D-pad POV=1D-pad Down=DOWND-pad Left=LEFTD-pad Right=RIGHTD-pad Up=UPUseForceFeedback=1ForcePercent=100SwapMotor=0FFBType=0ControllerType=1LeftMotorPeriod=500Left Shoulder=7Left Analog X AntiDeadZone=0Left Analog Y AntiDeadZone=0Left Analog X=1Left Analog Y=-2Left Thumb=11Left Analog X DeadZone=0Left Analog Y DeadZone=0Left Analog Y- Button=0Left Analog X- Button=0Left Analog X+ Button=0Left Analog Y+ Button=0Left Trigger=5TriggerDeadzone=0PassThrough=0RightMotorPeriod=500Right Shoulder=8Right Analog X AntiDeadZone=0Right Analog Y AntiDeadZone=0Right Analog X=6Right Analog Y=-3Right Thumb=12Right Analog X DeadZone=0Right Analog Y DeadZone=0Right Analog Y- Button=0Right Analog X- Button=0Right Analog X+ Button=0Right Analog Y+ Button=0Right Trigger=6RightTriggerDeadZone=0[IG_a51936f0b21411e38002444553540000] ProductName=Twin USB Vibration Gamepad ProductGuid=00010810-0000-0000-0000-504944564944 InstanceGuid=a51936f0-b214-11e3-8002-444553540000AxisToDPadDeadZone=256 AxisToDPad=0 AxisToDPadOffset=0A=3B=2GuideButton=Back=9Start=10X=4Y=1D-pad POV=1D-pad Down=DOWND-pad Left=LEFTD-pad Right=RIGHTD-pad Up=UP UseForceFeedback=1 ForcePercent=100SwapMotor=0FFBType=0ControllerType=1 LeftMotorPeriod=60Left Shoulder=7Left Analog X AntiDeadZone=0 Left Analog Y AntiDeadZone=0 Left Analog X=1Left Analog Y=-2Left Thumb=11Left Analog X DeadZone=0Left Analog Y DeadZone=0Left Analog Y- Button=0Left Analog X- Button=0Left Analog X+ Button=0Left Analog Y+ Button=0Left Trigger=5 TriggerDeadzone=0 PassThrough=0 RightMotorPeriod=120Right Shoulder=8Right Analog X AntiDeadZone=0 Right Analog Y AntiDeadZone=0 Right Analog X=6Right Analog Y=-3Right Thumb=12Right Analog X DeadZone=0Right Analog Y DeadZone=0Right Analog Y- Button=0Right Analog X- Button=0Right Analog X+ Button=0Right Analog Y+ Button=0Right Trigger=6RightTriggerDeadZone=0[IG_c659efa02a9611e28001444553540000] ProductName=吉星游戏手柄ProductGuid=00060079-0000-0000-0000-504944564944 InstanceGuid=c659efa0-2a96-11e2-8001-444553540000 ControllerType=1PassThrough=0Right Trigger=8RightTriggerDeadZone=0Left Trigger=7TriggerDeadzone=5D-pad POV=1D-pad Up=UPD-pad Down=DOWND-pad Left=LEFTD-pad Right=RIGHTAxisToDPad=0AxisToDPadDeadZone=256AxisToDPadOffset=0Back=9Start=10A=3B=2X=4Y=1Left Shoulder=5Right Shoulder=6Left Analog X=1Left Analog Y=-2Left Analog X+ Button=0Left Analog X- Button=0Left Analog Y+ Button=0Left Analog Y- Button=0Left Thumb=11Left Analog X DeadZone=0Left Analog Y DeadZone=0Left Analog X AntiDeadZone=0Left Analog Y AntiDeadZone=0Right Analog X=3Right Analog Y=-6Right Analog X+ Button=0 Right Analog X- Button=0 Right Analog Y+ Button=0 Right Analog Y- Button=0Right Thumb=12Right Analog X DeadZone=0 Right Analog Y DeadZone=0 Right Analog X AntiDeadZone=0 Right Analog Y AntiDeadZone=0 UseForceFeedback=1 FFBType=0SwapMotor=1ForcePercent=100 LeftMotorPeriod=60 RightMotorPeriod=120。

AMD OpteronTM 6300系列处理器快速参考指南说明书

ReferencesAMD(2012)AMD Opteron TM6300series processor quick reference guide.Tech.Rep.,August Aochi H,Ulrich T,Ducellier A,Dupros F,Michea D(2013)Finite difference simulations of seismic wave propagation for understanding earthquake physics and predicting ground motions:advances and challenges.J Phys Conf Ser454(1):012010.https:///10.1088/ 1742-6596/454/1/012010Awasthi M,Nellans DW,Sudan K,Balasubramonian R,Davis A(2010)Handling the problems and opportunities posed by multiple on-chip memory controllers.In:Parallel architectures and compilation techniques(PACT),pp319–330Azimi R,Tam DK,Soares L,Stumm M(2009)Enhancing Operating system support for multicore processors by using hardware performance monitoring.ACM SIGOPS Oper Syst Rev43(2):56–65.https:///10.1145/1531793.1531803Bach M,Charney M,Cohn R,Demikhovsky E,Devor T,Hazelwood K,Jaleel A,Luk CK,Lyons G,Patil H,Tal A(2010)Analyzing parallel programs with pin.IEEE Comput43(3):34–41 Barrow-Williams N,Fensch C,Moore S(2009)A communication characterisation of splash-2and parsec.In:IEEE international symposium on workload characterization(IISWC),pp86–97.https:///10.1109/IISWC.2009.5306792Bellard F(2005)Qemu,a fast and portable dynamic translator.In:USENIX annual technical conference(ATEC).USENIX Association,Berkeley,pp41–41Bienia C,Kumar S,Li K(2008a)PARSEC vs.SPLASH-2:a quantitative comparison of two mul-tithreaded benchmark suites on Chip-Multiprocessors.In:IEEE international symposium on workload characterization(IISWC),pp47–56.https:///10.1109/IISWC.2008.4636090 Bienia C,Kumar S,Singh JP,Li K(2008b)The PARSEC benchmark suite:characterization and architectural implications.In:International conference on parallel architectures and compilation techniques(PACT),pp72–81Binkert N,Beckmann B,Black G,Reinhardt SK,Saidi A,Basu A,Hestness J,Hower DR,Krishna T,Sardashti S,Sen R,Sewell K,Shoaib M,Vaish N,Hill MD,Wood DA(2011)The gem5 simulator.ACM SIGARCH Comput Archit News39(2):1–7Borkar S,Chien AA(2011)The future of mun ACM54(5):67–77 Broquedis F,Aumage O,Goglin B,Thibault S,Wacrenier PA,Namyst R(2010)Structuring the execution of OpenMP applications for multicore architectures.In:IEEE international parallel &distributed processing symposium(IPDPS),pp1–10Caparros Cabezas V,Stanley-Marbell P(2011)Parallelism and data movement characterization of contemporary application classes.In:ACM symposium on parallelism in algorithms and architectures(SPAA)51©The Author(s),under exclusive licence to Springer International Publishing AG,part of Springer Nature2018E.H.M.Cruz et al.,Thread and Data Mapping for Multicore Systems,SpringerBriefs in Computer Science,https:///10.1007/978-3-319-91074-1Casavant TL,Kuhl JG(1988)A taxonomy of scheduling in general-purpose distributed computing systems.IEEE Trans Softw Eng14(2):141–154Chishti Z,Powell MD,Vijaykumar TN(2005)Optimizing replication,communication,and capacity allocation in CMPs.ACM SIGARCH Comput Archit News33(2):357–368.https:// /10.1145/1080695.1070001Conway P(2007)The AMD opteron northbridge architecture.IEEE Micro27(2):10–21Corbet J(2012a)AutoNUMA:the other approach to NUMA scheduling./Articles/ 488709/Corbet J(2012b)Toward better NUMA scheduling./Articles/486858/Coteus PW,Knickerbocker JU,Lam CH,Vlasov Y A(2011)Technologies for exascale systems.IBM J Res Develop55(5):14:1–14:12.https:///10.1147/JRD.2011.2163967Cruz EHM,Alves MAZ,Navaux POA(2010)Process mapping based on memory access traces.In:Symposium on computing systems(WSCAD-SCC),pp72–79Cruz E,Alves M,Carissimi A,Navaux P,Ribeiro C,Mehaut J(2011)Using memory access traces to map threads and data on hierarchical multi-core platforms.In:IEEE international symposium on parallel and distributed processing workshops and Phd forum(IPDPSW)Cruz EHM,Diener M,Navaux POA(2012)Using the translation lookaside buffer to map threads in parallel applications based on shared memory.In:IEEE international parallel&distributed processing symposium(IPDPS),pp532–543.https:///10.1109/IPDPS.2012.56Cruz EHM,Diener M,Alves MAZ,Navaux POA(2014)Dynamic thread mapping of shared memory applications by exploiting cache coherence protocols.J Parallel Distrib Comput 74(3):2215–2228.https:///10.1016/j.jpdc.2013.11.006Cruz EHM,Diener M,Navaux POA(2015a)Communication-aware thread mapping using the translation lookaside buffer.Concurr Comput Pract Exp22(6):685–701Cruz EHM,Diener M,Pilla LL,Navaux POA(2015b)An efficient algorithm for communication-based task mapping.In:International conference on parallel,distributed,and network-based processing(PDP),pp207–214Cruz EH,Diener M,Alves MA,Pilla LL,Navaux PO(2016a)Lapt:a locality-aware page table for thread and data mapping.Parallel Comput54(C):59–71./10.1016/j.parco.2015.12.001Cruz EHM,Diener M,Pilla LL,Navaux POA(2016b)A sharing-aware memory management unit for online mapping in multi-core architectures.In:Euro-par parallel processing,pp659–671.https:///10.1007/978-3-319-43659-3Cruz EHM,Diener M,Pilla LL,Navaux POA(2016c)Hardware-assisted thread and data mapping in hierarchical multicore architectures.ACM Trans Archit Code Optim13(3):1–25.https://doi.org/10.1145/2975587Dashti M,Fedorova A,Funston J,Gaud F,Lachaize R,Lepers B,Quéma V,Roth M(2013)Traffic management:a holistic approach to memory placement on NUMA systems.In:Architectural support for programming languages and operating systems(ASPLOS),pp381–393Diener M,Madruga FL,Rodrigues ER,Alves MAZ,Navaux POA(2010)Evaluating thread placement based on memory access patterns for multi-core processors.In:IEEE international conference on high performance computing and communications(HPCC),pp491–496.http:// /10.1109/HPCC.2010.114Diener M,Cruz EHM,Navaux POA(2013)Communication-based mapping using shared pages.In:IEEE international parallel&distributed processing symposium(IPDPS),pp700–711.https:///10.1109/IPDPS.2013.57Diener M,Cruz EHM,Navaux POA,Busse A,HeißHU(2014)kMAF:automatic kernel-level management of thread and data affinity.In:International conference on parallel architectures and compilation techniques(PACT),pp277–288Diener M,Cruz EHM,Navaux POA,Busse A,HeißHU(2015a)Communication-aware process and thread mapping using online communication detection.Parallel Comput43(March):43–63 Diener M,Cruz EHM,Pilla LL,Dupros F,Navaux POA(2015b)Characterizing communi-cation and page usage of parallel applications for thread and data mapping.Perform Eval 88–89(June):18–36Diener M,Cruz EHM,Alves MAZ,Navaux POA,Koren I(2016)Affinity-based thread and data mapping in shared memory systems.ACM Comput Surv49(4):64:1–64:38./10.1145/3006385Dupros F,Aochi H,Ducellier A,Komatitsch D,Roman J(2008)Exploiting intensive multi-threading for the efficient simulation of3d seismic wave propagation.In:IEEE international conference on computational science and engineering(CSE),pp253–260.https:///10.1109/CSE.2008.51Feliu J,Sahuquillo J,Petit S,Duato J(2012)Understanding cache hierarchy contention in CMPs to improve job scheduling.In:International parallel and distributed processing symposium (IPDPS).https:///10.1109/IPDPS.2012.54Gabriel E,Fagg GE,Bosilca G,Angskun T,Dongarra JJ,Squyres JM,Sahay V,Kambadur P, Barrett B,Lumsdaine A(2004)Open MPI:goals,concept,and design of a next generation MPI implementation.In:Recent advances in parallel virtual machine and message passing interface Gennaro ID,Pellegrini A,Quaglia F(2016)OS-based NUMA optimization:tackling the case of truly multi-thread applications with non-partitioned virtual page accesses.In:IEEE/ACM international symposium on cluster,cloud,and grid computing(CCGRID),pp291–300.https:// /10.1109/CCGrid.2016.91Intel(2008)Quad-core Intel R Xeon R processor5400series datasheet.Tech.Rep.,March.http:// /assets/PDF/datasheet/318589.pdfIntel(2010a)Intel R Itanium R architecture software developer’s manual.Tech.Rep.Intel(2010b)Intel R Xeon R processor7500series.Tech.Rep.,MarchIntel(2012)2nd generation Intel core processor family.Tech.Rep.,SeptemberJin H,Frumkin M,Yan J(1999)The OpenMP implementation of NAS parallel benchmarks and its performance.Tech.Rep.,October,NASAJohnson M,McCraw H,Moore S,Mucci P,Nelson J,Terpstra D,Weaver V,Mohan T(2012) PAPI-V:performance monitoring for virtual machines.In:International conference on parallel processing workshops(ICPPW),pp194–199.https:///10.1109/ICPPW.2012.29Klug T,Ott M,Weidendorfer J,Trinitis C(2008)Autopin—automated optimization of thread-to-core pinning on multicore systems.High Perform Embed Archit Compilers3(4):219–235 LaRowe RP,Holliday MA,Ellis CS(1992)An analysis of dynamic page placement on a NUMA multiprocessor.ACM SIGMETRICS Perform Eval Rev20(1):23–34Löf H,Holmgren S(2005)Affinity-on-next-touch:increasing the performance of an industrial PDE solver on a cc-NUMA system.In:International conference on supercomputing(SC), pp387–392Magnusson P,Christensson M,Eskilson J,Forsgren D,Hallberg G,Hogberg J,Larsson F,Moestedt A,Werner B(2002)Simics:a full system simulation platform.IEEE Comput35(2):50–58.https:///10.1109/2.982916Marathe J,Mueller F(2006)Hardware profile-guided automatic page placement for ccNUMA systems.In:ACM SIGPLAN symposium on principles and practice of parallel programming (PPoPP),pp90–99Marathe J,Thakkar V,Mueller F(2010)Feedback-directed page placement for ccNUMA via hardware-generated memory traces.J Parallel Distrib Comput70(12):1204–1219Martin MMK,Hill MD,Sorin DJ(2012)Why on-chip cache coherence is here to mun ACM55(7):78.https:///10.1145/2209249.2209269Nethercote N,Seward J(2007)Valgrind:a framework for heavyweight dynamic binary instrumen-tation.In:ACM SIGPLAN conference on programming language design and implementation (PLDI)OpenMP(2013)OpenMP application program interface.Tech.Rep.,JulyPatel A,Afram F,Chen S,Ghose K(2011)MARSSx86:a full system simulator for x86CPUs.In: Design automation conference2011(DAC’11)Piccoli G,Santos HN,Rodrigues RE,Pousa C,Borin E,Quintão Pereira FM,Magno F(2014) Compiler support for selective page migration in NUMA architectures.In:International conference on parallel architectures and compilation techniques(PACT),pp369–380Radojkovi´c P,Cakarevi´c V,VerdúJ,Pajuelo A,Cazorla FJ,Nemirovsky M,Valero M(2013) Thread assignment of multithreaded network applications in multicore/multithreaded proces-sors.IEEE Trans Parallel Distrib Syst24(12):2513–2525Ribeiro CP,Méhaut JF,Carissimi A,Castro M,Fernandes LG(2009)Memory affinity for hierar-chical shared memory multiprocessors.In:International symposium on computer architecture and high performance computing(SBAC-PAD),pp59–66Ribeiro CP,Castro M,Méhaut JF,Carissimi A(2011)Improving memory affinity of geophysics applications on numa platforms using minas.In:International conference on high performance computing for computational science(VECPAR)Shwartsman S,Mihocka D(2008)Virtualization without direct execution or jitting:designing a portable virtual machine infrastructure.In:International symposium on computer architecture (ISCA),BeijingSwamy T,Ubal R(2014)Multi2sim4.2–a compilation and simulation framework for hetero-geneous computing.In:International conference on architectural support for programming languages and operating systems(ASPLOS)Tanenbaum AS(2007)Modern operating systems,3rd edn.Prentice Hall Press,Upper Saddle RiverTerboven C,an Mey D,Schmidl D,Jin H,Reichstein T(2008)Data and thread affinity in OpenMP programs.In:Workshop on memory access on future processors:a solved problem?(MAW), pp377–384.https:///10.1145/1366219.1366222Tikir MM,Hollingsworth JK(2008)Hardware monitors for dynamic page migration.J Parallel and Distrib Comput68(9):1186–1200Tolentino M,Cameron K(2012)The optimist,the pessimist,and the global race to exascale in20 megawatts.IEEE Comput45(1):95–97Torrellas J(2009)Architectures for extreme-scale computing.IEEE Comput42(11):28–35 Verghese B,Devine S,Gupta A,Rosenblum M(1996)OS support for improving data locality on CC-NUMA compute servers.Tech.Rep.,FebruaryVillavieja C,Karakostas V,Vilanova L,Etsion Y,Ramirez A,Mendelson A,Navarro N,Cristal A,Unsal OS(2011)DiDi:mitigating the performance impact of TLB Shootdowns using a shared TLB directory.In:International conference on parallel architectures and compilation techniques(PACT),pp340–349.https:///10.1109/PACT.2011.65Wang W,Dey T,Mars J,Tang L,Davidson JW,Soffa ML(2012)Performance analysis of thread mappings with a holistic view of the hardware resources.In:IEEE International symposium on performance analysis of systems&software(ISPASS)Woodacre M,Robb D,Roe D,Feind K(2005)The SGI Altix3000global shared-memory architecture.Tech.Rep.Zhou X,Chen W,Zheng W(2009)Cache sharing management for performance fairness in chip multiprocessors.In:International conference on parallel architectures and compilation techniques(PACT),pp384–393.https:///10.1109/PACT.2009.40Ziakas D,Baum A,Maddox RA,Safranek RJ(2010)Intel quickpath interconnect-architectural features supporting scalable system architectures.In:Symposium on high performance inter-connects(HOTI),pp1–6。

TGS_Tutor_5000_User_Manual_B5_eng GMDSS 模拟器 手册

COSPAS-SARSAT EPIRB E3 (McMurdo) ................................................... 44 COSPAS-SARSAT EPIRB G5 SmartFind (McMurdo) ................................. 45 Radar Transponder RT9 (MсMurdo) ............................................................ 45 Radar Transponder S4 Rescue (MсMurdo) ................................................. 46 TRON AIS-SART (Jotron)............................................................................. 46 Portable GMDSS VHF Radio Station SAILOR SP3520 ............................... 47 Portable VHF Radio Station SAILOR SP3300 ............................................. 47 Portable VHF Radio Station SAILOR SP3110 ............................................. 48 VHF Radio Station for the Communication with Aircraft TRON-AIR (Jotron)48 GPS Receiver FURUNO GP-90 ................................................................... 49 GLONASS/GPS Receiver TRANSAS T-701 ................................................ 49 TRANSAS M-3 AIS Transponder Class A .................................................... 50 Alarm Panel Sailor AP5065 .......................................................................... 51 Alarm Panel Sailor AP4365 .......................................................................... 52 Battery Panel for Sailor 5000 ........................................................................ 52 Battery Panel Sailor BP4680 ........................................................................ 53 Feeder Switchboard ...................................................................................... 53 Direction Finder Rhotheta RT-500-M ............................................................ 54 Radar and Steering Panel............................................................................. 55 VHF Radio Station SAILOR RT2048 ............................................................ 57 DSC Modem with Channel 70 Receiver SAILOR RM2042 .......................... 58 MF/HF Radio Station SAILOR RE2100 ........................................................ 59 MF/HF DSC Modem and Distress Frequency Scanning Receiver SAILOR RM2150 ......................................................................................................... 60 MF/HF DSC and Telex Modem, Scanning Receiver and Telex Terminal SAILOR RM2151/H2098B ............................................................................ 61 Remote Control Panel of Charging Unit SAILOR H2180 ............................. 62 Watch Receiver 2182 kHz SAILOR R501 .................................................... 63 Ship Security Alert System SAT-101 ............................................................ 63 Use of the Chart System ......................................................................... 64 General Information ...................................................................................... 64 Chart Controls ............................................................................................... 65 Chart Scaling................................................................................................. 66 Range and Bearing Measurements .............................................................. 67 Creating, Editing and Deleting Ships on the Chart ....................................... 68 Plotting a New Ship on the Chart .................................................. 68 Editing Parameters of the Ships Plotted on the Chart .................... 68 Changing Coordinates of the Ships Plotted on the Chart ............... 69 Deleting Ships Plotted on the Chart .............................................. 69 Obtaining Information on the Objects Plotted on the Chart .......................... 69

蒸汽与魔法的碰撞蜗牛游戏《黑金》大本营探访

第 现场蒸汽与魔法的碰撞◆ಙ፞ѳᓠḼ小T ◆ᤂтᑼḼო《黑金》是游戏蜗牛精心打造的蒸汽奇幻风格的3D多人在线网络游戏。

该游戏为玩家描述了一个唯美奇幻风格与写实蒸汽朋克风格相融合的世界。

笔者也对去年CJ现场的黑金“移动城堡”印象深刻,只是一直都没机会去好好体验一番游戏。

前段时间正好应蜗牛《黑金》邀请,笔者和坨坨也亲赴对方大本营为大家带来最深入、最详细的报道!蜗牛游戏《黑金》大本营探访蜗牛游戏公司坐落于“上有天堂下有苏杭”之称的苏州,笔者此次也是第一次来到这个美丽的地方,但是并没有忘记自己本身的重要任务,于是刚到苏州就立马前往蜗牛游戏的游戏运营中心。

沿途的一路美景也让笔者一直好奇蜗牛游戏的办公大楼到底是什么样子的?位于苏州城中南部的运营部并没有在什么高楼大厦里,而是藏在一个极具艺术气息的工作区中,在房屋外围充满各种艺术气息的涂鸦和装饰中,笔者第一眼就看到了当年最喜欢的游戏《航海世纪》LOGO;此刻笔者已经忍不住冲进去了。

在蜗牛游戏工作MM的陪同下,笔者终于一睹公司内部风采。

上楼后当看到熟悉的隔离式办公环境之时,笔者并未发觉和其他公司有什么区别,甚至一点游戏的气息都探测不到,笔者甚至怀疑走错地方了,直到顺着外围的过道逐渐深入,看到门口《九阴真经》李连杰的大幅宣传画时,笔者才确信这里的确是蜗牛游戏公司,而真正的乾坤还在后面。

在公司内部的正中央,工作人员一个个分散的坐在一个大圆环之中,而圆环从上往下逐渐扩大为成了一个大圆弧,笔者的第一反应:这不是美国电影中情报局的布局形式吗?太高端帅气了,旁边的陪同MM则笑着给我解释道:不觉得像是一个蜗牛的造型吗?确实蜗牛游戏公司中各个地方都充满了艺术气息,在随后的参观中无论是年画剪纸式的贴纸,还是由员工照片组成的蜗牛图案,亦或是构建奇特的员工餐厅,在各个细节之处都能发现不同于其他公司的独特艺术文化。

浓郁的艺术氛围环境设计,或许和蜗牛游戏CEO石总艺术出生有关,不过能在这种环境里工作的话,所诞生的游戏其文化韵味绝对不会差!当然以上的内容并不是我们的主题,在钓足了玩家们的胃口后,想必大家一定对《黑金》这款游戏到底是什么样子的充满了好奇。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

The gem5SimulatorNathan Binkert1,Bradford Beckmann2,Gabriel Black3,Steven K.Reinhardt2,Ali Saidi4,Arkaprava Basu5,Joel Hestness6, Derek R.Hower5,Tushar Krishna7,Somayeh Sardashti5,Rathijit Sen5,Korey Sewell8, Muhammad Shoaib5,Nilay Vaish5,Mark D.Hill5,and David A.Wood5AbstractThe gem5simulation infrastructure is the merger of the best aspects of the M5[4]and GEMS[9]simulators. M5provides a highly configurable simulation framework, multiple ISAs,and diverse CPU models.GEMS comple-ments these features with a detailed andflexible mem-ory system,including support for multiple cache coher-ence protocols and interconnect models.Currently,gem5 supports most commercial ISAs(ARM,ALPHA,MIPS, Power,SPARC,and x86),including booting Linux on three of them(ARM,ALPHA,and x86).The project is the result of the combined efforts of many academic and industrial institutions,including AMD, ARM,HP,MIPS,Princeton,MIT,and the Universities of Michigan,Texas,and Wisconsin.Over the past ten years,M5and GEMS have been used in hundreds of pub-lications and have been downloaded tens of thousands of times.The high level of collaboration on the gem5 project,combined with the previous success of the com-ponent parts and a liberal BSD-like license,make gem5a valuable full-system simulation tool.1IntroductionComputer architecture researchers commonly use soft-ware simulation to prototype and evaluate their ideas. As the computer industry continues to advance,the range of designs being considered increases.On one hand,the 1Hewlett-Packard Labs,Palo Alto,Cal.2Advanced Micro Devices,Inc.,Bellevue,Wash.3Google,Inc.,Mountain View,Cal.4ARM,Inc.,Austin,Tex.5University of Wisconsin,Madison,Wisc.6University of Texas,Austin,Tex.7Massachusetts Institute of Technology,Cambridge,Mass.8University of Michigan,Ann Arbor,Mich.emergence of multicore systems and deeper cache hier-archies has presented architects with several new dimen-sions of exploration.On the other hand,researchers need aflexible simulation framework that can evaluate a wide diversity of designs and support rich OS facilities includ-ing IO and networking.Computer architecture researchers also need a simula-tion framework that allows them to collaborate with their colleagues in both industry and academia.However,a simulator’s licensing terms and code quality can inhibit that collaboration.Some open source software licenses can be too restrictive,especially in an industrial setting, because they require publishing any simulator enhance-ments.Furthermore,poor code quality and the lack of modularity can make it difficult for new users to under-stand and modify the code.The gem5simulator overcomes these limitations by providing aflexible,modular simulation system that is capable of evaluating a broad range of systems and is widely available to all researchers.This infrastructure providesflexibility by offering a diverse set of CPU mod-els,system execution modes,and memory system models.A commitment to modularity and clean interfaces allows researchers to focus on a particular aspect of the code without understanding the entire code base.The BSD-based license makes the code available to all researchers without awkward legal restrictions.This paper provides a brief overview of gem5’s goals, philosophy,capabilities,and future work along with pointers to sources of additional information.2Overall GoalsThe overarching goal of the gem5simulator is to be a community tool focused on architectural modeling.Three key aspects of this goal areflexible modeling to appeal to a broad range of users,wide availability and utility toFigure1:Speed vs.Accuracy Spectrum.the community,and high level of developer interaction to foster collaboration.2.1FlexibilityFlexibility is a fundamental requirement of any success-ful simulation infrastructure.For instance,as an idea evolves from a high-level concept to a specific design,ar-chitects need a tool that can evaluate systems at various levels of detail,balancing simulation speed and accuracy. Different types of experiments may also require different simulation capabilities.For example,afine-grain clock gating experiment may require a detailed CPU model, but modeling multiple cores is unnecessary.Meanwhile, a highly scalable interconnect model may require several CPUs,but those CPUs don’t need much detail.Also,by using the same infrastructure over time,an architect will be able to get more done more quickly with less overhead. The gem5simulator provides a wide variety of capa-bilities and components which give it a lot offlexibility. These vary in multiple dimensions and cover a wide range of speed/accuracy trade offs as shown in Figure1.The key dimensions of gem5’s capabilities are:•CPU Model.The gem5simulator currently provides four different CPU models,each of which lie at a unique point in the speed-vs.-accuracy spectrum.AtomicSim-ple is a minimal single IPC CPU model,TimingSimple is similar but also simulates the timing of memory refer-ences,InOrder is a pipelined,in-order CPU,and O3is a pipelined,out-of-order CPU model.Both the O3and InOrder models are“execute-in-execute”designs[4].•System Mode.Each execution-driven CPU model can operate in either of two modes.System-call Emula-tion(SE)mode avoids the need to model devices or anoperating system(OS)by emulating most system-level services.Meanwhile,Full-System(FS)mode executes both user-level and kernel-level instructions and models a complete system including the OS and devices.•Memory System.The gem5simulator includes twodifferent memory system models,Classic and Ruby. The Classic model(from M5)provides a fast and eas-ily configurable memory system,while the Ruby model (from GEMS)provides aflexible infrastructure capable of accurately simulating a wide variety of cache coher-ent memory systems.The gem5simulator can also execute workloads in a number of ISAs,including today’s most common ISAs, x86and ARM.This significantly increases the number of workloads and configurations gem5can simulate. Section4provides a more detailed discussion of these capabilities.2.2AvailabilityThere are several types of gem5user;each has different goals and requirements.These include academic and cor-porate researchers,engineers in industry,and undergrad-uate and graduate students.We want the gem5simulator to be broadly available to each of these types of user.The gem5license(based on BSD)is friendly both to corporate users,since businesses need not fear being forced to re-veal proprietary information,and to to academics,since they retain their copyright and thus get credit for their contributions.2.3High level of collaborationFull-system simulators are complex tools.Dozens of person-years of effort have gone into the gem5simula-tor,developing both the infrastructure forflexible model-ing and the numerous detailed component models.By being an open source,community-led project,we can leverage the work of many researchers,each with differ-ent specialties.The gem5community is very active and leverages a number of collaborative technologies to fos-ter gem5use and development,including mailing lists,a wiki,web-based patch reviews,and a publicly accessible source repository.3Design FeaturesThis section focuses on a few key aspects of gem5’s im-plementation:pervasive object orientation,Python inte-gration,domain-specific languages,and use of standardinterfaces.While most of these features are simply good software engineering practice,they are all particularly useful for designing simulators.3.1Pervasive Object-Oriented DesignFlexibility is an important goal of the gem5simulator and key aspect of its success.Flexibility is primarily achieved through object-oriented design.The ability to construct configurations from independent,composable objects leads naturally to advanced capabilities such as multi-core and multi-system modeling.All major simulation components in the gem5simu-lator are SimObjects and share common behaviors for configuration,initialization,statistics,and serialization (checkpointing).SimObjects include models of concrete hardware components such as processor cores,caches,in-terconnect elements and devices,as well as more abstract entities such as a workload and its associated process con-text for system-call emulation.Every SimObject is represented by two classes,one in Python and one in C++which derive from SimObject base classes present in each language.The Python class definition specifies the SimObject’s parameters and is used in script-based configuration.The common Python base class provides uniform mechanisms for instantiation, naming,and setting parameter values.The C++class en-compasses the SimObject’s state and remaining behavior, including the performance-critical simulation model. 3.2Python IntegrationThe gem5simulator derives significant power from tight integration of Python into the simulator.While85%of the simulator is written in C++,Python pervades all aspects of its operation.As mentioned in Section3.1, all SimObjects are reflected in both Python and C++. The Python aspect provides initialization,configuration, and simulation control.The simulator begins execut-ing Python code almost immediately on start-up;the standard main()function is written in Python,and all command-line processing and startup code is written in Python.3.3Domain-Specific LanguagesIn situations that require significantflexibility in perform-ing a specialized task,domain-specific languages(DSLs) provide a powerful and concise way to express a variety of solutions by leveraging knowledge and idioms common to that problem space.The gem5environment provides two domain-specific languages,one for specifying instruc-tion sets(inherited from M5)and one for specifying cache coherence protocols(inherited from GEMS).ISA DSL.The gem5ISA description language unifies the decoding of binary instructions and the specification of their semantics.The gem5CPU models achieve ISA independence by using a common C++base class to de-scribe instructions.Derived classes override virtual func-tions like execute()to implement opcodes,such as add. Instances of these derived classes represent specific ma-chine instructions,such as add r1,r2,r3.Implementing a specific ISA thus requires a set of C++declarations for these derived classes,plus a function that takes a machine instruction and returns an instance of one of the derived classes that corresponds to that instruction.The ISA description language allows users to specify this required C++code compactly.Part of the language allows the specification of class templates(more general than C++templates)that cover broad categories of in-structions,such as register-to-register arithmetic opera-tions.Another portion of the language provides for the specification of a decode tree that concisely combines op-code decoding with the creation of specific derived classes as instances of the previously defined templates.While the original ISA description language targeted RISC architectures such as the Alpha ISA,it has been sig-nificantly extended to cope with complex variable-length ISAs,particularly x86,and ISAs with complex register semantics like SPARC.These extensions include a mi-crocode assembler,a predecoder,and multi-level register index translation.These extensions are discussed in more detail in a recent book chapter[5].Cache Coherence DSL.SLICC is a domain-specific language that gives gem5theflexibility to implement a wide variety of cache coherence protocols.Essentially, SLICC defines the cache,memory,and DMA controllers as individual per-memory-block state machines that to-gether form the overall protocol.By defining the con-troller logic in a higher-level language,SLICC allows dif-ferent protocols to incorporate the same underlying state transition mechanisms with minimal programmer effort. The gem5version of SLICC is very similar to the prior GEMS version of SLICC[9].Just like the prior version, gem5SLICC defines protocols as a set of states,events, transitions,and actions.Within the specificationfiles, individual transition statements define the valid combi-nations and actions within each transition specify the op-erations that must be performed.Also similar to the pre-vious version,gem5SLICC ties the state machine-specific logic to protocol-independent components such as cache memories and network ports.While gem5SLICC contains several similarities to its predecessor design,the language does include several en-hancements.First,the language itself is now imple-mented in Python rather than C++,making it easier to read and edit.Second,to adhere to the gem5SimOb-ject structure,all configuration parameters are specified as input parameters and gem5SLICC automatically gen-erates the appropriate C++and Pythonfiles.Finally, gem5SLICC allows local variables to simplify program-ming and improve performance.3.4Standard InterfacesStandard interfaces are fundamental to object-oriented design.Two central interfaces are the port interface and the message buffer interface.Ports are one of the interfaces used to connect two memory objects together in gem5.In the Classic memory system,the ports interface connects all memory objects including CPUs to caches,caches to busses,and busses to devices and memories.Ports support three mecha-nisms for accessing data(timing,atomic,and functional) and an interface for things like determining topology and debugging.Timing mode is used to model the detailed timing of memory accesses.Requests are made to the memory system by sending messages,and responses are expected to return asynchronously via other messages. Atomic mode is used to get some timing information,but is not message-oriented.When an atomic call is made (via a function call),the state change for the operation is performed synchronously.This has higher performance but gives up some accuracy because message interactions are not modeled.Finally,functional accesses update the simulator state without changing any timing information. These are generally used for debugging,system-call emu-lation,and initialization.Ruby utilizes the ports interface to connect to CPUs and devices,and adds message buffers to connect to Ruby objects internally.Message buffers are similar to ports in that they provide a standard communication interface. However,message buffers differ in some subtle ways with regards to message typing and storage.In the future, ports and message buffers may evolve into a unified in-terface.4Simulation CapabilitiesThe gem5simulator has a wide range of simulation capa-bilities ranging from the selection of ISA,CPU model,and coherence protocol to the instantiation of interconnection networks,devices and multiple systems.This section de-scribes some of the different options available in these categories.ISAs.The gem5simulator currently supports a variety of ISAs including Alpha,ARM,MIPS,Power,SPARC, and x86.The simulator’s modularity allows these differ-ent ISAs to plug into the generic CPU models and the memory system without having to specialize one for the other.However,not all possible combinations of ISAs and other components are currently known to work.An up-to-date list can be found on the gem5website. Execution Modes.The gem5simulator can oper-ate in two modes:System-call Emulation(SE)and Full-System(FS).In SE mode,gem5emulates most com-mon system calls(e.g.read()).Whenever the pro-gram executes a system call,gem5traps and emulates the call,often by passing it to the host operating system. There is currently no thread scheduler in SE mode,so threads must be statically mapped to cores,limiting its use with multi-threaded applications.The SPEC CPU benchmarks are often run in SE mode.In FS mode,gem5simulates a bare-metal environment suitable for running an OS.This includes support for in-terrupts,exceptions,privilege levels,I/O devices,etc. Because of the additional complexity and completeness required,not all ISAs current support FS mode. Compared to SE mode,FS mode improves both the simulation accuracy and variety of workloads that gem5 can execute.While SPEC CPU benchmarks can be run in SE mode,running them in FS mode will provide more realistic interactions with the OS.Workloads that require many OS services or I/O devices may only be run in FS mode.For example,because a web server relies on the kernel’s TCP/IP protocol stack and a network interface to send and receive requests and a web browser requires a X11server and display adapter to visualize web pages these workloads must be run is FS mode.CPU Models.The gem5simulator supports four dif-ferent CPU models:AtomicSimple,TimingSimple,In-Order,and O3.AtomicSimple and TimingSimple are non-pipelined CPU models that attempt to fetch,decode, execute and commit a single instruction on every cycle. The AtomicSimple CPU is a minimal,single IPC CPU which completes all memory accesses immediately.This low overhead makes AtomicSimple a good choice for sim-ulation tasks such as fast-forwarding.Correspondingly, the TimingSimple CPU also only allows one outstanding memory request at a time,but the CPU does model the timing of memory accesses.The InOrder model is an“execute-in-execute”CPU model emphasizing instruction timing and simulation ac-curacy with an in-order pipeline.InOrder can be config-ured to model different numbers of pipeline stages,issue width,and numbers of hardware threads.Finally,the O3CPU is a pipelined,out-of-order model that simulates dependencies between instructions,func-tional units,memory accesses,and pipeline stages.Pa-rameterizable pipeline resources such as the load/store queue and reorder buffer allow O3to simulate superscalar architectures and CPUs with multiple hardware threads (SMT).The O3model is also“execute-in-execute”,mean-ing that instructions are only executed in the execute stage after all dependencies have been resolved.Cache Coherence Protocols.SLICC enables gem5’s Ruby memory model to implement many differ-ent types of invalidation-based cache coherence protocols, from snooping to directory protocols and several points in between.SLICC separates cache coherence logic from the rest of the memory system,providing the necessary abstraction to implement a wide range of protocol logic. Similar to its GEMS predecessor[9],SLICC performs all operations at a cache-block granularity.The word-level granularity required by update-based protocols is not cur-rently supported.This limitation has not been a issue so far because invalidation-based protocols dominate the commercial market.Specifically,gem5SLICC currently models a broadcast-based protocol based on the AMD Opteron TM[7],as well as a CMP directory protocol[10]. Not only is SLICCflexible enough to model different types of protocols,but it also simulates them in sufficient depth to model detailed timing behavior.Specifically, SLICC allows specifying transient states within the in-dividual state machines as cache blocks move from one base state to another.SLICC also includes separate vir-tual networks(work message classes)so message dependencies and stalls can be properly ing these virtual networks,the SLICC-generated controllers connect to the interconnection network. Interconnection Networks.The Ruby memory model supports a vast array of interconnection topologies and includes two different network models.In essence, Ruby can create any arbitrary topology as long as it is composed of point-to-point links.A simple Pythonfile declares the connections between components and short-est path analysis is used to create the routing tables. Once Ruby creates the links and routing tables,it can implement the resulting network in one of two ways. Thefirst Ruby network model is referred to as the Sim-ple network.The Simple network models link and router latency as well as link bandwidth.However,the Simple network does not model router resource contention and flow control.This model is great for experiments that require Ruby’s detailed protocol modeling but that can sacrifice detailed network modeling for faster simulation. The second Ruby network model is the Garnet network model[1].Unlike the simple network,Garnet models the router micro-architecture in detail,including all relevant resource contention andflow control timing.This model is suitable for on-chip network studies.Devices.The gem5simulator supports several I/O devices ranging from simple timers to complex network interface controllers.Base classes are available that en-capsulates common device interfaces such as PCI to avoid code duplication and simplify implementing new devices. Currently implemented models includes NICs,an IDE controller,a frame buffer,DMA engines,UARTs,and interrupt controllers.Modeling Multiple Systems.Because of the simu-lator’s object oriented design it also supports simulating multiple complete systems.This is done by instantiating another set of objects(CPU,memory,I/O devices,etc.). Generally,the user connects the systems via the network interfaces described above to create a client/server pair that communicate over TCP/IP.Since all the simulated systems are tightly coupled within gem5the results of multi-system simulation is still deterministic.5Future WorkWhile gem5is a highly capable simulator,there is always a desire for additional features and other improvements.A few of the efforts underway or under consideration in-clude:•Afirst-class power model.While external power mod-els such as Orion[6]and McPAT[8]have been used with GEMS and M5,we are working on a more com-prehensive,modular,and integrated power model for gem5.•Full cross-product ISA/CPU/memory system support. The modularity andflexibility of gem5enables a wide variety of combinations of ISAs,CPU models,and memory systems,as illustrated in Figure1,each of which can be used in SE or FS mode.Because each component model must support the union of all fea-tures required by any ISA in any mode,particular com-ponent models do not always work in every conceivable circumstance.We continue to work to eliminate these inconsistencies.•Parallelization.To address the inherent performance limitations of detailed simulation and leverage the ubiq-uity of multi-core systems,we have been refactoringgem5’s internal event system to support parallel dis-crete event simulation[11].•Checkpoint import.Although gem5’s simple CPU models are much faster than their detailed counter-parts,they are still considerably slower than binary translation-based emulators such as QEMU[3]and SimNow TM[2].Rather than duplicating the enor-mous effort of developing a binary translation capabil-ity within gem5,we plan to enable the transfer of state checkpoints from these emulators into ers will be able to fast-forward large workloads to interesting points using these high-performance alternatives,then simulate from those points in gem5.Even higher per-formance may be possible by using a hardware virtual machine environment such as KVM1rather than binary translation.6User ResourcesAll gem5simulator documentation and information is available at the website .The web-site includes instructions on how to check out,build,and run the gem5simulator,as well as how to download sup-plemental supportfiles like OS binaries and disk images. The gem5user community is active and communicates through three mailing lists:(1)the announce mailing list is used to announce significant modifications or achieve-ments;(2)the user mailing list is used for general discus-sions about gem5and for questions about how to use it; and(3)the dev mailing list is for discussions regarding mainline gem5development.Developers willfind support resources in the form of systems for revision control,bug tracking,code reviews, and code browsing.All of these can be accessed through the main website.We encourage you to visit the web site,subscribe to the mailing lists,and help us make gem5a valuable com-munity resource.AcknowledgementsThe authors of this paper are only a small subset of peo-ple that have contributed to gem5over the years.We would like to specially thank all those prior contributors to GEMS and M5,especially Dan Gibson who played a key role in the initial integration effort.Without their work,the unification of GEMS and M5would not have been possible.1The gem5simulator has been developed with gen-erous support from several sources,including the Na-tional Science Foundation,AMD,ARM,Google,Hewlett-Packard,IBM,Intel,Microsoft,MIPS,Sandia National Laboratories and Sun.Individuals working on gem5 have also been supported by fellowships from Intel,Lu-cent,and the Alfred P.Sloan Foundation.This material is based upon work supported by the National Science Foundation under the following grants:CCR-0105503, CCR-0219640,CCR-0324878,EAI/CNS-0205286,CCR-0105721,CRI-0551401,CSR-0720565,CCF-0916725,and CCF-1017650.Any opinions,findings and conclusions or recommenda-tions expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation(NSF)or any other sponsor. References[1]Agarwal,N.,Krishna,T.,Peh,L.-S.,andJha,N.K.GARNET:A detailed on-chip network model inside a full-system simulator.In Proceedings of IEEE International Symposium on Performance Analysis of Systems and Software(ISPASS)(Apr.2009),pp.33–42.[2]Barnes,B.,and Slice,J.SimNow:A fast andfunctionally accurate AMD X86-64system simula-tor.Tutorial at the IEEE International Workload Characterization Symposium,2005.[3]Bellard,F.QEMU,a fast and portable dynamictranslator.In Proceedings of the USENIX Annual Technical Conference(2005),pp.41–46.[4]Binkert,N.L.,Dreslinski,R.G.,Hsu,L.R.,Lim,K.T.,Saidi,A.G.,and Reinhardt,S.K.The M5Simulator:Modeling Networked Systems.IEEE Micro26,4(Jul/Aug2006),52–60.[5]Black,G.,Binkert,N.,Reinhardt,S.K.,and Saidi,A.Processor and System-on-Chip Sim-ulation.Springer,2010,ch.5,“Modular ISA-Independent Full-System Simulation”.[6]Kahng,A.B.,Li,B.,Peh,L.-S.,and Samadi,K.ORION2.0:a fast and accurate NoC power and area model for early-stage design space explo-ration.In Proceedings of the Conference on Design, Automation and Test in Europe(2009),pp.423–428.[7]Keltcher,C.N.,McGrath,K.J.,Ahmed,A.,and Conway,P.The AMD Opteron Processor forMultiprocessor Servers.IEEE Micro23,2(Mar/Apr 2003),66–76.[8]Li,S.,Ahn,J.H.,Strong,R.D.,Brockman,J.B.,Tullsen,D.M.,and Jouppi,N.P.Mc-PAT:an integrated power,area,and timing modeling framework for multicore and manycore architectures.In Proceedings of the42nd Annual IEEE/ACM In-ternational Symposium on Microarchitecture(2009), pp.469–480.[9]Martin,M.M.K.,Sorin, D.J.,Beckmann,B.M.,Marty,M.R.,Xu,M.,Alameldeen,A.R.,Moore,K.E.,Hill,M.D.,and Wood,D. A.Multifacet’s general execution-driven mul-tiprocessor simulator(GEMS)toolset.SIGARCH Comput.Archit.News33,4(2005),92–99.[10]Marty,M.R.,Bingham,J.D.,Hill,M.D.,Hu,A.J.,Martin,M.M.K.,and Wood,D.A.Improving multiple-CMP systems using token coher-ence.In Proceedings of the11th Annual International Symposium on High-Performance Computer Archi-tecture(HPCA)(2005),pp.328–339.[11]Reinhardt,S.K.,Hill,M.D.,Larus,J.R.,Lebeck,A.R.,Lewis,J.C.,and Wood,D.A.The Wisconsin Wind Tunnel:Virtual prototyping of parallel computers.In Proceedings of the1993 ACM SIGMETRICS Conference on Measurement and Modeling of Computer Systems(1993),pp.48–60.。