数字电路实验二讲稿

数字电路实验二实验报告

实验二门电路逻辑变换一.实验目的1 学会门电路逻辑变换的基本方法。

2 掌握虚拟实验逻辑转换器的使用方法。

二.实验设备安装有Multsim10软件的个人电脑。

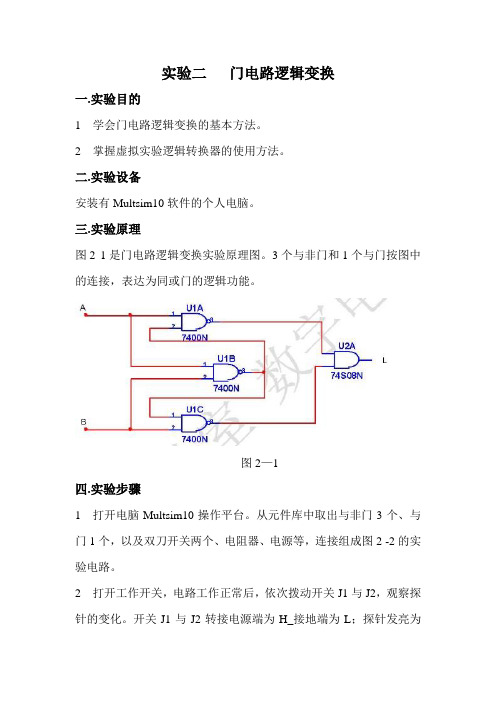

三.实验原理图2 1是门电路逻辑变换实验原理图。

3个与非门和1个与门按图中的连接,表达为同或门的逻辑功能。

图2—1四.实验步骤1 打开电脑Multsim10操作平台。

从元件库中取出与非门3个、与门1个,以及双刀开关两个、电阻器、电源等,连接组成图2 -2的实验电路。

2 打开工作开关,电路工作正常后,依次拨动开关J1与J2,观察探针的变化。

开关J1与J2转接电源端为H_接地端为L;探针发亮为H_熄灭为L,将观察结果填入表2- 1。

表2-1J1 J2 探针L L HL H LH L LH H H图2—21)J1接电源,J2接地2)J1接地,J2接电源3)J1接地,J2接地4)J1接电源,J2接电源3将表2- 1变换为如下表2-2的真值表。

开关J1为A,J2为B,H为“1”,L为“0”;探针x1为F发亮为“1”,熄灭为“0”。

表2-2A B F0 0 10 1 01 0 01 1 14 按上述图2-2写出逻辑表达式为BAF,根据真值表及=BA∙+∙逻辑表达式判断,它是一个同或门电路。

5 逻辑转换器的使用重新设置Multisim仿真工作界面,运用逻辑转换器,转换出逻辑表达式为BF+=的门电路逻辑图,然后配置开关、探针等,并将电ABA路仿真运转验证,列出实验验证结果(例如上述表2-1)。

应注意,在逻辑转换器中,逻辑表达式有不同,要用“’”表示求反,例如用A’来表示A的求反即A,其它类似。

1)点击simulate-----instruments------logic converter,打开逻辑转换仪。

2)设计出逻辑函数表达式为:B=,如图1所示。

F+ABA3)点击右边第五个图标,把逻辑表达式转换为与,或非门电路,如图2所示。

4)点击右边第六个图标,把逻辑表达式转换为与非门电路,如图3所示。

数字电路实验讲义

数字电路实验讲义课题:实验一门电路逻辑功能及测试课型:验证性实验教学目标:熟悉门电路逻辑功能,熟悉数字电路实验箱及示波器使用方法重点:熟悉门电路逻辑功能。

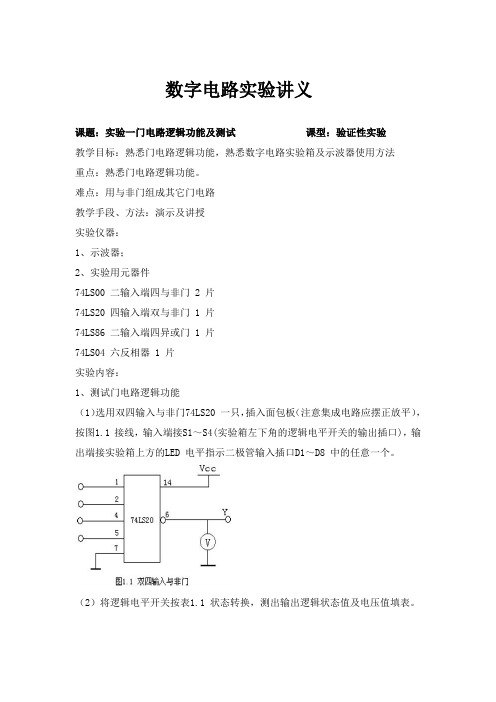

难点:用与非门组成其它门电路教学手段、方法:演示及讲授实验仪器:1、示波器;2、实验用元器件74LS00 二输入端四与非门 2 片74LS20 四输入端双与非门 1 片74LS86 二输入端四异或门 1 片74LS04 六反相器 1 片实验内容:1、测试门电路逻辑功能(1)选用双四输入与非门74LS20 一只,插入面包板(注意集成电路应摆正放平),按图1.1接线,输入端接S1~S4(实验箱左下角的逻辑电平开关的输出插口),输出端接实验箱上方的LED 电平指示二极管输入插口D1~D8 中的任意一个。

(2)将逻辑电平开关按表1.1 状态转换,测出输出逻辑状态值及电压值填表。

2、逻辑电路的逻辑关系(1)用74LS00 双输入四与非门电路,按图1.2、图1.3 接线,将输入输出逻辑关系分别填入表1.2,表1.3 中。

(2)写出两个电路的逻辑表达式。

3、利用与非门控制输出用一片74LS00 按图1.4 接线。

S 分别接高、低电平开关,用示波器观察S 对输出脉冲的控制作用。

4、用与非门组成其它门电路并测试验证。

(1)组成或非门:用一片二输入端四与非门组成或非门B==,画出电路图,测试并填+Y∙ABA表1.4。

(2)组成异或门:①将异或门表达式转化为与非门表达式;②画出逻辑电路图;③测试并填表1.5。

5、异或门逻辑功能测试(1)选二输入四异或门电路74LS86,按图1.5 接线,输入端1、2、4、5 接电平开关输出插口,输出端A、B、Y 接电平显示发光二极管。

(2)将电平开关按表1.6 的状态转换,将结果填入表中。

6、逻辑门传输延迟时间的测量用六反相器74LS04 逻辑电路按图1.6 接线,输入200Hz 连续脉冲(实验箱脉冲源),将输入脉冲和输出脉冲分别接入双踪示波器Y1、Y2 轴,观察输入、输出相位差。

数字电路实验报告 实验2

实验二 译码器及其应用一、 实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

4、学习译码器的扩展。

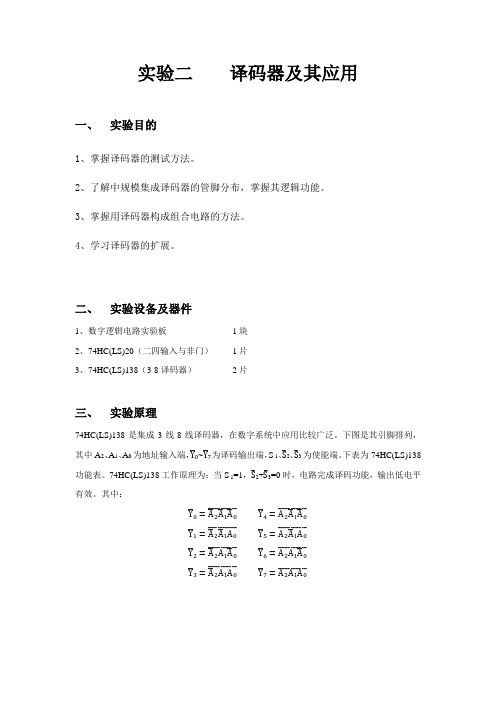

二、 实验设备及器件1、数字逻辑电路实验板1块 2、74HC(LS)20(二四输入与非门) 1片 3、74HC(LS)138(3-8译码器)2片三、 实验原理74HC(LS)138是集成3线-8线译码器,在数字系统中应用比较广泛。

下图是其引脚排列,其中A 2、A 1、A 0为地址输入端,Y ̅0~Y ̅7为译码输出端,S 1、S ̅2、S ̅3为使能端。

下表为74HC(LS)138功能表。

74HC(LS)138工作原理为:当S 1=1,S ̅2+S ̅3=0时,电路完成译码功能,输出低电平有效。

其中:Y ̅0=A ̅2A ̅1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅4=A 2A ̅1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅1=A ̅2A ̅1A 0̅̅̅̅̅̅̅̅̅̅ Y ̅5=A 2A ̅1A 0̅̅̅̅̅̅̅̅̅̅ Y ̅2=A ̅2A 1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅6=A 2A 1A ̅0̅̅̅̅̅̅̅̅̅̅ Y ̅3=A ̅2A 1A 0̅̅̅̅̅̅̅̅̅̅Y ̅7=A 2A 1A 0̅̅̅̅̅̅̅̅̅̅因为74HC(LS)138的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项(的非),因此可以利用八条输出线组合构成三变量的任意组合电路。

实验用器件管脚介绍:1、74HC(LS)20(二四输入与非门)管脚如下图所示。

2、74HC(LS)138(3-8译码器)管脚如下图所示。

四、实验内容与步骤(四学时)1、逻辑功能测试(基本命题)m。

验证74HC(LS)138的逻辑功能,说明其输出确为最小项i注:将Y̅0~Y̅7输出端接到LED指示灯上,因低电平有效,所以当输入为000时,Y̅0所接的LED指示灯亮,其他同理。

数字电路实验讲义

数字电路实验讲义目录1 数字电路实验箱简介2 实验一基本门电路和触发器的逻辑功能测试3 实验二常用集成组合逻辑电路(MSI)的功能测试及应用4 实验三常用中规模集成时序逻辑电路的功能及应用5 实验四组合逻辑电路的设计6 实验五时序逻辑电路的设计7 实验六综合设计实验8 附录功能常用芯片引脚图数字电路实验箱简介TPE系列数字电路实验箱是清华大学科教仪器厂的产品,该实验箱提供了数字电路实验所必需的基本条件。

如电源,集成电路接线板,逻辑电平产生电路,单脉冲产生电路和逻辑电平测量显示电路,实验箱还为复杂实验提供了一些其他功能。

下面以JK触发器测试为例说明最典型的测试电路,图1为74LS112双JK触发器的测试电路。

其中Sd、Rd 、J、K为电平有效的较入信号,由实验箱的逻辑电平产生电路提供。

CP为边沿有效的触发信号,由单脉冲产生电路提供。

Q和为电路的输出,接至逻辑电平测量显示电路,改变不同输入的组合和触发条件,记录对应的输出,即可测试该触发器的功能。

逻辑电平测量显示图1. JK触发器测试电路实验一 基本门电路和触发器的逻辑功能测试一、 实验目的1、掌握集成芯片管脚识别方法。

2、掌握门电路逻辑功能的测试方法。

3、掌握RS 触发器、JK 触发器的工作原理和功能测试方法。

二、实验设备与器件 1、数字电路实验箱 2、万用表 3、双列直插式组件 74LS00:四—2输入与非门 74LS86:四—2输入异或门 74LS112:双J-K 触发器三、实验原理与内容 1、测试与非门的逻辑功能74LS00为四—2输入与非门,在一个双列直插14引脚的芯片里封装了四个2输入与非门,引脚图见附录。

14脚为电源端,工作时接5V,7脚为接地端,1A ,113和1Y 组成一个与非门,B A Y 111⋅=。

剩余三个与非门类似。

按图1—1连接实验电路。

改变输信号,测量对应输出,填入表1—1中,验证其逻辑功能。

测 量 显示逻 辑 电平图1—1 74LS00测试电路2、测试基本RS 触发器功能两个与非门相接可构成基本RS 触发器,R 、S 为触发器的清0和置1输入端。

数字电路与逻辑设计实验报告二

实验二常用电子仪器的使用

一、实验目的

掌握常用的电子仪器(示波器、函数信号发生器、直流稳压电源、数字万用表等)的主要技术指标、性能及正确使用方法。

二、实验条件,设备,器材

示波器、函数信号发生器、直流稳压电源、数字万用表。

三、实验原理

输入的电信号通过一个ADC(通常采用8bits 或者256个量化电平)数字化,输出的数据存储在示波器的存储器中。

数字化速率和放大器频宽决定所能精确地取样和显示的最快信号。

四、实验内容

1、示波器探头校正

2、测量并记录实验箱5M、1M、500K、100K连续脉冲源;

3、使用信号发生器产生50M、1M、1K正弦波、方波等信号。

五、实验步骤及数据记录

1.示波器探头校正

将示波器探头接【Probe Comp】; 使用【Auto Scale】; 测量、记录相关数据并保存波形图像。

2.测量并记录实验箱连续脉冲源

测量、记录相关数据并保存波形图像。

3.使用信号发生器产生相关信号并测量

使用信号发生器产生50M、1M、10K、1K正弦波、方波等信号

六、实验分析,结论,体会

通过本次实验,初步掌握了常用的电子仪器(示波器、函数信号发生器、直流稳压电源、数字万用表等)的主要技术指标、性能及正确使用方法。

数字电路实验二

(1) 根据设计要求和要点提示,设计出东西方向和南北方向绿、 黄、红灯的逻辑表达式;

东西方向:绿:EWG= 黄:EWY= 红:EWR= 南北方向:绿:NSG= 黄:NSY= 红:NSR= (2) 根据控制信号灯表达式画出实现电路图,即完善电路图5; (3)用74LS164、74LS08和74LS00在实验箱上连接出电路; (4) 列表记录电路的输入与输出结果。

0 0 000 0 0 0 QA QB QC QD QE QF QG QH 1 QA QB QC QD QE QF QG 0 QA QB QC QD QE QF QG 0 QA QB QC QD QE QF QG

,

图4 74164时序图

4. 设计任务

由东西方向和南北方向道路的汇合点形成十字交叉路口,为确保车辆 安全通行,在交叉路口的每个入口处设置了红、黄、绿三色交通信号灯, 红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停靠 在禁止线之外。

1 (黄灯亮)

(3) 调节CP周期为4秒,南北方向亮6个CP周期时,东西方向绿灯亮5 个CP周期时长,接着黄灯亮1个CP周期时长。反之亦然。即实现了两个 方向红、黄、绿灯交替点亮 24、4、5秒的要求。

5. 实验内容

1. 设计实现一个模12的扭环计数器。

(1)用74LS164在实验箱上连接出电路; (2)列表记录电路的输出结果(用LED显示)。

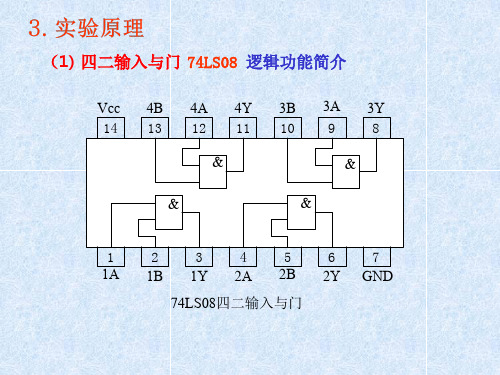

(1) 四二输入与门 74LS08 逻辑功能简介

Vcc 4B 4A 4Y 3B 3A 3Y

14 13 12 11 10 9

8

&

&

&

&

1

2

3

4

5

数字电路实验二讲稿

74LS04灌电流特性

测试电路

东南大学电工电子实验中心

74LS04灌电流特性 Y:4.97V 100K

Y:146mV

东南大学电工电子实验中心

74LS04灌电流特性 Y:4.99V 10K

Y:169mV

东南大学电工电子实验中心

74LS04灌电流特性

Y:5.0V

2K

Y:225mV

实验方法来测定或通过器件手册查到的

东南大学电工电子实验中心

数字电路延时

2014/11/12

东南大学电工电子实验中心

61

实验电路

3(奇数)个门组成的环形振荡器

假设电路接通电源的一瞬间,电路A点为逻辑1 经过一级门的延迟时间,使B点为逻辑0 又经过一级门的延时,使C点为逻辑1 再经过一级门的延时A点由逻辑1变成逻辑0 同理再经过3级门的延时,A点重新回到逻辑1,电路振荡 要使某一点发生一个周期的振荡,必须要经过6级门的延迟时间

5

演示实验1

采用示波器X-Y方式测量并比较74LS04和74HC04 两种器件的电压传输特性VO=f(Vi)

2014/11/12

东南大学电工电子实验中心

6

74LS04传输特性曲线

东南大学电工电子实验中心

74LS04传输特性曲线 X:295mV Y:4.48V

X:1.15V Y:124mV

东南大学电工电子实验中心

100K

Y:146mV

东南大学电工电子实验中心

74LS04拉电流特性

10K

Y:3.57V

Y:146mV

东南大学电工电子实验中心

74LS04拉电流特性

2K

Y:3.47V

数字电子技术--实验2

3、 CC4012电压传输特性测试

如图2-3所示,调节电位器RW,使Vi 从0V向5V变化,逐点测试Vi和VO值,并将 结果记录。以便画出实验数据曲线。

四、实验结果分析

1、TTL与非门闲置输入端的有那些处置方法? 答:有以下三种处理方法:A:悬空。B:与其它 输入端并联:C:接固定高电平。 2、实验中所得ICCL和ICCH与单个门相差多少? 答:实验中所得数据是单个门参数的两倍。

一:实验目的

1、掌握TTL和CMOS与非门主要参数的意义及测 试方法 2、进一步熟悉数字逻辑实验箱的基本功能和使 用方法。

二:实验仪器及设备

1、数字逻辑实验箱DSB-3 1台 2、万用表 1只 3、元器件: 74LS20 CC4012 各一块 2CK11 4只 4、电阻、导线 若干

三、实验内容

1、 74LS20静态参数测试 2、 74LS20电压传输特性 3、 CC4012电压传输特性测试

1、 74LS20静态参数测试

导通电源电流Iccl和截止电源电流Icch以及 低电平输入电流Iil 和高电平输入电流Iih 。测 试电路如图2-1。注:74LS20为双与非门,两 个门的输入端作相同处理。

2、 74LS20电压传输特性测试

如图2-2所示,调节电位器RW,使Vi从 0V向5V变化,逐点测试Vi和VO值,并将结 果记录。以便画出实验数据曲线。

本次实验的内容结束。 请各位

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

项目处理--分析和综合(Analysis & Synthesis)

点击主工具栏上的 Synthesis”编译过程 按钮,开始“Analysis and

东南大学电工电子实验中心

分配管脚

Analysis and Synthesis全部通过后,为了把的设计 下载到实际电路中进行验证,还必须把设计项目的 输入输出端口和器件相应的引脚绑定在一起 有两种分配方法

周 期:50.3 ns 门延迟:5.38 ns 线延迟: 18 ns

东南大学电工电子实验中心

74LS04门延时测量(3个非门+示波器带宽限制)

带宽限制:20M

东南大学电工电子实验中心

示波器测量脉冲信号

脉冲信号看成是无穷多次个正弦谐波的叠加 占空比为50%理想TTL信号函数表示式为

f t ( ) 5 f (t ) 0 进行傅立叶展开后为

2 1.5 1 0.5 0

东南大学电工电子实验中心

74LS04灌电流特性

东南大学电工电子实验中心

74HC04拉电流特性

Y:5.0V

无负载

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

Y:5.0V

100K

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

Y:4.99V

200

Y:3.83V

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

100

Y:2.82V

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

R(Ω) 1000000 100000 10000 2000 1000 500 200 100

U(V) 5 5 4.99 4.89 4.77 4.52 3.83 2.82

数字逻辑设计实践

实验二

东南大学电工电子实验中心

教学目标

门电路的静态和动态特性 可编程数字系统设计

东南大学电工电子实验中心

数字逻辑器件

东南大学电工电子实验中心

门电路特性-TTL静态电压

2014/11/12

东南大学电工电子实验中心

4

门电路特性-噪声容限

2014/11/12

东南大学电工电子实验中心

5

演示实验1

采用示波器X-Y方式测量并比较74LS04和74HC04 两种器件的电压传输特性VO=f(Vi)

2014/11/12

东南大学电工电子实验中心

6

74LS04传输特性曲线

东南大学电工电子实验中心

74LS04传输特性曲线

X:295mV Y:4.48V

X:1.15V Y:124mV

东南大学电工电子实验中心

东南大学电工电子实验中心

74HC04静态电压

东南大学电工电子实验中心

器件互连-电压匹配

VOH min VOL max

VIH min VIL max

2014/11/12

东南大学电工电子实验中心

14

常用电压标准

东南大学电工电子实验中心

常用电压标准

5 TTL 5 TTL 5 CMOS 3 LVTTL 2.5 CMOS 1.8 CMOS Yes Yes Yes Yes No

Y:394mV

东南大学电工电子实验中心

74HC04灌电流特性

Y:5.0V

200

Y:979mV

东南大学电工电子实验中心

74HC04灌电流特性

Y:5.0V

100

Y:1.92V

东南大学电工电子实验中心

74HC04灌电流特性

R(Ω) 1000000 100000 10000 2000 1000 500 200 100

Y ( DCBA) m(0,1,2,5,8,10,12,13)

降维

东南大学电工电子实验中心

项目处理--分析和综合(Analysis & Synthesis)

分析(Analysis )

检查工程的逻辑完整性和一致性,并检查边界连接和语 法错误

综合(Synthesis)

在设计实体或工程文件的逻辑上进行综合和技术映射, 综合器可以从Verilog HDL和VHDL中推断触发器、锁 存器和状态机 为状态机建立状态分配,并作出能减少所用资源的选择 使用多种算法来减少门的数量,删除冗余逻辑协助实施 工程时序要求 优化设计以尽可能有效地利用器件体系结构

东南大学电工电子实验中心

74HC04灌电流特性

Y:5.0V

10K

Y:33.8mV

东南大学电工电子实验中心

74HC04灌电流特性

Y:5.0V

2K

Y:101mV

东南大学电工电子实验中心

74HC04灌电流特性

Y:5.0V

1K

Y:180mV

东南大学电工电子实验中心

74HC04灌电流特性

Y:5.0V

500

一种是给引脚分配信号 一种是给信号分配管脚

东南大学电工电子实验中心

分配管脚

信号 Y D C B A

东南大学电工电子实验中心

管脚 110 111 112 113 114

适配、编程和配置、时序分析

Y:1.85V

东南大学电工电子实验中心

74LS04灌电流特性

R(Ω) 1000000 100000 10000 2000 1000 500 200 100

U(V) 0 0.146 0.169 0.225 0.258 0.326 0.551 1.85

I(mA) 0.0 0.0 0.5 2.4 4.7 9.3 22.2 31.5

U(V) 0 0.011 0.0338 0.101 0.18 0.394 0.979 1.92

I(mA) 0.00 0.05 0.49 2.41 4.61 8.04 15.40 30.80

2.5 2 1.5 1 0.5 0

东南大学电工电子实验中心

74HC04灌电流特性

东南大学电工电子实验中心

器件互连-电流匹配

IOH max IOL max

I IH max I IL max

2014/11/12

东南大学电工电子实验中心

59

数字电路门延时

门的内部电路中

晶体管从导通变为截止或从截止变为导通都需要一定的时间 存在晶体管以及电阻、连接线等的寄生电容

理想的矩形波电压信号经过门电路后

输出电压波形要比输入信号滞后 波形的上升沿和下降沿也变坏, 上升沿延迟时间tPLH略大于下降沿延迟时间tPHL 如果忽略它们之间的差别,可用平均传输延迟时间tPd来表示 这个参数由于涉及的因素比较多,不易准确计算,所以都是通过 实验方法来测定或通过器件手册查到的

T 0t 2 T t T 2

5 45 1 1 1 f (t ) (sin t sin 3t sin 5t sin 7t ) 2 3 5 7 2

东南大学电工电子实验中心

T

示波器测量脉冲信号

基波幅度10%以上的谐波,是对波形形状影响较大 的分量,在分析的时候必须考虑, 基波幅度10%以下的谐波分量则可以忽略不计 占空比为50%的脉冲信号至少要考虑到9次谐波

U(V) 4.48 4.13 3.57 3.47 3.39 3.29 2.89 2.3

I(mA) 0.0 0.0 0.4 1.7 3.4 6.6 14.5 23.0

5 4 3 2 1 0 0.0 0.0 0.4 1.7 3.4 6.6 14.5 23.0

东南大学电工电子实验中心

74LS04拉电流特性

10K

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

Y:4.89V

2K

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

Y:4.77V

1K

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

Y:4.52V

500

Y:11.3mV

东南大学电工电子实验中心

74HC04拉电流特性

东南大学电工电子实验中心

74LS04门延时测量(5个非门+示波器带宽限制)

带宽限制:20M

东南大学电工电子实验中心

数字逻辑电路发展趋势

东南大学电工电子实验中心

数字逻辑电路发展趋势

东南大学电工电子实验中心

可编程数字逻辑器件

一种大规模的集成电路 内部预置了大量易于实现各种逻辑函数的结构 同时还有一些用来保持信息或控制连接的特殊结构 这些保持的信息或连接确定了器件实现的实际逻辑 功能 当改变这些信息或连接时器件的功能也将随之改变 利用软件工具来进行设计。

东南大学电工电子实验中心

74LS04灌电流特性

测试电路

东南大学电工电子实验中心

74LS04灌电流特性

Y:4.97V

100K

Y:146mV

东南大学电工电子实验中心

74LS04灌电流特性

Y:4.99V

10K

Y:169mV

东南大学电工电子实验中心

74LS04灌电流特性

Y:5.0V

2K

Y:225mV

东南大学电工电子实验中心

74LS04灌电流特性

Y:5.0V

1K

Y:258mV

东南大学电工电子实验中心

74LS04灌电流特性

Y:5.0V

500

Y:326mV

东南大学电工电子实验中心

74LS04灌电流特性

Y:5.0V

200

Y:551mV

东南大学电工电子实验中心

74LS04灌电流特性