三种片上总线的分析与比较

简述对计算机系统总线的理解

计算机系统总线是连接计算机内部各个部件的公共通道,也称为系统总线或主板总线。

它负责传输数据、地址和控制信号,是计算机系统中非常关键的部分之一。

计算机系统总线通常包含三种类型的线路:数据总线、地址总线和控制总线。

其中,数据总线用于传输数据,地址总线用于传输内存地址和I/O设备地址,控制总线用于传输控制信号,例如读写命令、中断请求等。

计算机系统总线的速度和带宽决定了计算机系统的性能。

随着计算机硬件的不断升级和更新,计算机系统总线的速度和带宽也在不断提升。

目前,计算机系统总线的标准包括PCI、AGP、USB、SATA、Ethernet等,它们分别用于不同类型的接口和设备。

除了速度和带宽之外,计算机系统总线还需要具备可靠性、兼容性和扩展性等特点。

因此,计算机系统总线的设计和开发需要综合考虑各种因素,以满足不同用户和应用场景的需求。

AMBA_总线_介绍

SEP3203

2

目录

AMBA总线概述 AHB APB 不同IP之间的互连

3

系统总线简介

系统芯片中各个模块之间需要有接口来连接 总线作为子系统之间共享的通信链路 优点

低成本 方便易用

缺点

会造成性能瓶颈

4

AMBA介绍

Advanced Microcontroller Bus Architecture

end case;

Default_Slave logic

case HTRANS is when IDLE|BUSY => HRESP <= OKAY; when others => HRESP <= ERROR;

end case;

18

AHB信号

19

基本AHB信号

HRESETn

低电平有效

HADDR[31:0]

▪ HADDR must be aligned to a multiple of data size as given by HSIZE

32

BURST传输

AHB Burst 操作

4beat、8beat、16beat、单个字节传输、未定义长度 的传输 支持incrementing和wrapping两种burst传输

AMBA 3.0

AMBA Advanced eXtensible Interface (AXI)

6

一个典型的AMBA系统

处理器和其它主设备/从设备都是可以替换的

7

AHB

高速总线,高性能 流水线操作 可支持多个总线主设备(最多16个) 支持burst传输 总线带宽:8、16、32、64、128bits 上升沿触发操作 对于一个新设计建议使用AHB

英飞凌tricore用户手册 第4章 片上总线和总线桥

数据总线信息 • LMB错误属性寄存器(LEATT)保存总线错误事件的状态信息

4.2.4 忙碌从设备对传送请求的响应 若LMB从设备在接收到LMB传送请求时正忙,它会延迟执行LMB传送。LMB主设

备在发出传送请求之后释放LMB一个时钟周期,从而允许LMB从设备指示自身是否做 好处理LMB传送的准备。 注:对于LMB缺省主设备,一个时钟周期的间隙不会导致性能下降,因为若没有其它

用户手册 总线,V1.9

4-1

V1.0,2011-12

TC1728

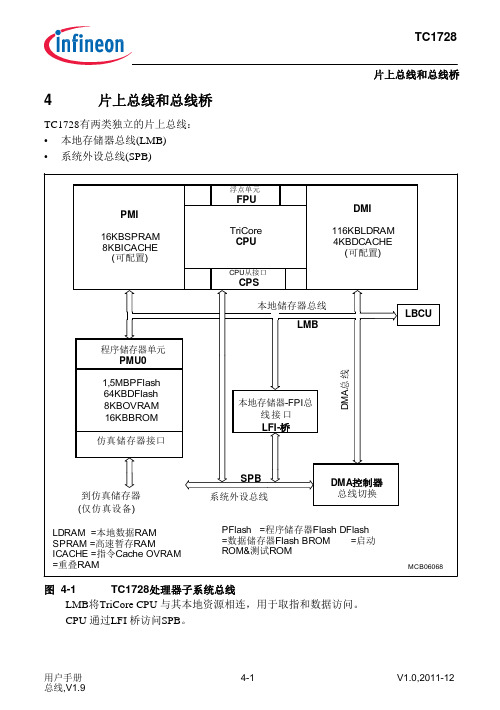

4.1

更新

AudoFuture在片上总线系统结构上和AudoNG的不同:

片上总线和总线桥

• TC1728基于两个片上总线(LMB, SPB)。远程外设总线(RPB)被拆除。

• DMA另外连接到主接口的LMB总线。

• E-Ray模块通过从接口另外连接到SPB。

片上总线和总线桥

4.3.1 基本操作

LBCU 用于控制(由主设备请求的)LMB传送的周期序列。LBCU 还能够检测总线 错误以及对未实现地址的寻址。总线出错时,LBCU 会将总线地址、总线数据和总线状 态信息等所有相关数据捕获到寄存器中,以便软件进行分析。

4.3.2 LMB总线仲裁

所有请求LMB传送的主设备将参与仲裁。在每个总线周期首先进行仲裁。每个LMB主设 备的优先级固定,如表4-2所示。

说明

偏移地址 访问模式 读写

保留 LBCU 模块ID寄存器

片上通信结构——共享总线和NoC的分析与比较

c mmu iain a c ie tr . mp tr En i e ig a p iain , 0 7, 3 1 : 2 —1 4 o nc t r htcu eCo u e gnern nd Ap l to s 2 0 4 ( 5) 1 1 2 . o c

Ab ta t T e a e n lz s o c mmo f au e o h s a e b s i c n r l e a b t t n n t d me so a No sr c : h p p r a ay e s me o n e tr s f t e h r d u w t e t i d r i ai a d wo i n in l h az r o C t ru h a mo u a t o . i t h wo o h o g d lr me h d F r te t c mmu i ain r h t cu e ae d s r e t h y t e i d Vei g ln u g a d t o s n c t a c i tr s r e c b d wi t e s n h sz r o a g a e, n w o e i h e l f n t n v r c t n a d c ce a c r t ef r n e a ay i n io me t a e as mp e n e o e au t h i p r r a c . h u c i e f ai n y l c u ae p r ma c n lss e v rn n s r l i l me td t v l ae e r e o o i t o o o t f m n eT e e p rme t r s l h ws t e s a e u s c n i e a l mal r i r a t a C fr t e s me tc n lg b t t e t r u h u f xe i n e u t o h h r d b s i o s r by s l n a e h n No o h a e h oo y, u h h o g p t e- s d e i e c n a d d h o o b iu l up r r h h r d b s f a g — c l n c i o f in v a d b n wit f N C o vo sy o t e o s t e s a e u r lr e s a e o — h p c mmu iai n c fm o nc t . o

微型计算机的总线技术原理分析

2021/4/21

20

(6)USB传输线能够提供100mA的电流,而带电源的USB Hub使得每个接口可以提供500 mA的电流。

(7)USB V1.1规范提供全速12Mbps的模式和低速1.5Mbps 的模式,USB V2.0规范提供高达480Mbps的数据传输速 率,可以适应各种不同类型的外设。

8位ISA总线是一种开放式的结构总线,在总线母板上有8个系 统插槽,用于I/O设备和PC机的连接。由于8位ISA总线具有价格 低、可靠性好、使用灵活等特点,并且对插板兼容性好。

8位ISA总线引脚信号总共有62条。通过一个31脚分为A、B两 面的连接插槽来实现,其中,A面为元件面,B面为焊接面。符 合ISA总线标准的接插件可以方便的插入,以便对微型计算机 系统进行功能扩展。

16位ISA总线的前62引脚的信号分布及其功能与8位ISA总线基 本相同,仅有两处作了改动。

16位ISA总线中新增加的36引脚插槽信号扩展了8位数据线、7 位地址线、存储器和I/O设备的读写控制线、中断和DMA控制线 、电源和地线等。

新插槽中的引脚信号分为C(元件面)和D(焊接面)两列。

2021/4/21

2021/4/21

13

4.3 局部总线

4.3.1 VESA总线

VESA(Video Electronics Standards Association 视频电 子标准协会)总线是一种32位接口的局部总线,通 常称为VL总线。

由于EISA总线工作频率是8MHz,而VESA局部总线工 作频率可以达到33MHz。因此,需要高速数据传输 的系统可以采用VESA局部总线。它通常用于视频和 磁盘到基于80486的PC机的接口。

PCI V2.0版本支持32/64位数据总线,总线时钟为25~ 33MHz,数据传输率达132~264MB/s。1995年推出的PCI V2.1版本支持64位数据总线,总线速度为66MHz,最大 数据传输率达528MB/s。这个速度是最初的IBM PC总线的 100倍,是最快的ISA总线的40倍。PCI总线的优良性能使 它成为当前Pentium系列芯片的最佳选择,现在所有 Pentium主板都使用了PCI V2.1和更新版的PCI总线。

FPGA_ASIC-嵌入式SoC总线分析与研究

嵌入式SoC总线分析与研究马秦生,魏翠,孙力军,秦鸣,曹阳武汉大学电子信息学院,湖北武汉 430079摘要:本文主要介绍和分析了在集成芯片设计中几种常用的片上系统总线-CoreConnect总线、AMBA总线、Wishbone总线和OCP总线,通过比较这些总线的特性及适用范围,展望了它们的发展前景。

关键词:IP SoC 片上总线The Analyse And Research of embeded SoC BusAbstract:In this paper, the OCB of CoreConnect, AMBA(Advanced Microcontroller Bus Architecture), Wishbone, OCP(Open Core Protocol) are mainly introduced and analyzed. By comparing the characteristic and the applied scope of these SoC bus, the paper views the foreground of the SoC bus mentioned above.Key words: IP SoC OCB(On-Chip Bus)1.引言随着深亚微米工艺制造技术的发展,集成电路芯片的规模越来越大,目前,在单一IC 芯片中已经允许包含数亿个晶体管。

与此同时,IC的设计方法也从基于时序驱动的方式,发展到了基于IP复用的方式,这种基于IP复用的设计方法已经在SoC设计中得到了广泛应用。

基于IP复用的设计方法的关键是建立片上总线(OCB,on-chip bus),片上总线除了必须具有正确、高效和灵活的特点外,还必须具有可复用性。

这样,就可以实现IP芯核的可移植性和IP设计的可复用性,就可以充分地利用公共外设核处理器,就可以提高从公共设计平台创建产品的定制化能力。

因此,实现OCB的标准化是十分必要的。

CSMA令牌环令牌总线比较

CSMA令牌环令牌总线⽐较CSMA/CD,令牌环,令牌总线1.CSMA/CDCSMA全拼为Carrier Sense Multiple Access(载波侦听多路访问),是⼯作在OSI参考模型的数据链路层的介质访问控制⼦层。

是⼀种抢占型的半双⼯介质访问控制协议,采⽤分布式控制⽅法。

其中:载波侦听(Carrier Sense,CS)指任何连接到介质的设备在欲发送帧前,必须对介质进⾏侦听,当确认其空闲时,才可以发送。

多路访问(Multiple Access,MA)指多个设备可以同时访问介质,⼀个设备发送的帧也可以被多个设备接收。

根据发⽣冲突时的解决策略,CSMA可分为CSMA/BA, CSMA/CA,CSMA/CD,CSMA/CP四种,其中CSMA/CD是最为常见的⼀种,CSMA/CD 在发送时检测冲突,并采取适当措施进⾏补救。

CSMA/CD是⼴泛⽤于总线或树形局部⽹络的⼀种访问协议。

在基带系统中, 最早采⽤这种访问协议的是著名的原型以太⽹( 1976年) , 最早采⽤此类访问协议的宽带系统是MITERNET (1979年) 。

其基本思想起源于ALOHA系统,ALOHA⽅式具体可分为纯ALOHA和时间⽚ALOHA两种形式, 最⼤吞吐量分别只有18.4%和39.8%。

造成ALOHA⽅式信道效率低的根本原因是节点的发送意图与信道状态⽆关。

为克服此弱点, CSMA/CD⽅式应运⽽⽣, 其主要改进是增添了“讲前先听”的功能。

它具体可分为三种形式1.断续监听式2.1-持续监听式和3.P-持续监听式。

断续监听式CSMA遵守如下规则。

( 1 ) 若信道闲, 发送节点可发送信包, ( 2 ) 若信道忙,则后退⼀随机时间⽚, 然后再次监听信道, 并重复以上算法。

对于1-持续式CSMA , 发送节点遵守下列规则:< 1 >若信道闲, 则以概1发送信包, < 2 >若信道忙, 则持续监听信道, 直到信道由忙变闲为⽌, 然后以概率1发送。

Wishbone标准

本文详细介绍了Wishbone标准,主要参考了Wishbone标准版本的核心内容,感兴趣的读者可去下载英文原文。

一、片上总线技术综述随着超大规模集成电路的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管。

如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和外设等数块芯片实现的功能集成起来,由单片集成电路构成功能强大的、完整的系统,这就是我们通常所说的片上系统。

IP复用是片上系统时代的核心技术之一。

由于IP核的设计千差万别,它们要能够直接连接,就要遵守相同的接口标准。

在片上系统中,处理器核和所有外设通过共享总线互通互联,因此这些IP核必须遵守相同的总线规范。

总线规范定义的是IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP核的功能和接口如何实现。

一个片上总线规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系。

芯片与电路板的资源和环境的不同,导致片上总线与板上总线存在若干明显差异,包括:①片上总线多采用单向信号线,而板上总线多采用三态信号。

片上三态总线无论在功耗、速度、可测性上都存在很大缺陷,而且一旦出现多驱动情况便会损毁芯片(比如若应该输出"Z"的信号实际输出为"1",而另有一个信号输出为"0",就形成一个低电阻通路,导致局部电流过大,热量难以及时释放,从而增加芯片功耗和大大降低芯片寿命)。

由于片上布线资源较为丰富,因此片上总线多采用单向信号线。

由于电路板上布线资源较为昂贵,因此板上总线多采用三态总线,但是由于三态总线的功耗问题和速度限制,目前板上总线也在向串行和非三态方向发展,如USB和PCI Express。

②片上总线比板上总线更加简单灵活。

首先片上总线结构要简单,这样可以占用较少的逻辑单元;其次时序要简单,以利于提高总线的速度;第三接口要简单,如此可减少与IP核连接的复杂度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

三种常用SoC片上总线的分析与比较作者:李瑞张春元罗莉来源:国防科技大学发表时间:2006-02-22内容摘要随着集成电路设计技术的发展,在片上系统(SoC)中,越来越多地使用各种功能IP核部件构成系统。

总线是这些部件连接的主要方式,目前有数家公司和组织研发了多种面向SoC设计的总线系统。

本文介绍SoC中常用的三种片上总线AMBA、Wishbone和Avalon,分析和比较其特性,并针对其不同的特点阐述其使用范围。

引言 嵌入式系统是当今计算机工业发展的一个热点。

随着超大规模集成电路的迅速发展,半导体工业进入深亚微米时代,器件特征尺寸越来越小,芯片规模越来越大,可以在单芯片上集成上百万到数亿只晶体管。

如此密集的集成度使我们现在能够在一小块芯片上把以前由CPU和若干I/O接口等数块芯片实现的功能集成起来,由单片集成电路构成功能强大的、完整的系统,这就是我们通常所说的片上系统SoC (System on Chip)。

由于功能完整,SoC逐渐成为嵌入式系统发展的主流。

相比板上系统,具有许多优点:SoC ①充分利用IP技术,减少产品设计复杂性和开发成本,缩短产品开发的时间; ②单芯片集成电路可以有效地降低系统功耗; ③减少芯片对外引脚数,简化系统加工的复杂性; ④减少外围驱动接口单元及电路板之间的信号传递,加快了数据传输和处理的速度; ⑤内嵌的线路可以减少甚至避免电路板信号传送时所造成的系统信号串扰。

SoC的设计过程中,最具特色的是IP复用技术。

即选择所需功能的IP(给出IP定义)核,集成到一个芯片中用。

由于IP核的设计千差万别,IP核的连接就成为构造SoC的关键。

片上总线(On-Chip Bus,OCB)是实现SoC中IP核连接最常见的技术手段,它以总线方式实现IP核之间数据通信。

与板上总线不同,片上总线不用驱动底板上的信号和连接器,使用更简单,速度更快。

一个片上总线规范一般需要定义各个模块之间初始化、仲裁、请求传输、响应、发送接收等过程中驱动、时序、策略等关系。

由于片上总线与板上总线应用范围不同,存在着较大的差异,其主要特点如下: ①片上总线要尽可能简单。

首先结构要简单,这样可以占用较少的逻辑单元;其次时序要简单,以利于提高总线的速度;第三接口要简单,如此可减少与IP核连接的复杂度。

②片上总线有较大的灵活性。

由于片上系统应用广泛,不同的应用对总线的要求各异,因此片上总线具有较大的灵活性。

其一,多数片上总线的数据和地址宽度都可变,如AMBA AHB支持32位~128位数据总线宽度;其二,部分片上总线的互连结构可变,如Wishbone总线支持点到点、数据流、共享总线和交叉开关四种互连方式;其三,部分片上总线的仲裁机制灵活可变,如Wishbone总线的仲裁机制可以完全由用户定制。

③片上总线要尽可能降低功耗。

因此,在实际应用时,总线上各种信号尽量保持不变,并且多采用单向信号线,降低了功耗,同时也简化了时序。

上述三种片上总线输入数据线和输出数据线都是分开的,且都没有信号复用现象。

片上总线有两种实现方案,一是选用国际上公开通用的总线结构;二是根据特定领域自主开发片上总线。

本文就目前SoC上使用较多的三种片上总线标准——ARM的AMBA、Silicore的Wishbone和Altera的Avalon进行讨论,对三者特性进行分析和比较。

1 AMBA总线 (Advanced Microcontroller Bus Architecture)总线规范是ARM公司设计的一种用于AMBA高性能嵌入式系统的总线标准。

它独立于处理器和制造工艺技术,增强了各种应用中的外设和系统宏单元的可重用性。

AMBA总线规范是一个开放标准,可免费从ARM获得。

目前,AMBA 拥有众多第三方支持,被ARM公司90%以上的合作伙伴采用,在基于ARM处理器内核的SoC设计中,已经成为广泛支持的现有互联标准之一。

AMBA总线规范2.0于1999年发布,该规范引入的先进高性能总线(AHB)是现阶段AMBA实现的主要形式。

AHB的关键是对接口和互连均进行定义,目的是在任何工艺条件下实现接口和互连的最大带宽。

AHB接口已与互连功能分离,不再仅仅是一种总线,而是一种带有接口模块的互连体系。

总线规范主要设计目的如下:①满足具有一个或多个CPU或DSP的嵌入式系统产品的快速AMBA开发要求;②增加设计技术上的独立性,确保可重用的多种IP核可以成功地移植到不同的系统中,适合全定制、标准单元和门阵列等技术;③促进系统模块化设计,以增加处理器的独立性;④减少对底层硅的需求,以使片外的操作和测试通信更加有效。

AMBA 总线是一个多总线系统。

规范定义了三种可以组合使用的不同类型的总线:AHB(Advanced High-performance Bus)、ASB(Advanced System Bus)和APB(Advanced Peripheral Bus)。

典型的基于AMBA的SoC核心部分如图1所示。

其中高性能系统总线(AHB或ASB)主要用以满足CPU和存储器之间的带宽要求。

CPU、片内存储器和DMA设备等高速设备连接在其上,而系统的大部分低速外部设备则连接在低带宽总线APB上。

系统总线和外设总线之间用一个桥接器(AHB/ASB-APB-Bridge)进行连接。

的AHB适用于高性能和高时钟频率的系统模块。

它作为高性能系统的骨干总线,主要用于连AMBA接高性能和高吞吐量设备之间的连接,如CPU、片上存储器、DMA设备和DSP或其它协处理器等。

其主要特性如下:◇支持多个总线主设备控制器;◇支持猝发、分裂、流水等数据传输方式;◇单周期总线主设备控制权转换;◇32~128位数据总线宽度;◇具有访问保护机制,以区分特权模式和非特权模式访问,指令和数据读取等;◇数据猝发传输最大为16段;◇地址空间32位;◇支持字节、半字和字传输。

的ASB适用于高性能的系统模块。

在不必要适用AHB的高速特性的场合,可选择ASB作AMBA为系统总线。

它同样支持处理器、片上存储器和片外处理器接口与低功耗外部宏单元之间的连接。

其主要特性与AHB类似,主要不同点是它读数据和写数据采用同一条双向数据总线。

的APB适用于低功耗的外部设备,它已经过优化,以减少功耗和对外设接口的复杂度;它可AMBA连接在两种系统总线上。

其主要特性如下:◇低速、低功耗外部总线;◇单个总线主设备控制器;◇非常简单,加上CLOCK和RESET,总共只有4个控制信号;◇32位地址空间;◇最大32位数据总线;◇读数据总线与写数据总线分开。

2 Wishbone总线 最先是由Silicore公司提出的,现在已被移交给OpenCores组织维护。

由于其开放性,Wishbone现在已有不少的用户群体,特别是一些免费的IP核,大多数都采用Wishbone标准。

总线规范是一种片上系统IP核互连体系结构。

它定义了一种IP核之间公共的逻辑接口,Wishbone减轻了系统组件集成的难度,提高了系统组件的可重用性、可靠性和可移植性,加快了产品市场化的速度。

Wishbone总线规范可用于软核、固核和硬核,对开发工具和目标硬件没有特殊要求,并且几乎兼容已有所有的综合工具,可以用多种硬件描述语言来实现。

总线规范的目的是作为一种IP核之间的通用接口,因此它定义了一套标准的信号和总线Wishbone周期,以连接不同的模块,而不是试图去规范IP核的功能和接口。

总线结构十分简单,它仅仅定义了一条高速总线。

在一个复杂的系统中,可以采用两条WishboneWishbone总线的多级总线结构:其一用于高性能系统部分,其二用于低速外设部分,两者之间需要一个接口。

这个接口虽然占用一些电路资源,但这比设计并连接两种不同的总线要简单多了。

用户可以按需要自定义Wishbone标准,如字节对齐方式和标志位(TAG)的含义等等,还可以加上一些其它的特性。

Wishbone的一种互连结构如图2所示。

灵活性是Wishbone总线的另一个优点。

由于IP核种类多样,其间并没有一种统一的间接方式。

为满足不同系统的需要,Wishbone总线提供了四种不同的IP核互连方式:◇点到点(point-to-point),用于两IP核直接互连;◇数据流(data flow),用于多个串行IP核之间的数据并发传输;◇共享总线(shared bus),多个IP核共享一条总线;◇交叉开关(crossbar switch)(图2),同时连接多个主从部件,提高系统吞吐量。

还有一种片外连接方式,可以连接到上面任何一种互连网络中。

比如说,两个有Wishbone接口的不同芯片之间就可以用点到点方式进行连接。

总线主要特征如下:Wishbone◆所有应用适用于同一种总线体系结构;◆是一种简单、紧凑的逻辑IP核硬件接口,只需很少的逻辑单元即可实现;◆时序非常简单;◆主/从结构的总线,支持多个总线主设备;◆ 8~64位数据总线(可扩充);◆单周期读写;◆支持所有常用的总线数据传输协议,如单字节读写周期、块传输周期、控制操作及其它的总线事务等;◆支持多种IP核互连网络,如单向总线、双向总线、基于多路互用的互连网络、基于三态的互连网络等;◆支持总线周期的正常结束、重试结束和错误结束;◆使用用户自定义标记(TAG),确定数据传输类型、中断向量等;◆仲裁器机制由用户自定义;◆独立于硬件技术(FPGA、ASIC、bipolar、MOS等)、IP核类型(软核、固核或硬核)、综合工具、布局和布线技术等。

3 Avalon总线 总线是Altera公司设计的用于SOPC(System On Programmable Chip,可编程片上Avalon系统)中,连接片上处理器和其它IP模块的一种简单的总线协议,规定了主部件和从部件之间进行连接的端口和通信的时序。

总线的主要设计目的如下:①简单性,提供一种非常易于理解的协议;②优化总线逻辑的Avalon资源使用率,将逻辑单元保存在PLD(Programmable Logic Device,可编程逻辑器件)中;③同步操作,将其它的逻辑单元很好地集成到同一PLD中,同时避免复杂的时序。

传统的总线结构中,一个中心仲裁器控制多个主设备和从设备之间的通信。

这种结构会产生一个瓶颈,因为任何时候只有一个主设备能访问系统总线。

Avalon总线的开关构造使用一种称之为从设备仲裁(Slave-side arbitration)的技术,允许多个主设备控制器真正地同步操作。

当有多个主设备访问同一个从设备时,从设备仲裁器将决定哪个主设备获得访问权。

图3是一个多主设备同时访问存储器的例子。

在此系统中,高带宽外设,如100M以太网卡,可以不需暂停CPU而直接访问存储器。