集成电路标准精选(最新)

集成电路类检验标准

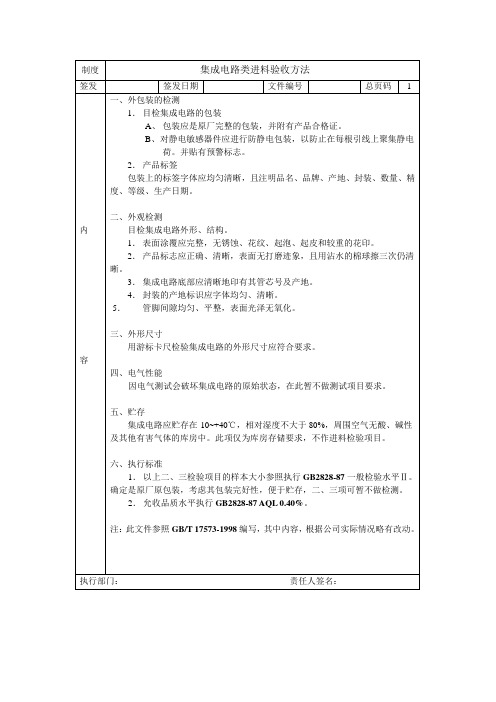

集成电路类进料验收方法

签发

签发日期

文件编号

总页码

1

内

容

一、外包装的检测

1.目检集成电路的包装

A、包装应是原厂完整的包装,并附有产品合格证。

B、对静电敏感器件应进行防静电包装,以防止在每根引线上聚集静电

荷。并贴有预警标志。

2.产品标签

包装上的标签字体应均匀清晰,且注明品名、品牌、产地、封装、数量、精

三、外形尺寸

用游标卡尺检验集成电路的外形尺寸应符合要求。

四、电气性能

因电气测试会破坏集成电路的原始状态,在此暂不做测试项目要求。

五、贮存

集成电路应贮存在-10~+40℃,相对湿度不大于80%,周围空气无酸、碱性

及其他有害气体的库房中。此项仅为库房存储要求,不作进料检验项目。

六、执行标准

1.以上二、三检验项目的样本大小参照执行GB2828-87一般检验水平Ⅱ。

确定是原厂原包装,考虑其包装完好性,便于贮存,二、三项可暂不做检测。

2.允收品质水平执行GB2828-87 AQL 0.40%。

注:此文件参照GB/T 17573-1998编写,其中内容,根据公司实际情况略有改动。

执行部门:责任人签名:

度、等级、生产日期。

二、外观检测

目检集成电路外形、结构。

1.表面涂覆应完整,无锈蚀、ห้องสมุดไป่ตู้纹、起泡、起皮和较重的花印。

2.产品标志应正确、清晰,表面无打磨迹象,且用沾水的棉球擦三次仍清

晰。

3.集成电路底部应清晰地印有其管芯号及产地。

4.封装的产地标识应字体均匀、清晰。

5.管脚间隙均匀、平整,表面光泽无氧化。

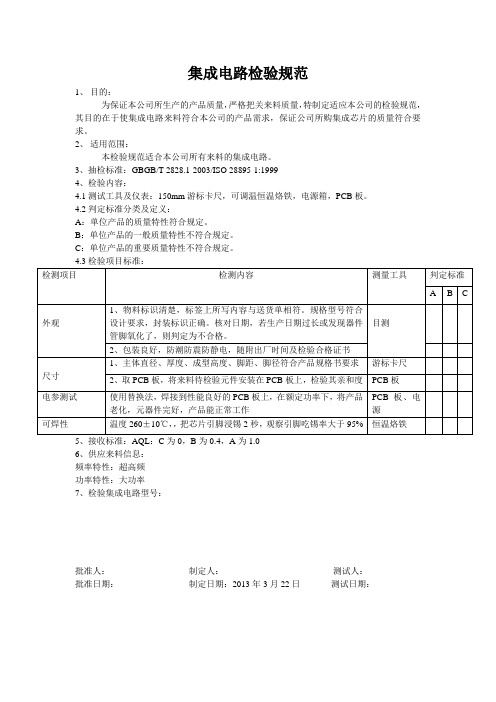

集成电路检验规范

集成电路检验规范

1、目的:

为保证本公司所生产的产品质量,严格把关来料质量,特制定适应本公司的检验规范,其目的在于使集成电路来料符合本公司的产品需求,保证公司所购集成芯片的质量符合要求。

2、适用范围:

本检验规范适合本公司所有来料的集成电路。

3、抽检标准:GBGB/T 2828.1-2003/ISO 28895-1:1999

4、检验内容:

4.1测试工具及仪表:150mm游标卡尺,可调温恒温烙铁,电源箱,PCB板。

4.2判定标准分类及定义:

A:单位产品的质量特性符合规定。

B:单位产品的一般质量特性不符合规定。

C:单位产品的重要质量特性不符合规定。

5、接收标准:AQL:C为0,B为0.4,A为1.0

6、供应来料信息:

频率特性:超高频

功率特性:大功率

7、检验集成电路型号:

批准人:制定人:测试人:

批准日期:制定日期:2013年3月22日测试日期:。

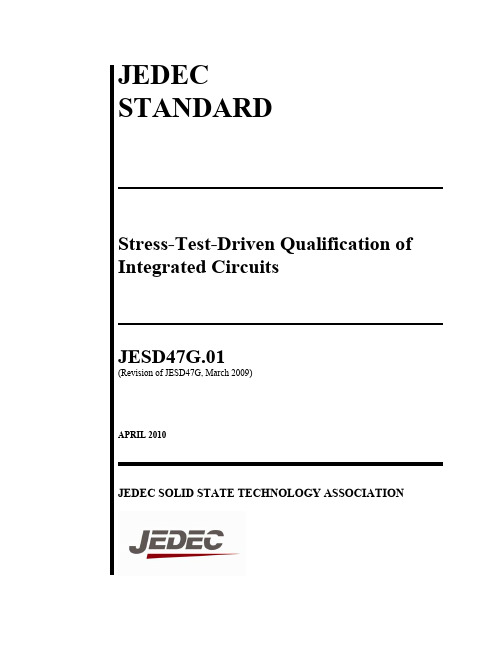

集成电路测试标准

Stress-Test-Driven Qualification of Integrated Circuits

JESD47G.01

(Revision of JESD47G, March 2009)

APRIL 2010

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

PLEASE! DON’T VIOLATE THE LAW!

This document is copyrighted by JEDEC and may not be reproduced without permission. Organizations may obtain permission to reproduce a limited number of copies through entering into a license agreement. For information, contact:

NOTICE JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel. JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally. JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications. The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard. No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met. Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or call (703) 907-7559 or Published by ©JEDEC Solid State Technology Association 2010 3103 North 10th Street, Suite 240 South Arlington, VA 22201 This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material. PRICE: Please refer to the current Catalog of JEDEC Engineering Standards and Publications online at /Catalog/catalog.cfm Printed in the U.S.A. All rights reserved

集成电路技术专业标准

集成电路技术专业标准集成电路技术专业标准主要涵盖以下七个方面。

1.职业概况集成电路技术专业涉及的职业名称为集成电路工程技术人员,职业编码为2020906。

从事集成电路需求分析、集成电路架构设计、集成电路详细设计、测试验证、网表设计和版图设计的工程技术人员。

2.专业技术等级本职业共设三个等级,分别为初级、中级、高级。

初级、中级、高级均设三个职业方向:集成电路设计、集成电路工艺实现和集成电路封测。

3.职业能力特征集成电路工程技术人员需要具备较强的学习、分析、计算、表达、推理、判断能力。

4.普通受教育程度从事集成电路技术专业的技术人员需具备大学专科学历(或高等职业学校毕业)。

5.职业培训要求集成电路工程技术人员需按照国家职业技术技能标准参加有关课程培训,完成规定学时,取得学时证明。

初级需完成128标准学时,中级需完成128标准学时,高级需完成256标准学时。

6.主要课程集成电路技术专业的主要课程包括电路基础、模拟电子技术、数字电子技术、单片机与接口技术、电路分析与测试、模拟电子技术、数字电子技术、C语言程序设计、P CB设计等。

7.实践能力要求集成电路技术专业的毕业生需要具备以下实践能力:具有应用专业信息技术的能力。

具有集成电路芯片逻辑提取和辅助设计的能力。

具有集成电路版图设计和版图验证的能力。

具有集成电路应用开发的能力。

具有FPGA开发及应用的能力。

具有在集成电路晶圆制造过程中解决实际工艺问题的能力。

具有在集成电路封装、测试生产中解决实际问题的能力。

具有依照国家法律、行业规范开展绿色生产、安全生产、质量管理等的能力。

这些专业标准为集成电路技术专业的人才培养提供了指导,有助于培养具备实践能力和创新精神的高素质技术技能人才。

ic集成电路)检验标准

√

2、封装样式符合承认书及样板。

√

包装

1、根据来料单据及承认书核对来料包装方式、数量,确认来料标示清楚、完整。

来料单据、承认书、目视

√

2、不可有短装、混料、包装脏污等不良现象。

√

3、针对散装物料要求包装完好,防静电,真空包装需完好,无破损、漏气不良。

√

可焊性

在炉温250±5℃状态下将稳压二极管引脚浸入锡炉2±0.5S观察引脚上锡率>95%。

检验项目

检验内容

检验方法及工具

判定标准

CR

MA

MI

外观

1、表面字符丝印清晰、完整,易于识别,丝印无模糊、错误丝印、漏丝印、重影不良。

目视、放大镜

√

2、无变形、严重划伤、缺料,无表面污渍现象。

√

3、元件脚无连脚丶脱落、氧化现象。

√

4、元件脚在同一平面,无变形、偏位。

√

结构

1、按照承认书标注尺寸要求,进行尺寸检查。

锡炉

√

备注:1.拿取时需戴手套;

2.可焊性按每批次10PCS抽取。

IC(集成电路)检验标准

文件编号

BC-QM-015

生效日期

批准

审核

拟制

版本/修订号

A.0

制订部门

品质部

1.0目的:为使IC(集成电路)来料符合本厂之产品要求,特制定检验成电路)检验.

3.0检验环境:在正常光源下,距30CM远,以45°视角观看产品。

4.0检验标准:GB/T2828.1-2012正常检验一次抽样方案,一般检验水平Ⅱ级,特殊检验水平S-3之AQL值CR=0,MA=0.65,MI=1.5进行抽样检查。

集成电路的分类标准

集成电路的分类标准

集成电路可以按照不同的分类标准进行分类,主要的分类标准包括以下几种:

1. 按照集成度分类:分为小规模集成电路(SSI)、中规模集

成电路(MSI)、大规模集成电路(LSI)和超大规模集成电

路(VLSI)四种,其中小规模集成电路包含的器件数量最少,超大规模集成电路包含的器件数量最多。

2. 按照工作原理分类:分为数模混合电路、模拟电路和数字电路三种。

3. 按照功能分类:分为通用型集成电路和特定功能集成电路两种,通用型集成电路可以被广泛应用,而特定功能集成电路则只能完成特定的功能。

4. 按照应用领域分类:分为通信、计算机、汽车电子、工业控制、医疗设备等不同领域,每个领域都具有不同的需求和应用范畴。

5. 按照制造工艺分类:分为Bipolar、MOS、BiCMOS、DMOS、CMOS等不同的制造工艺。

以上是常见的五种分类标准,不同的分类标准可以为我们提供不同的视角来了解集成电路的产生和发展。

集成电路的质量标准及检验方法

集成电路的质量标准及检验方法集成电路(Integrated Circuit,简称IC)是由数百个或数千个微弱的电子元件(如二极管、晶体管、电阻等)和配套的被联系在一起的导线、测量电流、电压等元器件构成的微电子器件。

IC的质量标准及检验方法对于保证产品的质量与性能至关重要。

下面将详细介绍IC的质量标准及检验方法。

首先,IC的质量标准应包含以下几个方面:1. 尺寸标准:对于IC的外观尺寸、引脚位置、引脚间距等进行明确的规定。

2. 电气性能标准:包括电气参数、工作电压范围、功耗等。

3. 可靠性标准:要求IC在规定的环境条件下具有良好的耐用性,包括温度、湿度、抗辐射等。

4. 效率标准:IC应具有较高的性能效率,包括信号放大倍数、功耗效率等。

5. 一致性标准:IC的生产批次之间的差异应控制在一定的范围内,以保证产品的一致性。

接下来,IC的检验方法主要包括以下几个方面:1. 外观检验:通过目测或显微镜观察IC的外观,检查是否有划痕、裂纹、焊接不良等表面缺陷。

2. 引脚间距检验:使用千分尺或显微镜测量IC引脚之间的间距是否符合规范要求。

3. 电性能检验:使用特定的测试仪器,通过量测IC在不同电压下的电流、电压等参数来判断IC的电性能是否符合标准要求。

4. 可靠性检验:将IC置于不同的环境条件下,例如高温、低温、高湿度等,观察其性能是否受到影响以及是否满足可靠性要求。

5. 一致性检验:通过对生产批次中的多个IC进行抽样测试,对比其性能参数,判断是否在规定的一致性范围内。

6. 功能检验:根据IC所设计的功能,通过电路连接和信号输入,观察IC的功能是否正常。

总结:IC作为重要的电子元件,其质量标准及检验方法直接关系到电子产品的品质与性能。

通过明确的质量标准,可以确保IC 在制造过程中符合规范要求;通过有效的检验方法,可以及时发现IC的缺陷,并采取相应措施进行修正或淘汰。

因此,合理制定和实施IC的质量标准及检验方法是保证IC产品质量的重要保证。

集成电路的设计流程和验收标准

集成电路的设计流程和验收标准集成电路设计流程:1. 概述集成电路设计的重要性和流程的目的- 集成电路设计是将电路和器件功能集成在一个芯片上的过程。

设计流程旨在确保设计准确性和功能性,并满足用户需求。

2. 需求分析和规格制定- 确定设计的目标和约束条件,如性能要求、功耗限制、电路布局要求等。

3. 概念设计- 设计团队根据需求和规格制定,提出多种可能的设计方案,并评估每个方案的优缺点。

4. 详细设计- 选定最佳的概念设计方案后,进行详细的电路设计和电子元件选择。

设计团队使用EDA(电子设计自动化)工具,如仿真软件和布局工具,对电路进行仿真和布局。

5. 电路验证和优化- 通过仿真软件对电路进行验证,确保其满足设计规格和性能要求。

如果发现问题,团队将进行优化和修改。

6. 物理设计和版图绘制- 使用专业工具进行物理设计和版图绘制。

该阶段将确定芯片的尺寸、焊盘布局、连线等。

7. 设计规则检查(DRC)- 使用DRC工具对设计的物理布局进行检查,以确保符合工艺制造规范。

8. 电气规则检查(ERC)- 使用ERC工具对设计进行电气规则检查,以确保电路设计符合电路标准和安全要求。

9. 设计数据准备和提交- 准备设计文件和工艺文件,并提交给制造商或集成电路生产厂商。

集成电路设计的验收标准:1. 功能性能- 集成电路的最重要标准之一是其功能性能。

它必须按照规格要求准确执行预期任务,并具备可靠性和稳定性。

2. 电气特性- 集成电路应符合正常工作电压范围和电流要求,并具备恰当的功耗特性。

3. 信号完整性- 集成电路的设计应确保信号在电路中的传输不受干扰,保证信号完整性。

4. 可测试性- 集成电路的设计应该具备可测试性,便于进行故障诊断与修复。

5. 可制造性- 集成电路设计应符合制造工艺的要求,如版图设计规范、电路工艺要求等。

6. 可维护性- 集成电路的设计应该便于维护,有助于故障排查和修复。

7. 可靠性- 集成电路设计必须具备足够的可靠性,使其能够在长期使用中保持正常运行。

2023年10月10日集成电路标准

2023年10月10日集成电路标准集成电路是现代电子科技的重要组成部分,广泛应用于通信、计算机、家电、汽车等各个领域。

为了确保集成电路的质量和可靠性,制定统一的集成电路标准是必要的。

2023年10月10日,我国发布了新的集成电路标准,旨在促进行业发展、提高产品质量、推动技术进步。

新的集成电路标准在以下几个方面进行了更新和完善。

首先是制造工艺方面。

随着科技的进步,集成电路制造工艺不断改进,新的标准对制造工艺进行了详细规定。

标准包括了芯片设计、晶圆加工、封装测试等各个环节的要求,详细规定了每个步骤的工艺参数、质量控制点和测试要求。

这将帮助企业提高生产效率,确保产品的一致性和稳定性。

其次是电子元器件的选用。

新的集成电路标准对电子元器件的可靠性、稳定性和兼容性提出了更高要求。

标准规定了集成电路需要符合的性能指标,以及对供应链的要求。

这将有助于提高产品的可靠性和稳定性,减少故障率,保障产品的质量。

第三是环境保护要求。

新的集成电路标准注重减少对环境的影响,规定了生产过程中的环境保护要求。

标准对废水、废气、废弃物的排放进行了明确规定,要求企业进行环境监测和治理,减少对环境的污染。

同时,标准鼓励使用环保材料和技术,推动绿色制造。

此外,新的集成电路标准还对产品质量进行了更加细致的要求。

标准对产品的可靠性、稳定性、安全性和兼容性等方面进行了详细规定,要求企业在生产过程中加强质量控制和检测。

标准还对产品的包装、标识和说明进行了要求,以便消费者正确使用产品,防止使用不当导致事故或故障。

新的集成电路标准的发布,将对我国集成电路产业的发展起到积极的推动作用。

一方面,标准的实施将强化企业的生产管理,提高产品质量,增加市场竞争力。

另一方面,标准的制定将促进技术创新,推动行业不断进步。

通过标准的统一,企业之间可以进行更加有效的合作,加强合规审核,实现资源共享,推动整个行业的发展。

总之,2023年10月10日发布的新的集成电路标准对于行业的发展具有重要意义。

集成电路封装标准

集成电路封装标准1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路标准精选(最新)

G4377《GB/T4377-1996 半导体集成电路电压调整器测试方法和基本原理》

G5965《GB/T5965-2000 集成电路:双极型单片数字集成电路门电路空白详细规范》

G6798《GB/T6798-1996半导体集成电路电压比较器测试方法的基本原理》

G8976《GB/T8976-1996 膜集成电路和混合膜集成电路总规范》

G9424《GB/T9424-1998 半导体器件集成电路:CMOS数字集成电路4000B和4000UB》

G12750《GB/T 12750-2006 半导体器件集成电路:半导体集成电路分规范(不包括混合电路)》

G14619《GB/T14619-1993 厚膜集成电路用氧化铝陶瓷基片》

G14620《GB/T14620-1993 薄膜集成电路用氧化铝陶瓷基片》

G15651.2《GB/T15651.2-2003 半导体器件分立器件和集成电路:光电子器件基本额定值和特性》

G15651.3《GB/T15651.3-2003 半导体器件分立器件和集成电路:光电子器件测试方法》

G16464《GB/T16464-1996 半导体器件集成电路总则》

G16465《GB/T16465-1996 膜集成电路和混合膜集成电路分规范》

G16466《GB/T16466-1996 膜集成电路和混合膜集成电路空白详细规范》

G16878《GB/T16878-1997 用于集成电路制造技术的检测图形单元规范》

G17023《GB/T17023-1997 HCOMS数字集成电路系列族规范》

G17024《GB/T17024-1997 HCOMS数字集成电路空白详细规范》

G17572《GB/T17572-1999 半导体CMOS集成电路:4000B和4000UB系列族规范》G17573《GB/T17573-1999 半导体分立元件和集成电路:总则》

G17574《GB/T17574-1999 半导体分集成电路:数字集成电路》

G17574.9《GB/T 17574.9-2006 数字集成电路紫外光擦除电可编程MOS只读存储器空白详细规范》

G17574.10《GB/T 17574.10-2003 半导体器件集成电路第2-10部分:数字集成电路集成电路动态读/写存储器空白详细规范》

G17574.11《GB/T 17574.11-2006 数字集成电路单电源集成电路电可擦可编程只读存储器空白详细规范》

G17574.20 《GB/T 17574.20-2006 半导体器件集成电路:数字集成电路低压集成电路族规范》

G17940《GB/T17940-2000 半导体集成电路:模拟集成电路》

G18500.1《GB/T18500.1-2001 半导体集成电路:线性数字/模拟转换器(DAG)》G18500.2《GB/T18500.2-2001 半导体集成电路:线性模拟/数字转换器(ADC)》G19248《GB/T19248-2003 封装引线电阻测试方法》

G19403.1《GB/T19403.1-2003 半导体集成电路内部目检(不包括混合电路)》

G20296《GB/T 20296-2012 集成电路记忆法与符号》

G20515《GB/T 20515-2006 半导体器件集成电路:半定制集成电路》

G20870.1《GB/T 20870.1-2007 半导体器件:微波集成电路放大器》

G28639《GB/T 28639-2012 DNA微阵列芯片通用技术条件》

GJ597B《GJB 597B-2012 半导体集成电路通用规范》

GJ1799《GJB1799-1993 大规模集成电路用磷扩散源化学分析方法》

GJ2438A《GJB 2438A-2002 混合集成电路通用规范》

GJ3233《GJB3233-1998半导体集成电路失效分析程序和方法》

QJ10006《QJ10006-2008 宇航用半导体集成电路通用规范》

SJ10741《SJ/T10741-2000 半成品集成电路CMOS电路测试方法的基本原理》SJ10804《SJ/T10804-2000 半成品集成电路电平转换器测试方法的基本原理》SJ10805《SJ/T10805-2000 半成品集成电路电压比较器测试方法的基本原理》SJ11351《SJ/Z 11351-2006 用于描述、选择和转让的集成电路IP核属性格式标准》97.80

SJ11352《SJ/Z 11352-2006 集成电路IP核测试数据交换格式和准则规范》

SJ11353《SJ/Z 11353-2006 集成电路IP核转让规范》

SJ11354《SJ/Z 11354-2006 集成电路模拟/混合信号IP核规范》

SJ11355《SJ/Z 11355-2006 集成电路IP/SoC功能验证规范》

SJ11357《SJ/Z 11357-2006 集成电路IP软核、硬核的结构、性能和物理建模规范》

SJ11358《SJ/Z 11358-2006 集成电路IP核模型分类法》

SJ11359《SJ/Z 11359-2006 集成电路IP核开发与集成的功能验证分类法》

SJ11360《SJ/Z 11360-2006 集成电路IP核信号完整性规范》

SJ11361《SJ/Z 11361-2006 集成电路IP核保护大纲》

SJ20674《SJ20674-1998微波电路系列和品种微波信号检波器系列的品种》

SJ20675《SJ20675-1998微波电路系列和品种微波固态噪声源系列的品种》

SJ20676《SJ20676-1998通信对抗固态宽频带功率放大模块通用规范》

SJ20677《SJ20677-1998微波集成PIN单刀开关模块通用规范》

SJ20678《SJ20678-1998交换网络模块通用规范》

SJ20679《SJ20679-1998通信用户接口模块通用规范》

SJ20680《SJ20680-1998通信群路接口模块通用规范》

SJ20711《SJ20711-1998分步投影曝光机通用规范》

SJ20750《SJ20750-1999军用CMOS电路用抗辐射硅单晶片规范》

SJ20758《SJ20758-1999半导体集成电路CMOS门阵列器件规范》

SJ20759《SJ20759-1999混合集成电路系列与品种DC/DC变换器系列的品种》SJ20802《SJ20802-2001集成电路金属外壳目检标准》

SJ20804《SJ20804-2001微波电路系列和品种微波衰减器系列的品种》

SJ20869《SJ 20869-2003 铌酸锂集成光学调制器测试方法》

SJ20874《SJ 20874-2003 表面安装集成电路试验用插座通用规范》

SJ20875《SJ 20875-2003 扁平封装集成电路插座通用规范》

SJ20954《SJ 20954-2006 集成电路锁定试验》

SJ20961《SJ 20961-2006 集成电路 A/D和D/A转换器测试方法的基本原理》JJG1015《JJG1015-2006 通用数字集成电路测试系统检定规程》

JJF1160《JJF 1160-2006 中小规模数字集成电路测试设备校准规范》

JJF1179《JJF 1179-2007 集成电路高温动态老化系统校准规范》

JJF1238《JJF1238-2010 集成电路静电放电敏感度测试设备校准规范》。