用于高速高分辨率ADC 的C M OS 全差分运算放大器的设计

全差分运算放大器设计概要

全差分运算放大器设计概要全差分运算放大器是一种常见的电子电路,它可以将输入信号的差分放大,并在输出端提供差分信号。

全差分运算放大器广泛应用于模拟与数字信号处理中,如低噪声放大器、滤波器和交叉耦合放大器等领域。

本文将介绍全差分运算放大器的设计概要,包括电路结构、设计要点和性能指标等。

[图片]该电路由两个共模反馈放大器组成,其中一个作为正放大器,另一个作为负放大器。

输入信号通过差分输入端口加到两个反馈放大器上,经过放大后,在输出端口提供差分信号。

为了保证优良的性能,必须对电路的参数进行适当的设计和调整。

首先,需要确定全差分运算放大器的增益要求。

增益是指输出信号与输入信号之间的比例关系。

在不同的应用中,增益要求可能不同。

根据增益要求,可以选择合适的放大器型号和电路拓扑结构。

其次,需要选择适当的放大器元件。

放大器元件包括晶体管、电阻、电容等。

选择合适的元件是设计成功的关键。

晶体管的选择要考虑其增益、噪声系数、带宽等指标。

电阻和电容的选择要考虑其阻值、容值、精度等因素。

然后,需要确定电路的偏置方案。

全差分运算放大器需要提供适当的偏置电压,以确保电路能够正常工作。

偏置电压的选择要考虑元件的工作状态和参数的稳定性。

常见的偏置方案包括电流镜偏置、电流源偏置等。

设计完成后,需要对电路进行性能测试和优化。

性能测试包括增益、带宽、噪声系数、非线性失真等指标的测试。

根据测试结果,可以进行相应的电路优化,以满足设计要求。

最后,需要对电路进行可靠性分析。

可靠性分析是为了确保电路在长时间工作过程中不会出现故障。

可靠性分析包括温度分析、电路重要参数的敏感度分析等。

全差分运算放大器设计的关键在于电路的结构和元件的选择。

合理的电路结构和适当的元件选择可以使电路具有较高的增益、宽带和低噪声等性能。

此外,还需要注意电路的偏置方案和可靠性分析,以确保电路的正常工作和长时间可靠性。

总之,全差分运算放大器是一种重要的电子电路,具有广泛的应用前景。

全差分CMOS运算放大器的设计毕业设计

CMOS运算放大器的设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日目录第一章绪论 (7)1.1设计平台及软件介绍 (7)1.1.1PSPICE简介 (7)1.1.2 L-Edit简介 (7)1.1.3 Cadence OrCAD Capture简介 (7)1.2 设计方法 (8)1.2.1CMOS运算放大器设计方法 (8)1.2.2运算放大器的性能优化 (8)第二章全差分运算放大器基础 (10)2.1 MOS器件基本特性 (11)2.1.1 MOSFET的结构和大信号特性 (11)2.1.2 MOSFET的小信号模型 (12)2.2运算放大器概述 (13)2.3全差分运算放大器特点 (14)第三章CMOS模拟运放设计 (16)3.1设计目标 (16)3.2电路结构分析 (16)3.3.1 输入级设计 (18)3.3.2电流镜电路 (18)3.3.3偏置电路 (19)3.3.4 输出级 (20)3.3.5 整体电路 (20)第四章运放参数的模拟与测量 (22)4.1瞬态分析 (22)4.2 温度特性 (23)4.3输出阻抗 (24)4.4交流特性分析 (25)5.1版图设计基础 (26)5.1.1设计流程 (26)5.1.2 L-edit中的版图设计 (27)5.2 版图设计 (28)5.3版图参数的提取并仿真 (29)5.3.1版图参数的提取和修改 (29)5.3.2电路仿真 (29)第六章总结 (31)【参考资料】 (32)附录: (33)一、Pspice仿真代码: (33)1、原理层次仿真代码(偏置电压由直流电压直接替代) (33)2、MOS分压电路中MOS宽长比确定电路 (35)3、最终Pspice仿真代码 (35)二、版图生成代码 (37)三、版图修改代码 (40)第一章绪论1.1设计平台及软件介绍1.1.1 PSPICE简介PSPICE是由SPICE(Simulation Program with Intergrated Circuit Emphasis)发展而来的用于微机系列的通用电路分析程序。

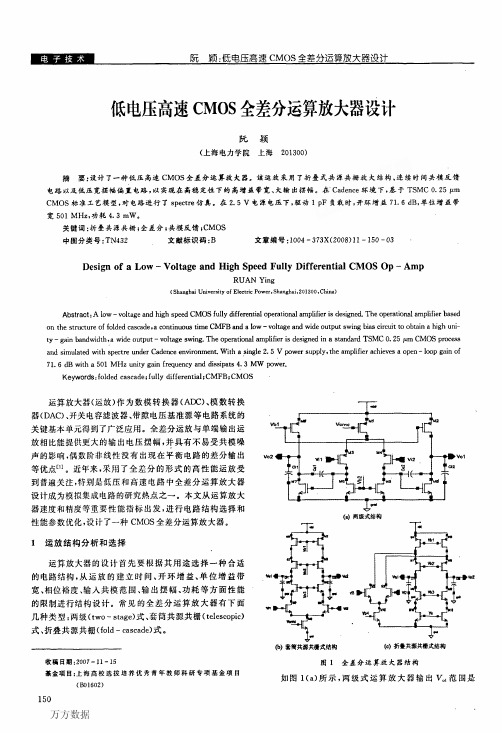

低电压高速CMOS全差分运算放大器设计双

运算放大器的设计首先要根据其用途选择一种合适 的电路结构,从运放的建立时问、开环增益、单位增益带 宽、相位裕度、输入共模范围、输出摆幅、功耗等方面性能 的限制进行结构设计。常见的全差分运算放大器有下面 几种类型:两级(two—stage)式、套筒共源共栅(telescopic) 式、折叠共源共栅(fold—cascade)式。

4‘结语

本文使用TSMC公司的CM025工艺

设计并实现了一个低压高速全差分运算放

大器。采用折叠共源共栅结构,在达到较高

的带宽同时,增大了输出摆幅。连续时间共

模反馈电路以及低压宽摆幅偏置电路,实现

(1)信置电路OO半电路小信号等效模型

图3偏置电路及半电路小信号等效模型

了电路的高稳定性。该运放在2.5 V电源 电压下,’单位增益带宽可以达到501 MHz, 直流增益71.6 dB,相位裕度51。,功耗

P。《P,,更接近于原点,因此P2为折叠共源共栅运放的 主极点,P。为次极点。

要提高开环增益A。,可以采取增加M8,M9的跨导和

1 5】

沟逝长度,但将引起其源极寄生电容的增加和漏源饱和电 正减小,从而降低运放的次极点频率。同样增加M10, M11的沟道长度,会使A。增加而次极点频率减小。考虑 到M4,M5,M6,M7不在信号通路上,因此可以增加其沟 道长度球增加输出阻抗,而不降低工作速度。

△gM9(r2//rlo)r9 R。。“M7一r4+r7[1+(gM7+gM7b)^]

△gM7 r7 r4 r为MOS管的小信号输出电阻。负载电容C。远大于MOS 管各端的寄生电容,CL△cD瞰+CD曲+CD酊。。

节点1对应的极点P。:

P-=一石万勿习丽i1冠i而△一等

节点2对应的极点P。:

全差分运算放大器设计

全差分运算放大器设计全差分运放(Fully-Differential Amplifier,简称FDA)是一种特殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信号走线的对称性和阻抗匹配,以提高传输性能。

一种新型高速CMOS全差分运算放大器设计

一种新型高速CMOS全差分运算放大器设计宋奇伟;张正平【摘要】A low-voltage high-speed CMOS fully-differential operational amplifier based on the pipelined ADC was designed. The operational amplifier combining the amplifying structure of folded cascode with a novel continuous time CMFB circuit achieves high speed and high stability. The Spectre simulation of the operational amplifier is implemented on the basis of SMIC 0. 25 ? M CMOS standard process model under Cadence. At the voltage of 2. 5 V single power supply, the open loop DC gain is 71. 1 dB, the unity gain bandwidth is 303 MHz, the phase margin is 52°, the slew rate is 368. 7 V/μs and the settling time is 12. 4 ns while the load capacitance is 0. 5 pF.%设计了一种基于流水线模/数转换系统应用的低压高速CMOS全差分运算放大器.该运放采用了折叠式共源共栅放大结构与一种新型连续时间共模反馈电路相结合以达到高速度及较好的稳定性.设计基于SMIC0.25μmCMOS标准工艺模型,在Cadence环境下对电路进行了Spectre仿真.在2.5V单电源电压下,驱动0.5pF负载时,开环增益为71.1dB,单位增益带宽为303MHz,相位裕度为52°,转换速率高达368.7V/μs,建立时间为12.4ns.【期刊名称】《现代电子技术》【年(卷),期】2012(035)004【总页数】4页(P166-168,172)【关键词】高速运算放大器;全差分;折叠式共源共栅;共模反馈【作者】宋奇伟;张正平【作者单位】贵州大学理学院,贵州贵阳550025;贵州大学理学院,贵州贵阳550025【正文语种】中文【中图分类】TN919-34随着数/模转换器(DAC)、模/数转换器(ADC)的广泛应用,高速运算放大器作为其核心部件受到越来越广泛的关注和研究。

采用折叠式共源共栅结构实现高速CMOS全差分运算放大器的设计

采用折叠式共源共栅结构实现高速CMOS全差分运算放大器的设计折叠式共源共栅结构是一种常用于高速CMOS全差分运算放大器设计的电路结构。

它结合了共源和共栅结构的优点,在设计高速差分运算放大器时具有重要的应用价值。

在设计高速CMOS全差分运算放大器时,首先需要确定电路的工作频率和增益要求。

然后,根据设计要求选择合适的MOS管尺寸以及电路拓扑结构。

在采用折叠式共源共栅结构之前,我们先来了解一下共源和共栅结构的特点。

共源结构是一种常见的差分放大器结构,它提供了较大的增益和较高的输入阻抗,但由于电流镜电路(如PMOS电流镜)的引入,使得其增益和频率特性受到限制。

共栅结构是一种常见的高速差分放大器结构,它具有良好的增益和频率特性,但输入阻抗较低。

因此,为了综合考虑增益、频率特性和输入阻抗,我们可以采用折叠式共源共栅结构。

折叠式共源共栅结构的基本原理是将两个共源结构和两个共栅结构连接在一起形成一个差分放大器。

其中,一个共源结构用作输入级,另一个共源结构用作输出级。

同时,一个共栅结构用于提供增益,另一个共栅结构用于提供带宽。

具体来说,折叠式共源共栅结构的输入级包含一个共源结构和一个共栅结构。

其中,共源结构的输入端连接输入信号,输出端通过一个电流源连接到共源结构的源极。

共栅结构通过一个电流源连接到共源结构的源极。

这样,共源结构和共栅结构共同构成输入级。

折叠式共源共栅结构的输出级也包含一个共源结构和一个共栅结构。

其中,共源结构的源极通过一个电流源连接到地,栅极接受输入信号。

共栅结构的源极通过一个电流源连接到共源结构的源极。

这样,共源结构和共栅结构共同构成输出级。

在折叠式共源共栅结构中,输入级的共源结构和共栅结构提供了较大的增益和较高的输入阻抗,输出级的共源结构和共栅结构提供了较大的带宽和较低的输出阻抗。

通过适当选择MOS管的尺寸和电流源的电流,可以实现高速差分运算放大器的设计要求。

综上所述,采用折叠式共源共栅结构可以实现高速CMOS全差分运算放大器的设计。

毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://img.taocdn.com/s3/m/15f996a177232f60dccca185.png)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

一种用于高速高精度ADC的电压基准源设计

6 05 ; 1 0 4

2 河 南省 电 力 公 司 洛 阳供 电 公 司 ,河 南 洛 阳 . 4 0 9 71 0 )

(. 1电子薄膜 与 集成 器件 国 家重点 实验 室 ,四) 成都 l l

摘 要 :针 对 电压 基 准 源对流 水 线结构 的 高速 高精 度A C D 的性 能 影响进 行 了建模 分 析 .提 出

第年月

蘧钎雾

V1 o o2 . . N3 1

Ma.2 0 r 01

d i 03 6 0i n16 - 7 52 1 . .1 o: . 9 .s . 3 4 9 .0 00 0 7 1 9 s 5 3

一

种用于 高速 高精度A C D 的 电压基准源设计

由于 流过R 和 R 的 电流, 正 比与 N, 故可 4 5 N L L

表示 为 :

可 以得 到 D L 基 准 电压 源 温 度 系 数 的 要 N 对

=

求 ,即温度 系数 T  ̄68 p / c . p m %。式 中 , 1 室 < 4 D 为

温2 o时 的基 准 电压值 。 5C

放 的 d 近 1 d 趋 ;三 是 引入 预 校正 技 术 ,即通 过 一 个 反 馈 电路 将 电源 电压 稳 定在 ,并 由V 为 基

准 电路 供 电 ,以有效 提高P R S R。 本 文 的 电路 结构 除采 用 共源 共栅 电流镜 技术 外 ,所 加入 的电源 抑制 比提 高 电路还 可使 运 放 的 A削 近 1 趋 ,从 而大大 提 高基准 源 的电源抑 制 比。

统 集 成 技 术 的提 出 .对 模 拟 集 成 电路 基 本 模 块 ( / 如A D、D A转换 器 、滤 波 器 以及 锁 相 环等 电路) / 提 出 了更 高 的精度 和速 度要 求 。这 也就 意 味 着 系

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图1包含运算放大器的采样-保持电路

采样—保持电路是整个ADC处理的关键主要是利用开关电容电路的电容上的电荷重分配的原理来实现的。

图中IN与IN为输入的模拟信

图2带有辅助放大器的折叠式共源共栅型运算放大器2.1折叠式共源共栅(Folded Ca s c ode)

折叠式共源共栅结构特别适用于低电压设计,它被用作主运放。

在设计中,主运放采用大尺寸器件以驱动负载电容,本身可以产生很高的单

图3带辅助运放的共源共栅级原型

应基于在M2管上附加辅助运放以提升其共源共栅效应而达到。

设辅助运放放大倍数为A add,通

图5共模反馈电路

图4设计采用的辅助运放

应增大同样的倍数:

A v=g

m1r o1(g m2r o2(A add+1)+1)(4)

图6运放的交流响应

开环增益模拟显示,在驱动大小为2pF的负载

时,运放可以达到94dB的增益以及260MHz的

单位增益带宽。

图7为模数转换器芯片中该运放

图7运放版图

总结

推出了一种带辅助放大器的运算放大器,该[3]B ult K and Geelen G.A Fast-Settling CMOS Op Amp

SC Circuits with90-d B DC Gain[J].IEEE Journal of

State Circuits,D ecember1990,25(6):1379-1384.。