锁相环PLL基本原理设计与应用

什么是电子电路中的锁相环及其应用

什么是电子电路中的锁相环及其应用电子电路中的锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用的反馈控制电路,用于将输入信号的相位与频率与参考信号的相位与频率同步,从而实现信号的稳定性和精确性。

锁相环在通信、计算机、音频处理等领域都有重要的应用。

一、锁相环的工作原理锁相环主要由相位比较器(Phase Detector)、环形数字控制振荡器(VCO)和低通滤波器(LPF)组成。

相位比较器用来比较输入信号和参考信号的相位差,输出一个宽度等于相位差的脉冲信号。

VCO根据相位比较器输出的脉冲信号的宽度和方向来调节输出频率,使其与参考信号的频率和相位同步。

LPF用来滤除VCO输出信号中的高频成分,保证输出的稳定性。

二、锁相环的应用1. 通信领域:在数字通信系统中,锁相环被广泛应用于时钟恢复、时钟生成和时钟变换等方面。

通过锁相环可以实现对时钟信号的稳定传输,提高通信系统的可靠性和容错性。

2. 音频处理:在音频设备中,锁相环被用于时钟同步和抖动消除。

通过锁相环可以实现音频数据的同步传输和精确抖动控制,提高音质和信号稳定性。

3. 数字系统:在数字系统中,锁相环可用于时钟恢复、频率合成和位钟提取等方面。

通过锁相环可以实现对时钟信号的稳定提取和精确合成,确保系统的可靠运行。

4. 频率调制与解调:在调制与解调系统中,锁相环被应用于频偏补偿和相位同步。

通过锁相环可以实现对信号频偏和相位偏移的补偿,保证调制与解调的准确性和稳定性。

5. 频谱分析:锁相环还可以应用于频谱分析仪中,通过锁相环可以实现频率分析的准确性、稳定性和精确性。

三、锁相环的特点1. 稳定性:锁相环可以通过调整VCO的输出频率来实现输入信号和参考信号的同步,从而提高信号的稳定性。

2. 精确性:锁相环可以通过精确的相位比较和频率调节,实现对信号相位和频率的精确控制,提高信号处理的准确性。

3. 自适应性:锁相环可以根据输入信号和参考信号的变化自动调节,适应不同输入条件下的信号同步要求。

锁相环的组成和原理及应用

锁相环的组成和原理及应用一.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

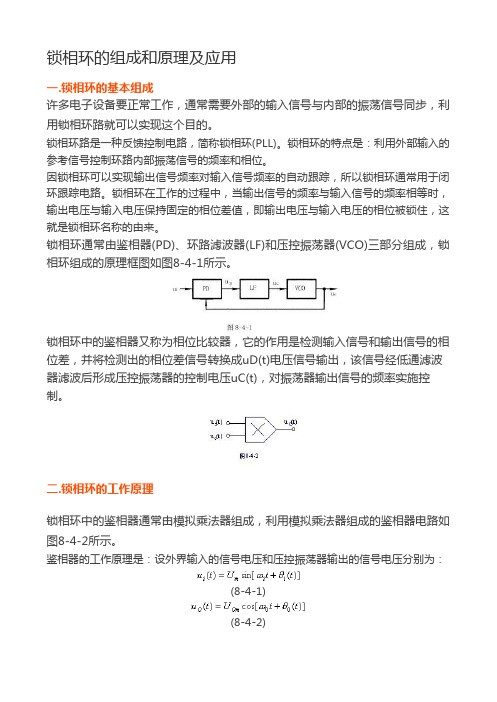

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

二.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压uD为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。

即uC(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。

锁相环pll原理与应用

$number {01}

目 录

• 锁相环PLL的基本原理 • 锁相环PLL的种类与特性 • 锁相环PLL的应用 • 锁相环PLL的发展趋势与挑战 • 锁相环PLL的设计与实现

01

锁相环PLL的基本原理

PLL的基本结构

鉴相器(PD)

用于比较输入信号和反馈信号的相位 差。

压控振荡器(VCO)

相位同步

锁相环PLL用于电力系统的相位同步,确保不同电源之间的相位一 致,提高电力系统的稳定性。

频率跟踪

锁相环PLL用于电力系统的频率跟踪,实时监测电网频率变化,确 保电力系统的正常运行。

故障定位

通过分析电网信号的相位和频率变化,结合锁相环PLL实现电力故 障的快速定位和排查。

其他领域的应用

电子测量

PLL的发展趋势

高速化

随着通信技术的发展, 对信号的传输速率要求 越来越高,锁相环PLL 的频率合成速度和跟踪

速度也在不断加快。

数字化

随着数字信号处理技术 的进步,越来越多的锁 相环PLL开始采用数字 控制方式,提高了系统 的稳定性和灵活性。

集成化

为了减小电路体积和降 低成本,锁相环PLL的 集成化程度越来越高, 越来越多的功能被集成

软件PLL具有灵活性高、可重 构性好等优点,但同时也存在 计算量大、实时性差等缺点。

各种PLL的优缺点比较

1 2

3

模拟PLL

优点是响应速度快、跟踪性能好;缺点是元件参数漂移、温 度稳定性差。

数字PLL

优点是精度高、稳定性好、易于集成;缺点是响应速度慢、 跟踪性能较差。

软件PLL

优点是灵活性高、可重构性好;缺点是计算量大、实时性差 。

晶振锁相环的原理与应用

晶振锁相环的原理与应用1. 简介晶振锁相环(Phase Locked Loop,PLL)是一种常用的电子电路,用于将一个参考频率和一个输入频率进行相位和频率的同步。

它由相位比较器、低通滤波器、倍频器和控制电压源等组成,广泛应用于通信、计算机、音频设备等领域。

2. 原理晶振锁相环的工作原理可以简单概括为以下几个步骤:•相位比较器(Phase Comparator):将参考频率和输入频率进行相位比较,产生一个误差信号。

•低通滤波器(Low Pass Filter):对误差信号进行滤波,得到一个平滑的控制电压。

•倍频器(Multiplier):将输入频率与控制电压相乘,得到一个倍频的信号。

•控制电压源(Control Voltage Source):根据倍频信号调整参考频率,使其与输入频率同步。

3. 应用晶振锁相环在电子电路中有广泛的应用,下面列举几个常见的应用场景:3.1 时钟同步在许多数字系统中,需要对时钟信号进行同步,晶振锁相环可以将一个稳定的参考时钟与系统中的时钟进行同步。

它可以减小时钟误差,提高系统的精确性和稳定性。

3.2 频率合成晶振锁相环可以将一个较低的频率合成成一个较高的频率。

这在通信系统中常用于频率合成器、频率变换器等设备上。

晶振锁相环可以实现高精度的频率合成,保证通信设备的稳定性。

3.3 信号恢复在信号传输过程中,由于信号噪声、衰减等因素,信号可能会变得不稳定。

晶振锁相环可以通过同步技术,将失真的信号恢复为原始的稳定信号。

这在通信设备、音频设备等领域中特别重要。

3.4 频率调制晶振锁相环可以将一个输入频率调制到一个不同的频率。

这在调制解调器、调频电台等设备中广泛应用。

晶振锁相环可以实现精确的频率调制,保证通信设备的稳定性和可靠性。

3.5 相位调制晶振锁相环还可以实现相位调制。

相位调制在无线通信、雷达系统等领域中有广泛的应用。

晶振锁相环可以实现相位调制的精确控制,提高系统的性能和可靠性。

锁相环原理及应用

锁相电路(PLL)及其应用自动相位控制(APC)电路,也称为锁相环路(PLL),它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

它是一个以相位误差为控制对象的反馈控制系统,是将参考信号与受控振荡器输出信号之间的相位进行比较,产生相位误差电压来调整受控振荡器输出信号的相位,从而使受控振荡器输出频率与参考信号频率相一致。

在两者频率相同而相位并不完全相同的情况下,两个信号之间的相位差能稳定在一个很小的范围内。

目前,锁相环路在滤波、频率综合、调制与解调、信号检测等许多技术领域获得了广泛的应用,在模拟与数字通信系统中已成为不可缺少的基本部件。

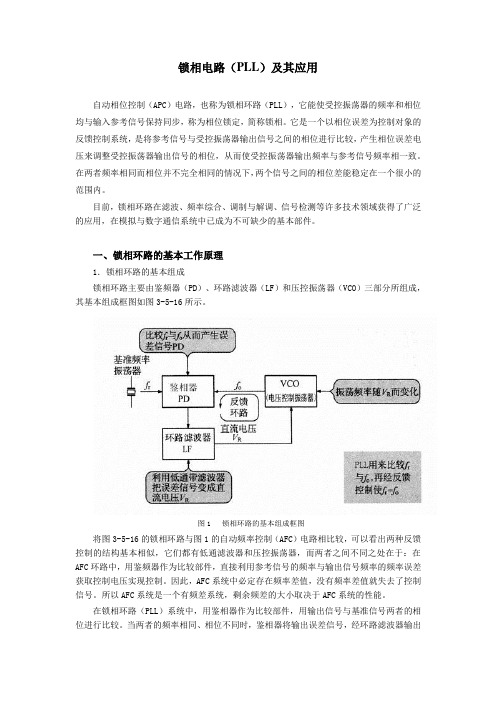

一、锁相环路的基本工作原理1.锁相环路的基本组成锁相环路主要由鉴频器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分所组成,其基本组成框图如图3-5-16所示。

图1 锁相环路的基本组成框图将图3-5-16的锁相环路与图1的自动频率控制(AFC)电路相比较,可以看出两种反馈控制的结构基本相似,它们都有低通滤波器和压控振荡器,而两者之间不同之处在于:在AFC环路中,用鉴频器作为比较部件,直接利用参考信号的频率与输出信号频率的频率误差获取控制电压实现控制。

因此,AFC系统中必定存在频率差值,没有频率差值就失去了控制信号。

所以AFC系统是一个有频差系统,剩余频差的大小取决于AFC系统的性能。

在锁相环路(PLL)系统中,用鉴相器作为比较部件,用输出信号与基准信号两者的相位进行比较。

当两者的频率相同、相位不同时,鉴相器将输出误差信号,经环路滤波器输出控制信号去控制VCO ,使其输出信号的频率与参考信号一致,而相位则相差一个预定值。

因此,锁相环路是一个无频差系统,能使VCO 的频率与基准频率完全相等,但二者间存在恒定相位差(稳态相位差),此稳态相位差经鉴相器转变为直流误差信号,通过低通滤波器去控制VCO ,使0f 与r f 同步。

2.锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。

锁相环的基本原理锁相环基本原理及其应用

锁相环的基本原理锁相环基本原理及其应用锁相环的基本原理锁相环基本原理及其应用锁相环及其应用所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF)和压控振荡器(简称VCO)三个部件组成闭合系统。

这是一个基本环路,其各种形式均由它变化而来PLL概念设环路输入信号v= Viomimsin(ωit+φi)环路输出信号v= Vosin(ωot+φo)——其中ωo=ωr+△ωo通过相位反馈控制,最终使相位保持同步,实现了受控频率准确跟踪基准信号频率的自动控制系统称为锁相环路。

PLL构成由鉴相器(PD)环路滤波器(LPF)压控振荡器(VCO)组成的环路。

PLL原理从捕捉过程→锁定A.捕捉过程(是失锁的)a. b.φi┈φi均是随时间变化的,经相位比较产生误差相位φe=φi-φo,也是变化的。

φe(t)由鉴相器产生误差电压v(t)=f(φde)完成相位误差—电压的变换作用。

v(t)为交流电压。

dc.v(t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由VCO产生d控制角频差△ω0,使ω0随ωi变化。

B.锁定(即相位稳定)a. b.一旦锁定φe(t)=φe∞(很小常数)v(t)= V(直流电压)ddω0≡ωi输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ω0max, 即ω0=ωr+△ω0max。

ωr为VCO固有振荡角频率。

)锁相基本组成和基本方程(时域)各基本组成部件鉴相器(PD)数学模式v(t)=AsinφdDe(t)相位模式环路滤波器(LPF) 数学模式v(t)=A(P) v(t)cFd相位模式压控振荡器(VCO)数学模式相位模式环路模型相位模式:指锁相环(PLL)输入相位和输出相位的反馈调节关系。

相位模型:把鉴相器,环路滤波器和压控振荡器三个部件的相位模型依次级联起来就构成锁相相位模型。

锁相环PLL原理与应用

Uφ(t) f2’

uc VCO

Ud(t)

对锁相环的另一种描述

uo Uo’(t)

反馈过程简单描述: ωo(t)↑→频差↓→ PD的直流分量↓→ LPF的直流分量↓→ ωo(t) ↓→频差↑→ PD的直流分量↑→ LPF的直流分量↑→ ωo(t)↑→循环往复 频差=0 → PD的直流分量=常数→ LPF的直流分量=常数→

用低通滤波器LPF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压

u c A d sio n ( t ) t { o ( t ) [ [ ]i( t ) t i( t )]}

此时的ωi(t)为输入信号的瞬时振荡角频率, ωo(t)为输出信号的瞬时振荡角频率;φi (t)和φo(t)分别 为输入信号和输出信号的瞬时位相。瞬时频率(单位时间变化的弧度)和瞬时相位的关系为:

对一个二阶系统而言,就存在ωn、ξ。在同样的LPF条件下,VCO灵敏度越高, ξ越小(很快锁定)。

锁相环仿真前对一些基本仿真原件的认识

——VCO0

FM、VCO 信号相乘

一种由数字电路组成的鉴相器。 检测到输入信号过零时开启计数器;检测到参考信号过零时锁定计数器。其间计数器内的 计数值就是相位差的某种表达。该计数值经过A/D后就成为相位差某种表达模拟量。

RS触发器

ui PD

ud LPF

UI(t) f1

ui

ud

uc

uo

PD

LPF

VCO

鉴相器PD:是一个完成相位比较的单元,用来比较输入信号和基准信号的之间的相位。它的输出 电压正比于两个输入信号之相位差。

低通滤波器LPF:是一个有源频及其他的高频噪声),起平滑滤波的作用。通常由电阻、电容或电感等组成,有时也包含运 算放大器。

锁相环的基本原理和应用

锁相环的基本原理和应用1. 什么是锁相环锁相环(Phase-Locked Loop,简称PLL)是一种电路模块,其基本原理是通过对输入信号和参考信号的相位进行比较和调节,以使输出信号与参考信号保持稳定的相位差。

锁相环广泛应用于通信、测量、频率合成等领域,因其能够实现信号调频、时钟控制等功能而备受关注。

2. 锁相环的基本结构锁相环由相位比较器(Phase Comparator)、环路滤波器(Loop Filter)、振荡器(VCO)和分频器(Divider)组成。

其基本结构如下所示:•相位比较器:相位比较器用于比较输入信号和参考信号的相位差,并产生一个与相位差成正比的控制电压。

•环路滤波器:环路滤波器用于平滑相位比较器输出的控制电压,并将其转换成稳定的直流电压。

•振荡器:振荡器根据环路滤波器输出的控制电压来调节其输出频率,使其与参考信号频率保持一致。

•分频器:分频器将振荡器输出的信号进行频率分频,以产生一个与参考信号频率一致且稳定的输出信号。

3. 锁相环的工作过程锁相环的工作过程可以分为四个阶段:捕获(Capture)、跟踪(Track)、保持(Hold)和丢失(Lose)四个阶段。

•捕获阶段:在捕获阶段,锁相环通过不断调节VCO的频率,使其与参考信号频率逐渐接近,并将相位差逐渐减小。

•跟踪阶段:当锁相环的输出频率与参考信号频率相等时,进入跟踪阶段。

在该阶段,VCO的频率和相位与输入信号保持一致。

•保持阶段:在保持阶段,锁相环维持着与输入信号相同的相位和频率。

任何相位和频率的变化都会通过反馈回路进行补偿。

•丢失阶段:如果输入信号的频率超出锁相环的捕获范围,锁相环无法跟踪该信号,进入丢失阶段。

在该阶段,锁相环输出的信号频率与输入信号频率不一致。

4. 锁相环的应用锁相环在各个领域有着广泛的应用,下面列举几个常见的应用:•频率合成器:锁相环可以将稳定的参考频率合成为其他频率,广泛用于通信、雷达、测量等领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

sini (t) o (t) i (t) o (t)

第 23 页

因此可以把式 ud (t) K d sin (t)写成

ud (t) Kd i (t) o (t) Kd(t)

所以,当φ(t)≤30°时,鉴相器特性近似为直线,ud(t)与 φ(t)成正比。

参考信号

鉴相器

环路 滤波器

压控 输出信号 振荡器

u路入 位鉴环压o所信和(相路控t)要器号输的滤振是求的入相波荡相的位频信器位,性率号的受比它能靠的作环较的。拢相用路装输图,位是置滤出直保4,滤波电-至持用2除压器来两 某uu输基id比(者 种t出()本较t是的特)电中输对锁频定压的入应率的相u高信于c相关环号频(这t同系)u两的分框i,,(个t控量图)与使达信制及压得到号,噪控相相V使声振C位位O振,荡差锁输荡以器的定出输频保函的信出率证数目号信。向环的号的输。相

第六节 锁相环路的应用

一、集成锁相环芯片

二、 方波发生器 三、PLL在调制解调技术中的应用

四、PLL在空间技术上的应用

五、PLL在稳频技术中的应用

六、PLL在频率合成器中的应用

第3页

第一节 锁相环路(PLL)及其反馈控制电路简介

在无线电技术中,为了改善电子设备的性能,广泛采用 各种的反馈控制电路。常用的有自动相位控制(APC)电路, 也称为锁相环路(PLL-Phase Locked Loop),自动增益控 (AGC)电路以及自动频率控制(AFC)电路。

AFC电路是以消除频率误差为目的的反馈控制电路,由于它的 基本原理利用频率误差电压去消除频率误差,这样,当电路达到平 衡时,必然有剩余的频率误差存在,无法达到现代通信中对高精度 频率同步(频差为0)和相位跟踪的广泛要求.要实现频率和相位的 跟踪,必须采用自动相位控制电路,即锁相环(PLL: Prase Locked Loop)

2006年电子技术竞赛讲座

第1页

锁相环(PLL)基本原理、设计与应用

刘颖

第一节 反馈控制电路简介

第2页

第二节 自动增益控制电路(AGC)

第三节 自动频率控制(AFC)电路

第四节 锁相环路(PLL)基本原理

一、PLL概述

二、基本锁相环的构成

三、锁相环的基本原理

四、锁相环各组成部分分析

五、环路的锁定、捕获和跟踪,同步带和捕捉带

压控振荡器的特性可用调频特性(即瞬时振荡频率ωo(t)相 对于输入控制电压uc(t) 的关系)来表示,如图4-6所示。

第 29 页

在一定范围内,ωo(t)与uc(t) 是成线形关系的,可用下式表示, 即

o (t) o K uc (t)

高频成分

低频成分

第 21 页

通过环路滤波器,把上式中高频分量滤除。则鉴相器的输出为

ud

(t)

1 2

AmU1mU 2m

sini

(t)

o

(t)

ud (t) K d sin (t)

式中

Kd

1 2

AmU1mU 2m

其中Am 为乘法器的增益系数,量纲为1/V。

(t) i (t) o (t)

在锁相频率合成器中,锁相环路具有稳频作用,能够完 成频率的加、减、乘、除等运算,可以作为频率的加减器、 倍频器、分频器等使用。

二、基本锁相环的构成

第 15 页

基本的锁相环路组成

鉴相器(PD-Phase Detector) 环路滤波器(LF-Loop Filter) 压控振荡器(VOC: Voltage Controlled Oscillater)

的性能,也就方便的改变了锁相环的性能。

第 27 页

3.压控振荡器VOC

压控振荡器受环路滤波器输出电压uc(t) 的控制,使振 荡频率向输入信号的频率靠拢,直至两者的频率相同,使 得VCO输出信号的相位和输入信号的的相位保持某种关系, 达到相位锁定的目的。

第 28 页

压控振荡器就是在振荡电路中采用压控元件作为频率控制 元件。压控元件一般都是变容二极管。由环路滤波器送来的控 制信号电压uc(t) 加在压控振荡器振荡回路中的变容二极管,当 uc(t) 变化时,引起变容二极管结电容的变化,从而使振荡器的 频率发生变化。因此压控振荡器实际上就是一种电压-频率变换 器。它在锁相环路中起着电压-相位变化的作用。

•自动频率控制(AFC)的原理框图

第 11 页

图3-1 AFC的原理方框图

第 12 页

工作原理: 图3-1是AFC的原理框图。被稳定的振荡器频率f0 与 标准频率fr 在频率比较器中进行比较。当f0 = fr时,频率比较器 无输出,控制元件不受影响;当 f0 ≠ fr时,频率比较器有误差 电压输出,该电压大小与| f0 - fr | 成正比。此时,控制元件的参 数即受到控制而发生变化,从而使 发生变化,直到使频率误差 减小到某一定值Δ f ,自动频率微调过程停止,被稳定的振荡 器就稳定在 f0 = f0± Δf 的频率上。

三、锁相环的基本原理

第 17 页

设输入信号ui(t)和本振信号(VCO输出信号)uo(t)分别是正 弦和余弦信号,它们在鉴相器内进行比较,鉴相器的输出是一

个与两者间的相位差成比例的电压ud(t),一般把ud(t)称为误差 电压。

环路低通滤波器滤除鉴相器中的高频分量,然后把输出电

压ud(t)加到VCO的输入端,VCO送出的本振信号频率随着输入电 压的变化而变化。如果二者频率不一致,则鉴相器的输出将产

图4-5 三种常用的环路滤波器

第 26 页

环路滤波器的作用是滤除 ud(t) 中的高频分量及噪声,以 保证环路所要求的性能。

环路滤波器如果用的是图4-5(b)或(c)所示的比例积 分器时,比例积分器把鉴相器输出的即使是非常微小的电压积

累起来,形成一个相当大的VCO控制电压,并保持到 φo(t)=φi(t) 时刻。只要改变环路滤波器的R1 、R2、C 就能改变环路滤波器

uo (t) U2m cos0t o (t) U2m cos0t o (t)

式中 o (t) o (t) ,经乘法器相乘后,其输出为

ui (t) uo (t)

Am

1 2

AmU1mU2m sin 2ot

i (t)

o (t) sini (t) o (t)

其中: i (t) i o t i (t)

t i (t)

i o 是输入信号角频率与VCO振荡器信号角频率 之差,称之为固有频差。

按上面的新定义,可将式PLL输入、输出信号改写为

第 20 页

ui (t) U1m sinot i (t)

第四节 锁相环路(PLL)

第 13 页

一、PLL概述

锁相环路是一个相位误差控制系统,是将参考信号与输出 信号之间的相位进行比较,产生相位误差电压来调整输出信号 的相位,以达到与参考信号同频的目的。

参考 信号

鉴相器

环路 滤波器

输出

压控

信号

振荡器

图4-1 锁相环系统框图

第 14 页

锁相环路应用

锁相接收机 微波锁相振荡源 锁相调频器 锁相鉴频器 定时提取(滤波) 锁相频率合成器 ……

态”。

第 18 页

四、锁相环各组成部分分析

1.鉴相器 鉴相器是锁相环路的关键部件,它的形式很多,我们仅介

绍其中常用的“正弦波鉴相器”。

1)正弦波鉴相器的数学模型 任何一个理想模拟乘法器都可以作为有正弦特性的

鉴相器。设输入信号为:

ui (t) U1m sinit i (t)

压控振荡器的输出信号为:

在时域中鉴相器数学模型如图4-4所示

第 24 页

图4-4 鉴相器的线性数学化模型(时域)

2.环路滤波器(Loop Filter,简称LF)

第 25 页

环路滤波器是线性电路,由线性元件电阻、电感和电容 组成,有时还包括运算放大器在内。它是低通滤波器。在锁 相环路中,常用的滤波器有以下的三种,如图4-5所示。

第 16 页

鉴相器是相位比较装置,用来比较输入信号ui(t)与压控 振荡器输出信号uo(t) 的相位,它的输出电压ui(t)是对应于 这两个信号相位差的函数。

环路滤波器的作用是滤除ud(t)中的高频分量及噪声, 以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压uc(t)的控制,使 振荡频率向输入信号的频率靠拢,直至两者的频率相同, 使得VCO输出信号的相位和输入信号的相位保持某种特 定的关系,达到相位锁定的目的。

它们所起的作用不同,电路构成也不同,但它们同属于 反馈控制系统,其基本工作原理和分析方法(AGC)

自动增益控制电路是某些电子设备特别是接收设备的 重要辅助电路之一,其主要作用是使设备的输出电平保持 一定的数值。所以也叫自动电平控制(ALC)电路。

自动增益控制电路是一种反馈控制电路,当输入信号电 平变化时,用改变增益的方法,维持输出信号电平基本不 变的一种反馈控制系统。

鉴相器的作用:将两个输入信号的相位差φ(t) 转变为输出

电压ud(t)。

第 22 页

由式 ud (t) K d sin (t)可得出鉴相特性,如图4-3所示。

图4-3 正弦特性曲线

由于 ud(t) 随 φ(t) 作周期性的正弦变化,因此这种鉴相器

称为正弦波鉴相器。

2)鉴相器线性化的数学模型

UUii与与增增益益KK的的关关系系曲曲线线

第9页

Ui与UO的关系曲线

加上AGC后,放 大器增益K随Ui的增加 而减小(曲线1),因而 输出电压UO 和输入电 压Ui不再是线性关系, 振幅特性UO~ Ui不再 是一条直线,而是如

图2-3 所示的曲线2’。

图2-3 简单的AGC特性

从曲线可知:当Ui 较小时,控制电压Up 也较小, 这时增益可K虽略有减小, 但变化不大,因此振幅曲线基本上仍是一段直线;当 足够大时,Up的控制作用 较强,增益K显著减小。这时UO基本保持不变,振幅特性曲线2‘的bc段所示。通 常把UO基本上保持不变这部分叫做AGC的可控范围。可控范围越大,AGC的特 性越好。