Cadence原理图输入

cadence使用技巧

点击dsn后,Tools→Generate Part,在Part name中输 入要生成的元件名,点OK确定完成。元件化的原理图当做 元件使用,通常使用频率高的模块可以生成元件来使用。

自动备份设置

Options→Autobackup,设置间隔时间、备份数目和存放目录。

添加原理图库

如果采用现有自创的原理图库,可以右击Library,点Add File, 找到库存放的路径及库名,点打开添加。

未连接管脚处理

→Place→No Connect,在未连接管脚上放置“×”符号。

添加文本

→点击右端的Place text工具栏图标,输入文字内容,点击 Color的下拉菜单,选择喜欢的颜色。然后点击Font下的 Change后,选择brary下的库,按Delete键删除或右击鼠标,选Cut删除。

Capture库

orcad元件列表

capture库

总线连接

→放置总线的命令是Place→Bus或点击右端工具栏图标, 按住shit键可以画出斜线。

总线支线

→Place→Bus Entry可以放置一小段斜线,即总线支线。

Cadence--原理图的设计2

线进行连接,则需要在A图纸和B图纸上分别放置两 个“页面连接器”,而且两个图纸上的页面连接器 的名称应该完全一致,这样才能表示它们之间的连 接关系。

层次式电路原理图设计

现代电路设计往往采用“由顶而下”的设计方法

(其实不仅仅是电路设计,程序设计、结构设计等, 也常常采用“由顶而下”的方法),层次式原理图 就适应了这种设计思想。

Cadence—原理图设计2

原理图的类型

平坦式电路原理图设计

层次式电路原理图设计

平坦式电路原理图设计

平坦式电路原理图,就相当于把一张大的原理图切

割成若干份,而每张图纸就是切割后的小图,同时 各个图纸之间是通过“页面连接器”相互连接的。 放置页面连接器时,首先点击

比如在A图纸的电路与B图纸的电路之间,有两条连

在层次式电路原理主图中,反映各个 子图之间的连接关系;子图反映内部具体的电路。

我们的设计最好采用先设计主图,并由主图中的子

图块生成子图,再绘制子图电路。这样的设计方法 是典型的“由顶而下”的设计方法。

绘制子图块,点击

绘制子图的对话框

课堂作业

1、完成一个平坦式原理图

2、完成一个层次式原理图

检查调试至无错

在这之后,我们应该绘制该子图所对应的具体电路,

在此过程中,接口的位置也可以根据需要进行移动。

创建完成后项目管理器和信息输出可以看见主图、

子图以及接口的信息。

模块一

模块二

模块三

在绘制了所有子图的电路之后,按照以前的步骤,

还需要进行DRC校验、元件重新编号、元件封装的 设置、生成网络表等工作。

在主图上画出了子图块之后,还要给它填上接口,添

加接口的方法是,首先点击子图块,使其处于被选中 的状态,然后点击 图标。

cadence原理图输入工具composer使用

建立新单元

视图(view) 同一个单元会有不同的视图; 对于不同视图是不同的文件,但代表同一个电路; 建立新单元:

建立原理图视图 建立符号图

<13页> 2011/9/15 16:01

建立新单元

建立原理图视图步骤:

(1)在库管理中选择工作库;

<14页> 2011/9/15 16:01

建立新单元

(4) 原理图编辑 示例:标准单元库中的一个门或用户曾设计好的单元; 添加示例: Add→Instance或快捷键 i 或F3

<19页> 2011/9/15 16:01

建立新单元

弹出对话框

Component Browser对话

框 AddInstance

对话框

库 单元 视图 示例名

<20页> 2011/9/15 16:01

晶体管级原理图

晶体管可以用来设计基本“门”单元; 用在verilog中内建的晶体管开关模型来仿真,也可用

Spectre或Spice模拟仿真器仿真。 通用晶体管部件库NCSU_Analog_Parts

<54页> 2011/9/15 16:01

晶体管级原理图

<55页> 2011/9/15 16:01

<35页> 2011/9/15 16:01

建立新单元

(9)关闭窗口 Windows→Close 或 ctrl+w

<36页> 2011/9/15 16:01

建立新单元

问题:下图全加器与书中全加器比较,两者区别, 书中所画全加器优点?

<37页> 2011/9/15 16:01

CADENCE原理图与PCB设计说明

CADENCE原理图与PCB设计说明内部资料请勿外传CADENCE原理图与PCB设计说明(第1版)⽬录⽬录序⾔ (1)第⼀章系统简介 (2)1.1 系统组成 (2)1.1.1 库 (2)1.1.2 原理图输⼊ (2)1.1.3 设计转换和修改管理 (2)1.1.4 物理设计与加⼯数据的⽣成 (3)1.1.5 ⾼速PCB规划设计环境 (3)1.2 Cadence设计流程 (3)第⼆章Cadence安装 (4)2.1安装步骤 (4)2.2 LICENSE设置 (7)2.3 库映射 (7)2.4 修改cds.lib⽂件,设置原理图库: (8)2.5 编辑ENV⽂件,设置PCB库: (9)第三章CADENCE库管理 (11)3.1 中兴EDA库管理系统 (11)3.2 CADENCE库结构 (13)3.2.1 原理图(Concept HDL)库结构: (13)3.2.2 PCB库结构: (13)第四章项⽬管理器 (15)4.1 项⽬管理的概念 (15)4.2 创建或打开⼀个项⽬ (15)4.3 原理图库的添加: (16)4.4 填写设计(Design)名称 (17)4.5 增加新的Design(设计) (18)- I -CADENCE原理图与PCB设计说明4.6 项⽬的⽬录结构 (18)第五章原理图设计 (20)5.1 图纸版⾯设置 (20)5.1.1 图纸统⼀格式设置 (20)5.1.2 栅格设置 (22)5.2Concept-HDL的启动 (23)5.3添加元件 (24)5.3.1 逻辑⽅式添加器件 (24)5.3.2 物理⽅式添加器件 (25)5.4画线 (26)5.4.1 Draw⽅式 (26)5.4.2 Route⽅式 (27)5.5 添加信号名 (27)5.6 画总线 (28)5.7 信号名命名规则 (29)5.8 元件位号 (31)5.8.1 元件位号⼿⼯标注 (31)5.8.2 元件位号的⾃动标注 (32)5.8.3 元件位号的⾃动排序 (33)5.9 Cadence属性 (34)5.10 组操作 (36)5.10.1 组定义: (36)5.10.2 组命名 (36)5.10.3 组操作 (37)5.11 常⽤命令 (38)5.11.1 常⽤的快捷键 (38)5.11.2 检查连接关系 (39)5.11.3 点画命令 (39)5.11.4 查找元件和⽹络 (39)5.11.5 两个不同⽹络名的⽹络连接的⽅法 (40)5.11.6 错误检查 (40)5.11.7 检查Cadence原理图单个⽹络名 (40)- II -⽬录5.11.8 对隐藏了电源和地腿的器件定义电源和地信号 (41)5.12 增加新的原理图页 (41)5.13 原理图多页⾯操作 (42)5.14 信号的页区位置交叉标注(Cross Reference) (42)5.14.1 信号的页区位置交叉标注(Cross Reference)的作⽤ (42) 5.14.2 交叉标注需注意的⼏点: (43)5.14.3 信号的交叉标注(Cross Refrence)的⽅法 (43)5.14.4 层次设计中出模块信号的交叉标注 (43)5.14.5 出页信号的交叉标注的要求 (44)5.15 在不同的project下实现原理图拷贝 (44)5.16 打印图纸 (47)5.17 ⾃动⽣成料单 (48)5.18 原理图归档 (50)5.19 原理图评审 (51)第六章从原理图到PCB (52)6.1从原理图到PCB的实现 (52)6.1 .1 原理图到PCB的转换过程: (52)第七章PCB设计 (55)7.1 导⼊数据 (55)7.2 Allegro⽤户界⾯ (55)7.2.1 控制⾯板的作⽤ (56)7.2.2 ⼯具栏的显⽰ (57)7.3 Layout准备 (58)7.3.1 创建PCB图的物理外形 (58)7.3.1.2 在Allegro界⾯下创建板外框: (61) 7.3.2 设置板图尺⼨参数 (62)7.3.3 设置版图的栅格值: (63)7.3.4 设置板图选项 (63)7.3.5 设置PCB板的叠层 (64)7.3.6 设置约束条件 (65)7.3.6.1 设置板的缺省间距: (65)- III -CADENCE原理图与PCB设计说明7.3.6.2 设置扩展的距离规则 (66)7.3.6.3 设置扩展的物理规则 (69)7.3.6.4 编辑属性 (69)7.3.7 可视性和颜⾊设置 (70)7.4 PCB布局 (70)7.5 PCB布线: (73)7.6 添加过孔和替换过孔 (74)7.6.1 添加过孔 (74)7.6.2 替换过孔 (75)7.7 优化⾛线 (76)7.8 覆铜处理 (77)7.8.1 阴版覆铜 (77)7.8.2 阳版覆铜 (78)7.9 分割电源平⾯ (80)7.10 位号标注 (83)7.11 加测试点 (83)7.12 DRC检查 (83)7.13 ⽣成报告⽂件 (84)7.14 V ALOR检查 (85)7.15 ⽣成光绘⽂件和钻孔⽂件 (85)7.15.1 ⽣成光圈⽂件(art-aper.txt),即D码表 (85)7.15.2 ⽣成钻孔⽂件 (86)7.15.3 ⽣成光绘⽂件 (86)7.15.3.1 在Artwork中加⼊所需的层 (86)7.15.3.2 ⽣成光绘⽂件 (90)7.16 PCB评审 (93)第⼋章公司的PCB设计规范 (94)- IV -序⾔序⾔Cadence软件是我们公司统⼀使⽤的原理图设计、PCB设计、⾼速仿真的EDA⼯具。

cadence学习笔记1--原理图的创建、查看等系列操作(持续更新)

1、亲手操作教程内容2、OrCAD Capture CIS进行原理图设计3、Cadece PCB Editor 进行PCB布局布线4、光绘文件(Artwork)制作,如何生成Gerber文件OrCAD Capture CIS与OrCAD Capture的区别元件的管理非常方便一、原理图的创建、重命名、删除1、cadence原理图的创建第一种方法:首先先选中原理图文件,然后点击菜单栏上的Design--New Schematic Page输入原理图名称第二种方法:先选中原理图文件,然后右键单击,选择New Page输入原理图名称2、删除原理图文件第一种方法:首先选择你要删除的原理图文件,然后点击菜单栏上的Edit---Delete,点击Delete之后,就会弹出下面的对话框。

点击确定之后,原理图2就删除了。

第二种方法:首先选择你要删除的原理图文件,然后鼠标右键点击Delete,如下图所示弹出如下所示,点击确定,原理图即删除。

3、cadence原理图的重命名第一种方法:选择需要更改原理图文件名的文件,然后点击菜单栏中的Design---Rename在弹出的对话框中,输入名称,点击OK即可。

第二种方法:选择需要更改原理图文件名的文件,然后右键点击Rename弹出对话框,在弹出的对话框中,输入名称,点击OK即可。

二、原理图的放大、缩小方法一: 直接按下快捷---i /o方法二:选择需要放大、缩小的原理图,然后选择菜单栏上的View---Zoom----In 放大Out 缩小方法三:按住键盘上的CTRL键,鼠标上的滑轮,向前滑动,原理图放大;向后滑动,原理图缩小。

如果原理图放的很大,可以移动滚动条进行原理图的上下左右的滚动。

也可以利用快捷键进行滚动条的移动,按住CTRL+PAGEUP,原理图向左移动;按住CTRL+PAGEDOWN,原理图向右移动;按住PAGEUP,原理图向上移动;按住PAGEDOWN,原理图向下移动。

ConceptHDL原理图设计说明

Allegro Design Entry HDL原理图输入方式海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

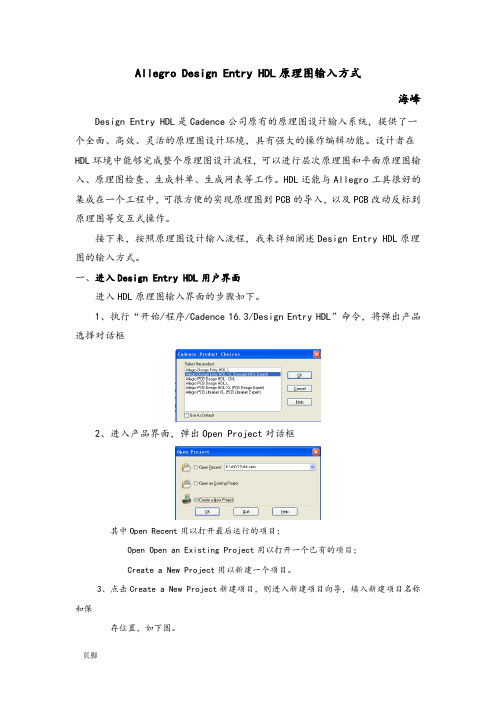

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

Cadence常用技巧、网表导入PADS、CAD板框导入

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB 设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择orPadspc.dll,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为Demo.pcb.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的Demo.pcb文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做temp.pcb.b、打开temp.pcb文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭temp.pcb。

Cadence学习笔记1__原理图

cadence学习笔记1__原理图打开Design Entry CIS或OrCAD Capture CIS组件,选择OrCAD Capture CIS(不要选择OrCAD Capture,因为少了一些东西),如果勾选了左下角的“Use as default”复选框,下次就不用选择了,如果要使用其他的部分,就在打开后点击File→Change Product,会弹出一个“Cadence Product Choices”窗口:元器件库File→New→Library新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是New Part From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCB Footprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

中间的虚线框是这个元件的区域,右边会有一个工具栏,画直线、方框、圆、曲线,也可以输入一些字符,或者点放置一组引脚,放置结束后鼠标右击选择End Mode或按键盘左上角Esc键使命令结束,放置一组引脚的时候,还可以设置引脚的类型,比如输入、输出、双向、电源等等,这个没有区分电源和地,电源和地都是power型的,现在输入下面的几个数字,线型都是默认的Passive,引脚间距Pin Spacing设为1,点击ok,放置好后成为下面的样子,有些部分不需要显示,双击空白处弹出一个属性对话框,虚框里面的数字是PinName,虚框外面的数字是PinNumber,如果可视属性改成False就不显示了。

如果想改变其中一个引脚的引脚名、引脚编号、引脚类型,选中该引脚,右击选择Edit Properties,或者双击该引脚,如下图:画直线的时候,这里默认是按照栅格点为最小单位的,可以改变这种限制,画出任意长度任意角度的线,在工具栏Options Grid Display中,不要勾选Pointer snap to grid就可以了,记得画完想要的任意直线后,再将这里勾选,这是一个好习惯,可以让画出的线更规则整齐。

[笔记]CadenceConceptHDL原理图输入

Allegro Design Entry HDL原理图输入方式00孙海峰00Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL 环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

00接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

00一、进入Design Entry HDL用户界面00进入HDL原理图输入界面的步骤如下。

001、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框002、进入产品界面,弹出Open Project对话框00其中Open Recent用以打开最后运行的项目;0Open Open an Existing Project用以打开一个已有的项目;00Create a New Project用以新建一个项目。

003、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保00存位置,如下图。

004、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库005、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可00以填写新建项目名称,也可以选择已有元件,对其进行修改。

06、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

007、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,00并出现原理图工作界面。

00其中:(1)标题栏——显示文件所在路径和文件名称;00(2)菜单栏——项目所有相关操作的集合;00包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、00模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗00口菜单和帮助菜单。

Cadence学习笔记1__原理图

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

点击左侧工具栏make图标 ,所有的横线和竖线都变成粉红色的,这就生成了一个表格,鼠标右击选择Tag Pin Name,在引脚名这一列点一下,会在这一列最上面出现“Name”,同样的,右击选择TagPin Number,在引脚编号这一列点一下,会在这一列最上面出现“Num”,如果放错了,比如说该放Name的地方放成了Num,可以在放Num之后再点一次,Num就消失了,产生的结果如上图右。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

原理图输入流程

建库 建底层单元 电路图输入 设置电路元件属性 Check & Save 生成symbol

建库

选择CIW中的菜单:File->New->Library… 指定库名、路径和工艺文件

创建基本单元

选择CIW中的File->New->Cell View… 输入单元名、ViewName、所属库

层次原理图输入

下层单元改变后要重新进行check&save 被调用单元的接口改变后,要重新生成 symbol,上层单元才会更新。 要从底向上逐层check&save 运用wire name实现成组信号线的连接

导出网表

通过CIW中的export菜单可以导出hspice格式 的电路网表; 导出的电路网表都是子电路形式电路名就是单 元的名字; 下层单元也是按照电路的层次以子电路形式描 述; 导出的网表文件不包含控制卡、模型卡,不能 直接用于分析。

添加wire name

点击wire name按钮 输入节点名 点击目标wire,放 置 Wire name相当于给 节点命名,同名节 点被认为是一个电 气节点。

加PIN

点击PIN按钮 输入名字、 input/output 单击放置Biblioteka 原理图编辑复制/移动:

点击工具栏复制/移动按钮; 单击操作对象,该对象就会粘到鼠标指针上,如果 想把几个对象作为一个整体一起移动,则要先选中 所有操作对象; 再次单击一下鼠标,放置对象。 按delete按钮, 选中要删除的对象; 或者先选中要删除的对象,然后按delete按钮。

Cadence原理图输入

清华大学微电子所 2002年8月

Cadence的文件组织

设计库

工艺库(techfile)

单元1

单元2

单元3(基本单元)

schematic

layout

symbol

schematic

symbol

symbol

Cadence工具包

icfb composer schematic virtuso layout ……

删除:

原理图编辑

Undo:点击Undo按钮,缺省只能Undo一次; 改变编辑模式:在按过功能按钮后系统会保持 相应的编辑状态,因此可以连续操作。

模式切换:按其它按钮 退出当前模式:按Esc键。 点击”Instance properties”按钮

查看、更改属性:

电路检查与保存

点击check&save按钮 错误内容:CIW窗口会显示错误说明。

基本单元有的含有参数有的是固定属性的。 电气互连:wire(narrow)/wire(wide),wire Name

单元调用

与元件放置相同——选择基本单元的 symbol 含有参数的基本单元通过“Instance properties”编辑功能设置参数。 上层单元与基本单元没有本质区别,都 是只包含下层的symbol信息 下层单元是只读的

电路图组成

Instance Wire Wire name Pin 以上元素的复制、移 动、删除操作相 同,属性编辑也相 同。

基本单元输入

基本元件:analogLib库-nmos/pmos (衬底与源端短接), nmos4/pmos4 (含衬底端)……还有basic,sample等自 带基本单元库。 器件的CDF属性对应于HSPICE模型中的 各属性,Instance Name对应网单中的元 件名,Model Name表明管子的类型。

节点悬空 输出短路 输入开路

生成symbol

选择COMPOSER的菜单:Design->Create Cellview->From Cellview… 填入库名、单元名 设置pin名称与位置

逻辑输入

调用基本单元:

基本单元往往由厂商或系统提供。 可以调用其它库中的单元(不能循环调用) 本层电路调用的是底层单元的symbol

Instance放置

点击放置按钮 ; 从Library Browser – Add Instance窗口 选择元件,View选择symbol; 调整元件姿态 输入元件属性 单击鼠标放置

Wire连接

单击wire(narrow)按钮 鼠标单击选中起始点; 再点击鼠标选中第二点; 双击——画出终点; Wire(wide)的绘制方法与此相同,二者无 本质区别。