电子科技大学数字无线电课后作业答案

电子科技大学2012年数电半期考试题参考解答

电子科技大学二零壹壹年至二零一贰学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟) 考试日期 2012年4月22日I. To fill the answers in the “( )” (2’ X 20=40) 1. [42.25 ]10 = ( 2A.4 )16 = ( 52.2 )8 .2. The binary two ’s complement is (1011), then its corresponding 8-bit two ’s complement is ( 11111011 ), and 8-bit one ’s complement is ( 11111010 ), and 8-bit signed-magnitude is ( 10000101 ).3. The 8421-BCD code is (10011000)8421-BCD ,then its corresponding decimal number is ( 98 ).4. The binary number code is (10101011)2, then its corresponding Gray code is ( 11111110 ).5. If F = ∏ABC (1,3,5),then its dual expression is =D F ∑ABC ( 2,4,6 ), and the complement expression of the function F is F ’=∑ABC ( 1,3,5)。

6. The range of 8-bit two ’s complement is (-128 ~ 127), and the range of 8-bit unsigned binary number is (0 ~ 255).7. If there are 2012 different states, we need at least ( 11 ) bits binary code to represent them.8. For the two ’s complement addition and subtraction operation, if [ A ] two’s -complement =11011011, and [ B] two’s -complement =10011111 , calculate [-A-B ] two’s -complement , [A-B ] two’s -complement , and indicate whether or not overflow occurs.[-A-B ] two’s -complement = [ 10000110 ], overflow: [ yes ] [A-B ] two’s -complement = [ 00111100 ], overflow: [ no ]9. The maximum LOW-state output current I OLmax for an HC-series CMOS gate driving CMOS inputs is 0.02mA, the maximum HIGH-state output current I OHmax is -0.02mA, and the maximum input current I Imax for an HC-series CMOS input in any states is A μ1±, the DC fanout at HIGH-state is ( 20 ).10. The unused CMOS NAND gate inputs should be tied to logic ( 1 ).11. The following logic diagram Fig.1 implements a function of 3-variable with a 74x138. The logicfunction can be expressed as F (A,B,C) =∏A,B,C ( 2, 3,4,5,7 ).Fig.112. The CMOS circuit is shown in Fig.2. Write the function of the circuit. ( F=(AB+C+D)’ )Fig.2II. There is only one correct answer in the following questions.(3’ X 10=30)1. What is the correct 2’s -complement representation of the decimal number -325?( A ) A) 1010111011 B) 1101000101 C) 1011010011 D) 10101001102. A 20-to-1 multiplexer need ( B ) selection control inputs at least.A) 4B) 5C) 6D) 203. In the 8-radix number system, the result of operation 721/20 is: ( B )A) 36.05B) 35.04C) 35.05D) 36.044. What is the duality logic function of the logic function: F = ∑ABC (0,3,5,7)( C )A),,(1,2,4,6)A B C ∑ B),,(0,2,4,7)A B C ∑ C),,(0,2,4,7)A B C ∏D),,(1,2,4,6)A B C ∏5. The inputs waveform A,B,C and output waveform F of a combinational circuit are shown as Fig.3. The canonical product-of-sums expression of this circuit is ( D )A)(),,2,3,5,7A B C∑B)(),,0,2,4,6A B C∑C) ,,(1,2,4,7)A B C ∏ D),,(0,3,5,6)A B C ∏Fig.36. For each of the following logic expressions, ( B ) is the hazard-free circuit.A) F=A’·B + A·C + B’·C B ) F=A’·B + A·C + B·C C) F=(A+B)·(B’+C)·(C+D) D) F=(A+B’)·(B+C)·(C’+D) 7. For the logic function )''()''(),,,(C B D C AB D C B A F '++=, the corresponding minimal sum is ( A ).A) A’+B+C’D’ B ) (A’+B+C’)(A’+B+D’) C) A’+B+B’C’D’ D ) A’+B+AC’D’8. The INVERTER and AND-OR-INVERTER circuits are shown as Fig.4 (a), (b) respectively, which conclusion below is correct? ( C )A) The delay between input and output of (a) circuit is much less than (b) circuit. B) The delay between input and output of (a) circuit is much greater than (b) circuit. C) The delay between input and output of (a) circuit is about same as (b) circuit. D) The delay relationship between circuit (a) and (b) is uncertainty.Fig.4 (a)Fig.4 (b)9. The circuit shown in Fig.5 realize a logic functin F about input variable W, X, Y . Then, the Fis:( A )A) F=,,,(0,1,3,7,9,13,14)w x y z ∑B) F=,,,(0,2,5,7,9,13,14)w x y z ∑C) F=,,,(0,1,3,7,8,12,15)w x y z ∑D) F=,,,(1,2,5,7,9,12,15)w x y z ∑Fig.510. Which of the following statements are NOT correct about logic function? ( D ) A) There are multi-expressions of a logic function ’s minimal sum. B) The canonical sum of a circuit is a sum of minterms.C) Any logic function can be expressed using a sum of minterms or a product of maxterms. D) A sum of prime implicants must be the logic function ’s minimal sum. III. Combinational Circuit Analysis And Design: [30’]1.Write the truth table and the logic function performed by the CMOS circuit in Figure 6. (7’)Fig.6Solution :Z=S ’A+SB评分标准:真值表正确 4 分, 错一个扣0.5分;表达式正确 3分。

数字无线电技术 电子科技大学 电子工程学院 严禁转载 绝密 2015期末考试

其中,zBI (t)就是 I 信号,zBQ (t)就是 Q 信号。 因此,由已调信号 x(t)获得基带信号 zBI (t)、zBQ (t)后,其幅度、相位或频率 的调制信息可通过运算获得:

a (t ) = Re 2 [ z (t )] + Im 2 [ z (t )] = x 2 (t ) + H 2 [ x(t )]

电视伴音 6.5MHz/ 100kHz 滤 波 陶瓷 混 频

300MHz/ 1MHz 滤 波 晶体 本振 1 293.5MHz 本振 2 混 频

210~230MHz/ 20MHz 滤 波 功

放

数据 输入 19.2kbps

载波 6.5MHz

510~530MHz

(b)

发射端结构 2

基本概念: 信源数字化 信道数字化 信道软件化 → → → 无线数字通信 数字无线电 软件无线电

z (t ) = a (t )e j[ω0t +φ (t )] = a (t )e jφ (t ) ⋅ e jω0t = z B (t ) ⋅ e jω0t

ZB(t)为基带调制信号

z B (t ) = z (t ) ⋅ e − jω0t = a (t ) ⋅ e jφ (t ) ⋅ e jω0t ⋅ e − jω0t = a (t ) cos[φ (t )] + ja (t ) sin[φ (t )] = z BI (t ) + jz BQ (t )

第一讲

无线电系统与结构

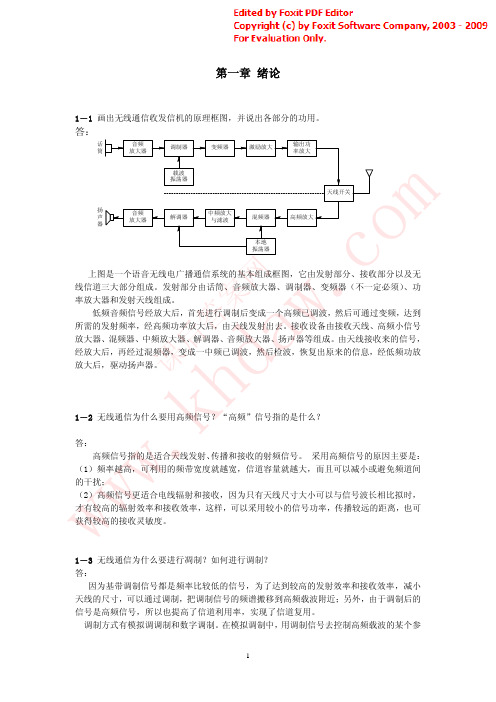

一、典型的无线电应用系统 1.无线电广播、电视、电报系统 2.无线电对讲、差转系统 3.无线电移动通信系统 4.无线电导航系统(航海、航空、航天) 5.无线电探测系统(雷达:单/多基、陆/海/空/天基)

二、无线电应用系统 1.单工无线电接收机的设计 案例 1:中波调幅收音机的设计 参数: 射频频率:800kHz; 信号带宽:10kHz; 调制方式:AM。 (1) 直放式

通信原理_电子科技大学中国大学mooc课后章节答案期末考试题库2023年

通信原理_电子科技大学中国大学mooc课后章节答案期末考试题库2023年1.数字传输信号的功率谱与码元传输波形有关,也与波特率有关。

参考答案:正确2.某数字基带系统总的传输特性为升余弦滚降滤波器,其带宽为10 MHz,下面哪些数据速率的二元信号通过该系统,不会产生码间干扰。

参考答案:20 Mbps_15 Mbps_10 Mbps3.匹配滤波器输出的最大信噪比与下面哪些因素有关?()参考答案:接收信号波形能量_信道噪声功率谱密度4.某带通信号,其中心频率为30 MHz,信号带宽为6 MHz,则该信号无频谱重叠的最低采样频率为()MHz。

参考答案:13.25.对典型语音信号进行PCM抽样的频率通常采用()。

参考答案:8000 Hz6.对于DPSK信号,下列说法正确的是()。

参考答案:相干检测系统性能稍优于非相干检测系统_可以解决相移键控中的“相位模糊”问题7.某八元数字基带传输系统的传输比特速率为4500 bps。

则该系统的码元速率是()。

参考答案:1500 Baud8.无码间干扰基带传输系统的传输特性是滚降系数为0.5的升余弦滚降滤波器,传输码元速率为1200 Baud。

则该系统的截止带宽为()。

参考答案:900 Hz9.当0、1码等概率出现时,下列信号中,具有多条离散谱线的信号是。

参考答案:单极性RZ信号10.角调信号接收的关键是将加载在载波相位中的消息信号转换为蕴含消息信号的幅度调制信号,之后再进行幅度调制解调。

参考答案:正确11.SSB信号通常使用相干解调法进行接收。

参考答案:正确12.日常生活中,收音机通常采用哪两种调制方式?()参考答案:AM_FM13.对DSB-SC调制与常规AM调制的差异性描述正确的是()。

参考答案:DSB-SC的调制效率比常规AM高_对于相同的调制信号,DSB-SC信号的带宽与常规AM信号相同14.系统的输出信噪比是模拟通信系统的()指标。

参考答案:可靠性15.对于调制指数为0.5的AM信号,以下说法正确的是()。

信号与系统课后习题答案(西安电子科技大学)

因此: ⎪⎨x′(t) = y′(t)

即: y′′(t) + 3y′(t) + 2 y(t) = f (t)

⎪⎩x′′(t) = y′′(t)

(d)系统框图等价为:

1.19 设系统的初始状态为 x1(·)和 x2(·),输入为 y(·),完全响应为 y(·),试判断下 列系统的性质(线性/非线性,时变/时不变,因果/非因果,稳定/不稳定)。

−p i2 (t) = 3 p

−p −p

f (t) −p −1 1+ p

−1 −p

=

− p(2 p2 + 3 p + 3) / p − ( p3 + 2 p2 + 2 p + 3)

f (t) =

p(2 p2 + 3 p + 3) f (t) p( p3 + 2 p2 + 2 p + 3)

t

Qτ → 0, f (t) → δ (t)

∫ ∫ ∫ ∴ ∞ f (t)dt = 2K ∞ sin t /τ dt = 2K ∞ sin t /τ d (t /τ ) = −2Kπ = 1

−∞

−∞ t

−∞ t /τ

⇒ K = 1/ 2π

解:(3) f (t) = Ae j5t = A(cos 5t + j sin 5t) ω = 5,T = 2π / ω = 2π / 5

=6+27e-t 十 2e-3t,t≥0 1.26 设有一线性时不变系统,当输入波形如图(a)所示时,系统的零状态响应 yf(t)如图 (b)所示。 (a)试画出输入为 2f(t+4)时,系统零状态响应 yf(t)的波形; (b)画出输入波形如(c)时,系统零状态响应 yf(t) 的波形.

电子科技大学微电子器件 (习题解答)

s Emax

qND

在

x

xi2 处,E3

Emax

q

s

NA xp

,

由此得:xp

s Emax

qNA

(2) 对于无 I 型区的PN结,

xi1 0,

xi2 0,

E1

q

s

ND (x

xn ),

E3

q

s

NA(x

xp )

在

x

0 处,电场达到最大, Emax

q

s

ND xn

q

s

NA xp

E

Emax

E1

E3

x

0

表面上,两种结构的 Emax 的表达式相同,但由于两种结构 的掺杂相同,因而Vbi 相同(即电场曲线与横轴所围面积相同), 所以两种结构的 xn、xp与 Emax 并不相同。

WB

dWB dVCE

0 NBdx

IC VA

WB

VA 0 NBdx

N

B

(WB

)

dWB dVCE

对均匀基区,VA

WB dWB dVCE

式中,dWB dxdB , VCE VCB VBE

因

VBE

保持不变,所以 dVCE

dVCB ,

于是:VA

WB dxdB dVCB

1

xdB

2s N

2DB n

,

将n

106 s 及 WB 、DB

之值代入,得: 0.9987。

7、

b

WB2 2DB

2

1

1

1.1251011(s)

8、以 NPN 管为例,当基区与发射区都是非均匀掺杂时, 由式(3-33a)和式(3-33b),

电子技术应用实验(数字电路综合实验)_电子科技大学中国大学mooc课后章节答案期末考试题库2023年

电子技术应用实验2(数字电路综合实验)_电子科技大学中国大学mooc课后章节答案期末考试题库2023年1.用数字示波器双踪测量不同频率的相关信号时,应选哪个信号为触发源?参考答案:频率低的信号2.约束文件中“set_property PULLDOWN true [get_ports {col[3]}]”是?参考答案:将第3列下拉至低电平3.若工程中只使用矩阵键盘中的一个按键,则参考答案:可以不需要按键扫描4.在本次实验示例中,将行列式键盘的行值定义为参考答案:输出信号5.如果要求不仅能显示16进制数,还要包括"-",那么显示译码器接收的数据至少应为参考答案:5位6.实现6位数码管动态显示16进制数时,可以不改写哪部分的代码?参考答案:显示译码器部分7.如果你要在一个工程中添加自定义的IP核,首先应在Project manager中点击参考答案:Settings8.IP核的意思是参考答案:知识产权核9.如果实现5位数码管动态显示,则电路中计数器的位数至少为参考答案:310.所介绍的555多谐振荡器电路中,振荡周期的改变与()有关。

参考答案:电容C_电阻R2_电阻R111.所介绍的555多谐振荡器电路中,占空比的改变与()无关。

参考答案:电容C12.对于本次实验中的多谐振荡器电路,若要实现其输出矩形波的振荡频率约为160Hz,占空比约为89%。

所选择的电阻R1和R2的比值约为()。

参考答案:7:113.对于本次实验中的多谐振荡器电路,若要实现其输出矩形波的振荡频率约为4700Hz,可供选择的电阻R1和R2值约为10千欧姆,则电容C应选取()。

参考答案:0.01微法14.所介绍的555多谐振荡器电路中,当VCC(引脚8端)为9V,电压控制端(引脚5)悬空,则该多谐振荡器Vc(2、6脚)处三角波的幅度大约为()。

参考答案:3V15.用视频中介绍的方法产生占空比为50%的分频信号输出,将50MHz信号分频为2KHz,如果计数器计数值从0依次加一到999循环,那么输出频率为?参考答案:25KHz16.假如clr是清零端,通过语句always@(posedge CP or posedge clr),可以知道clr是哪一种清零?参考答案:异步清零17.在过程块中哪种赋值语句必须按照编写顺序依次执行?参考答案:阻塞式赋值18.非阻塞式赋值的赋值运算符是?参考答案:<=19.在always块中,应该采用哪种赋值?参考答案:过程赋值20.在verilog语言中,下面哪个符号不能用作设计源文件或约束文件里的注释符号?参考答案:*21.本实验中门电路构成的单稳触发器输出信号的脉冲幅度和以下哪些因素有关?参考答案:门电路的电源电压_最后一个与非门的器件类型22.根据实验电路中给出的参数,这个单稳触发器最大定时时间可能是?参考答案:约4uS23.本实验中门电路构成的单稳触发器电路对输入信号的触发条件为?参考答案:下降沿触发24.施密特触发器和单稳态触发器都可以对脉冲实现整形,这两种电路对脉冲整形后,那种电路可以得到相同的脉宽?参考答案:单稳态触发器25.在Verilog语言中关于if-else语句说法不正确的是?参考答案:有一条if语句就有一条对应的else语句26.实验开发板的时钟为50MHZ,实验中要求设计的计数器时钟为5HZ,则分频器的分频比应为多少?采用实验介绍的分频方法,verilog语句中的分频计数范围应设为多少?参考答案:10M, 0~499999927.在本实验内容一的顶层模块连接图中,对应模块u2正确的例化语句应该是?参考答案:counter10 u2(。

西安电子科技大学数字电路基础参考答案

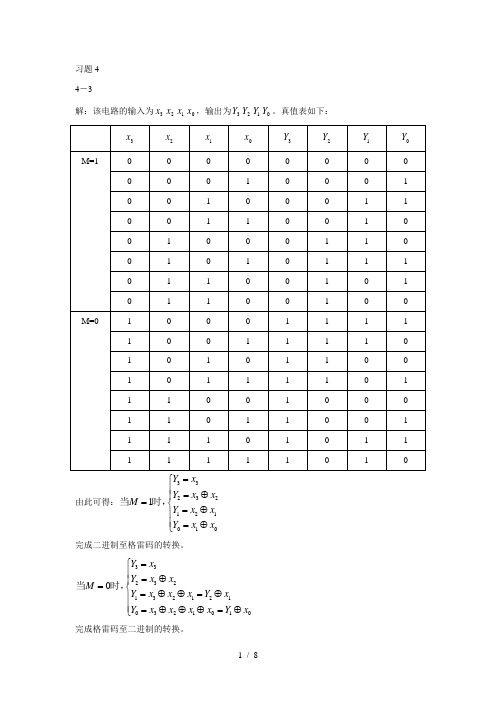

习题4 4-3解:该电路的输入为3x 2x 1x 0x ,输出为3Y 2Y 1Y 0Y 。

真值表如下:由此可得:1M =当时,33232121010Y x Y x x Y x x Y x x =⎧⎪=⊕⎪⎨=⊕⎪⎪=⊕⎩ 完成二进制至格雷码的转换。

0M =当时,332321321210321010Y x Y x x Y x x x Y x Y x x x x Y x =⎧⎪=⊕⎪⎨=⊕⊕=⊕⎪⎪=⊕⊕⊕=⊕⎩ 完成格雷码至二进制的转换。

4-9 设计一个全加(减)器,其输入为A,B,C 和X(当X =0时,实现加法运算;当X =1时,实现减法运算),输出为S(表示和或差),P (表示进位或借位)。

列出真值表,试用3个异或门和3个与非门实现该电路,画出逻辑电路图。

解:根据全加器和全减器的原理,我们可以作出如下的真值表:由真值表可以画出卡诺图,由卡诺图得出逻辑表达式,并画出逻辑电路图:A B C XP4-10 设计一个交通灯故障检测电路,要求红,黄,绿三个灯仅有一个灯亮时,输出F =0;若无灯亮或有两个以上的灯亮,则均为故障,输出F =1。

试用最少的非门和与非门实现该电路。

要求列出真值表,化简逻辑函数,并指出所有74系列器件的型号。

解:根据题意,我们可以列出真值表如下:对上述的真值表可以作出卡诺图,由卡诺图我们可以得出以下的逻辑函数:F AB AC BC ABC AB AC BC ABC =+++=∙∙∙逻辑电路图如下所示:A F4-13 试用一片3-8译码器和少量逻辑门设计下列多地址输入的译码电路。

(1) 有8根地址输入线7A ~1A ,要求当地址码为A8H,A9H ,…,AFH 时,译码器输出为0Y ~7Y 分别被译中,且地电平有效。

(2) 有10根地址输入线9A ~0A ,要求当地址码为2E0H,2E1H, …,2E7H 时,译码器输出0Y ~7Y 分别被译中,且地电平有效。

解:(1)当122100A BE E E =,即75364210111,00,A A A A A A A A ==从000~111变化时07~Y Y 分别被译中,电路如下图所示:Y Y (2)当122100A B E E E =,即97538432101111,000,A A A A A A A A A A ==从000~111变化时,07~Y Y 分别被译中。

《高频电路原理与分析》第四版西安电子科技大学课后答案

kh da w. co m

H0 = R

∞ 0

解 2-7:

题 2-8 图

解 2-8: 此题中主要噪音来自二极管的散粒噪音,因此

流过二极管的电流为 E-VD 9.3 = = 0.465mA, I0 = 20000 R 26mV 二极管电阻为RD = ≈ 56Ω I0 网络传输函数为 H(j ω ) = 1 1 + jω C R // RD ≈ 1 1 + jω C RD = RD , 1 + jω CRD H 0 = RD

1 1 109 = = = 88464260 2πf0Crq 2π × 5 × 103 × 0.024 × 10−12 × 15 3.6π

后

=

答

答 2-4: 石英晶体有以下几个特点 1. 晶体的谐振频率只与晶片的材料、尺寸、切割方式、几何形状等有关,温度系数非 常小,因此受外界温度影响很小 2. 具有很高的品质因数 3. 具有非常小的接入系数,因此手外部电路的影响很小。 4. 在工作频率附近有很大的等效电感,阻抗变化率大,因此谐振阻抗很大 5. 构成震荡器非常方便,而且由于上述特点,会使频率非常稳定。

答

案 网

7

=∫

∞

1 1 df = ∫ df 2 1 + (ω CRD ) 1 + (2π fCRD )2 0

∞

(1)采用额定功率法

⎛ ⎞ R3 Es ⎟ ⎜ R + R1 + R3 ⎠ =⎝数N F =

E s2 , 4 Rs

输出匹配功率Psmo

2

Psmi R0 ⎛ Rs + R1 + R3 ⎞ = ×⎜ ⎟ Psmo Rs ⎝ R3 ⎠

w.

课

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

答案: 1)数字下变频器:

zBI(n)

cos(3n/2) 0,-1,0,1,0

NCO

x(t

)

A/D

x(n

)

RT DSP

1,0,-1,0,1 -sin(3n/2)

fS=30MHz zBQ(n)

NCO

频 率 :

2

22.5MHz 3 30MHz 2

, 注 意 , 也 可 以

2

7.5MHz ,但上图中 sin(3 n / 2) 要变为 sin( n / 2) 。 30MHz 2

15MHz = 30 ,但考虑到 DLPF 的过渡带(若抽取 0.5MHz

2)三级抽取倍数和 CIC 滤波器的展开结构 最大可抽取倍数 Dmax

D 7 2 2 , D1 7 , D2 2 , D3 2 。

对于第一级抽取滤波器,其 c 2 0.5 / 30 / 30 a 2 / 7 0.29 , 因此可选择 7 倍抽取 CIC 滤波器作为抽取滤波器。 为降低 CIC 滤波器的主副比, 利用 5 级级联 CIC 滤波器, 则主副比达到 67.3dB 。

30 倍,则最后一级抽取后信号采样频率将变为 1MHz。由于基带信号的最高频率 为 0.5MHz, 在采样频率为 1MHz 的情况下, 要求 DLPF 是理想滤波器, 但实际 DLPF 有过渡带,因此不能使用刚好是 0.5MHz 两倍的采样频率。 ) ,抽取倍数选为

D 28 (抽取倍数为 29 时,将无法设计三级抽取方式) ,将抽取倍数分 14.36 (1/ 2 7 /15)

输出对应的其 c 2 7 / 30 7 /15 抽取后的采样频率为: f s3 30 /14MHz = 15 / 7MHz 第三级抽取 D3 2 ,用半带滤波器,其 c 7 /15 , a 8 /15 输出对应的其 c 2 7 /15 14 /15 抽取后的采样频率为: f s 4 30 / 28MHz = 15 /14MHz HB 滤波器过渡带混叠严重,最后加一级 FIR 滤波器 第四级 FIR 滤波器 c 14 /15 ,a=,取纹波系数=0.001 则其阶数为:

作业 4: 输入采样率 30MHz 的中频信号,设计一个数字下变频器,将中心频率 52.5MHz, 带宽 1MHz 的信号正交解调至基带,选择 CIC 滤波器,半带滤波器和 FIR 滤波器 作三级抽取,输出最低的数据率。 1)画出下变频器结构; 2)设计三级抽取的倍数,画出 CIC 滤波器的展开结构; 3)画出各级滤波器的频谱图。

z 1

z 1

z 1

z 1

x(n1 )

2

x '(n2 )

抽取后的采样频率为: f s 2 30 / 7MHz 对 于 第 二 级 抽 取 D2 2 , 用 半 带 滤 波 器 , 其 c 2 3.5 / 30 7 / 30 ,

a c 23 / 30 。