Xilinx ISE 6[1].2实验指导

3 Xilinx_ISE 应用I

// 灯闪烁

assign led_out = counter[3:0]; // 仿真时将counter的低4位传给led_out以提高频率,加快仿真速度 assign led_out = counter[26:23]; // 实际下载时将counter的高4位传给led_out以降低频率,看到led

2.创建新的Verilog源

生成的top.v文件

添加代码到top.v文件中

2.创建新的Verilog源

实验代码如下:

////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 12:07:24 06/21/2011 // Design Name: // Module Name: led // //////////////////////////////////////////////////////////////////////////////////

4 设计仿真

(1) 点击led HDL 文件,创建一个新 的测试平台源文件: Project New Source.在源文件 向导里, 点击 Verilog Test Fixture 作为源文 件类型, 输入文件 名称为test.

4 设计仿真

(2) 一直点击next,直 到点击finish,自动生 成test.v的测试模板, 在此基础上编辑输入激 励:时钟周期设定为 10ns,复位信号为高 持续500ns后,再将复 位信号置低。

四、Xilinx开发板Basys2介绍

四、Xilinx开发板Basys2介绍

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

(ISE使用流程)逻辑设计实验

实验一ISE工具的使用流程--拨码开关控制LED实验1.1 实验目的1.学会ISE的基本开发流程和常用功能的使用,本实验直接使用新建一个拨码开关控制led 实验来作为设计文件,通过ise 综合、映射、布局布线后,生成FPGA位流配置文件,通过JTAG口对开发板上FPGA进行配置。

2学会最基本拨码开关和led 工作原理。

1.2 实验原理1.实验开发板的拨码开关向上拨动时处于低电平,向下处于高电平,用此来控制LED灯。

2.LED灯的的一端已经接高电平,另一端接FPGA的IO口,因此当IO输出低电平是便可点亮LED灯,否则LED为暗。

3.按键默认为高电平,按键按下时接地为低电平来检测按键的按下的复位信号。

1.3 实验步骤1.打开ISE应用程序,进入图形化界面图表 12.点击File->New project,在弹出的对话框中设定工程和工程路径,用HDL源码,NEXT图表 23.选定器件和封装,点击NEXT.图表 34.在工程中创建源文件,选择New Source.,选中Verilog Module,输入源文件名称图表 45.可在弹出的对话框中输入信号的输入输出定义,也可暂时不定义图表 56.点击下一步,点击finish,然后自动回到creat a new source 对话框,点击下一步,再击下一步,然后点击finish 。

图表 66.点击设计的源文件,然后整个界面如图所示图表77.将鼠标置于输入输出的下方,点击工具栏中的,然后进入各子目录选择如下,这是一个快捷操作模板。

右键use in file,可在源文件中看到已经添加相应的模板,然后修改一些端口、添加内容完善整个工程设计。

图表88.写源文件的代码如下module key_led(clk, key, reset_n, led);input clk;input key;input reset_n;output led;reg led;// Usage of asynchronous resets may negatively impact FPGA resources// and timing. In general faster and smaller FPGA designs will// result from not using asynchronous resets. Please refer to// the Synthesis and Simulation Design Guide for more information.always @(posedge clk or negedge reset_n)if (!reset_n) beginled <= 1;endelse beginif(key==0)led <=0;elseled <=1;endendmodule可用design Utilities点击create schematic symbol下观看所生成的原理图来分析电路的性能。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

Xilinx ISE 大学计划使用教程PPT 2

北京中教仪装备技术有限公司

KCPSM3 汇编器

--constant.txt文件和labels.txt文件

这两个文件提供了行标号的列表和它相关的地址, 以及常数的列表和值.

北京中教仪装备技术有限公司

KCPSM3 汇编器

--pass.dat文件

pass.dat文件是汇编器的 内 部文件,用来表示汇编过程中 的中间步骤.这些文件可不去 理会,但能帮助识别汇编器如 何理解(翻译)程序的.当开 始汇编时,这些文件自动删 除.

KCPSM3编程语法 编程语法

--ADDRESS指令

ADDRESS强迫指令在给定地址执行.

LOG文件给出的描述.

北京中教仪装备技术有限公司

KCPSM3中断处理 中断处理

--中断使能

使用ENABLE INTERRUPT指令来使能中断.当不 允许中断时,使用DISABLE INTERRUPT来禁止中断. 使用RETURNI ENABLE/DISABLE指令来从中断返回主 程序. 当中断产生时,进行下面的步骤: 1)将程序计数器入栈,保护CARRY和ZERO标志; 2)禁止中断输入; 3)程序计数器的值为"3FF".

KCPSM3 CALL/RETURN栈 栈

--调用和返回处理过程

PicoBlaze包含一个自动的嵌入式的堆栈,用来 当遇到CALL指令时保存PC的值,在遇到RETURN(I) 是恢复PC的值.堆栈不需要初始化(或者用户的控 制).然而堆栈只支持到最多31级的嵌套的子程序. 下面给出一个例子来说明这个问题.

北京中教仪装备技术有限公司

KCPSM3输出端口的设计 输出端口的设计

--简单输出端口

北京中教仪装备技术有限公司

ISE实用指导书

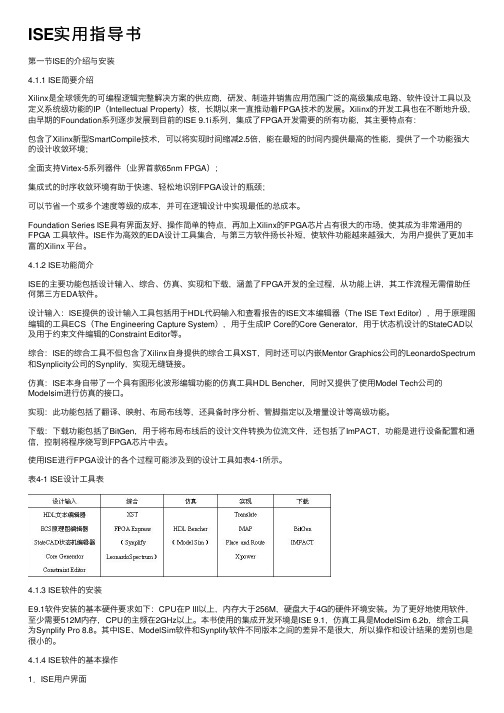

ISE实⽤指导书第⼀节ISE的介绍与安装4.1.1 ISE简要介绍Xilinx是全球领先的可编程逻辑完整解决⽅案的供应商,研发、制造并销售应⽤范围⼴泛的⾼级集成电路、软件设计⼯具以及定义系统级功能的IP(Intellectual Property)核,长期以来⼀直推动着FPGA技术的发展。

Xilinx的开发⼯具也在不断地升级,由早期的Foundation系列逐步发展到⽬前的ISE 9.1i系列,集成了FPGA开发需要的所有功能,其主要特点有:包含了Xilinx新型SmartCompile技术,可以将实现时间缩减2.5倍,能在最短的时间内提供最⾼的性能,提供了⼀个功能强⼤的设计收敛环境;全⾯⽀持Virtex-5系列器件(业界⾸款65nm FPGA);集成式的时序收敛环境有助于快速、轻松地识别FPGA设计的瓶颈;可以节省⼀个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

Foundation Series ISE具有界⾯友好、操作简单的特点,再加上Xilinx的FPGA芯⽚占有很⼤的市场,使其成为⾮常通⽤的FPGA ⼯具软件。

ISE作为⾼效的EDA设计⼯具集合,与第三⽅软件扬长补短,使软件功能越来越强⼤,为⽤户提供了更加丰富的Xilinx 平台。

4.1.2 ISE功能简介ISE的主要功能包括设计输⼊、综合、仿真、实现和下载,涵盖了FPGA开发的全过程,从功能上讲,其⼯作流程⽆需借助任何第三⽅EDA软件。

设计输⼊:ISE提供的设计输⼊⼯具包括⽤于HDL代码输⼊和查看报告的ISE⽂本编辑器(The ISE Text Editor),⽤于原理图编辑的⼯具ECS(The Engineering Capture System),⽤于⽣成IP Core的Core Generator,⽤于状态机设计的StateCAD以及⽤于约束⽂件编辑的Constraint Editor等。

综合:ISE的综合⼯具不但包含了Xilinx⾃⾝提供的综合⼯具XST,同时还可以内嵌Mentor Graphics公司的LeonardoSpectrum 和Synplicity公司的Synplify,实现⽆缝链接。

ISE的使用说明

ISE的使用说明ISE(Integrated Software Environment)是一种集成软件环境,用于设计和验证硬件开发项目。

它由Xilinx公司开发,旨在为FPGA(Field-Programmable Gate Array)和SoC(System-on-a-Chip)设计提供完整的解决方案。

ISE具有多种功能和工具,可以帮助工程师在整个开发过程中完成各种任务。

ISE的安装:ISE的主要功能:ISE为硬件设计和验证提供了全面的解决方案。

以下是ISE的主要功能:2.综合和优化:ISE包含了综合和优化工具,将HDL代码转换为布尔函数表示。

综合工具会分析代码并生成等效的硬件电路电路。

优化工具会尝试将电路改进为更有效的形式,以提高性能和减少资源消耗。

3.约束和分析:在设计过程中,您通常需要对硬件进行约束,以满足特定的要求。

ISE提供了工具来定义时序约束、电气约束和物理约束,并分析设计是否满足这些约束。

4.实现和布局:一旦设计和优化完成,ISE将使用实现和布局工具将电路映射到目标FPGA或SoC中。

这些工具将选择适当的逻辑资源,并将其布局在特定的芯片区域,以最大程度地提高性能和效率。

5.仿真和调试:在设计过程中,您需要对硬件进行仿真和调试,以验证其正确性和性能。

ISE提供了仿真工具,可以对设计进行功能仿真、时序仿真和混合信号仿真。

它还提供了调试功能,可帮助您定位和解决问题。

以下是使用ISE的一般步骤:1.创建新工程:在ISE中,您需要先创建一个新的工程,用于存储和组织设计文件。

可以在ISE中创建一个新的工程,并选择适当的目标设备。

2. 添加设计文件:一旦工程创建完成,您可以添加设计文件到工程中。

通过右键单击工程文件夹,并选择“Add Source”来添加设计文件。

选择适当的文件类型,并在文件对话框中选择要添加的文件。

3. 设置约束:在设计过程中,您需要为硬件设计设置约束,以满足特定的要求。

通过右键单击工程文件夹,并选择“Add Constraints”来添加约束文件。

Xilinx_ISE使用教程

Next

--主要功能

ISE的主要功能包括设计输入、综合、仿真、实现和 下载,涵盖了可编程逻辑器件开发的全过程,从功能上 讲,完成CPLD/FPGA的设计流程无需借助任何第三方 EDA软件。下面简要说明各功能的作用: 1、设计输入:ISE提供的设计输入工具包括用于 HDL代码输入和查看报告的ISE文本编辑器(The ISE Text Editor),用于原理图编辑的工具ECS(The Engineering Capture System),用于生成IP Core的Core Generator,用于状态机设计的StateCAD以及用于约束文 件编辑的Constraint Editor等。

Xilinx公司ISE10.1软件介绍

--ISE设计流程

规划 和预算 创建代码/ 原理图 HDL RTL 仿真

实现

翻译 映射 布局和布线 得到时序收敛 功能仿真 综合以创建网表

时序仿真

产生.1软件介绍

--ISE主界面

Xilinx公司ISE10.1软件介绍

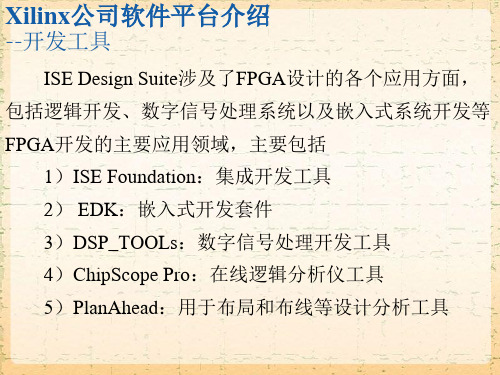

Xilinx公司软件平台介绍

--DSP_Tools软件

Xilinx公司推出了简化FPGA数字处理系统的集成开 发工具DSP Tools,快速、简易地将DSP系统的抽象算法 转化成可综合的、可靠的硬件系统,为DSP设计者扫清 了编程的障碍。DSP Tools主要包括System Genetator和 AccelDSP两部分,前者和Mathworks公司的Simulink实现 无缝链接,后者主要针对c/.m语言。

--创建一个新工程

新建文件 的类型, 不同的类 型有着不 同的功能 和意义。

该文 件的 实体 名

Xilinx公司ISE10.1软件设计流程介绍

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一EDA软件实验实验性质:验证性实验级别:必做开课单位:信息与通信工程学院通信工程系学时:4学时一、实验目的:1、了解Xilinx ISE 6.2软件的功能。

2、掌握Xilinx ISE 6.2的VHDL输入方法。

3、掌握Xilinx ISE 6.2的原理图文件输入和元件库的调用方法。

4、掌握Xilinx ISE 6.2软件元件的生成方法和调用方法。

5、掌握Xilinx ISE 6.2编译、功能仿真和时序仿真。

6、掌握Xilinx ISE 6.2原理图设计、管脚分配、综合与实现、数据流下载方法。

7、了解所编电路器件资源的消耗情况。

二、实验器材:计算机、Quartus II软件或xilinx ISE三、实验内容:1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 6.2软件平台上完成设计电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。

下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 6.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

四、实验步骤:4.1 Xilinx ISE 6.2环境1、三线八线译码器(74LS138)VHDL电路设计(1)、三线八线译码器(74LS138)的VHDL源程序的输入打开Xilinx ISE 6.2编程环境软件Project Navigator,执行“file”菜单中的【New Project】命令,为三线八线译码器(74LS138)建立设计项目。

项目名称【Project Name】为“Shiyan”,工程建立路径为“C:\Xilinx\bin\adder8”,其中“顶层模块类型(Top-Level Module Type)”为硬件描述语言(HDL),如图1所示。

图1点击【下一步】,弹出【Select the Device and Design Flow for the Project】对话框,在该对话框内进行硬件芯片选择与工程设计工具配置过程。

各标签具体含义如下:●【Device Family】:定义所选芯片器件族●【Device】:定义器件名●【Package】:定义器件封装形式●【Speed Grade】:定义芯片工作速度等级●【Top-Level Module Type】:定义顶层模块类型●【Synthesis Tool】:定义综合工具●【Simulator】:定义仿真测试工具●【Generated Simulation Language】:定义硬件描述语言针对本试验所用开发板我们选择“CoolRunner2 CPLDs”系列的“XC2C256-7PQ208”器件作为目标芯片进行仿真,如图2所示。

图2完成具体选择后点击【下一步】弹出如图3所示对话框,在该对话框内创建文件资源。

图3打开【New Source】标签,弹出如图4所示对话框,在左侧方框中包含了用户可以创建的文件类型,包括以下内容:●【Schematic】:原理图类型文件●【State Diagram】:状态图类型文件●【Test Bench Waveform】:波形类型测试文件●【User Document】:用户类型文件●【Verilog Module】:Verilog类型文件●【Verilog Test Fixture】:Verilog语言描述类型测试文件●【VHDL Library】:VHDL库文件●【VHDL Module】:VHDL类型模块文件●【VHDL Package】:VHDL类型文件封装库●【VHDL Test Bench】:VHDL语言描述类型测试文件图4在【File】标签下对话框内写入用户自定义的文件名称,标签【Locatior】下显示了新定义文件的创建路径,选中标签【Add to proje】前的对号标记,将新创建的文件adder8添加到工程“Shiyan”中。

点击【下一步】,弹出如图5所示对话框,在此对话框中输入三线八线译码器(74LS138)的的端口信息。

图5点击【下一步】弹出【New Source Information】对话框,在该对话框内显示了新建文件的属性及信息,如图6所示。

图6点击【完成】返回资源创建对话框,其中显示了新建文件“LS74138.vhdl”,如图7。

图7点击【下一步】弹出工程信息对话框【New Project Information】,该对话框给出了所设计的工程信息,如图8所示。

图8点击【完成】标签结束新建工程过程。

进入Xilinx ISE文本编辑方式,在文本框中编辑输入8位加法器的VHDL源程序,如下图所示:图2(增加ELSE 语句否则产生寄存器)在VHDL源程序中,G1和G2为两个使能控制信号,INP为命令码输入信号,Y为8位译码输出信号。

(2)、设计文件存盘与语法检查图13 图14完成程序代码输入后单击高亮“ls74138-behavioral(LS74138.vhdl)”标签(图13),此时工具窗口将显示“Process for Source(ls74138-behavioral)”。

用鼠标右键点击Process窗口中【Check Syntax】标签,点击运行选项,进行程序语法检查,当显示一绿色对号标志时即表示程序中不存在语法问题,如图14所示。

(3)、仿真文件设计为了验证所设计电路功能,需要输入测试文件对电路程序功能进行测试。

在【Process】菜单中选择【New Source】选项,即可弹出如图5所示对话框,选择【VHDL Test Bench】添加测试向量文件,并将文件添加到LS74138模块中,如图15所示图15 图16运行行为仿真选项卡,Xilinx ISE自动调用ModelSim SE 6.1c仿真平台作为仿真工具。

运行ModelSim SE 6.1c菜单【Simulate】->【Run】->【Restart】,将仿真时间点置零。

在【transcript】窗口中输入仿真时间。

在波形【Wave】窗口内使用按钮实现仿真图的“放大”“缩小”“全局”功能。

图17即为电路仿真结果,由图中时序及逻辑关系可知该三线八线译码器行为仿真正常。

图17测试向量参考程序如下:LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.numeric_std.ALL;ENTITY ls74138_tb_74138_vhd_tb ISEND ls74138_tb_74138_vhd_tb;ARCHITECTURE behavior OF ls74138_tb_74138_vhd_tb ISCOMPONENT ls74138PORT(G1 : IN std_logic;G2 : IN std_logic;INP : IN std_logic_vector( 2 downto 0);Y : OUT std_logic_vector(7 downto 0));END COMPONENT;SIGNAL G1 : std_logic;SIGNAL G2 : std_logic;SIGNAL INP : std_logic_vector( 2 downto 0);SIGNAL Y : std_logic_vector(7 downto 0);BEGINuut: ls74138 PORT MAP(G1 => G1,G2 => G2,INP => INP,Y => Y);-- *** Test Bench - User Defined Section ***u1:PROCESSBEGING1<='0';wait for 10us;G1<='1';wait for 90us;G1<='0';wait;END PROCESS u1;u2:PROCESSBEGING2<='0';wait for 10us;G2<='1';wait for 90us;G2<='0';wait;END PROCESS u2;u3:PROCESSBEGININP<="000";wait for 20us;INP<="001";wait for 10us;INP<="010";wait for 10us;INP<="011";wait for 10us;INP<="100";wait for 10us;INP<="101";wait for 10us;INP<="110";wait for 10us;INP<="111";wait;end PROCESS u3;-- *** End Test Bench - User Defined Section *** END;(4)芯片管脚定义如前所述添加用户定义限制文件,运行【Assign Package Pins】选项卡,Xilinx ISE将弹出管脚分配窗口,在如图19,输入各个端口管脚位置并保存,完成芯片管脚定义。

图18 图19(5)编译与综合图20 图21运行【Process for Source】中的【Implement Design】(图20),ISE将自动完成编译并调用内嵌的综合工具XST完成综合过程,运行结果如图21所示。

编译通过后即自动生成了电路烧录下载文件(*.jed)以及资源消耗报告,通过该报告即可了解所设计电路的资源消耗情况。

图22由图22可知,在三线八线译码器(74LS138)的设计中使用了8个宏单元,9个乘积项,8个寄存器单元,13个用户引脚及5个功能输入块。

(5)、编程下载本试验用并行电缆将开发实验平台与计算机接在一起。

确认下载电缆连接无误后执行Xilinx ISE的【iMPACT】命令,将三线八线译码器(74LS138)设计文件下载到目标芯片XC2C256-7PQ208中,硬件验证所设计电路功能。

2、元件的生成、调用和仿真1、新建原理图文件,命名为“Sch_LS74138”并添加到工程“Shiyan”中,如图23。

点击【下一步】完成原理图文件的创建。

在弹出的原理图编辑框内选择【Symbols】标签,在其目录列表内显示了所有可用电路器件,其中包括了我们所设计的LS74138(图24)。