四位全加器的电路和版图仿真.

4位全加器

四位全加器的VHDL实现通信0704 王学申0120703490117一、设计要求:采用QuartusII或Max+PlusII集成开发环境,利用VHDL硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。

二、设计分析加法器是数字系统中的基本逻辑器件。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0).三、加法器的分类(一)半加器能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

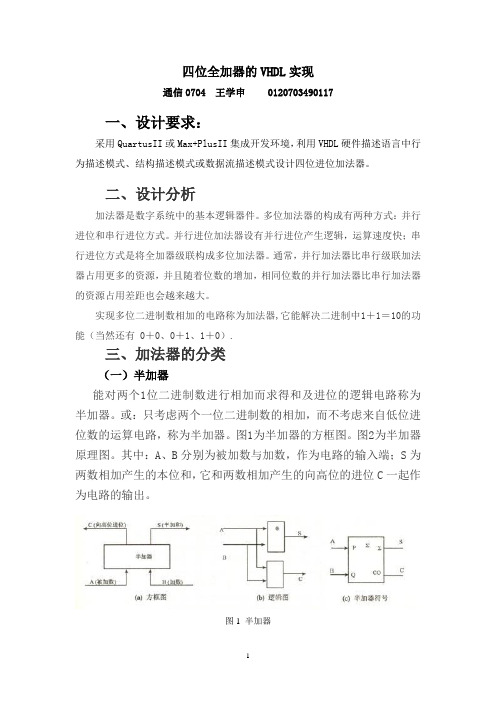

图1为半加器的方框图。

图2为半加器原理图。

其中:A、B分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

图1 半加器图2 半加器原理图根据二进制数相加的原则,得到半加器的真值表如表1所列。

信号输入信号输出A B S C0 0 0 00 1 1 01 0 1 01 1 0 1表1 半加器的真值表由真值表可分别写出和数S,进位数C的逻辑函数表达式为:(1) C=AB (2)由此可见,式(1)是一个异或逻辑关系,可用一个异或门来实现;式(2)可用一个与门实现。

仿真结果如图3所示:图3 半加器仿真图(二)全加器除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

图4为全加器的方框图。

图5全加器原理图。

被加数A i、加数B i从低位向本位进位C i-1作为电路的输入,全加和S i与向高位的进位C i作为电路的输出。

能实现全加运算功能的电路称为全加电路。

实验2:4位加法器 实验报告

EDA 技术基础实验报告实验项目名称:用原理图输入法设计4位加法器学院专业:信息学院电子专业姓名:学号:实验日期:20 实验成绩:实验评定标准:一、实验目的熟悉利用Quartus Ⅱ的原理图输入方法设计简单组合电路,掌握层次化设计的方法。

并通过一个4位全加器的设计把握利用EDA 软件进行原理图输入方式的电子线路设计的详细流程。

二、实验器材电脑一台Quartus Ⅱ软件三、实验内容与步骤1.在Quartus Ⅱ软件中建立工程,画图生成一个半加器的.bdf文件。

2.将此半加器文件设置成可调用的元件,使之成为一个元件符号存盘。

3.设计全加器顶层文件,以.bdf存盘。

4.将设计项目(.bdf文件)设置成工程和时序仿真。

5.截图保存波形文件图,及仿真结果。

6.将全加器原理图文件设置成符号元件,以供4位加法器的更高层设计。

7.按实验要求画出4位加法器原理图,建立其波形并仿真,截下仿真结果图。

四、实验电路图(程序)1.半加器电路原理图如下:半加器h_adder.bdf电路原理图(1)2.全加器电路原理图如下:全加器f_adder.bdf电路原理图(2)3.4位加法器four_adder.bdf电路原理图如下:4位加法器four_adder.bdf电路原理图(3)五、实验仿真结果及分析1. 全加器的仿真波形图如下:全加器波形仿真图(3)分析:ain, bin, cin 三段为输入,sum 为和,com 为进位,满足相关的逻辑表达式{sum =(ain ′bin ′cin ′+ain bin ′cin +ain ′bin cin +ain bin cin ′)‘com =(ain ′bin ′+bin ′cin ′+ain′cin′)′2. 4位全加器仿真波形图如下:分析:4位a[3..0]输入与4位b[3..0]输入以及来自cin 输入的数码相加得到4位输出s[3..0]和进位输出c,由图可见满足加法原理。

实验一 4位全加器的设计(1)

实验一4位全加器的设计一、实验目的:1 熟悉QuartusⅡ与ModelSim的使用;2 学会使用文本输入方式和原理图输入方式进行工程设计;3 分别使用行为和结构化描述方法进行四位全加器的设计;4 理解RTL视图和Technology Map视图的区别;5 掌握简单的testbench文件的编写。

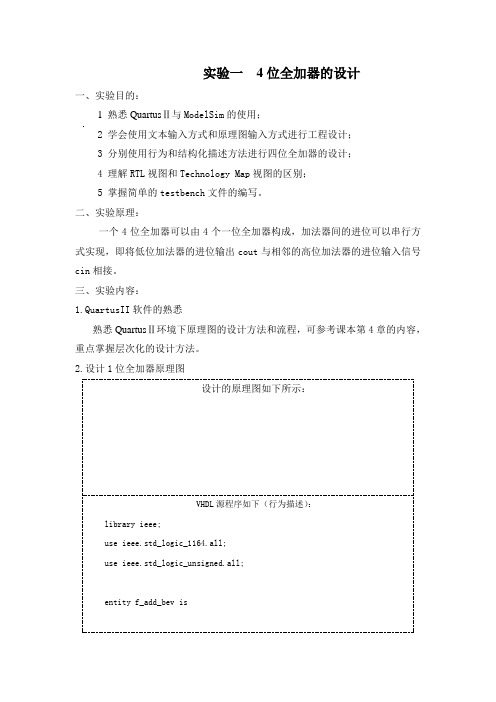

二、实验原理:一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的进位输入信号cin相接。

三、实验内容:1.QuartusII软件的熟悉熟悉QuartusⅡ环境下原理图的设计方法和流程,可参考课本第4章的内容,重点掌握层次化的设计方法。

2.设计1位全加器原理图设计的原理图如下所示:VHDL源程序如下(行为描述):library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f_add_bev is(A : in std_logic;B : in std_logic;CIN : in std_logic;S : out std_logic;CO : out std_logic);end entity;architecture bev of f_add_bev isbegin(CO,S)<=('0',A)+('0',B)+('0',CIN);end bev;VHDL源程序如下(行为描述)的RTL与technology map视图VHDL源程序如下(数据流描述):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity f_add_fl is(A : in std_logic;B : in std_logic;CIN : in std_logic;S : OUT std_logic;CO : out std_logic);end entity;architecture fl of f_add_fl isbeginS<=A XOR B XOR CIN;CO<=((A XOR B)AND CIN)OR(A AND B);end fl;VHDL源程序如下(数据流描述)的RTL与technology map视图:VHDL源程序如下(结构化描述):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity f_add_con isport(A : in std_logic;B : in std_logic;CIN : in std_logic;S : OUT std_logic;CO : out std_logic );end entity;architecture con of f_add_con is COMPONENT hadd_vhdPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;co : OUT STD_LOGIC;s : OUT STD_LOGIC );END COMPONENT;SIGNAL S1:STD_LOGIC;SIGNAL CO1:STD_LOGIC;SIGNAL CO2:STD_LOGIC;beginh_add1 : hadd_vhdport map(a => a,B => B,S => S1,CO => CO1);h_add2 : hadd_vhdport map(a => S1,B => CIN,S => S,CO => CO2);CO<=CO1 OR CO2;end con;VHDL源程序如下(结构化描述)的RTL与technology map视图:Testbench文件源程序如下:LIBRARY cycloneiii ;LIBRARY ieee ;USE cycloneiii.cycloneiii_components.all ;USE ieee.std_logic_1164.all ;ENTITY f_add_fl_tb ISEND ;ARCHITECTURE f_add_fl_tb_arch OF f_add_fl_tb ISSIGNAL A : STD_LOGIC :='0';SIGNAL CO : STD_LOGIC ;SIGNAL CIN : STD_LOGIC :='0'; SIGNAL B : STD_LOGIC :='0'; SIGNAL S : STD_LOGIC ;COMPONENT f_add_flPORT (A : in STD_LOGIC ;CO : buffer STD_LOGIC ;CIN : in STD_LOGIC ;B : in STD_LOGIC ;S : buffer STD_LOGIC );END COMPONENT ;BEGINDUT : f_add_flPORT MAP (A => A ,CO => CO ,CIN => CIN ,B => B ,S => S ) ;A<=NOT A AFTER 0.25US;B<=NOT B AFTER 0.5US;CIN<=NOT CIN AFTER 1US;END ;功能仿真波形如下:时序仿真波形如下:3.利用层次化原理图方法设计4位全加器(1)生成新的空白原理图,作为4位全加器设计输入(2)利用已经生成的1位全加器作为电路单元,设计4位全加器。

四位全加器实验Verilog

实验四四位全加器一、实验目的l. 用组合电路设计4位全加器。

2.了解Verilog HDL语言的行为描述的优点。

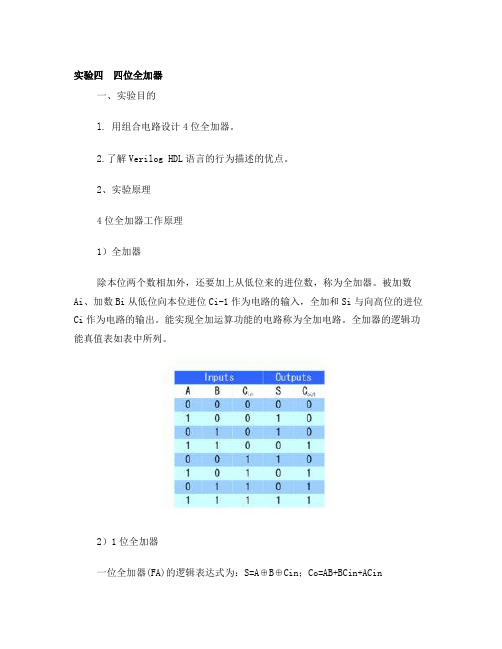

2、实验原理4位全加器工作原理1)全加器除本位两个数相加外,还要加上从低位来的进位数,称为全加器。

被加数Ai、加数Bi从低位向本位进位Ci-1作为电路的输入,全加和Si与向高位的进位Ci作为电路的输出。

能实现全加运算功能的电路称为全加电路。

全加器的逻辑功能真值表如表中所列。

2)1位全加器一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin;Co=AB+BCin+ACin其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;这两幅图略微有差别,但最后的结果是一样的。

3)4位全加器4位全加器可看作4个1位全加器串行构成, 具体连接方法如下图所示:采用Verilog HDL语言设计该4位全加器,通过主模块调用子模块(1位全加器)的方法来实现。

3、实验步骤四、实验连线K1-K4:14-11K5-K8:18-15L5-L8:7-10VIJN:83L4:64KHZ:805、心得体会首先,实现这一段全加器代码并不难,但是由于困惑给的三个时钟输入,没有太懂意思,所以只写了全加器控制LED灯的代码;后来问清楚后,运行全加器代码,有错误,原来是建文件时用的是verilog hdl,我建的是其他类型的;后来还有错,原来是把冒号打成分号;编译成功后,LED不亮,后来发现是硬件老化,换了箱子。

这一部分做好后,我准备把控制声音的加上去,本来准备再加一个模块,可是不能有两个顶层块,就对主模块做了补充,用case命令调用不同的状态,因为时间紧迫,所以代码写得比较简单,没有用经典的分频代码。

这里附一小段,是我在研究分频控制时看懂的网上的经典分频代码,适合乐曲自动播放等高级的实现,仅供分享assign preclk=(divider==16383)?1:0;//divider==16383,preclk=1always @(posedge clk) //基频上升沿触发beginif(preclk) //preclk=1divider=origin;elsedivider=divider+1;endalways @(posedge preclk) //调整占空比beginspeaker=~speaker; //2 分频产生方波信号end这部分实现了分频功能,其中origin+divider=16384=2^14,这个数根据自己的需要而定。

四位全加器

4位加法计数器一、实验目的(1)学习时序电路的VHDL描述方法。

(2)掌握时序进程中同步、异步控制信号的设计。

(3)熟悉EDA的仿真分析和硬件测试技术。

二、实验原理设计一个含计数使能、异步复位和并行预置功能的4位加法计数器,RST是异步复位信号,高电平有效;CLK是时钟信号;当使能信号ENA为1时,加法计数,COUT为计数进位输出,OUTY为计数输出。

VHDL参考程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity CNT4B isport(clk:in std_logic;rst:in std_logic;ena:in std_logic;outy:out std_logic_vector(3 downto 0);cout:out std_logic);end CNT4B;architecture BEHA V of CNT4B issignal CQI:std_logic_vector(3 downto 0);beginP_REG:process(clk,rst,ena)beginif rst = '1' then CQI <= "0000";elsif clk'event and clk = '1' thenif ena = '1' then CQI <= CQI + 1;end if;end if;outy <= CQI;end process P_REG;cout <= CQI(0) and CQI(1) and CQI(2) and CQI(3);end BEHA V;三、实验任务(1)编写4位二进制加法计数器的VHDL程序。

(2)在ispDsignEXPERT System或者Quartu sⅡ上对加法计数器进行仿真。

verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave)

verilog之四位全加器的编译及仿真(⽤开源免费的软件——iverilog+GTKWave)四位全加器的verilog的代码⽐⽐皆是,这⾥上⼀个⽐较简单的:/*4位全加器全加器需要有输⼊输出,需要有下级向上进位的输⼊,需要有向上⼀位进位的输出。

⼤家看⼀下,这个模块已经包含全部的输⼊输出信息。

⼤家都知道,N位加法器得出来的出来的和最多是N+1位因此可以清晰从下⾯代码中看到相关信息。

然后assign⽤的是阻塞赋值。

相加即满⾜相关的需求。

*/module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule在写testbeach⽂件之前,先普及⼀点testbeach的知识:⼀般来讲,在数据类型声明时,和被测模块的输⼊端⼝相连的信号定义为reg类型,这样便于在initial语句和always语句块中对其进⾏赋值;和被测模块输出端⼝相连的信号定义为wire类型,便于进⾏检测。

Testbench模块最重要的的任务就是利⽤各种合法的语句,产⽣适当的时序和数据,以完成测试,并达到覆盖率要求。

那么testbeach⽂件如下:/*File Name : test_adder4.vDescription : The testbench of the adder_4.vWritten By : LiMingData : 2011/04/18 20:13modefied : 在仿真的时候,把延时从10ns改为5ns: cout显⽰为2位*///test_adder4 (top-level module)`timescale 1ns/1nsmodule test_adder4;//Declare variableswire[3:0] sum;wire cout;reg[3:0] ina,inb;reg cin;//Instantiate the module adder4adder4 adder4_1(cout,sum,ina,inb,cin);//Stimulate the inputs, Finish the stimulation at 90 time unitsinitialbegin#0 ina = 4'b0001; inb = 4'b1010; cin = 1'b0;#5 ina = 4'b0010; inb = 4'b1010; cin = 1'b1;#5 ina = 4'b0010; inb = 4'b1110; cin = 1'b0;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0111; inb = 4'b1001; cin = 1'b0;#5 ina = 4'b0001; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b0;#5 ina = 4'b0111; inb = 4'b1111; cin = 1'b1;#5 $finish;endinitial$monitor("At time %t, ina(%b) + inb(%b) + cin(%b) = sum(%b)(%2d),cout(%b)",$time, ina, inb, cin, sum, sum, cout);initialbegin$dumpfile("test.vcd");$dumpvars(0,test_adder4);endendmodule由于是在windows的cmd下进⾏命令⾏的运⾏,所以有时候每次输⼊⼀个命令显得很费时间,所以我这⾥⼜写了⼀个(批处理⽂件)bat⽂件:go.batECHO OFFECHO *********************************ECHO * Batch fileECHO *********************************ECHO *ECHO ONiverilog -o test adder4.v test_adder4.vvvp -n test -lxt2cp test.vcd test.lxtgtkwave test.lxt(说明⼀下,我在windows下安装了gnuwin的软件,即能在windows下⽤gnu的⼀些⼩的实⽤的⼯具!)哈哈,这⾥就可以⼀键运⾏了,上⾯的⼀些命令的解释可以到我的“wndows下如何⽤Iverilog+GTKWave进⾏verilog的编译和查看仿真波形”的博⽂⾥去看看吧。

4位全加器实验报告

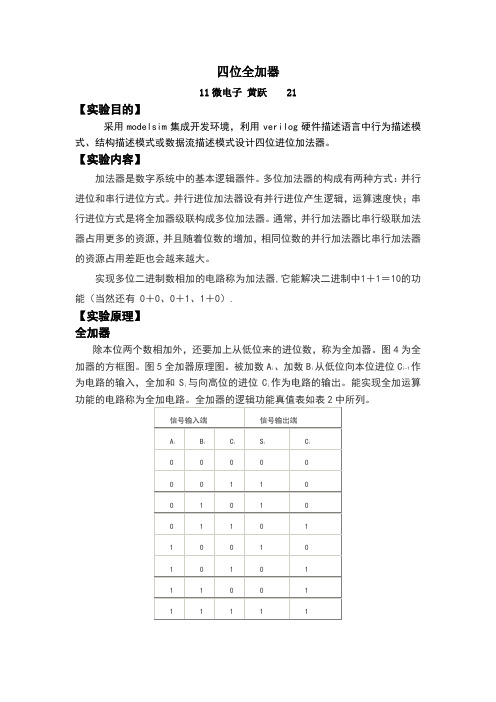

四位全加器11微电子黄跃21【实验目的】采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。

【实验内容】加法器是数字系统中的基本逻辑器件。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0).【实验原理】表2 全加器逻辑功能真值表图4 全加器方框图图5 全加器原理图多位全加器连接可以是逐位进位,也可以是超前进位。

逐位进位也称串行进位,其逻辑电路简单,但速度也较低。

四位全加器如图9所示,四位全加器是由半加器和一位全加器组建而成:图9 四位全加器原理图【实验步骤】(1)建立新工程项目:打开modelsim软件,进入集成开发环境,点击File→New project建立一个工程项目adder_4bit。

建立文本编辑文件:点击File→New在该项目下新建Verilog源程序文件并且输入源程序。

(2)编译和仿真工程项目:在verilog主页面下,选择Compile— Compile All或点击工具栏上的按钮启动编译,直到project出现status栏全勾,即可进行仿真。

选择simulate - start simulate或点击工具栏上的按钮开始仿真,在跳出来的 start simulate框中选择work-test_adder_4bit测试模块,同时撤销Enable Optimisim前的勾,之后选择ok。

在sim-default框内右击选择test_adder_4bit,选择Add Wave,然后选择simulate-run-runall,观察波形,得出结论,仿真结束。

实验二 原理图输入法设计-4位加法器

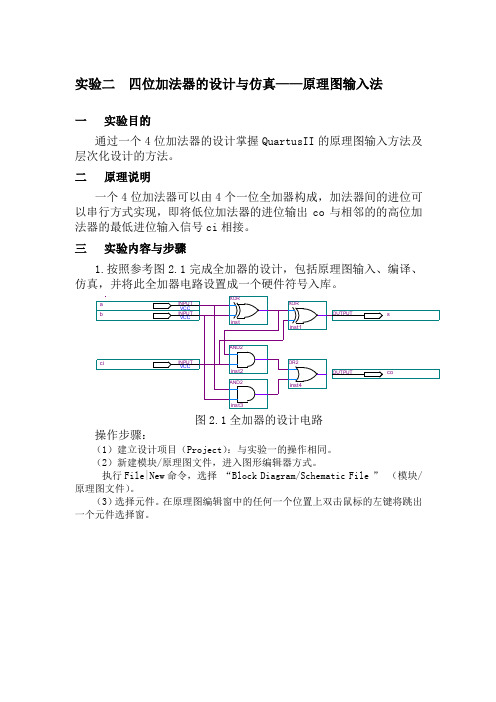

实验二四位加法器的设计与仿真——原理图输入法一实验目的通过一个4位加法器的设计掌握QuartusII的原理图输入方法及层次化设计的方法。

二原理说明一个4位加法器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出co与相邻的的高位加法器的最低进位输入信号ci相接。

三实验内容与步骤1.按照参考图2.1完成全加器的设计,包括原理图输入、编译、仿真,并将此全加器电路设置成一个硬件符号入库。

图2.1全加器的设计电路操作步骤:(1)建立设计项目(Project):与实验一的操作相同。

(2)新建模块/原理图文件,进入图形编辑器方式。

执行File|New命令,选择“Block Diagram/Schematic File ”(模块/原理图文件)。

(3)选择元件。

在原理图编辑窗中的任何一个位置上双击鼠标的左键将跳出一个元件选择窗。

图2.2元件选择对话框(4)编辑图形文件在元件库找到自己想要的元件,放好后连线并添加输入输出端口,画出完整的电路图后保存并编译通过。

(5)对设计项目设置进行仿真:过程与方法与实验一相同。

(6)将设计项目设置成可调用的元件以便调用基本逻辑元件库参数可设置的强函数元件库基本逻辑元件库中的元件 由此输入所需要的元件名MAX+plus 库 图2.3 一位全加器的图形编辑文件图2.4 将一位全加器模块生成符号入库2.建立一个更高的原理图设计层次,调用以上获得的1位全加器构成4位加法器,并完成编译、综合、仿真。

3.设计文件打包上传。

四实验报告:详细叙述4位加法器的设计流程;给出各层次的原理图及其对应的仿真波形图;将实验原理、实验过程、仿真结果写进实验报告。

五思考题:为了提高加法器的速度,如何改进以上设计的进位方式?六选作内容:用一片74163和一片74138构成一个具有8路顺序脉冲输出的顺序脉冲产生器。

要求在原理图上标明第1路到第8路输出的位置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计过程

本题目标设计面积小、功耗低、速度快的最基本电路四位全加器的 电路和版图,并对其性能进行仿真。首先设计半加器、全加器全加 器;在此原理上进行推广,设计出串行进位加法器,并对其进位进 一步改进、优化,利用各位之间的状态来预先产生高位的进位信号 ,设计出四位超前进位加法器并分析了其组成结构、结构参数以及 其工作原理,用数字设计软件Quartus II 进行了逻辑电路的初步设 计与仿真验证。接着用S-edit软件将逻辑电路转化为 CMOS电路图, 并通过T-spice进行仿真实验,从而验证了电路的准确性。最后介绍 了基于2umCMOS工艺版图设计的规则,通过L-edit绘制出它的版图, 并用LVS对它的版图与电路图进行了一致性检测及版图仿真,进一步 验证了设计的正确性。

全加器

在作二进制加法运算时,一般两个加数 都不会是一位,而是多位的。因此需要 考虑从低位来的进位,对于半加器而言, 即相当于3个1位二进制数的相加,求得 和及进位的逻辑电路称为全加器,其真 值表参见表2-2所列。

全加器逻辑图及仿真图

四位串行进位加法器

串行进位加法器是比较简单、基本的加 法器结构,也称为“行波进位加法器” 一个四位的串行进位加法器要求 4 个全 加器串联起来,进位输出位用来作为下 一位的进位输入,设计思路如下:

初步设计与仿真验证,逻辑电路转化为 CMOS 电路图,并通过 Tspice进行仿真实验,从而验证了电路的准确信。 第四章:通过 L-edit绘制出它的版图,并用LVS 对它的版图与电路 图进行了一致性检测及版图仿真,进一步验证了设计的正确性。 最后对本文的设计进行结论。

半加器加器逻辑图及仿真图

全加器

在作二进制加法运算时,一般两个加数 都不会是一位,而是多位的。因此需要 考虑从低位来的进位,对于半加器而言, 即相当于3个1位二进制数的相加,求得 和及进位的逻辑电路称为全加器,其真 值表参见表2-2所列。

全加器

当Ai、Bi、Ci-1有两个以上1就会产生进位。 当A1、B1、C0中有计数个1,Si为1,偶数个1为,Si为 0。。

与门、或门版图的绘制

四位串行进位加法器版图的绘制

四位超前进位加法器版图的绘制

四位超前进位加法器版图仿真结果

超前进位加法器

优化后四位超前进位加法器进位的原理图如下:

用整套Tanner软件设计集成电路的流程[12]如图所示:

反相器的CMOS电路及仿真

1.根据设计要求划分功能模块

反相器的CMOS电路及仿真

1.根据设计要求划分功能模块

异或门的逻辑及CMOS电路

异或门的逻辑及CMOS电路仿真

四位串行进位加法器的逻辑及CMOS电路、仿真

四位串行进位加法器逻辑图及仿真图

超前进位加法器

为了提高运算速度,必须设法减小或消除由于进位信号逐 级传递所消耗的时间,利用各位之间的状态来预先产生高 位的进位信号,于是制成了超前进位加法器。 由全加器的真值表及基本加法器的公式可得串行全加器的 Si和Ci的逻辑表达式:

四位串行进位加法器

定义两个中间变量Gi和Pi:

四位全加器的电路和版图仿真

本文内容章节安排

第一章:概述加法器研究背景及意义及本论文的主要工作内容。 第二章:介绍半加器、全加器,设计原理,在此原理上进行推广, 设计出串行进位加法器,并对其进位进一步改进、优化,设计四位超前

进位加法器,然后用数字电路设计软件 Quartus II 进行了逻辑电路的

超前进位加法器

因为设计的是四位加法器,其最低位C0为0,所以将四位 全加器的进位链优化如下,可大大简化电路,减少CMOS 数量,以便减少后面版图的工作量。

C1 G1 C 2 G 2 P 2G1 C 3 G3 P3G 2 P3P 2G1 C 4 G 4 P 4G3 P 4 P3G 2 P 4 P3P 2G1

S1 P 1 C0 S2 P 2 C1 S3 P 3 C2 S4 P 4 C3

超前进位加法器

将以上的公式用逻辑图表达如下:

超前进位加法器

为了提高运算速度,必须设法减小或消除由于进位信号逐 级传递所消耗的时间,利用各位之间的状态来预先产生高 位的进位信号,于是制成了超前进位加法器。 由全加器的真值表及基本加法器的公式可得串行全加器的 Si和Ci的逻辑表达式:

2.1 基本加法器

数字电子计算机能进行各种信息处理, 其中最常用的是各种算数运算。因为算 数中的加、减、乘、除四则运算,在数 字电路中往往是将其转化为加法运算来 实现的,所以加法运算是运算电路的基 本单元。能实现二进制加法运算的逻辑 电路称为加法器。

半加器

由真值表可知:当A,B中只有一个为1时,S0=1;当A, B同时为1时,C0=1:

四位串行进位加法器的逻辑及CMOS电路图仿真

四位超前进位加法器的逻辑和CMOS电 路

四位超前进位加法器的CMOS电路仿真

以下为PMOS版图绘制的步骤:

1、绘制N阱 2、绘制P Select 3、绘制有源区 4、绘制栅极多晶硅 5、绘制有源区接触孔

反相器版图的版图绘制

异或门CMOS电路版图