第5章80868088总线操作和时序

80868088 CPU的工作时序

微机原理第2章8086/8088系统结构8086/8088 的工作时序1. 时钟周期、总线周期、指令周期微机原理时钟周期:是CPU的基本时间单位,记为T,其值为计算机主频的倒数。

微机原理时钟周期:是CPU 的基本时间单位,记为T ,其值为计算机主频的倒数。

总线周期:CPU 通过总线对存储器或I/O 进行1次访问所需要的时间。

它至少包含4个T ,记为T 1,T 2,T 3,T 4.1. 时钟周期、总线周期、指令周期1. 时钟周期、总线周期、指令周期微机原理的时间,它包含一个或多个总线周期。

常采用MIPS(Million Instructions Per Second)作单位。

微机原理(1) 8086读总线周期T 1T 2T3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/R DENA 15~A 02. 读/写工作时序微机原理(2) 8086写总线周期T 1T 2T 3T 4一个总线周期CLK A 19 ~ A 16S 6 ~ S 3A 19/S 6 ~ A 16/S 3DATA OUTAD 15 ~ AD 0ALE 高=I/O ,低=MM/IOWRDT/R DENA 15~A 0微机原理(3)8086具有等待状态的读总线周期T 1T 2T 3T W 一个总线周期CLK A 19~A 16A 19/S 6 ~ A 16/S 3DATA INAD 15 ~ AD 0ALE 低=I/O ,高=MM/IORD DT/RDEN A 15~A 0T 4READYWAITREADYS 6~S 3微机原理(4) 8088读总线周期T 1T 2T 3T 4一个总线周期CLK A 19~A 16S 6~S 3A 19/S 6 ~ A 16/S 3DATA INAD 7 ~ AD 0ALE 高=I/O ,低=MIO/MRD DT/R DENA 7~A 0A 15 ~ A 8A 15~A 8微机原理例1:在8088 CPU 中对存储器进行读操作时,CPU 引脚的IO/M 、RD 、WR 、DT/R 的输出电平分别是什么?例2:在若在1个总线周期中,插入了3个T W ,请问在该总线周期中对READY 信号进行了几次采样?低电平低电平高电平低电平4微机原理下次课见。

微机原理第5章80868088CPU总线操作与时序

读周期

CPU从内存或I/O设备读取数据的过程,包括地 址发送、数据读取和数据返回三个阶段。

写周期

CPU向内存或I/O设备写入数据的过程,包括地址发送、数据写入和数据返回三 个阶段。

03

数据传输过程

读周期

总结词

在读周期中,CPU从内存中读取数据。

详细描述

读周期是CPU从内存中读取数据的过程。在读周期开始时,CPU通过地址总线发送要读取的内存地址,然后通过 数据总线从内存中读取数据。这个过程需要多个时钟周期,具体取决于数据的存储位置和CPU的速度。

然而,随着总线技术的不断发展,也 面临着一些技术挑战。例如,如何提 高总线的传输效率、降低能耗以及优 化系统性能等。为了解决这些问题, 需要不断进行技术创新和改进。

展望

未来,CPU总线技术将继续发挥其在 微机原理中的重要作用。随着技术的 不断进步和应用需求的增加,总线技 术将更加成熟和多样化。同时,随着 人工智能、大数据等新兴技术的发展 ,总线技术也将与这些领域进行更深 入的融合,为解决实际问题提供更多 可能性。

8086/8088 CPU的总线结构

地址总线

用于传输地址信息,确定要访问的内存单元或I/O 端口。

数据总线

用于传输数据信息,实现数据在CPU和内存或I/O 设备之间的传输。

控制总线

用于传输控制信号,控制CPU和内存或I/O设备之 间的操作。

总线操作时序

时钟信号

用于同步总线上的操作,确保数据传输的正确 性。

中断源

指引发中断的事件或异常情况,如输入/输出设备、定时器、故障等。

中断向量

指中断处理程序的入口地址。

中断响应过程

保存程序计数器

当发生中断时,CPU会自动将当前的程序计数器(PC)值保存到堆栈 中,以便在中断处理完毕后能够正确返回到原程序。

微机原理第5章80868088CPU总线操作与时序

微机原理与接口技术 第5章 8086/8088CPU的总线操作与时序

GND AD14 AD13 AD12 AD11 AD10 AD9 AD8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND

最小系统模式系统中只有8086一个处理器,所有的 控制信号都是由8086CPU产生。

最大系统模式系统中可包含一个以上的处理器,如协 处理器8087。系统规模比较大时,系统控制信号不由 8086直接产生,而通过与8086配套的总线控制器形成。

*DMA方式

•管脚分析内容: 信号流向:输入、输出、双向 管脚状态:0、1、高阻(悬空)

一、概述 二、8086管脚分类

(一)地址数据线 (二)地址状态线 (三)控制总线(1)-(17) (四) 单CPU模式管脚说明

(五) 多CPU模式引脚说明 三、8088管脚功能 §5.3 8086/8088支持的芯片及最大/最小系统 §5.4 CPU时序

一、微概机述原理与接口技术 第5章 8086/8088CPU的总线操作与时序 •8086、8088为40条引脚, DIP封装 •典型工作模式:

微机原理与接口技术 第5章 8086/8088CPU的总线操作与时序

微机原理与接口技术 第5章 8086/8088CPU的总线操作与时序

第1章

第2章

课 第3章

程

第4章 第5章

教 第6章

学

第7章 第8章

单 第9章

第10章

元 第11章

第12章

第5章 8086的总线操作

第5章 8086的总线操作

8088最大模式图

第5章 8086的总线操作

5.2.2 8086 CPU引脚功能

1.与工作模式无关的引脚功能

⑴ AD15~AD0(双向,三态) 为低16位地址/数据的复用引脚线。采用分时的多路

转换方法来实现对地址线和数据线的复用。在总线周期 的T1状态,这些引线表示作为低16位地址线,在总线周 期的T2,T3,TW状态,这些引线作为数据总线。可见对 复用信号是用时间来加以划分的,所以在T1状态,必须 用锁存器将地址加以锁存,这样在随后的T状态,即使 这些线用作数据线,而地址信息不变。在DMA方式时, 这些引线被浮空,置为高阻状态。

第5章 8086的总线操作

5.1.2 8086/8088引脚信号

第5章 8086的总线操作

5.2 8086的两种模式

5.2.1 最小模式和最大模式的概念

当把8086CPU与存储器和外设构成一个计算机系统时,根据所 连的存储器和外设的规模,8086具有两种不同的工作模式,即 最小模式和最大模式。8086到底工作在最大模式还是最小模式, 由硬件设计决定,需要通过总线进行读或写操作。 与CPU内部操作相比,通过总线进行的操作需要较长的时间。我们把 CPU通过总线进行某种操作的过程称为总线周期(Bus Cycle)。根据 总线操作功能的不同,有多种不同的总线周期。如存储器读周期、存 储器写周期、I/O读周期、I/O写周期等。

第5章 8086的总线操作

8088最小模式图

第5章 8086的总线操作

2.最大模式

最大模式是相对最小模式而言的。最大模式用 在中等规模的或者大型的8086系统中。若要构成 的系统较大,就要求有较强的总线驱动能力,这 样8086要通过一个总线控制器8288来形成各种总 线周期,控制信号由8288供给。在最大模式系统 中,总是包含有两个以上总线主控设备,其中一 个就是8086或者8088微处理器,其他的通常是协 处理器,它们是协助微处理器工作的。

计算机教程:8088的总线与时序

•8284内部一晶体震荡器,只要外接一石英晶体,便产生和晶体共振 荡频率的时钟OSC,经三分频成CLK时钟信号,再二分 频成PCLK 某些外设时钟(主要是8253计数器)。

•当加电或按CTRL-ALT-DEL键时,开关电源产生电源的RES信号送 8284,内部复位逻辑便产生系统复位信号RESET。

(3)AMWC——存储器超前写命令(MEMW),同 MWTC,只是提前一个时钟脉冲。

(4)IORC——I/O读命令(IOR),通知被选中I/O口, 把数据发送到数据线上。

(5)IOWC——I/O写命令(IOW),把数据线上的数据, 写入被选中I/O口。

(6)AIOWC——I/O超前写,同IOWC,超前一个时钟脉 冲。

S4S3组合表示哪个段 寄存器正在被使用

二、控制和状态线——分两种:一种8088组态 有关的线,另一类是与组态无关的线。

1、MN/MX 工作模式标志(输入),最小/最大组

态输入控制信号。即接+5V 最小组态,接地 最大组态。

2、最小组态下的引线:

(1)IO/M 区分是存储器访问还是I/O访问(输出, 三态),输出低电平访问存储器,输出高电平 I/O访问。

§4.2

8088的CPU系统

总线分

片内总线 芯片总线 系统总线

CPU系统的作用 产生系统三总线,由引脚功能可 知,还需附加地址锁存器,数据总线驱动器,时钟信号产 生器,总线控制器等。

一、地址锁存器

1.作用——将CPU发出的动态地址锁存,即暂存器。因为 低8位与高4位地址和数据与状态分时复用,先输出地址, 后输出数据/状态,然后利用这些稳定的地址,选择某个 存储单元或I/O口来读/写。DMA期间隔离8088与系统总线。

微机原理及应用总结

第八章 输入输出控制

1、掌握输入输出数据的传输控制方式 2、掌握中断类型码、中断向量、中断向 量表的 关系 3、8259A响应中断过程 4、 了解8259A基本构成与引脚信号

5、8259A的工作方式(课件) 6、8259A编程方法 7、课件例题、作业

7、传统的串行接口COM、 并行打印机接口LPT 辅存接口ATA/IDE接口、SCSI接口、 通用串行总线USB接口 IEEE 1394视频接口(Fire Wire火线) 10、作业

8、在串行通讯中,数据的传送方式:单工 半双工 全双工 9、在串行通讯中,信号的传送方式:基带传输 频 带传输(调制方法:调频 调幅调相) 10、5251A的基本功能 11、5251A的引脚、编程、应用 12、例11、12、13 13、USB、1394、RS232-C的用途

第11章 D/A、A/D转换与接口技术

微机原理及应用总结

第一章 基础知识

数制及其相互转换

第二章 微型计算机系统概述

1、了解微型计算机的发展、应用及其分类 2、掌握计算机的构成 3、掌握计算机的工作过程 4、掌握8086/8088处理器的结构、功能和操作 5、最大工作模式与最小工作模式的区别 6、作业

第三章 8086/8088微处理器的指令系统

第五章 总线操作与时序

概念 三总线的形成

第六章 存储器

1、存储器分类、微机存储系统的层次结构 2、主存储器的基本结构、存储器主要技术指标 3、静态RAM、动态ROM的常用芯片用法 4、只读存储器的分类、常用芯片用法 5、存储器芯片的扩展,位扩展、字扩充 6、存储器芯片设计 7、课件例题

微机原理知识点总结

微机原理复习总结第1章基础知识⏹计算机中的数制⏹BCD码与二进制数11001011B等值的压缩型BCD码是11001011B。

F第2章微型计算机概论⏹计算机硬件体系的基本结构计算机硬件体系结构基本上还是经典的冯·诺依曼结构,由运算器、控制器、存储器、输入设备和输出设备5个基本部分组成。

⏹计算机工作原理1.计算机由运算器、控制器、存储器、输入设备和输出设备5个基本部分组成。

2.数据和指令以二进制代码形式不加区分地存放在存储器重,地址码也以二进制形式;计算机自动区分指令和数据。

3.编号程序事先存入存储器。

⏹微型计算机系统是以微型计算机为核心,再配以相应的外围设备、电源、辅助电路和控制微型计算机工作的软件而构成的完整的计算机系统。

⏹微型计算机总线系统数据总线 DB(双向)、控制总线CB(双向)、地址总线AB(单向);⏹8086CPU结构包括总线接口部分BIU和执行部分EUBIU负责CPU与存储器,,输入/输出设备之间的数据传送,包括取指令、存储器读写、和I/O读写等操作。

EU部分负责指令的执行。

⏹存储器的物理地址和逻辑地址物理地址=段地址后加4个0(B)+偏移地址=段地址×10(十六进制)+偏移地址逻辑段:1). 可开始于任何地方只要满足最低位为0H即可2). 非物理划分3). 两段可以覆盖1、8086为16位CPU,说明(A )A. 8086 CPU内有16条数据线B. 8086 CPU内有16个寄存器C. 8086 CPU内有16条地址线D. 8086 CPU内有16条控制线解析:8086有16根数据线,20根地址线;2、指令指针寄存器IP的作用是(A )A. 保存将要执行的下一条指令所在的位置B. 保存CPU要访问的内存单元地址C. 保存运算器运算结果内容D. 保存正在执行的一条指令3、8086 CPU中,由逻辑地址形成存储器物理地址的方法是(B )A. 段基址+偏移地址B. 段基址左移4位+偏移地址C. 段基址*16H+偏移地址D. 段基址*10+偏移地址4、8086系统中,若某存储器单元的物理地址为2ABCDH,且该存储单元所在的段基址为2A12H,则该存储单元的偏移地址应为(0AADH )。

(完整版)第五章8088的总线操作和时序微机原理第2版课后答案

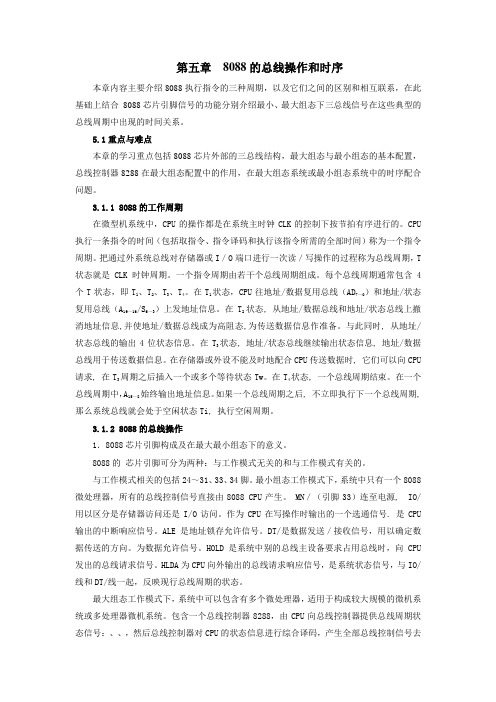

第五章8088的总线操作和时序本章内容主要介绍8088执行指令的三种周期,以及它们之间的区别和相互联系,在此基础上结合8088芯片引脚信号的功能分别介绍最小、最大组态下三总线信号在这些典型的总线周期中出现的时间关系。

5.1重点与难点本章的学习重点包括8088芯片外部的三总线结构,最大组态与最小组态的基本配置,总线控制器8288在最大组态配置中的作用,在最大组态系统或最小组态系统中的时序配合问题。

3.1.1 8088的工作周期在微型机系统中,CPU的操作都是在系统主时钟CLK的控制下按节拍有序进行的。

CPU 执行一条指令的时间(包括取指令、指令译码和执行该指令所需的全部时间)称为一个指令周期。

把通过外系统总线对存储器或I/O端口进行一次读/写操作的过程称为总线周期,T 状态就是CLK时钟周期。

一个指令周期由若干个总线周期组成。

每个总线周期通常包含4个T状态,即T l、T2、T3、T4。

在T1状态,CPU往地址/数据复用总线(AD7~0)和地址/状态复用总线(A19~16/S6~3)上发地址信息。

在T2状态, 从地址/数据总线和地址/状态总线上撤消地址信息,并使地址/数据总线成为高阻态,为传送数据信息作准备。

与此同时, 从地址/状态总线的输出4位状态信息。

在T3状态, 地址/状态总线继续输出状态信息, 地址/数据总线用于传送数据信息。

在存储器或外设不能及时地配合CPU传送数据时, 它们可以向CPU 请求, 在T3周期之后插入一个或多个等待状态Tw。

在T4状态, 一个总线周期结束。

在一个总线周期中,A15~8始终输出地址信息。

如果一个总线周期之后, 不立即执行下一个总线周期, 那么系统总线就会处于空闲状态Ti, 执行空闲周期。

3.1.2 8088的总线操作1.8088芯片引脚构成及在最大最小组态下的意义。

8088的芯片引脚可分为两种:与工作模式无关的和与工作模式有关的。

与工作模式相关的包括24~31、33、34脚。