3.同步置数异步清零D触发器

大学课程《数字电子技术基础》试题及答案(三)

大学课程《数字电子技术基础》试题及答案一、填空题组合逻辑电路1. 数字电路按逻辑功能的不同特点可分为两大类,即: 逻辑电路和 逻辑电路 。

答:组合 、时序2. 从一组输入数据中选出一个作为数据传输的常用组合逻辑电路叫做 。

答:数据选择器3.用于比较两个数字大小的逻辑电路叫做 。

答:数值比较器4. 驱动共阳极七段数码管的译码器的输出电平为 有效,而驱动共阴极的输出电平为 有效。

答:低、高5.一个8选1的多路选择器(数据选择器),应具有 个地址输入端。

答:3个6.编码器的逻辑功能是把输入的高低电平编成一个 ,目前经常使用的编码器有普通编码器和优先编码器两类。

答:二值代码7.译码器的逻辑功能是把输入的二进制代码译成对应的 信号,常用的译码器有二进制译码器,二-十进制译码器和显示译码器三类。

答:输出高、低电平8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

答:10111111二、选择题组合逻辑电路1.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A 2A 1A 0=100时,输出= 。

A 、00010000,B 、11101111C 、11110111D 、10000000答:B2.在下列逻辑电路中,不是组合逻辑电路的是( )。

A 、译码器B 、编码器C 、全加器D 、寄存器 答:D3.在下列逻辑电路中,不是组合逻辑电路的是( )。

A. 译码器B. 编码器C. 全加器D.寄存器 答:D4. 八选一数据选择器组成电路如下图所示,该电路实现的逻辑函数是Y= 。

A. ABC ABC ABC ABC +++ B. ABC ABC + C. BC ABC +D. ABC ABC ABC ABC +++ 答:D5.七段显示译码器是指 的电路。

A. 将二进制代码转换成0~9数字B. 将BCD 码转换成七段显示字形信号C. 将0~9数字转换成BCD 码D. 将七段显示字形信号转换成BCD 码 答:B6.组合逻辑电路通常由 组合而成。

数字电子技术期末试卷标准答案及评分标准(A卷)

班级:__________ 学号: __________姓名: __________阅卷教师: _____________ 成绩: _______________一、判断题(将答案添入下表,每题1分,共10分。

正确选“√”,错误选“×”) 1 2 3 4 5 6 7 8 9101.在时间和幅度上都断续变化的信号是数字信号,因为说话时语音是断续的,所以是数字信号。

( )2.若两个函数具有不同的逻辑函数式,则两个逻辑函数必然不相等。

( ) 3.N 变量逻辑函数全部2N 个最大项之积恒等于1。

( ) 4.因为逻辑表达式A+B+AB=A+B 成立,所以AB=0成立。

( )。

5.TTL 集电极开路门输出为1时由外接电源和电阻提供输出电流。

( ) 6.异步时序电路是指的各级触发器类型不同的电路。

( )7.D 触发器的特征方程Q n+1=D ,而与Q n 无关,所以,D 触发器不是时序电路。

( ) 8.D/A 转换器的最大输出电压的绝对值可达到基准电压V REF 。

( )9.施密特触发器可用于将正弦波变换成三角波。

( )10.SRAM 是指静态RAM ,DRAM 是指动态RAM ;对相同容量的SRAM 和DRAM 而言,前者造价高,响应速度也快。

( )二、试将下列函数化为最简与或形式(10分,每题5分,要有解题步骤,否则不给分)(1)D C B A D C B A D B A AD Y +++=(2)化简逻辑函数D C B A BCD A D C B A D C B A F ⋅⋅++⋅⋅=),,,(;给定约束条件:0=+++⋅+⋅++⋅D C B A D ABC ABCD D C B A D C AB D C B A CD B A三、已知电路如图所示,写出F1、F2、F3、F 与输入变量A 、B 、C 、D 之间的逻辑表达式。

(本题10分)阅卷教师: _____________ 成绩: _______________四、设计一个能被2 或3 整除的逻辑电路,其中被除数A、B、C、D是8421BCD编码。

西安交通大学数字电子技术实验报告

西安交通大学数字电子技术实验报告实验三、ISE基础实验预习:(1)安装ISE13.4软件。

(2)按照视频文件“Verilog语言输入法D_Flip_Flop.exe”进行演练。

实验内容和步骤:下载开发板相关器件的Datasheet,了解其性能。

按照P249附录A“FPGA实验预习报告模板”中的内容和步骤,完成D触发器的设计、综合、实现、仿真和下载全过程,熟悉ISE编程环境和用Adept下载编程文件的方法。

1.在G盘用自己的学号建立文件夹,进入用自己学号建立的文件夹后,再建立本次实验的文件夹,及本次实验所建工程的文件夹,文件夹名可以起名为:D_Flip_Flop、My_FirstISE、或Experiment_1、或Test_1,等等。

2.建立工程文件。

3.输入D触发器的Verilog程序。

4.编写D触发器的约束文件。

5.综合、实现及生成编程文件。

6.基于ISim的行为仿真。

7.采用Adept软件下载*.bit 程序到开发板。

8.测试D触发器的逻辑功能。

通过D触发器设计熟悉ISE软件后,自己设计一个门电路,例如与非门,重复以上ISE 软件的使用步骤。

验收:1.按照老师布置的逻辑门电路设计Verilog语言程序、约束文件、下载、仿真。

要能说明任一时刻输入输出的逻辑关系。

2.能够用开发板演示所设计的逻辑功能。

实验程序1.VERILOG工程文件module D_Flip_Flop(input clk,input set,input D,input clr,output reg q //注意:always模块中的输出必须是寄存器型变量);always @(posedge clk or posedge clr or posedge set)beginif(clr) q<=0;else if(set) q<=1;else q<=D;endendmodule2.约束文件NET "clk" LOC ="B8"; //时钟NET "D" LOC ="N3"; //SW7NET "set" LOC ="L3"; //SW1NET "clr" LOC ="P11"; //SW0NET "q" LOC ="G1"; //LD73.仿真文件module test_D_Flip_Flop;// Inputsreg clk;reg set;reg D;reg clr;// Outputswire q;// Instantiate the Unit Under Test (UUT) D_Flip_Flop uut (.clk(clk),.set(set),.D(D),.clr(clr),.q(q));initial begin// Initialize Inputsclk=0;set=1;D=0;clr=0;// Wait 100 ns for global reset to finish #100;// Add stimulus hereEndalways#10clk=~clk;always#12D=~D;always#33clk=~clk;always#42set=~set;endmodule仿真结果:实验四、组合逻辑电路实验Ⅰ(2学时)组合逻辑Ⅰ:(1)使用VERILOG设计一个新的逻辑功能(比如四输入或门、或非门、与或非门等等),并在开发板上验证,比如:进实验室前编写好VERILOG源文件、约束文件和仿真文件(见4.1.2,P101(2))。

机电一体化实验指导书

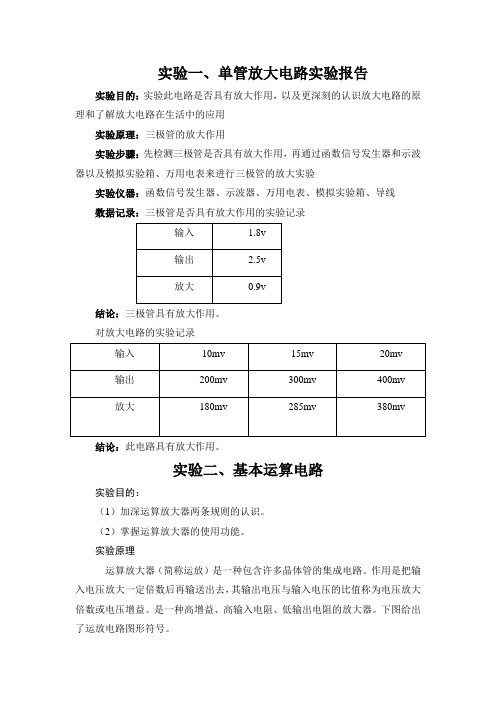

实验一、单管放大电路实验报告实验目的:实验此电路是否具有放大作用,以及更深刻的认识放大电路的原理和了解放大电路在生活中的应用实验原理:三极管的放大作用实验步骤:先检测三极管是否具有放大作用,再通过函数信号发生器和示波器以及模拟实验箱、万用电表来进行三极管的放大实验实验仪器:函数信号发生器、示波器、万用电表、模拟实验箱、导线数据记录:三极管是否具有放大作用的实验记录输入 1.8v输出 2.5v放大0.9v结论:三极管具有放大作用。

对放大电路的实验记录输入10mv 15mv 20mv输出200mv 300mv 400mv放大180mv 285mv 380mv结论:此电路具有放大作用。

实验二、基本运算电路实验目的:(1)加深运算放大器两条规则的认识。

(2)掌握运算放大器的使用功能。

实验原理运算放大器(简称运放)是一种包含许多晶体管的集成电路。

作用是把输入电压放大一定倍数后再输送出去,其输出电压与输入电压的比值称为电压放大倍数或电压增益。

是一种高增益、高输入电阻、低输出电阻的放大器。

下图给出了运放电路图形符号。

运放有两个输入端a (倒相输入端或反相输入端)、b (非倒相输入端或同相输入端)和一个输出端O 。

理想运放是指其开环放大倍数A →∞,输入电阻R í→∞,输出电阻R O →0,可以得出以下两条规则:(1)倒相端和非倒相端(反相输入端和同相输入端)的输入电流均为零(虚断I += I -=0)。

(2)对于公共端(地),倒相端和非倒相端(反相输入端和同相输入端)的电压相等(U +=U -)。

实验内容与步骤 1.反相比例运算电路反相比例运算电路如图所示,图 反相比例运算电路输入电压U i 通过电阻R 作用与运放的反相输入端(其中R 2=R 1∥R f )。

根据理想运放的两条规则有U P =U N =0 I P =I N ,所以节点N 的电流方程为1R Un Ui -=Rf UoUn -有U O =—Ui R Rf 1,U O 与U i 成比例关系,比例系数为 —1R Rf,负号表示U O 与U i 反相。

填空题数字电路

1.根据集成度的不同,数字集成电路分以下四类:小、中、大、超大规模集成电路。

2.二进制数是以2为基数的计数体制,十六进制数是以16为基数的计数体制。

3.二进制数只有0和1两个数码,其中计数的基数是2,加法运算的进位规则为逢二进一。

4.十进制数转换为二进制数的方法是:整数部分用除2取余法,小数部分用乘2取整法,十进制数23.75对应的二进制数为10111.11。

5.二进制数转换为十进制数的方法是各位加权系数之和,二进制数10110011对应的十进制数为179。

6.用8421BCD码表示十进制数时,则每位十进制数可用四位二进制代码表示,其位权值从高位到低位依次为8、4、2、1。

7.十进制数25的二进制数是11001,其对应的8421CBCD码是00100101。

8.负数补码和反码的关系是:补码=反码+1。

9.二进制数+1100101的原码为01100101,反码为01100101,补码为01100101,-1100101的原码为11100101,反码为10011010,补码10011011。

10.负数-35的二进制数是-100011,反码是1011100,补码是1011101。

1.逻辑代数中的三种最基本的逻辑运算是与运算,或运算,非运算。

2.逻辑函数的五种表示方法是真值表,逻辑函数式,逻辑图,波形图,卡诺图。

3.逻辑代数中的三条重要规则是代入规则,反演规则,对偶规则。

4.由n个变量构成逻辑函数的全部最小项有2n次方个,4变量卡诺图由16个小方格组成。

5.逻辑函数表达式有标准与-或式,标准或-与式。

6.最简与-或表达式的标准是:与项个数最少,每个与项变量数最少。

7.化简逻辑函数的主要方法有:公式化简法,图形化简法。

8.最小项表达式又称标准与-或表达式,最大项表达式又称标准或-与表达式。

1.在数字逻辑电路中,三极管工作在饱和状态和截止状态。

2.和TTL门电路相比,CMOS门电路的优点为静态功耗小,噪声容限大,输入电阻高。

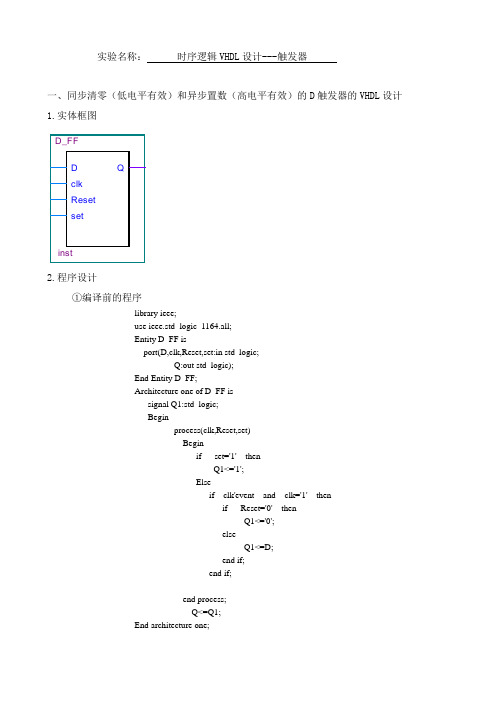

时序逻辑VHDL设计---触发器

实验名称:时序逻辑VHDL设计---触发器一、同步清零(低电平有效)和异步置数(高电平有效)的D触发器的VHDL设计1.实体框图Dclk Reset set QD_FFinst2.程序设计①编译前的程序library ieee;use ieee.std_logic_1164.all;Entity D_FF isport(D,clk,Reset,set:in std_logic;Q:out std_logic);End Entity D_FF;Architecture one of D_FF issignal Q1:std_logic;Beginprocess(clk,Reset,set)Beginif set='1' thenQ1<='1';Elseif clk'event and clk='1' thenif Reset='0' thenQ1<='0';elseQ1<=D;end if;end if;end process;Q<=Q1;End architecture one;②程序编译错误情况错误1:Error (10500): VHDL syntax error at D_FF.vhd(22) near text "process"; expecting "if"错误2:Error (10500): VHDL syntax error at D_FF.vhd(24) near text "architecture"; expecting "if"分析:经检查,发现原程序少了END if,没有与if匹配,添加即可。

③正确的程序library ieee;use ieee.std_logic_1164.all;Entity D_FF isport(D,clk,Reset,set:in std_logic;Q:out std_logic);End Entity D_FF;Architecture one of D_FF issignal Q1:std_logic;Beginprocess(clk,Reset,set)Beginif set='1' thenQ1<='1';Elseif clk'event and clk='1' thenif Reset='0' thenQ1<='0';elseQ1<=D;end if;end if;end if;end process;Q<=Q1;End architecture one;3.仿真波形图4.仿真波形分析当置数端SET出现高电平时,此时不管CP脉冲和D的状态如何,输出立即置为‘1’,实现异步置数的功能;当清零端RESET出现低电平时,而且必须当CP脉冲为上升沿时,输出清零,实现同步清零;除此之外,当CP脉冲为上升沿状态时,D=0,Q=0;D=1,Q=1;二、异步清零(高电平有效)和同步置数(低电平有效)的JK触发器的VHDL设计1.实体框图clk reset setJK[0..1]QJK_FFinst2.程序设计①编译前的程序Library ieee;use ieee.std_logic_1164.all;Entity JK_FF isport( clk,reset,set,J,K:in std_logic;Q:out std_logic);End entity JK_FF;Architecture two of JK_FF issignal Q1:std_logic;beginprocess(clk,reset,set,J,K)beginif reset='1' thenQ1<='0';elseif clk'event and clk='1' thenif set='0' thenQ1<='1';elsecase JK iswhen "00" => Q1<=Q1;when "10" => Q1<='1';when "11" => Q1<=not Q1;when others =>NULL;end case;end if;end if;end if;end process;Q<=Q1;end architecture two;②程序编译错误情况错误1:Error (10482): VHDL error at JK-FF.vhd(19): object "JK" is used but not declared错误2:Error (10523): Ignored construct two at JK-FF.vhd(7) due to previous errors分析:JK为两位,需要定义如下:JK:in std_logic_vector(0 to 1);③正确的程序Library ieee;use ieee.std_logic_1164.all;Entity JK_FF isport( clk,reset,set:in std_logic;JK:in std_logic_vector(0 to 1);Q:out std_logic);End entity JK_FF;Architecture two of JK_FF issignal Q1:std_logic;beginprocess(clk,reset,set,JK)beginif reset='1' thenQ1<='0';elseif clk'event and clk='1' thenif set='0' thenQ1<='1';elsecase JK iswhen "00" => Q1<=Q1;when "01" => Q1<='0';when "10" => Q1<='1';when "11" => Q1<=not Q1;end case;end if;end if;end if;end process;Q<=Q1;end architecture two;3.仿真波形图4.仿真波形分析当清零端ResET出现高电平时,此时不管CP脉冲和JK的状态如何,输出立即清零,实现异步清零的功能;当置数端SET出现低电平时,而且必须当CP脉冲为上升沿时,输出立即置数‘1‘,实现同步置数的功能;除此之外,当CP脉冲为上升沿状态时,J=K=0,Q保持;J=0,K=1,Q置零;J=1,K=0,Q置1;J=K=1,Q翻转一、8位锁存器的VHDL设计1.实体框图D[0..7] clk Q[0..7]latch8a2.程序设计①编译前的程序Library ieee;use ieee.std_logic_1164.all;Entity latch8a isport(D:in std_logic_vector(7 to 0);clk:in std_logic;Q:out std_logic_vector(7 to 0));End latch8a;Architecture three of latch8a issignal q1:std_logic_vector(7 to 0);beginprocess (clk,D)beginif clk'event and clk='1' thenQ1<=D;end if;end process;Q<=Q1;End architecture three;②程序编译错误情况错误:无③正确的程序Library ieee;use ieee.std_logic_1164.all;Entity latch8a isport(D:in std_logic_vector(0 to 7);clk:in std_logic;Q:out std_logic_vector(0 to 7));End latch8a;Architecture three of latch8a issignal q1:std_logic_vector(0 to 7);beginprocess (clk,D)beginif clk'event and clk='1' thenend if;end process;Q<=Q1;End architecture three;3.仿真波形图4.仿真波形分析当CLK脉冲为高电平时,输出为与其相对应的输出。

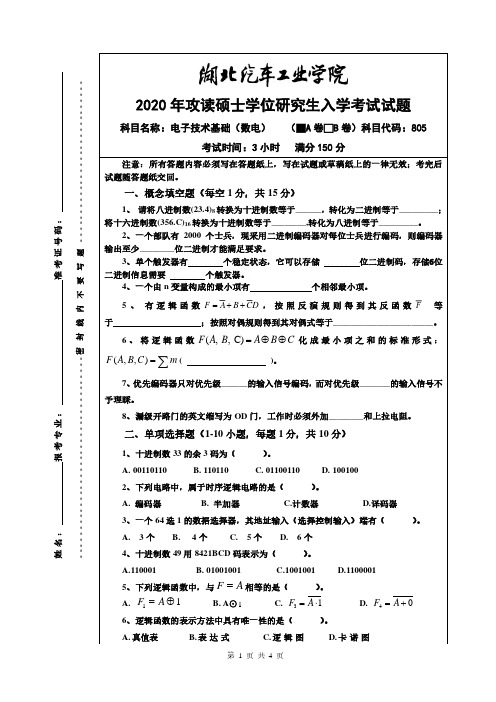

湖北汽车工业学院电子技术基础(数电A 2014--2020年考研初试真题+2016答案+2014答案

)。

A.110001

B. 01001001

C.1001001 D.1100001

5、下列逻辑函数中,与 F = A 相等的是(

)。

A. F1 = A 1

B. A⊙1

C. F3 = A1

6、逻辑函数的表示方法中具有唯一性的是(

)。

D. F4 = A + 0

A. 真值表

B. 表 达 式

C. 逻 辑 图

D. 卡 诺 图

F ( A, B,C) = m (

)。

报考专业:

7、优先编码器只对优先级______的输入信号编码,而对优先级_______的输入信号不 予理睬。

8、漏级开路门的英文缩写为 OD 门,工作时必须外加________和上拉电阻。

二、单项选择题(1-10 小题,每题 1 分,共 10 分)

1、十进制数 33 的余 3 码为(

图1 2、(本题 16 分)3 线-8 线译码器 74LS138 构成的电路如图 2 所示, A、B、C 为输 入变量。 (1)试写出输出函数 Z1 和 Z2 的表达式;(6 分) (2)列出 Z1 和 Z2 的真值表;(6 分) (3)描述 Z1 和 Z2 的逻辑功能。(4 分)

第2页共4页

图2 3、(本题 16 分)请用与非门设计一表决电路。共有包括班主任 A 在内的 4 人(A、B、 C、D)参加某学生集体的三好生投票,结果用 F 表示。多数人投赞成票可以通过,其中 班主任投否决票不通过,即班主任具有一票否决权。其中投赞成票用 1 表示,否决票用 0 表示,投票通过用 1 表示,投票不通过用 0 表示。要求:(1)列出真值表(6 分);(2)写出 逻辑表达式;(6 分)(3)画出逻辑图(仅限与非门)(4 分)。 4、(本题 16 分)分析如图 3 所示时序电路的逻辑功能,写出电路的激励方程组、状 态方程组,画出状态转换表、状态转换图和逻辑功能。

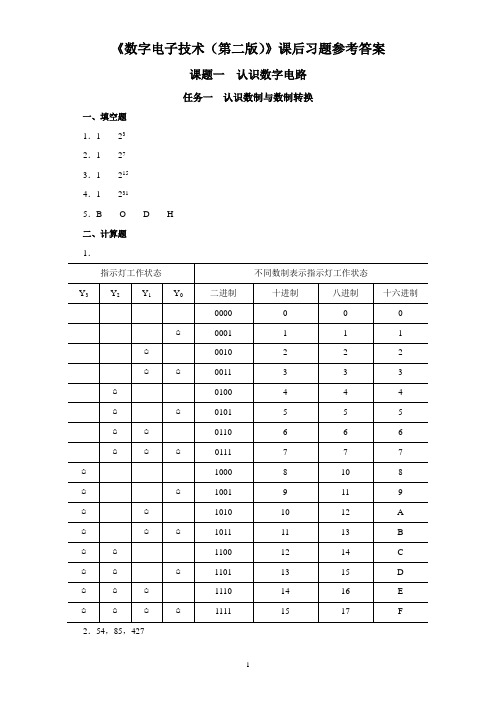

《数字电子技术(第二版)》课后习题参考答案

《数字电子技术(第二版)》课后习题参考答案课题一认识数字电路任务一认识数制与数制转换一、填空题1.1 232.1 273.1 2154.1 2315.B O D H二、计算题1.2.54,85,4273.0101,1100,1 1000,11 01114.17O,37O,66 O5.110B,010 111B,001 101 110B6.0FH,36H,0AE63H7.0001 0110B,0010 1010B,1111 1100 0000B任务二学习二进制数算术运算一、计算题(给出的二进制均是无符号数)1.(1)1 0000 (2)1 0000 10012.(1)10 1010 (2)1010 11113.(1)1 0100 (2)110 00004.(1)101 (2)11二、写出下列带符号位二进制数(原码)所表示的十进制数(1)+110 (2)-15 (3)-42 (4)+127 (5)+111(6)-63 (7)+0 (8)+32 767 (9)-32 768三、问答题1.(1)答:左移,移动3位,应作乘以8运算。

(2)答:左移,移动4位,应作乘以16运算。

(3)答:右移,移动7位,应作除以128运算。

(4)答:右移,移动3位,应作除以8运算。

2.答:4位二进制无符号数的最大值是15。

3.答:8位二进制无符号数、有符号数的最大值分别是255和+127。

4.答:16位二进制有符号数的最大值是+32 767。

任务三学习二进制代码一、填空题1.二进制数2.43.8,4,2,1二、判断题1.×2.× 3.√ 4.× 5.× 6.×三、计算题1.36,55,892.[0011 0010]8421,[0101 0010 0111]8421,[0001 0011 0110 1001]8421任务四认识基本逻辑关系并测试逻辑门一、填空题1.与或非2.13.04.1 05.Y=AB6.Y=A+B7.Y=A8.Y=AB9.Y=A+B10.Y=A B=AB+AB二、选择题1.D 2.A 3.B,C 4.A,D三、判断题1.× 2.× 3.× 4.√四、问答题1.答:Y1=ABCD2.答:Y2=A+B+C+D五绘图题1.2.3.4.任务五测试TTL集成门电路1.答:TTL集成门电路电源电压范围为4.75~5.25V之间,额定电压为5V。