抗总剂量辐射华夫饼功率管版图设计

大规模集成电路浮栅ROM器件总剂量辐射效应

第27卷 第1期2006年1月半 导 体 学 报CHIN ESE J OURNAL OF SEMICONDUCTORSVol.27 No.1J an.,2006通信作者.Email :baopinghe @ 2005208214收到,2005209225定稿ν2006中国电子学会大规模集成电路浮栅ROM 器件总剂量辐射效应何宝平1,2, 周荷琴1 郭红霞2 周 辉2 罗尹虹2 姚志斌2 张凤祁2(1中国科学技术大学,合肥 230026)(2西北核技术研究所,西安 710024)摘要:提出了一种大规模集成电路总剂量效应测试方法:在监测器件和电路功能参数的同时,监测器件功耗电流的变化情况,分析数据错误和器件功耗电流与辐射总剂量的关系.根据该方法利用60Co γ射线进行了浮栅ROM 集成电路(A T29C256)总剂量辐照实验,研究了功耗电流和出错数量在不同γ射线剂量率辐照下的总剂量效应,以及参数失效与功能失效时间随辐射剂量率的变化关系,并利用外推实验技术预估了电路在空间低剂量率环境下的失效时间.关键词:大规模集成电路;总剂量效应;低剂量率;失效时间PACC :6180E ;7340Q EEACC :2560R 中图分类号:TN38611 文献标识码:A 文章编号:025324177(2006)01201212051 引言目前我国航天器上已经大量使用大规模集成电路,然而,空间辐射环境中的带电粒子和电子产生的电离总剂量效应会导致大规模集成电路功能异常,严重影响航天器的可靠性及在轨寿命.近年来,大规模集成电路的总剂量辐射效应一直是国外辐射效应研究领域的热点[1,2],国内在小规模电路的效应机理、实验测量以及模拟方法等方面取得了一定的成绩[3~6].我们以往的总剂量效应研究都是针对中小规模集成电路,特别是门电路,大规模集成电路(存储器和CPU 等)的总剂量效应如何测试,抗总剂量水平如何评价,这些都是需要解决的问题.国外尚无统一规范的实验方法,目前国内对于大规模集成电路的总剂量效应研究尚处于探索阶段.大规模集成电路浮栅ROM 器件(主要是FL ASH ROM 和EEPROM )在单一的工作电压下,就可以完成读出、擦除和写入功能,克服了原有只读存储器(ROM )的不足;而且和静态随机存取存储器(SRAM )相比,其存储的数据是非挥发性的,即使掉电,也不会丢失数据.因此,浮栅ROM 集成电路已被广泛应用于包括航天器在内的各领域的电子系统中,开展浮栅ROM 集成电路的总剂量辐射效应研究具有重大的现实意义和应用价值.本文给出了初步的大规模集成电路总剂量效应的测试方法,并利用该方法对大规模集成电路浮栅ROM 器件总剂量辐射效应进行了研究.2 总剂量效应测试方法总剂量效应一个重要的敏感参数就是阈值电压,对于门电路、反相器等中小规模集成电路,主要测试其阈值电压随辐照剂量的变化.对于单个晶体管,可以得到氧化物陷阱导致的阈值电压漂移量和界面陷阱电荷导致的阈值电压漂移量.然而,对于由成千上万只nMOS 和pMOS 晶体管组成的大规模集成电路,仅有几十个管脚,目前尚无有效的方法来测量某个晶体管的阈值电压.因此,适用于小规模集成电路的总剂量效应测试方法无法应用于大规模集成电路.如果许多nMOS 晶体管的准静态电流增大,就会导致器件的功耗电流增大.随辐射电离总剂量的继续增加,阈值电压漂移越来越大,原本应该截止的晶体管导通(或相反)时,器件会出现逻辑功能错误,引起数据错误或运算错误.浮栅ROM 集成电路的集成度高,采用传统的方法测量内部某个晶体管的敏感参数(如阈值电压)不太容易,因此我们提出初步的总剂量效应测试方法:在线监测器件和电路功能参数的同时,监测器件功耗电流的变化情况.器件在进行辐照前,每个字节写入数据,在辐照过程中循环读取存储单元中的数据,与辐照前作比较,记录出错单元,统计出错类型和数量,同时监测器件功耗电流的变化情况,分析数据错误和器件功耗电流与辐射总剂量效应的变化关半 导 体 学 报第27卷系.3 辐射实验辐照实验是在西北核技术研究所的4000居里Co260γ源上进行,辐照温度为室温,利用UN IDOS 剂量仪标定的辐照剂量率有:50rad(Si)/s,16156rad (Si)/s,2193rad(Si)/s,0126rad(Si)/s四种.实验电路为浮栅ROM集成电路A T29C256,分两类:一类为A T29C256(9911),另一类为A T29C256(9939).辐照前每个字节写入数据“55H”,即:“0”与“1”相互间隔.在加电(+5V)状态下辐照,用存储器辐照效应测试系统和电流测试系统动态连续、实时监测被测电路的功能和功耗电流的大小,实时读取数据,统计出错单元的数量和功耗电流值,辐照结束后,继续室温在线监测半小时.4 实验结果4.1 总剂量辐射效应我们根据以往的研究了解到,受辐射的非加固CMOS器件,能够在栅氧化层中诱导产生氧化物陷阱电荷累积,这种累积的电荷能够引起CMOS晶体管阈值电压发生漂移.但是,辐射同样也会在场氧化层中发生氧化物陷阱电荷的积累,这样的电荷积累导致器件漏电情况增加.因此,对于许多非加固的集成电路来讲,功耗电流是一个敏感的辐射损伤参数.实验中,我们把功耗电流作为浮栅ROM集成电路一个辐射敏感参数,来研究其总剂量辐射效应.同时,利用存储器测试系统实时、在线监测集成电路出错数量与辐照剂量的变化,研究电路功能与辐照剂量的关系.图1,2分别给出了浮栅ROM集成电路A T29C256在不同剂量率辐照下,功耗电流和出错数量随时间的变化关系.因为集成电路辐照后第一个测量点的功耗电流与辐照前相比,基本没发生什么变化,它可以反映电路辐照前的电流情况,故图1中没有给出辐照前的数据点.图2给出的是辐照后翻转数与时间的变化关系,因为辐照前电路的翻转数为零.从图1,2中可以看出,剂量积累到一定程度,功耗电流逐渐增大,当电流增大到一定值时,出现数据错误.电路出现数据错误有个累积剂量阈值,当累积剂量小于某一个值时,无数据错误.当累积剂量达到一定值时,开始出现数据错误.随着累积剂量的增加,错误数量迅速增加.功耗电流和出错数量都随着辐照时间的增加而逐渐增加.这主要是因为γ辐射在浮栅及其周围的绝缘层内电离产生电子空穴对.图1 不同剂量率辐照下,功耗电流随辐照时间的变化Fig.1 At radiation of different dose rates,A T29C256 supply current versus time电子空穴在电场的作用下漂移,在界面处形成界面陷阱电荷,使晶体管的阈值电压向负方向漂移.当界面陷阱电荷积累到一定程度,使原来截止的晶体管导通,存储单元的状态发生变化,出现数据错误.由于界面陷阱电荷的积累需要一定的剂量积累,因此,错误的发生存在累积剂量阈值.随着γ累积剂量的增加,阈值电压漂移的晶体管数目增加,错误数量增加.刚开始出错时的错误单元和数据,错误数量及错误地址都不确定,即在某一时刻错误多,而在下一时刻,错误反而少了;某一单元在这一时刻出错,而在下一时刻却是正确的,出现不确定错误.这是由于阈值电压漂移量不大时,晶体管处于截止和导通的临界状态,没有使存储单元由一种状态彻底变为相反状态.在存储单元状态彻底改变之前的一段时间内,其状态是不确定的.实验中发现A T29C256器件的数据错误全是由“0”变成“1”,这时候对应的浮栅晶体管由截止变为导通,导致功耗电流增大.这种由“0”变成“1”的现221第1期何宝平等: 大规模集成电路浮栅ROM器件总剂量辐射效应图2 不同剂量率辐照下,错误数量随辐照时间的变化Fig.2 At radiation of different dose rates,A T29C256 error number versus time象随辐照时间的增加而增加,所以功耗电流随辐照时间的增加而增加.为了研究浮栅ROM器件29C256辐照后高温退火特性,我们将剂量率(50rad(Si)/s)辐照失效的浮栅ROM29C256器件置于70℃和100℃环境中进行高温退火,实验结果如图3所示.比较图2和图3,一方面可以看出,图2中50rad(Si)/s辐照结束时,器件出错数约为104位,而在70℃和100℃环境中开始退火时的出错数约为103位,这主要是因为器件在室温放置1h后出现退火恢复效应所致.另一方面可以看出,室温25℃环境下,器件出错数随退火时间的增加而减少,表现出明显的恢复效应,而100℃环境下出错数恢复比70℃要快,并且出错数开始随着退火时间的增加而增加,退火1000s后,出错数随退火时间的增加而开始减少,对于这种高温退火异常的详细解释,有待于进一步深入研究.4.2 空间低剂量率效应预估实验室条件下研究浮栅ROM集成电路图3 不同温度下,A T29C256出错数量随退火时间的变化Fig.3 At70℃and100℃,A T29C256error number versus anneal timeA T29C256不同剂量率下的辐射响应,目的是确定电路在剂量率降低的辐射响应趋向.本文介绍了一种利用实验室高剂量率辐射实验数据来外推空间低剂量率的辐射响应方法.该方法的主要思想是:根据定义的失效判据,将每一种剂量率辐射结果外推到失效定义值,可以得到不同剂量率辐射下的失效时间.然后将失效时间拟合成剂量率的函数,进而可以预估空间低剂量率的失效时间.在本研究中,我们定义浮栅ROM集成电路(A T29C256)失效判据:功耗电流超过100mA或者出错数超过10%为失效,也就是说,出错数超过25600为失效.图4(a),(b)分别给出了A T29C256(9911)集成电路不同剂量率辐照下,功耗电流和出错数的拟合、外推以及失效时间的提取过程.根据定义的失效判据,我们将从图4 (a)、(b)中提取的在不同剂量率辐照下的失效时间进行拟合,得到如下方程:T=10(A lg D+B)(1)其中 T为失效时间;D为辐照剂量率rad(Si)/s, A,B为常数.表1给出了拟合A T29C256(9911)和A T29C256(9939)实验数据,满足方程(1)的A,B 常数.表1 A T29C256(9911)和A T29C256(9939)满足方程(1)的常数A,BTable1 Constant A and B of equation(1)forA T29C256(9911)and A T29C256(9939)器件类型A T29C256(9911)A T29C256(9939)A B A B按功耗电流拟合-0.967 4.643-1.620 5.486按出错数量拟合-0.970 4.297-1.791 5.276利用方程(1)和表1中的数据,我们给出了浮栅ROM集成电路A T29C256失效时间随辐照剂量率的关系,见图5.对于典型的10-3rad(Si)/s空间剂321半 导 体 学 报第27卷图4 不同剂量率辐照下,实验数据的拟合和外推结果 (a)功耗电流;(b)出错数量Fig.4 Under different dose rate irradiation,fitting and extrapolation of experimental data量率环境,A T29C256(9911)电路按照功耗电流数据预估电路的失效时间约为314×107s,按照出错数预估电路的失效时间约为210×107s;A T29C256 (9939)电路按照功耗电流数据预估电路的失效时间约为212×1010s,按照出错数预估电路的失效时间约为414×1010s.5 结束语上述研究表明,对于大规模集成电路浮栅ROM器件,采取在监测器件和电路功能参数的同时监测器件功耗电流变化这一方法是可行的,有利于分析大规模集成电路总剂量效应.而且在我们并不详细了解其辐射损伤机理的情况下,在实验室条件下根据不同剂量率辐射的功耗电流和出错数量,利用外推技术可以预估集成电路在空间低剂量率的辐射效应.图5 A T29C256集成电路失效时间随辐射剂量率的变化Fig.5 Time to failure versus dose rate for A T29C256参考文献[1] Nguyen D N,Guertin S M,Swift G M,et al.Radiationeffect s on advanced flash memories.IEEE Trans Nucl Sci,1999,46(6):1744[2] Lelis A J,Murrill S R,Oldham T R,et al.Radiation responseof advanced commercial SRAMs.IEEE Trans Nucl Sci,1996,43(6):3103[3] Yao Yujuan,Zhang Zhengxuan,Jiang Jinghe,et al.Bias an2nealing of radiation induced positive trapped charges in metaloxide semiconductor transistor.Chinese Journal of Semicon2ductors,2000,21(4):378(in Chinese)[姚育娟,张正选,姜景和,等.MOS晶体管中辐照引起的陷阱正电荷的强压退火.半导体学报,2000,21(4):378][4] He Baoping,G ong Jiancheng,Wang Guizhen,et al.Isot hermaland isochronal annealing characteristics in irradiated MOS de2vices.Chinese Journal of Semiconductors,2004,25(3):302(inChinese)[何宝平,龚建成,王桂珍,等.CMOS器件的等时、等温退火效应.半导体学报,2004,25(3):302][5] He Baoping,Yao Yujuan,Peng Honglun,et al.Influence oftemperatures and radiation dose rate on CMOS device charac2teristic parameter.Chinese Journal of Semiconductors,2001,22(6):779(in Chinese)[何宝平,姚育娟,彭宏论,等.环境温421第1期何宝平等: 大规模集成电路浮栅ROM器件总剂量辐射效应度、电离辐射剂量率对NMOSFET器件特性参数的影响.半导体学报,2001,22(6):779][6] He Baoping,Wang Guizhen,Zhou Hui,et al.PredictingnMOS device radiation response at different dose rates inγ2rays environment.Acta Physica Sinica,2003,52(1):188(in Chinese)[何宝平,王桂珍,周辉,等.nMOS器件不同剂量率γ射线辐射响应的理论预估.物理学报,2003,52(1):188]Total Dose E ffect of Large2Scale Integrated Circuit Floating G ate ROM DevicesHe Baoping1,2, ,Zhou Heqin1,Guo Hongxia2,Zhou Hui2,L uo Y inhong2,Yao Zhibin2,and Zhang Fengqi2(1Universit y of Science and Technology of China,Hef ei 230026,China)(2N ort hwest I nstit ute of N uclear Technology,X i’an 710613,China)Abstract:A method for testing total dose effects is presented for VL SI.The consumption current of the device is measured. Meanwhile,the f unction parameters of the device and circuit are also measured.The relations between data errors,consumption current and total radiation dose are analyzed.Ionizing radiation experiments are performed on floating gate ROM devices by u2 sing60Coγ2rays as prescribed by this test method.The experimental aim is to examine the radiation response at various dose rates.The parameters and function failure of the devices as f unction of dose rate are studied.By extrapolation,we predict the failure time of a floating gate ROM device in a space radiation environment.K ey w ords:very large scale integrated circuits;total dose effect;low dose rate;failure timePACC:6180E;7340Q EEACC:2560RArticle ID:025324177(2006)0120121205Corresponding aut hor.Email:baopinghe@ Received14August2005,revised manuscript received25September2005ν2006Chinese Institute of Electronics521。

总剂量辐照与热载流子协同效应特性分析

V o 1 . 3 5N o . 6De e . ,2 0 1 7

总剂量辐 照与热载流子协 同效应特性分析 ★

4 4 -  ̄ , 中・ ,何 玉娟 2 郑婕 2 章 晓文

( 1 . 中 国 电子 科 技 集 团公 司第 五 十 四研 究 所 ,河 北 石 家 庄 0 5 0 0 0 0 ; 2 . 工 业 和 信 息 化 部 电 子 第 五 研 究 所 。广 东 广 州 5 1 0 6 1 0 )

2 . C E P R E I ,G u a n g z h o u 5 1 0 6 1 0 ,C h i n a )

Ab s t r a c t : Th e e fe c t o f t o t a l d o s e i r r a d i a t i o n o n t h e h o t c a r r i e r t e s t o f 0 . 3 5 t t m NM oS

d o i : 1 0 . 3 9 6 9  ̄ . i s s n . 1 6 7 2 - 5 4 6 8 . 2 0 1 7 . 0 6 . o o 3

The Ch a r a c t e r i s t i c An a l y s i s o f Co o p e r a t i v e Ef f e c t 0 f

Ke y wo r ds :t o t a l d o s e i r r a d i a t i o n;h o t c a r r i e r t e s t ;c o o p e r a t i v e e f f e c t

0 引 言

在空 间长 时 间运行 的设 备 和器 件 .在 受到 空间 辐 射效 应 影响 的 同时 .也会 由于热 载流 子 效应 的影

SOI技术的抗辐照能力报告

SOI技术的抗辐照能力报告目录SOI技术的定义: (3)SOI技术的特点: (3)空间辐射问题: (5)电子元器件所受到的辐射效应分类 (7)常用的四种抗辐射材料: (7)SOI抗辐照技术 (8)SOI技术的抗辐射指标 (8)SOI技术和体硅CMOS技术两种技术抗辐射效应的对比 (8)SOI器件实例: (9)SOI技术的应用: (10)SOI技术国际主流公司: (10)SOI产业联盟: (11)国内SOI技术研究: (11)SOI技术的市场份额: (12)SOI技术的定义:SOI技术是指:在硅衬底上嵌入绝缘体埋层,再在埋层上生长单晶硅薄膜的材料制备技术。

SOI是英文Silicon On Insulator的缩写,指的是绝缘层上的硅。

SOI技术是指在绝缘层上形成一层具有一定厚度的单晶半导体硅薄膜的材料制备技术。

SOI材料可实现完全的介质隔离,与由PN结隔离的体硅相比,具有无闩锁、高速率、低功耗、集成度高、耐高温等特点,在便携式电子产品、航天、卫星通讯等领域均受到普遍重视,被称为“21世纪的微电子技术”。

SOI(Silicon-On-Insulator)字面意思是绝缘体上硅,可以理解为一种特殊结构的硅材料。

而SOI技术却包含非常丰富的内容。

SOI 技术也包括材料、器件和集成电路制造技术。

SOI技术的特点:SOI技术作为一种全介质隔离技术,有着许多体硅技术不可比拟的优越性。

在SOI技术中,器件仅制造于表面很薄的硅膜中,器件与衬底之间由一层隐埋氧化层隔开,正是这种独特的结构使得SOI技术具有了体硅器件所无法比拟的优点。

SOI CMOS器件具有功耗低、抗干扰能力强、集成密度高(隔离面积小)、速度高(寄生电容小)、工艺简单、抗辐照能力强,并彻底消除了体硅CMOS器件的寄生闩锁效应等优点。

随着SOI顶层硅膜厚度减薄到全耗尽工作状态(硅膜厚度小于有效耗尽区宽度)时,全耗尽的SOI 器件将比传统SOI 器件具有更优越的特性,这种全耗尽SOI 结构更适合于高性能ULSI 和VHSI 电路。

SOI技术的抗辐照能力报告.doc

SOI技术的抗辐照能力报告SOISOI 技术的抗辐照能力报告技术的抗辐照能力报告目录目录 1 关于关于SOISOI 抗辐照技术的可行方案抗辐照技术的可行方案 3 2 2 SOISOI 技术简介技术简介.4 2.1 SOI 技术的定义4 2.2 SOI 技术的特点4 3 3 SOISOI 技术的研究现状技术的研究现状.7 3.1 常用的四种抗辐射材料.7 3.2 SOI 技术的应用7 3.3 SOI 技术国际主流公司8 3.4 SOI 产业联盟9 3.5 国内SOI 技术研究.9 3.6 SOI 技术的市场份额10 4 4 空间辐射问题空间辐射问题10 4.1 航天器面临的辐射环境.10 4.2 电子元器件所受到的辐射效应.12 5 5 SOISOI 抗辐照技术抗辐照技术.13 5.1 SOI 技术的抗辐射指标13 5.2 SOI 器件实例13 5.3 SOI 技术和体硅CMOS 技术两种技术抗辐射能力的对比14 5.4 SOI 不加固的抗辐照性能14 5.5 体硅不进行抗辐射加固的抗辐照性能.15 5.6 目前国内SOI 技术的工艺水平.16 5.6.1 0.8um 工艺芯片的集成度16 5.6.2 0.8um 工艺与0.18um 工艺集成度的差异17 6 6 STISTI 侧沟道隔离技术侧沟道隔离技术.17 6.1 隔离的目的.17 6.2 隔离技术的要求.18 6.3 常见的隔离工艺技术.18 6.4 LOCOS 隔离技术18 6.5 改进的LOCOS 结构隔离技术.20 6.6 STI 隔离技术22 1 关于关于SOISOI 抗辐照技术的可行方案抗辐照技术的可行方案国内现有四家做抗辐照方面研究的单位(1)七七一所目前在抗辐照芯片开发方面,工艺比较落后;(2)七七二所用体硅进行抗辐照加固做了一批抗辐照芯片,采用0.18um 工艺,在中芯国际流片,抗辐照指标达不到航天水平,只有一款芯片投入了实际应用,最近出了问题;而且芯片封装仅有391 个引脚。

EEPROM单元抗辐射版图设计技术

摘

要 :随着 E P O 存储 器件在太 空和军事领域 的广泛应 用,国际上对 E P M 抗辐射性 能的 ER M E RO

研 究越 来越 多。 为 了达 到提 高存储 器件抗 辐射 性 能的 目的 ,文章从 版 图设计的 角度 出发 ,首先 分

热点之一【 卜 。文章在现有的工艺基 础之上 ,研究 了

中图分类号 :T 4 2 N 0

文献标识码 :A

文章编号 :18 —0 0 (0 0 502 .3 6 117 2 1 )0.020

TheRa i to r e e y u sg o d a i n Ha d n d La o t De i n f rEEPROM l Cel

Z A i L NH i a ,H UXn i H OL, A aynZ O T - ij -e

( hn l t nc cn l yG opC roai o5 ee rh ntue W x 10 5 C i ) C ia e r i T h oo ru op rt n . R sac si t ui 4 3 , h a E co se g oN 8 I t , 2 n

o r s n o k b ts p l ahul e ee c o a a inh d n d ly u e i ni u u e f e e t r , u u p y awr t f fr n ef rrdito a e e a o td sg nf tr . p w r r Ke r : y WO ds EEP ROM elrd ainh d n d ly u if r e e t c l;a ito a e e ;a o ten o c m n r r

星载电子设备抗辐照分析及元器件选用

星载电⼦设备抗辐照分析及元器件选⽤⾃1971年⾄1986年期间,国外发射的39颗同步卫星因各种原因造成的故障共计1589次,其中与空间辐射有关的故障有1129次,占故障总数的71%,由此可见卫星和航天器的故障主要来源于空间辐射。

1、抗辐照分析 空间辐照环境中的带电粒⼦会导致星载电⼦设备⼯作异常和器件的失效,严重影响航天器的可靠性和寿命。

星载电⼦设备在⼯作期间所遇到的辐照问题主要是受到空间⾼能粒⼦(重离⼦和质⼦)的影响。

1.1 总剂量效应总剂量效应指在电⼦器件的特性(电流、电压门限值、转换时间)发⽣重⼤变化前,器件所能承受的总吸收能量级,超过这个能量级后器件就不能正常⼯作(出现永久故障)。

该剂量⽤Rad(Si)即存积在1gSi中的能量来度量。

典型轨道预计辐射量见表1。

总剂量效应会引起星上电⼦器件的物理效应和电器效应如产⽣电⼦空⽳对、影响载流⼦的流动、对双极型器件会降低其增益,对CMOS器件会使其阈值电压漂移、降低转换速率等。

另外在对某星载雷达所⽤CMOS器件进⾏总剂量实验时发现,总剂量效应在器件断电后会有⼀定的退⽕现象,但如果再加⼤辐射剂量,退⽕后的器件很快就不能⼯作。

所以对长寿命、⾼可靠的星载电⼦设备,必须考虑元器件的在轨期间的总剂量问题。

对于总剂量效应的防护可采⽤如下2种⽅法。

(1)选择半导体⼯艺:选择对宇宙射线不敏感的材料,CMOS蓝宝⽯硅⽚(SOS)⼯艺是⽬前最合适的⼯艺,但其成本⾼于其⼯艺。

(2)辐射屏蔽:卫星的结构框架以及电⼦设备的外壳的屏蔽作⽤可减轻辐射的影响,⼀般可减少2krad~3krad。

因为屏蔽材料本⾝有2次辐射,所以它并不能有效地防护⾼能粒⼦(宇宙射线)产⽣的影响。

2、单粒⼦效应 空间辐照环境使星载电⼦器件产⽣单粒⼦现象(SEP)。

随着电⼦器件集成度不断提⾼,器件尺⼨不断减⼩,星载电⼦设备也变得更加复杂,电⼦系统更易受到瞬态⼲扰,因此在星载电⼦系统的设计过程中不仅要考虑辐射总剂量的影响同时也要研究⾼能粒⼦引起的单粒⼦现象。

0.13 μm CMOS工艺抗辐射触发器优化设计

0.13 μm CMOS工艺抗辐射触发器优化设计李晓蓉;周昕杰【摘要】随着体硅CMOS工艺尺寸不断减小、集成度不断提高,电路受到单粒子辐射效应的影响会变得越来越严重.在大尺寸工艺条件下常用的DICE结构触发器结构,在受到单粒子效应影响后,会产生一定脉宽的扰动并传输至下一级,对整个电路的可靠性产生影响.为消除上述影响,采用了C单元结构对触发器的输出端口进行优化设计,将原有的一个结点输出结构优化为利用两个互补的存储结点作为C单元结构的输入.利用仿真手段对优化后的结构进行验证,证明了优化后的结构有很好的抗扰动能力,同时通过优化版图设计,提升触发器结构的抗辐射能力.经过此次对触发器的优化设计,为今后超深亚微米抗辐射电路的设计提供了借鉴.【期刊名称】《电子与封装》【年(卷),期】2015(015)010【总页数】4页(P26-29)【关键词】辐射效应;抗辐射设计;触发器【作者】李晓蓉;周昕杰【作者单位】中国电子科技集团公司第58研究所,江苏无锡214035;中国电子科技集团公司第58研究所,江苏无锡214035【正文语种】中文【中图分类】TN303随着我国航天事业的不断发展,集成电路在空间环境中的应用越来越多,这就对电路在辐射环境中的可靠性提出了很高的挑战。

目前,被大家熟知的辐射效应包括:总剂量效应和单粒子效应[1]。

随着体硅CMOS工艺尺寸不断减小、集成度不断提高,电路受总剂量效应的某些影响会有所改善,但受单粒子效应的影响会愈加严重。

特别是对低压、高频电路而言,单粒子效应会导致整个电路数据传输出错,导致电路失效、可靠性降低。

所以,国内外对单粒子效应展开了很多的研究[2~4]。

此次,针对大尺寸条件下常用的双互锁(DualInterlocked storage Cell, DICE)触发器加固结构[5],基于0.13 μm体硅CMOS工艺条件,分析了该触发器在低压、高频工作条件下抗单粒子辐射效应的缺陷,并对原有的DICE结构进行了优化。

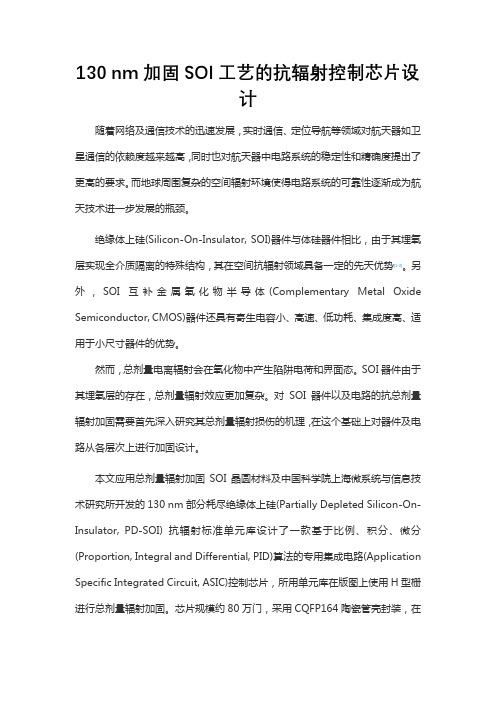

130 nm加固SOI工艺的抗辐射控制芯片设计

130 nm加固SOI工艺的抗辐射控制芯片设计随着网络及通信技术的迅速发展,实时通信、定位导航等领域对航天器如卫星通信的依赖度越来越高,同时也对航天器中电路系统的稳定性和精确度提出了更高的要求。

而地球周围复杂的空间辐射环境使得电路系统的可靠性逐渐成为航天技术进一步发展的瓶颈。

绝缘体上硅(Silicon-On-Insulator, SOI)器件与体硅器件相比,由于其埋氧层实现全介质隔离的特殊结构,其在空间抗辐射领域具备一定的先天优势[1-3]。

另外,SOI互补金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)器件还具有寄生电容小、高速、低功耗、集成度高、适用于小尺寸器件的优势。

然而,总剂量电离辐射会在氧化物中产生陷阱电荷和界面态。

SOI器件由于其埋氧层的存在,总剂量辐射效应更加复杂。

对SOI 器件以及电路的抗总剂量辐射加固需要首先深入研究其总剂量辐射损伤的机理,在这个基础上对器件及电路从各层次上进行加固设计。

本文应用总剂量辐射加固SOI晶圆材料及中国科学院上海微系统与信息技术研究所开发的130 nm部分耗尽绝缘体上硅(Partially Depleted Silicon-On-Insulator, PD-SOI) 抗辐射标准单元库设计了一款基于比例、积分、微分(Proportion, Integral and Differential, PID)算法的专用集成电路(Application Specific Integrated Circuit, ASIC)控制芯片,所用单元库在版图上使用H型栅进行总剂量辐射加固。

芯片规模约80万门,采用CQFP164陶瓷管壳封装,在基础功能测试通过后进行总剂量辐照试验。

试验在模拟空间辐射的环境下进行,结果表明被测试芯片的总剂量加固能力达到300 krad(Si),可以完全满足空间应用的需求。

1 基于PID控制算法的芯片设计1.1 PID控制算法分析图1为PID算法的原理示意图,PID控制采用比例、积分、微分方法进行闭环控制,具有架构简单、易于实现、鲁棒性强等特点[6]。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

G DS D

G DS D

G

(a)

positive trapped charge

(b)

positive trapped charge

source gate drain

LOCOS field oxide

P-type substrate

bird’s beak

source gate

drain

shallow trench field oxide

Keywords:total ionizing dose radiation;power MOSFET;waffle layout;leakage current

功率管大量用于功率集成电路中,通常会占据芯片很大的版图面积。在空间辐射环境下,功率管的电学参 数会发生退化,影响功率集成电路的正常功能。总剂量辐射效应会导致功率管发生阈值电压漂移和漏电增加[1]。 通常空间环境使用的集成电路都是通过特殊的抗辐射工艺生产出来的,但这些特殊工艺都较复杂且电学性能落 后于商用标准工艺。随着工艺线宽不断缩小,氧化层的厚度变得越来越薄,由辐射诱发的电荷被氧化层俘获的 机率将会降低,集成电路对辐射总剂量效应变得不那么敏感。因此可以在小线宽商用工艺线下,通过抗辐射加 固的版图设计[2]来提升集成电路的抗总剂量辐射能力,从而避免复杂的工艺过程调整。

沟道功率管和新型华夫饼结构 N 沟道功率管进行了 Co-60 辐射实验。总剂量辐射使 N 沟道条形栅

功率管发生漏电。辐射实验结果表明,经过无边缘化处理的漏电,能够大幅提升功率管的抗总剂量辐射能力。

关键词:总剂量辐射;功率管;华夫饼结构;漏电流

中图分类号:TN386.1

Fig.1 Typical layout of power MOSFET with fingers 图 1 典型条形栅功率管版图结构

Fig.2 Cross section of (a) LOCOS isolated and (b) shallow-trench isolated MOSFET

收稿日期:2018-01-19;修回日期:2018-04-13,第一作者姓名:周枭,E:\TJ 基金项目:国家自然科学基金联合基金(NSAF)资助项目(U1630117) *通信作者:罗 萍 email:pingl@

第4期

周 枭等:抗总剂量辐射华夫饼功率管版图设计

731

field oxide G G

文献标志码:A

doi: 10.11805/TKYDA201904.0730

Design of a TID radiation hardened power MOSFET with waffle layout

ZHOU Xiao,LUO Ping*,HE Linyan,XIAO Tiancheng

(State Key Laboratory of Electronic Thin Film and Integrated Devices,University of Electronic Science and Technology of China, Chengdu Sichuan 610054,China)

第 17 卷 第 4 期

太赫兹科学与电子信息学报

2019 年 8 月

Journal of Terahertz Science and Electronic Information Technology

Vo1.17,No.4 Aug.,2019

文章编号:2095-4980(2019)04-0730-05

Abstract:Power Metal Oxide Semiconductor Field Effect Transistor(MOSFET) is widely used in power Integrated Circuit(IC). Radiation in space may cause the leakage current at the edge of the channel in power MOSFET, which will lead to the degeneration of power IC. This paper presents a new waffle layout for power MOSFET in 0.35 μm Bipolar CMOS DMOS(BCD) process. Packaged power MOSFETs with finger and waffle layout are tested after Co-60 based irradiation experiment. The Total Ionizing Dose(TID) radiation induces the leakage current only in N-channel power MOSFET with finger layout. The presented waffle layout with its edgeless structure is proved to be effective to control the leakage current, which enhances the TID-tolerance of power MOSFET a lot.

1 功率集成电路中功率管的总剂量辐射效应

1.1 普通条形栅结构功率管

图 1 为典型的条形栅功率管版图结构,可以看作由很多普通条形栅 MOS 管并联在一起。条形栅结构很容 易进行复制拼贴,也容易通过 Cadence 软件的设计规则检查(Design Rule Check,DRC),广泛用于功率管设计。 但这种条形栅结构在有源区的边缘有非常厚的场氧化层,这部分氧化层对总剂量辐射非常敏感[1]。

抗总剂量辐射华夫饼功率管版图设计

周 枭,罗 萍*,何林彦,肖天成

(电子科技大学 电子薄膜与集成器件国家重点实验室,四川 成都 610054)

摘 要:功率管在空间辐射环境下会发生沟道边缘漏电,导致功率集成电路性能退化。介绍

了一种 0.35 μm 单片集成(BCD)工艺下基于华夫饼结构的全新功率管版图,并对普通条形栅结构 N