采用kogge-stone tree 实现的32位超前进位加法器

上海大学verilog设计32位浮点加法器设计

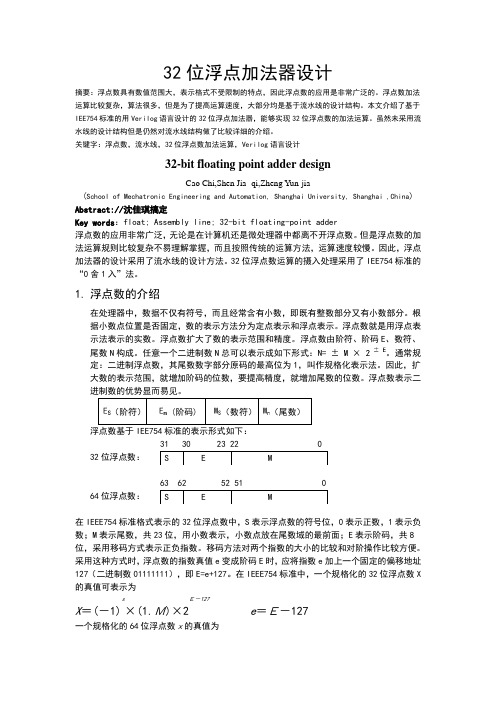

32位浮点加法器设计摘要:浮点数具有数值范围大,表示格式不受限制的特点,因此浮点数的应用是非常广泛的。

浮点数加法运算比较复杂,算法很多,但是为了提高运算速度,大部分均是基于流水线的设计结构。

本文介绍了基于IEE754标准的用Verilog 语言设计的32位浮点加法器,能够实现32位浮点数的加法运算。

虽然未采用流水线的设计结构但是仍然对流水线结构做了比较详细的介绍。

关键字:浮点数,流水线,32位浮点数加法运算,Verilog 语言设计32-bit floating point adder designCao Chi,Shen Jia- qi,Zheng Yun-jia(School of Mechatronic Engineering and Automation, Shanghai University, Shanghai ,China ) Abstract://沈佳琪搞定Key words :float; Assembly line; 32-bit floating-point adder 浮点数的应用非常广泛,无论是在计算机还是微处理器中都离不开浮点数。

但是浮点数的加法运算规则比较复杂不易理解掌握,而且按照传统的运算方法,运算速度较慢。

因此,浮点加法器的设计采用了流水线的设计方法。

32位浮点数运算的摄入处理采用了IEE754标准的“0舍1入”法。

1. 浮点数的介绍在处理器中,数据不仅有符号,而且经常含有小数,即既有整数部分又有小数部分。

根据小数点位置是否固定,数的表示方法分为定点表示和浮点表示。

浮点数就是用浮点表示法表示的实数。

浮点数扩大了数的表示范围和精度。

浮点数由阶符、阶码E 、数符、尾数N 构成。

任意一个二进制数N 总可以表示成如下形式:N=。

通常规定:二进制浮点数,其尾数数字部分原码的最高位为1,叫作规格化表示法。

因此,扩大数的表示范围,就增加阶码的位数,要提高精度,就增加尾数的位数。

数字系统设计实验---32位串行加法器实验综述

深圳大学实验报告课程名称:_________ 数字系统设计________________________ 实验项目名称: 32位串行加法器______________________ 学院_______________________ 专业_______________________ 指导教师: ______________________________________________报告人: ________ 学号:20091000000班级:1班实验时间:__________ 2011-12-4 ________________________实验报告提交时间:______________________教务处制一、实验目的与要求:实验目的:1、掌握串行加法器的原理和设计。

2、熟悉VHDL状态机的设计。

3、学会分析波形图。

实验要求:设计一个用一个1位加法器构建的一个32位串行加法器。

重点是算法状态机的实现还有系统的时序分析;输出和整理VHDL源代码;输出和整理电路结构图;输出和整理仿真波形图二、实验原理1、设计原理图:本图参考课本2、流程图:针对以上流程图,其中,Sh为控制移位寄存器的使能信号,k为工作状态指示信号,load为加载信号,counter为运算计数器,N为系统工作控制信号。

从流程图中可以看出加法器的整个工作流程是怎么样子的,具体工作情况如下面的设计。

三、实验内容与步骤1、VHDL代码的编写:----------- 控制器--------------------------------------------- library IEEE;use IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_ un sig ned.all;en tity con troller isPort ( clk : in STD_LOGIC;N : in STD_LOGIC;K,Sh,load : out STD_LOGIC);end con troller;architecture Behavioral of con troller issig nal state ,n extstate:i nteger range 0 to 2; ---设置状态sig nal coun ter:std_logic_vector(4 dow nto 0);beginprocess(clk)beginif(clk'event and clk='1') thenstate<=n extstate;end if;end process;process(clk,N)beginif(clk'event and clk='1') thencase state is ---设置各状态when 0 =>sh<='0';K<='0';load<='0';cou nter<="00000"; if N='1' the nload<='1';n extstate<=1;elsen extstate<=0;end if;when 1 =>sh<='1';K<='0';load<='0';if cou nter="11110" thencoun ter<=co un ter+1;n extstate<=2;elsecoun ter<=co un ter+1;n extstate<=1;end if;when 2 =>sh<='0';K<='1';load<='0:if N='0' the nn extstate<=0;elsen extstate<=2;end if;end case;end if;end process;end Behavioral;-------------- 加数寄存器 -------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;en tity registers_jiashu isPort ( in put : in STD_LOGIC_vector(31 dow nto 0);Sh,load,clk: in STD_LOGIC; SO : out STD_LOGIC);end registers_jiashu;architecture Behavioral of registers_jiashu is sig nal x:std_logic_vector(31 dow nto 0); begin process(clk) beginif(clk'event and clk='1') thenif (load='1‘)then x<=in put;elsif (sh='1') the n ---:x(30 dow nto 0)<=x(31 dow nto 1);end if;end if;end process;so<=x(0);end Behavioral;-------------- 累加器 ---------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;en tity registers_add isPort ( in put : in STD_LOGIC_vector(31 dow nto 0);clk : in STD_LOGIC;load,Sh,Si: in STD_LOGIC;SO : out STD LOGIC;output:out std_logic_vector(31 dow nto 0));end registers_add;architecture Behavioral of registers_add issig nal x:std_logic_vector(31 dow nto 0);beginprocess(clk)N<='0';wait for 10*clk_period; --延时10个时钟周期,进入下一轮仿真调试in putA<="01010101010101010101010101010101"; -- i nputa= 1431655765,in putB<="00110000000000000000000010101000"; -- i nputb= 805306536,N<='1'; --N=1时开始计时,并开始下载数据wait for 32*clk_period;--32 个时钟周期之后N<='0:--N=0,停止数据下载,得出相加后的结果wait for 10*clk_period; --延时10个时钟周期,进入下一轮仿真调试wait;end process;END;四、实验数据与分析1、综合的电路:设计图外观1 :adder 32l设计图外观2:adder_32oiJtputA(31:0)incl kNadder_321、控制器:2、全加器:情况二:in puta= 1431655765, in putb=805306536,outputa=2236962301Q- /adder _3 2_tE5tbendn /inputa EJ- /adder _32_te5tbenefi /inputb/adder _32_te£tbencfi /dk/adder_32Jbestberdn /n Q-」/adder_32_tEstberidi/outputa/addcr_32_testberidiA 731381211114 J1>55765805^)65363i ・i i17B957306J22369623012、仿真的波形图如下:情况一:in puta二 73,i nputb二 138,outputa=211/adder _32_t)&stlbench/inpLi taD- /adder _3 2_te&tbendi/inp*j thJ/ adder _32_testben 击/die /adder_32_testbendiAi/adder_3Z_testbendi/outputaJ/adder _32_testbench 4cD- /adder _3 2_testbendi^nputa73Q- .. add er 2_test±)endi /inpu tb133/adder _32_tes±>erKh/dk1/adder_32_testbendi /h0C- /adder _32_testberKhAxjtpu ta211/adder_32_testbencti 水1数据处理分析:每次从N=1开始,加法器进行数据下载,32个时钟周期之后,当N=0时, 输出k=1,表示串行累加的过程结束,此时输出的结果即为加法器的最后结果。

超前进位加法器设计

湖南师范大学职业技术学院(工学院)实验数据报告单实验课程:计算机组成原理实验题目:超前进位加法器设计实验日期: 2011年 10 月 25 日专业:计算机科学与技术年级:09级班级:04班姓名:涂小康学号:2009180414一.实验目的(1)掌握超前进位加法器的原理及其设计方法。

(2)熟悉CPLD应用设计及EMA软件的使用。

二.实验内容(1)设计电路原理图.(2)了解加法器的工作原理,掌握超前进位产生电路的设计方法.(3)正确将电路原理图下载到试验箱中.(4)正确通过实验箱连线实现4位二进制数的相加并得到正确结果三.实验原理加法器是执行二进制加法运算的逻辑部件,也是CPU运算器的基本逻辑部件(减法可以通过补码相加来实现)。

加法器又分半加器和全加器,不考虑低位的进位,只考虑两个二进制数相加,得到和以及向高位进位的加法器叫半加器,而全加器是在半加器的基础上又考虑了低位进来的进位信号。

串行加法器运算速度慢,其根本原因是每一位的结果就要依赖于低位的进位,因而可以通过并行进位的方式来提高效率。

只要能设计出专门的电路,使得每一位的进位能够并行地产生而与低位的运算情况无关,就能解决这个问题。

可以对加法器进位的逻辑表达式做进一步的推导:C o=0C i+1=A i B i+A i C i+B i C i=A i B i+(A i+B i)C i设G i=A i B iP i=A i+B i则有:C i+1=g i+p i C i=g i+p i(g i-1+p i-1C i-1)=g i+p i(g i-1+p i-1(g i-2+p i-2C i-2))…=g i+p i g i-1+p i p i-1g i-2+…+p i p i-1… p1p0+p i p i-1…p1p0C0由于g i、p i只和A i、B i有关,这样C i=1就只和A i、A i-1、…、A0,B i、B i-1、…、B0及C0有关。

32位浮点加法器设计

32位浮点加法器设计32位浮点加法器是一种用于计算机中的算术逻辑单元(ALU),用于执行浮点数的加法运算。

它可以将两个32位浮点数相加,并输出一个32位的结果。

设计一个高效的32位浮点加法器需要考虑多个方面,包括浮点数的表示形式、运算精度、舍入方式、运算逻辑等。

下面将详细介绍32位浮点加法器的设计。

1.浮点数的表示形式:浮点数通常采用IEEE754标准进行表示,其中32位浮点数由三个部分组成:符号位、阶码和尾数。

符号位用来表示浮点数的正负,阶码用来表示浮点数的指数,尾数用来表示浮点数的小数部分。

2.运算精度:在浮点数加法运算中,精度是一个重要的考虑因素。

通常,浮点数加法器采用单精度(32位)进行设计,可以处理较为广泛的应用需求。

如果需要更高的精度,可以考虑使用双精度(64位)浮点加法器。

3.舍入方式:浮点数加法运算中,结果通常需要进行舍入处理。

常见的舍入方式有以下几种:舍入到最近的偶数、舍入向上、舍入向下、舍入到零。

具体的舍入方式可以根据应用需求来确定。

4.运算逻辑:浮点数加法运算涉及到符号位、阶码和尾数的加法。

首先,需要判断两个浮点数的阶码大小,将较小的阶码移到较大的阶码对齐,并相应调整尾数。

然后,将尾数进行相加并进行规格化处理。

最后,根据求和结果的大小,进行溢出处理和舍入操作。

在32位浮点加法器的设计中,还需要考虑到性能和效率。

可以采用流水线技术来提高运算速度,将加法运算划分为多个阶段,并在每个阶段使用并行处理来加速运算。

此外,还可以使用硬件加速器和快速逻辑电路来优化运算过程。

总结起来,设计一个高效的32位浮点加法器需要考虑浮点数的表示形式、运算精度、舍入方式、运算逻辑以及性能和效率。

在实际设计中,还需要根据具体应用需求进行功能扩展和优化。

通过合理的设计和调优,可以实现高性能的浮点加法器,满足不同应用场景的需求。

计算机组成原理实验报告_32位ALU设计实验

实验三32位ALU设计实验一、实验目的学生理解算术逻辑运算单元(ALU)的基本构成,掌握Logisim 中各种运算组件的使用方法,熟悉多路选择器的使用,能利用前述实验完成的32位加法器、Logisim 中的运算组件构造指定规格的ALU 单元。

二、实验原理、内容与步骤实验原理、实验内容参考:1、32位加法功能的原理与设计1)设计原理1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

2)电路设计32位加法功能2、32位减法功能的原理与实现1)变减法为加法的原理1.在Y引脚处使用求补器(32位),即可变减法为加法2.用构造好的32位加法器。

Y各位取反,C0取1,即可达到减法变加法。

无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断2)电路设计32位减法功能3、加减溢出检测的设计(不考虑乘除法)1)有符号数溢出的设计有符号数溢出的设计2)无符号数溢出的设计无符号数溢出的设计4、移位的原理与设计1)逻辑移位逻辑移位2)算术移位算术移位5、逻辑运算功能的原理与设计2)与、或、异或、或非逻辑6、大于、等于、小于功能设计大于、等于、小于功能设计7、AluOP的控制原理与设计1)原理:AluOP的控制原理与设计8、总电路设计图算术逻辑运算单元ALU三、实验结论及分析(实验完成功能情况、存在问题分析或改进思路、自己的心得体会等。

组成原理-超前进位加法器设计

《计算机组成原理》实验报告专业:学号:学生姓名:实验日期:实验二一、实验名称:超前进位加法器设计二、实验目的:1 掌握超前进位加法器的原理及其设计方法。

2 熟悉CPLD 应用设计及EDA 软件的使用。

三、实验设备:PC 机一台,TD-CMA 实验系统一套,排线若干。

四、实验内容:1.了解加法器的工作原理,掌握超前进位产生电路的设计方法.2.正确将电路原理图下载到试验箱中.3.正确通过实验箱连线实现4位二进制数的相加并得到正确结果五、实验原理:加法器是执行二进制加法运算的逻辑部件,也是CPU 运算器的基本逻辑部件(减法可以通过补码相加来实现)。

加法器又分为半加器和全加器(FA),不考虑低位的进位,只考虑两个二进制数相加,得到和以及向高位进位的加法器为半加器,而全加器是在半加器的基础上又考虑了低位过来的进位信号。

表1-2-1 1 位全加器真值表A、B 为2 个1 位的加数,Ci 为来自低位的进位,S 为和,Co 为向高位的进位,根据表1-2-1所示的真值表,可得到全加器的逻辑表达式为:S = ABCi + ABCi + ABCi + ABCiCo = AB+ ACi + BCi根据逻辑表达式,可得到如图1-2-1 所示的逻辑电路图。

有了 1 位全加器,就可以用它来构造多位加法器,加法器根据电路结构的不同,可以分为串行加法器和并行加法器两种。

串行加法器低位全加器产生的进位要依次串行地向高位进位,其电路简单,占用资源较少,但是串行加法器每位和以及向高位的进位的产生都依赖于低位的进位,导致完成加法运算的延迟时间较长,效率并不高。

C0 = 0Ci+1 = AiBi + AiCi + BiCi = AiBi + (Ai + Bi)Ci设gi = AiBipi = Ai + Bi则有:Ci+1 = gi + piCi= gi + pi(gi-1 + pi-1Ci-1)= gi + pi(gi-1 + pi-1(gi-2 + pi-2Ci-2))…= gi + pi (gi-1 + pi-1(gi-2 + pi-2(…(g0 + p0C0)…)))= gi + pigi-1 + pipi-1gi-2 + … + pipi-1…p1g0 + pipi-1…p1p0C0由于gi、pi 只和Ai、Bi 有关,这样Ci+1 就只和Ai、Ai-1、…、A0,Bi、Bi-1、…、B0 及C0有关。

一种基于FPGA的32位快速加法器设计_岳伟甲

c24·( c16·c8·c0·∏ s i + c16· c8·∏ s i + c16) ∏ s i + c24 =

i =8 32 i = 16 32 i = 24 32

本文 FPGA 验证的软件环境是 Altera 公司 Quartus8. 0 开 [6 ] 发环境和 Modelsim6. 1g 。 硬件采用的是 选 择 的 是 Altera 公司的 EP1K100QI208 - 2 芯片。 验证 FPGA 中设计采用的 [7 ] 方法是编写 testbench 例化待测试设计、 输入激励向量进行

此时如果 x = 1 则会产生一个进位 c' = 1 , 其余的情况都 c = 0 ( 17 ) 综合上面两者得到 c' = x·d0 ·d1 ·d2 ·d3 ·d4 ·d5 ·d6 ·d7 + c ( 18 ) 由此得到级间进位的表达式

15

c' 16 = c8 ·c0 ∏ s i + c8

i =8 23

图4

改进前后延迟仿真结果

81 岳伟甲, 等: 一种基于 FPGA 的 32 位快速加法器设计

2003 ( 4 ) : 65 - 68. 晋中师范高等专科学校学报 ,

4

结束语

本文先采用 4 级流水线结构和 8 位先行进位加法器组

( 9 ) 带入式( 7 ) 得到 把式( 8 ) 、

i -1

ci =

∑y' ·c

j j =0

0

i = 1, 2, …, 8

( 12 ) ( 13 )

下面再分析级间进位的影响 。对于第一级来说 c' 8 = c8

后面 3 级的进位情况比较复杂 , 下面先分析 2 个 8 位 2 进制数相加的情况。这里假设 2 个 8 位 2 进制数 a 和 b, 两 者相加产生一个 8 位数 d, 不考虑低位进位时进位为 c, 考虑 低位进位时进位为 c' 。 先不考虑低位向高位的进位为 x。 假设此时 c = 1 , 即在 产生了进位的前提下, 只有当 a 和 b 都取到最大值时 d 取到 最大值

位可控加减法器设计32位算术逻辑运算单元

位可控加减法器设计32位算术逻辑运算单元标题:深入探讨位可控加减法器设计中的32位算术逻辑运算单元一、引言在计算机系统中,算术逻辑运算单元(ALU)是至关重要的部件,用于执行数字运算和逻辑运算。

而在ALU中,位可控加减法器设计是其中的重要部分,尤其在32位算术逻辑运算单元中更是不可或缺。

本文将深入探讨位可控加减法器设计在32位算术逻辑运算单元中的重要性,结构特点以及个人观点和理解。

二、位可控加减法器设计的重要性位可控加减法器是ALU中的重要组成部分,它具有对加法和减法操作进行控制的能力,可以根据输入信号来实现不同的运算操作。

在32位算术逻辑运算单元中,位可控加减法器的设计要考虑到对每一位进行并行操作,并且要保证高速、低功耗和稳定性。

位可控加减法器设计在32位算术逻辑运算单元中具有非常重要的意义。

三、位可控加减法器设计的结构特点在32位算术逻辑运算单元中,位可控加减法器的设计需要考虑到以下几个结构特点:1. 并行运算:位可控加减法器需要能够实现对32位数据的并行运算,以提高运算速度。

2. 控制信号:设计需要合理的控制信号输入,来实现不同的运算模式和操作类型。

3. 进位传递:保证进位信号能够正确传递和计算,以确保运算的准确性。

4. 低功耗:设计需要考虑到低功耗的特点,以满足现代计算机系统对能源的需求。

四、个人观点和理解在我看来,位可控加减法器设计在32位算术逻辑运算单元中扮演着十分重要的角色。

它不仅需要具备高速、稳定和精确的运算能力,还需要考虑到功耗和控制信号的合理设计。

只有兼具这些特点,才能更好地满足现代计算机系统对于高效、可靠和低功耗的需求。

五、总结和回顾通过本文对位可控加减法器设计在32位算术逻辑运算单元中的深入探讨,我们可以看到它在计算机系统中的重要性和结构特点。

而个人观点也表明了它需要具备高速、低功耗和稳定性等特点,才能更好地满足现代计算机系统的需求。

在写作过程中,我对位可控加减法器设计在32位算术逻辑运算单元中的重要性和结构特点进行了深入探讨,并分享了个人观点和理解。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

采用kogge-stone tree 实现的32位超前进位加法器。

经过modelsim验证正确可用,在DC下综合成功

优点:速度快

缺点:运用了过多的寄存器,造成加法器面积较大

//文件名:add_4.v

//模块名:add_4

//

module add_32 (a,b,cin,s,co);

input [31:0] a,b;

input cin;

output [31:0] s;

output co;

reg [31:0] G1,P1,G2,P2,G3,P3,G4,P4,G5,P5;

reg [31:0] cout;

wire[31:0] s,G0,P0;

assign P0=a^b;

assign G0=a&b;

assign s=P0^{cout[31:0],cin};

assign co=cout[31];

always @(P0 or G0 or P1 or G1 or P2 or G2 or P3 or G3 or P4 or G4 or P5 or G5 )

begin

P1[31:1]=P0[31:1]&P0[30:0];

G1[31:1]=G0[31:1]|P0[31:1]&G0[30:0];

G1[0]=G0[0];

P1[0]=P0[0];

P2[31:2]=P1[31:2]&P1[29:0];

G2[31:2]=G1[31:2]|P1[31:2]&G1[29:0];

G2[1:0]=G1[1:0];

P2[1:0]=P1[1:0];

P3[31:4]=P2[31:4]&P2[27:0];

G3[31:4]=G2[31:4]|P2[31:4]&G2[27:0];

G3[3:0]=G2[3:0];

P3[3:0]=P2[3:0];

P4[31:8]=P3[31:8]&P3[23:0];

G4[31:8]=G3[31:8]|P3[31:8]&G3[23:0];

G4[7:0]=G3[7:0];

P4[7:0]=P3[7:0];

P5[31:16]=P4[31:16]&P4[15:0];

G5[31:16]=G4[31:16]|P4[31:16]&G4[15:0];

G5[15:0]=G4[15:0];

P5[15:0]=P4[15:0];

cout=G5|P5&cin;

end

endmodule