超前进位加法器

超前进位加法器设计(参考资料)

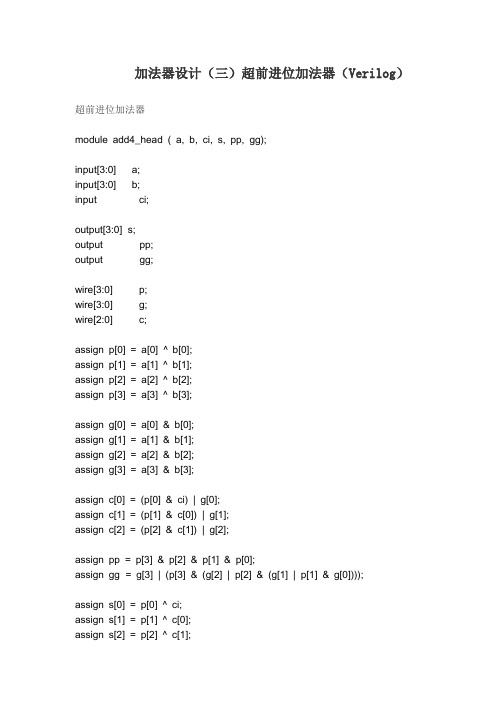

加法器设计(三)超前进位加法器(Verilog)超前进位加法器module add4_head ( a, b, ci, s, pp, gg);input[3:0] a;input[3:0] b;input ci;output[3:0] s;output pp;output gg;wire[3:0] p;wire[3:0] g;wire[2:0] c;assign p[0] = a[0] ^ b[0];assign p[1] = a[1] ^ b[1];assign p[2] = a[2] ^ b[2];assign p[3] = a[3] ^ b[3];assign g[0] = a[0] & b[0];assign g[1] = a[1] & b[1];assign g[2] = a[2] & b[2];assign g[3] = a[3] & b[3];assign c[0] = (p[0] & ci) | g[0];assign c[1] = (p[1] & c[0]) | g[1];assign c[2] = (p[2] & c[1]) | g[2];assign pp = p[3] & p[2] & p[1] & p[0];assign gg = g[3] | (p[3] & (g[2] | p[2] & (g[1] | p[1] & g[0])));assign s[0] = p[0] ^ ci;assign s[1] = p[1] ^ c[0];assign s[2] = p[2] ^ c[1];assign s[3] = p[3] ^ c[2];endmodule首先要明确几个概念:p表示进位否决信号(pass),如果p为0就否决调前一级的进位输入。

否决的意思就是即使前一级有进位,本级也不会向后一级产生进位输出。

32超前进位加法器

文档编号:GX_HW_0001文档分类:硬件技术文档访问权限:公开32位超前进位加法器总体设计方案Version 1.1版本信息版本日期描述作者V1.1 2011-10-07 采用超前进位链实现郭新32位超前进位加法器目录目录 (3)1.概述 (4)2.总体描述 (4)2.1.功能描述 (4)2.2.顶层框图 (4)2.3.引脚描述 (4)3.模块划分 (5)3.1 概述(叙述一下划分的几个大的模块) (5)3.2模块A (6)3.2.1功能定义 (6)3.2.2信号描述 (6)3.2.3 详细设计 (6)3.3模块B (7)3.3.1功能定义 (7)3.3.2信号描述 (7)3.3.3 详细设计 (7)3.4模块C (8)3.4.1功能定义 (8)3.4.2信号描述 (8)3.4.3 详细设计 (8)3.5模块D (9)3.5.1功能定义 (9)3.5.2信号描述 (9)3.5.3 详细设计 (9)4.验证方案 (10)5.设计开发环境 (10)6.源代码 (10)6.1顶层模块 (10)6.2模块A (12)6.3模块B (12)6.4模块C (13)6.5模块D (14)6.6测试模块 (15)6.7测试波形 (16)1.概述利用各位数据和最低位进位同时输入,各位之间的进位信号与和就能同时产生,实现超前进位加法器,这种加法器运算速度显著提高,但电路复杂程度也急剧增加。

2.总体描述2.1.功能描述超前进位逻辑从输入中读入进位、传播值和生成值等信息,计算每一位的进位值。

该逻辑产生进位值和加值,加值只是输入的异或。

进位值用4位超前进位块的三级树来计算。

2.2.顶层框图32bit_claa(31:0)b(31:0)cins(31:0)cout图2.1加法器顶层框图2.3.引脚描述表2.1 顶层接口信号描述名称输入/输出功能描述a 输入32位输入b 输入32位输入cin 输入低级进位输入s 输入32位输出cout 输入进位输出3.模块划分(各个模块中不涉及时序,时序分析略去。

超前进位加法器

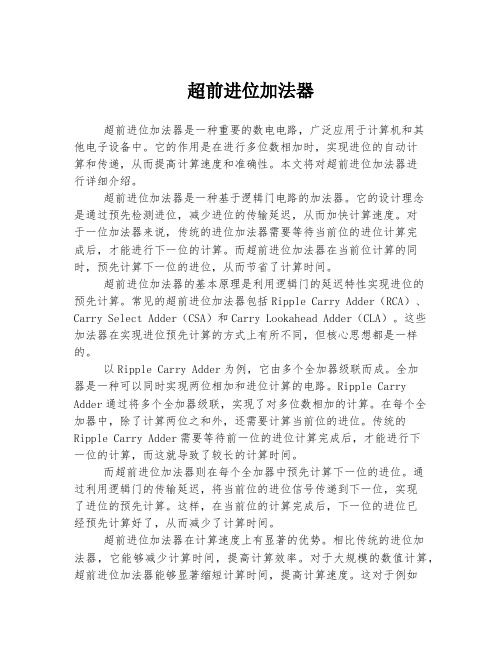

超前进位加法器超前进位加法器是一种重要的数电电路,广泛应用于计算机和其他电子设备中。

它的作用是在进行多位数相加时,实现进位的自动计算和传递,从而提高计算速度和准确性。

本文将对超前进位加法器进行详细介绍。

超前进位加法器是一种基于逻辑门电路的加法器。

它的设计理念是通过预先检测进位,减少进位的传输延迟,从而加快计算速度。

对于一位加法器来说,传统的进位加法器需要等待当前位的进位计算完成后,才能进行下一位的计算。

而超前进位加法器在当前位计算的同时,预先计算下一位的进位,从而节省了计算时间。

超前进位加法器的基本原理是利用逻辑门的延迟特性实现进位的预先计算。

常见的超前进位加法器包括Ripple Carry Adder(RCA)、Carry Select Adder(CSA)和Carry Lookahead Adder(CLA)。

这些加法器在实现进位预先计算的方式上有所不同,但核心思想都是一样的。

以Ripple Carry Adder为例,它由多个全加器级联而成。

全加器是一种可以同时实现两位相加和进位计算的电路。

Ripple Carry Adder通过将多个全加器级联,实现了对多位数相加的计算。

在每个全加器中,除了计算两位之和外,还需要计算当前位的进位。

传统的Ripple Carry Adder需要等待前一位的进位计算完成后,才能进行下一位的计算,而这就导致了较长的计算时间。

而超前进位加法器则在每个全加器中预先计算下一位的进位。

通过利用逻辑门的传输延迟,将当前位的进位信号传递到下一位,实现了进位的预先计算。

这样,在当前位的计算完成后,下一位的进位已经预先计算好了,从而减少了计算时间。

超前进位加法器在计算速度上有显著的优势。

相比传统的进位加法器,它能够减少计算时间,提高计算效率。

对于大规模的数值计算,超前进位加法器能够显著缩短计算时间,提高计算速度。

这对于例如计算机科学、数据处理和通信等领域的应用非常重要。

除了计算速度的优势,超前进位加法器在准确性上也有一定的优势。

试验二 超前进位加法器 设计

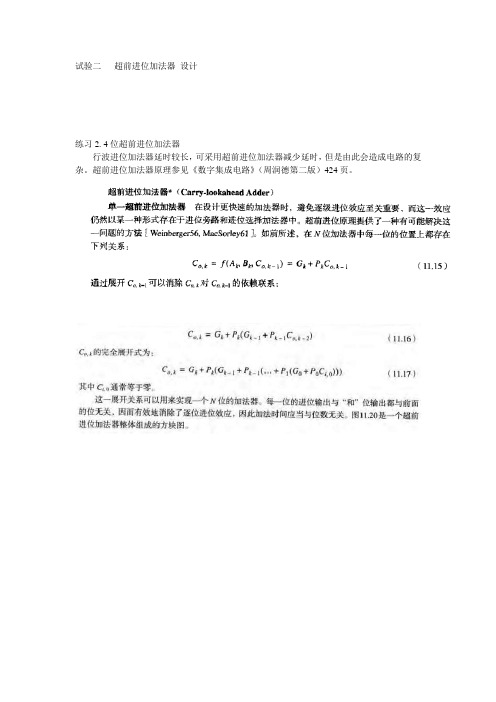

试验二超前进位加法器设计练习2. 4位超前进位加法器行波进位加法器延时较长,可采用超前进位加法器减少延时,但是由此会造成电路的复杂。

超前进位加法器原理参见《数字集成电路》(周润德第二版)424页。

对以上公式的注解:公式中的C O,K 表示第K 为的进位输出,G K 为第K 位的进位产生,P K 为第K 为的进位传播。

且:K K KK K KG A B P A B ==⊕ A K ,B K 为输入加数的第K 位。

将Co 和S 用G,P 重写为: O ii C G PC S P C =+=⊕由于低位的输出进位是高位的输入进位,所以有上面的(11.15)式源程序://this is a carry lookahead of 4bitmodule clad(ina,inb,ci,co,sum);input[3:0] ina,inb;input ci;output co;output[3:0]sum;wire co0,co1,co2,G0,G1,G2,G3,P0,P1,P2,P3;assignG0=ina[0]&inb[0],P0=ina[0]^inb[0],G1=ina[1]&inb[1],P1=ina[1]^inb[1],G2=ina[2]&inb[2],P2=ina[2]^inb[2],G3=ina[3]&inb[3],P3=ina[3]^inb[3],co0=G0|(P0&ci),co1=G1|(P1&co0),co2=G2|(P2&co1),co=G3|(P3&co2),sum[0]=P0^ci,sum[1]=P1^co0,sum[2]=P2^co1,sum[3]=P3^co2;endmodule测试程序:module clad_test;reg[3:0] ina,inb;reg ci;wire co;wire[3:0]sum;clad CI(.ina(ina),.inb(inb),.ci(ci),.co(co),.sum(sum)); initialbeginina=0;inb=0;ci=0;endalways #5 ina=ina+1'b1;always #80 inb=inb+1'b1;always #1280 ci=~ci;endmodule仿真结果:注:该结果为10进制显示练练手:参考《数字集成电路》(周润德第二版)420-421,设计一个16位的超前进位加法器,基本单元使用4位的加法器,结构自选。

数字电路课程设计之超前进位加法器

reg

Cin;

wire[3:0] S;

wire

Cout;

carry_look_add CAL (.A(A),.B(B),.Cin(Cin),.Cout(Cout),.S(S)); initial begin

#10 A=4'd0;B=4'd0;Cin=0; #10 A=4'd11;B=4'd1;Cin=0; #10 A=4'd10;B=4'd12;Cin=0; #10 A=4'd11;B=4'd4;Cin=0; #100 $stop; end endmodule

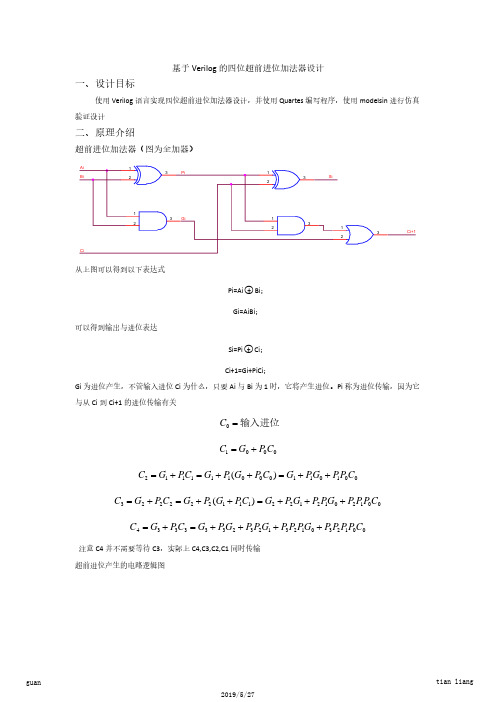

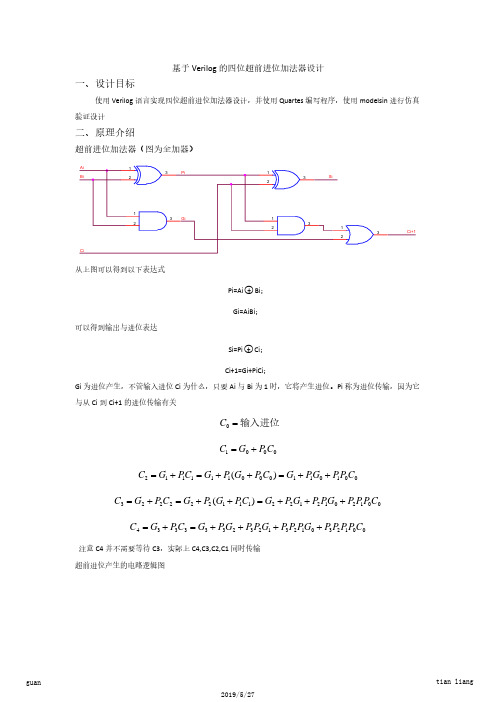

Pi=Ai○+ Bi;

可以得到输出与进位表达

Gi=AiBi;

Si=Pi○+ Ci;

Ci+1=Gi+PiCi; Gi 为进位产生,不管输入进位 Ci 为什么,只要 Ai 与 Bi 为 1 时,它将产生进位。Pi 称为进位传输,因为它 与从 Ci 到 Ci+1 的进位传输有关

C0 = 输入进位

C1 = G0 + P0C0

Half_Add H3(.a(A[2]),.b(B[2]),.s(v6),.c(v5));

Half_Add H4(.a(A[3]),.b(B[3]),.s(v8),.c(v7));

carry_look

CL1(.C0(Cin),.P0(v2),.G0(v1),.P1(v4),.G1(v3),.P2(v6),.G2(v5),.P3(v8),.G3(v7),.C1(o1),.C2(o2),.C3(o3),.C4(Cout));

注意 C4 并不需要等待 C3,实际上 C4,C3,C2,C1 同时传输 超前进位产生的电路逻辑图

超前进位加法器

8位超前进位加法器设计说明书超前进位加法器就是使各位的进位直接由加数和被加数来决定,而不需要依赖低位进位。

即有如下逻辑表达式:1)(-++=i i i i i i C B A B A C当第i 位被加数A i 和加数B i 均为1时,有1=i i B A ,不论低位运算结果如何本位必然有进位输出(1=i C ),所以定义i i i B A G =为进位产生函数。

当A i 和B i 中只有一个为1时,有0=i i B A ,1=+i i B A ,使得1-=i i C C ,所以定义i i i B A P +=为进位传递函数。

将P i 和G i 代入全加器的“和”及“进位”表达式有:1-⊕⊕=i i i i C B A Y从而构成超前进位加法器。

VHDL 示例程序如下:(本程序在MAXPLUSII V9.6上编译通过)--*****8位超前进位加法器*****LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE. STD_LOGIC _ARITH.ALL;USE IEEE. STD_LOGIC _UNSIGNED.ALL;ENTITY ADDER8BIT ISPORT(A, B: IN UNSIGNED(7 downto 0);CI,clk: IN STD_LOGIC;Y_OUT: OUT STD_LOGIC_VECTOR(7 downto 0);CO_OUT: OUT STD_LOGIC);END ADDER8BIT;ARCHITECTURE doing OF ADDER8BIT ISSIGNAL CO,Y: STD_LOGIC_VECTOR(7 downto 0);BEGINY(0)<=A(0) xor B(0) xor CI;CO(0)<=(A(0) and B(0)) or (B(0) and CI) or (A(0) and CI);GEN:for i in 1 to 7 GENERATEY(i)<=A(i) xor B(i) xor CO(i-1); --1-⊕⊕=i i i i C B A YCO(i)<=(CO(i-1) and A(i)) or (CO(i-1) and B(i)) or (A(i) and B(i)); -- 1)(-++=i i i i i i C B A B A Cend GENERATE;process(clk)beginif clk'event and clk='1' thenY_OUT<=Y(7) & Y(6) & Y(5) & Y(4) & Y(3) & Y(2) & Y(1) & Y(0);CO_OUT<=CO(7);end if;end process;END doing;附:仿真时序波形。

数字电路课程设计之超前进位加法器

# MACRO ./mul_run_msim_rtl_verilog.do PAUSED at line 14

通过查阅资料将 Verilog 测试文件

Timsbench 文件没有实例化,修改为

修改后仿真 OK 参考文献: 1.数字设计与 Verilog 实现 M.Morris Mano 著 第五版

Pi=Ai○+ Bi;

可以得到输出与进位表达

Gi=AiBi;

Si=Pi○+ Ci;

Ci+1=Gi+PiCi; Gi 为进位产生,不管输入进位 Ci 为什么,只要 Ai 与 Bi 为 1 时,它将产生进位。Pi 称为进位传输,因为它 与从 Ci 到 Ci+1 的进位传输有关

C0 = 输入进位

C1 = G0 + P0C0

instance name in instantiation of 'carry_look_add'.

#

#

Region: /carry_look_add_tb

# Error loading design

# Error: Error loading design

#

Pausing macro execution

基于 Verilog 的四位超前进位加法器设计

使用 Verilog 语言实现四位超前进位加法器设计,并使用 Quartes 编写程序,使用 modelsin 进行仿真

验证设计

二、原理介绍

超前进位加法器(图为全加器)

Ai

1

3

Pi

Bi

2

1

3

Si

2

1 3 Gi

2

Ci

1

3

计算机组成原理课程设计—超前进位加法器的设计资料

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:超前进位加法器的设计院(系):计算机学院专业:班级:学号:姓名:指导教师:完成日期:沈阳航空航天大学课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (2)1.3设计环境 (3)第2章详细设计方案 (4)2.1顶层方案图的设计与实现 (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 (5)2.1.3编译、综合、适配 (7)2.2功能模块的设计与实现 (7)2.2四位超前进位加法器模块的设计与实现 (7)2.3仿真调试 (9)第3章编程下载与硬件测试 (11)3.1编程下载 (11)3.2硬件测试及结果分析 (11)参考文献 (13)附录(程序清单或电路原理图) (14)第1章总体设计方案1.1设计原理八位超前进位加法器,可以由2个四位超前进位加法器构成。

由第一个四位超前进位加法器的进位输出作为第二个超前进位加法器的进位输入即可实现八位超前进位加法器的设计。

超前进位产生电路是根据各位进位的形成条件来实现的。

只要满足下述条件,就可形成进位C1、C2、C3、C4。

所以:第一位的进位C1=X1*Y1+(X1+Y1)*C0第二位的进位C2=X2*Y2+(X2+Y2)*X1*Y1+(X2+Y2)(X1+Y1)C0第三位的进位C3=X3*Y3+(X3+Y3)X2*Y2+(X3+Y3)*(X2+Y2)*X1*Y1+(X3+Y3)(X2+Y2)(X1+Y1)*C0第四位的进位C4=X4*Y4+(X4+Y4)*X3*Y3+(X4+Y4)*(X3+Y3) * X2*Y2+(X4+Y4)(X3+Y3)(X2+Y2)*X1*Y1+(X4+Y4)(X3+Y3)(X2+Y2)(X1+Y1)*C0 下面引入进位传递函数Pi和进位产生函数Gi的概念。

它们定义为:Pi=Xi+YiGi=Xi*YiP1的意义是:当X1和Y1中有一个为1时,若有进位输入,则本位向高位传递此进位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

超前进位加法器

超前进位加法器是一种数字电路设备,用于进行二进制

数的加法运算。

它通过将多个加法器级联,实现对多位二进制数的加法计算,并且能够在加法过程中实现超前进位,提高计算速度。

超前进位加法器的原理是基于二进制加法的原理。

在二

进制加法中,每一位的运算结果可以表示为:两个位的和与进位。

其中,和即为输入位的异或运算结果,进位则是输入位的与运算结果再经过左移一位。

超前进位加法器利用这一原理,通过预测进位产生的结果,以提前得到进位并作用于下一级的运算。

超前进位加法器可以分为两个部分:生成进位部分和传

递进位部分。

生成进位部分用于预测进位的产生情况,传递进位部分则是将进位传递给下一级的加法器。

生成进位部分的输入为两个相邻位的和,输出为进位。

传递进位部分的输入为前一级的进位以及生成进位部分的进位,输出为当前位的进位。

为了方便理解,以下以一个四位超前进位加法器为例进

行介绍。

这个四位加法器由四个单独的全加器组成,每个全加器负责一个位的运算。

生成进位部分和传递进位部分在全加器中都有相应的电路实现。

首先,生成进位部分。

对于第一位的全加器来说,由于

没有前一位的进位,因此直接将两个输入位的和作为输出位的进位。

对于其他位的全加器,需要预测进位的产生。

这个预测的规则是,如果前一位的和为1,则有可能会产生进位。

因此,

预测进位部分将前一位输入位的和与该位输入位的和进行与运算,得到预测的进位结果。

接下来,传递进位部分。

对于第一个全加器来说,由于没有前一位的进位,因此直接将生成进位部分的进位作为输出位的进位。

对于其他位的全加器,传递进位部分将前一位的进位与生成进位部分的进位进行或运算,得到当前位的进位。

将多个全加器级联后,就构成了一个超前进位加法器。

通过这种方式,每一位的运算可以并行进行,从而提高了计算速度。

同时,由于提前预测了进位的结果,可以减少了进位的传播延迟,进一步提高了计算效率。

超前进位加法器在数字电路的设计中具有重要的应用价值。

它可以广泛应用于计算机、通信等领域,用于处理大规模的二进制数的加法运算。

通过合理的设计和优化,可以进一步提高计算速度和性能。