基于FPGA的微处理器设计

FPGA_ASIC-基于同步原则的FPGA-CPU设计

基于同步原则的FPGA-CPU设计苏晓东,杨英华(东北大学信息科学与工程学院,辽宁沈阳110004)摘要:FPGA是一种可完成复杂逻辑功能的通用可编程器件,因其丰富的触发器资源、可重配置能力及低开发风险而广受欢迎。

该文以Altera 公司的Cyclone FPGA为目标器件,通过对原有CPU模型进行改进,讨论数字系统设计中的常见问题与满足同步原则的解决方案。

关键词:CPU;FPGA;数字系统;同步原则中图分类号:TN402 文献标识码:AAn FPGA-CPU Design Based o n Synchronous PrincipleSu Xiaodong, Yang Yinghua(College of Information Science and Engineering, Northeastern University, Shenyang 110004) Abstract: FPGAs are generic, programmable digital devices that can perform complex logical operations. FPGAs are widely used because of their rich trigger resources, configurable abilities and low development risk, making them increasingly popular. This paper presents some frequently confronted problems and the essentiality of synchronous design in digital systems based on an existed FPGA-CPU design.Keywords: CPU; FPGA; Digital Systems; Synchronous Principle0 引言随着电子工业和超大规模集成电路(VLSI)技术的高速发展, 要求专用集成电路(ASIC) 的功能越来越强, 功耗越来越低, 生产周期越来越短, 这些都对芯片设计提出了巨大的挑战, 传统的芯片设计方法已经不能适应复杂的应用需求了[1]。

基于FPGA的Verilog语言描述的SDRAM接口电路设计

基于FPGA的SDRAM存储器接口实现摘要随着信息科学的飞速发展,人们面临的信号处理任务越来越繁重,对数据采集处理系统的要求也越来越高。

单片机、DSP等微处理器内部RAM 有限,这就需要在微处理器的外部扩展存储器。

同步动态随机访问存储器具有价格低廉、密度高、数据读写速度快的优点,从而成为数据缓存的首选存储介质,在数据采集系统和图像处理系统等方面中有着重要和广泛的应用。

SDRAM 的读写逻辑复杂,最高时钟频率达100MHz 以上,普通单片机无法实现复杂的SDRAM 控制操作。

复杂可编程逻辑器件CPLD具有编程方便,集成度高,速度快,价格低等优点。

因此选用CPLD 设计SDRAM 接口控制模块, 简化主机对SDRAM 的读写控制。

通过设计基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

论文开始介绍了SDRAM接口设计研究的背景和研究的目的及意义,引出对SDRAM的研究,详细介绍了SDRAM的基本原理、内部结构、基本操作和工作时序,以及设计的重点及难点。

在这些理论基础上对SDRAM 接口进行模块化设计,了解设计中所使用的硬件和软件。

最后用Verilog语言在软件QuartusⅡ设计CPLD芯片,通过在硬件和软件上的调试基本实现了SDRAM接口的设计。

关键词SDRAM;接口;Verilog;CPLDThe Implementation of SDRAM MemoryInterface Based on the EPM570AbstractWith the rapid development of information science, people face more and more onerous task of signal processing, the requirements of data acquisition and processing system are getting higher and higher. Microprocessor such as single-chip microprocessor, DSP etc, their RAM is limited, which requires external expansion in the microprocessor memory. Synchronous Dynamic Random Access Memory has a low cost, high density, fast read and write data on the merits, thereby becoming the first choice for data cache storage medium, which paly an important role and widely used in the data acquisition system and image processing systems.SDRAM read and write logic is complex, the maximum clock frequency reaches above 100MHz, the ordinary microcontroller can not achieve complex SDRAM control operation. Complex programmable logic device has advantages such as programming convenience, high integrity, high speed and low cost etc. Therefore select CPLD to design control module of SDRAM interface , to simplify the host to read and write control of the SDRAM. Through the design of SDRAM controller interface based on CPLD, you can connect SDRAM in the external of STM series, ARM series, STC series single chip microprocessor and the DSP, increase system storage space.At the beginning of paper introduces the research background, research purpose and significance of the study of SDRAM interface design, leads to the study of SDRAM, detailed introduces information of SDRAM about the basic principles, the internal structure, the basic operation and timing of work, and the design emphasis and difficulty. Based on these theories, modularing the designof SDRAM interface, understanding hardware and software used in the design. Finally, it uses Verilog language in Quartus Ⅱsoftware to design CPLD chip, Through the hardware and the software realization SDRAM the commissioning of the basic design of the interface.Keywords SDRAM; Interface; Verilog; CPLD目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景 (1)1.2 课题研究的目的及意义 (1)1.3 同步动态随机存储器简介 (2)1.4 论文的结构和框架 (3)第2章SDRAM的工作原理 (4)2.1 存储器的概述 (4)2.1.1 存储器的分类 (4)2.1.2 存储器的技术指标 (5)2.1.3 存储器的比较 (5)2.2 SDRAM的工作原理 (6)2.2.1 SDRAM存储的基本原理 (6)2.2.2 SDRAM的内部结构 (7)2.3 本章小结 (8)第3章SDRAM的基本操作 (9)3.1 SDRAM的基本操作 (9)3.1.1 芯片初始化 (9)3.1.2 行有效 (9)3.1.3 列读写 (10)3.1.4 读操作 (11)3.1.5 写操作 (12)3.2 SDRAM的工作特性 (13)3.2.1 模式寄存器的设置 (13)3.2.2 预充电 (14)3.2.3 刷新 (15)3.3 SDRAM接口设计的要求 (16)3.3.1 存储器接口解决数据存取的难点 (17)3.3.2 存储器接口在工作方式上的初步优化 (17)3.4 本章小结 (18)第4章系统结构及硬件设计 (19)4.1 SDRAM接口设计的整体结构 (19)4.1.1 控制接口模块 (19)4.1.2 CAS延迟模块 (20)4.1.3 突发长度模块 (22)4.1.4 地址转换模块 (22)4.2 EPM570芯片简介 (23)4.2.1 MAXⅡ系列芯片功能简介 (24)4.2.2 逻辑阵列 (25)4.2.3 全局时钟 (25)4.2.4 I/O端口结构 (26)4.3 MT48LC系列芯片简介 (26)4.4 本章小结 (28)第5章软件设计与实现 (30)5.1 利用QuartusⅡ进行设计的流程 (30)5.2 软件的设计 (31)5.2.1 Verilog语言的特点 (31)5.2.2 采用Verilog设计综合的过程 (32)5.2.3 SDRAM接口设计的仿真 (34)5.3 本章小结 (36)结论 (37)致谢 (38)参考文献 (39)附录A (41)附录B (46)附录C (51)第1章绪论1.1课题背景数据采集处理技术是现代信号处理的基础,广泛应用于雷达、声纳、软件无线电、瞬态信号测试等领域。

基于FPGA的数据采集与处理技术的研究

3、FPGA-based Data Acquisition and Processing System:该系统将数 据采集、处理和传输等功能集成到FPGA中,实现了数据的快速处理和传输。但 系统复杂度高,开发难度较大。

结论与展望

本次演示对基于FPGA的数据采集与处理技术的研究进行了详细探讨。目前,该 领域已取得了显著的成果,但仍存在一些不足和挑战。例如,如何优化算法以 降低硬件资源消耗、提高数据处理速度和精度等问题仍需进一步研究。

文献综述

目前,ARM和FPGA已经在数据采集领域得到了广泛的应用。ARM是一种32位的 微处理器,具有高速的计算能力和丰富的外设接口,可以方便地应用于数据采 集系统中。而FPGA则是一种可编程逻辑器件,具有高度的灵活性和并行计算能 力,可以大大提高数据采集的速度。

然而,现有的ARM与FPGA相结合的数据采集技术还存在一些不足之处。首先, 由于ARM和FPGA的时钟频率不同,容易导致数据传输的同步问题。其次,现有 的技术往往没有充分挖掘ARM和FPGA的潜力,导致数据采集速度和精度还有待 提高。

系统设计

基于FPGA的数据采集与处理系统设计需要结合数据采集和处理的过程,将两者 有机地结合起来。具体步骤如下:

1、确定系统需求:明确系统需要实现的功能和性能指标,如采样频率、分辨 率、数据处理速度等。

2、选择合适的硬件:根据需求,选择合适的FPGA芯片、ADC、传感器等硬件 组件。

3、设计数据采集电路:根据传感器类型和性能指标,设计数据采集电路,包 括信号的放大、滤波、A/D转换等。

研究现状

自20世纪80年代FPGA问世以来,数据采集与处理技术取得了长足的进步。目 前,基于FPGA的数据采集与处理技术主要分为两大类:直接数据采集和间接数 据采集。直接数据采集通过FPGA内部的逻辑资源实现数据采集和处理的同步进 行,具有实时性强的优点,但逻辑资源消耗较大;间接数据采集先将数据传输 到FPGA外部的存储器,再通过软件对数据进行处理,具有数据处理能力强的优 点,但实时性较差。

基于FPGA实现四选一选择器的设计

基于FPGA实现四选一选择器的设计摘要本文是基于FPGA的四选一选择器的设计:基于FPGA在数据选择方面的优势,把FPGA作为选择器的控制核心;主要研究如下:软件部分——四选一选择器程序。

针对数据选择器的设计,对FPGA进行了型号选择,使用VHDL语言在型号FLEX10K/20RC208-4上编写了四选一选择器的程序,通过使能端的控制,从而达到四选一的功能。

硬件部分——使用protel画出原理图并作出PCB板。

本设计采用了单八路模拟开关CD4051,通过输入端的控制,选择一路信号,通过ADC0804模数转化,输出8路信号给FLEX10K/20RC208-4,经FLEX10K/20RC208-4处理后,接TCL7528后,将数字信号转换为模拟信号并输出。

本文通过软件和硬件的两个方面的设计,实现了四选一选择器的功能。

关键词:FPGA ;VHDL ;PROTEL ;选择器内蒙古科技大学毕业设计说明书(毕业论文)FPGA implementation based on four selected design of a selectorAbstrateThis article is based on a choice selection of four FPGA Design: FPGA-based data selection in the advantages of the FPGA as a selector control center; main research are as follows:Software parts - 4 election a choice program. Design for data selection, model selection on the FPGA, using the VHDL language in the model FLEX10K/20RC208-4 four selected to write a program selector, by enabling the client to control, so as to achieve a function of four elections.Hardware - protel schematic drawing and make a PCB board. This design uses a single eight-way analog switches CD4051, through the control input, select the way the signal, ADC0804 module through the transformation of the output signal 8 to FLEX10K/20RC208-4, by FLEX10K/20RC208-4 treatment, then TCL7528, will digital signal is converted to analog signals and output.In this paper, two aspects of hardware and software design, implementation, choose one of four selector functions.Keywords: FPGA ; VHDL ; ROTEL ; selectorI目录摘要 .............................................................................................................................................. Abstrate (I)第一章绪论 01.1 FPGA简介 01.1.1 FPGA发展现状 01.1.2 FPGA的发展趋势 (1)1.1.3 FPGA基本结构 (1)1.1.4 FPGA的特点 (3)1.1.5 FPGA选型 (4)1.1.6 FPGA设计原则 (5)1.2本论文研究的主要内容 (6)第二章FPGA芯片设计 (7)2.1 BTYG-EDA实验开发系统简介 (7)2.1.1 BTYG-EDA实验开发系统特点 (7)2.1.2 BTYG-EDA实验开发系统资源介绍 (7)2.1.3 主芯片引脚和外部硬件连接关系 (7)2.2 FLEX10K/20RC208-4 (11)2.3 本章小结 (13)第三章MAX+plus II软件和VHDL语言――软件部分 (14)3.1 MAX+plus II开发软件 (14)3.1.1 MAX+plus II功能特点 (14)3.1.2 MAX+plus II系统要求 (15)3.1.3 MAX+plus II设计流程 (15)3.2 VHDL语言简介 (18)3.2.1 VHDL基本介绍 (18)3.2.2 VHDL语言的特点 (19)3.2.3 VHDL系统优势 (20)II内蒙古科技大学毕业设计说明书(毕业论文)3.2.4 VHDL程序基本结构 (20)3.3 MAX十plus II中硬件描述语言输入的设计过程 (21)3.3.1 输入VHDL文件 (21)3.3.2 将文件指定为设计项目 (21)3.3.3 项目编译 (22)3.3.4 项目仿真 (22)3.4 程序仿真介绍及仿真图 (22)3.5本章小结 (24)第四章protel99——硬件部分 (25)4.1 protel简介 (25)4.1.1 Protel99SE的功能特点 (25)4.1.2 用Protel99SE进行电路设计的步骤 (26)4.2 四选一选择器的原理图及各元件介绍 (26)4.3 本章小结 (33)第五章总结与展望 (34)5.1 取得的成果 (34)5.2 工作展望 (34)参考文献 (35)附录A (36)附录B (37)致谢 (39)III第一章绪论1.1 FPGA简介1.1.1 FPGA发展现状当今社会是数字化的社会,是数字集成电路广泛应用的社会,数字集成电路本身在不断地进行更新换代。

基于FPGA的32位RISC微处理器设计

第2卷第3 6 期 2 1 年 5月 01

数

据

采

集

与

处

理

Vo . 6 No 3 1 2 .

Ma y 201 1

J u n lo t q iiin 8 r c sig o r a fDa aAc usto LP o esn

文 章 编 号 :0 49 3 ( 0 10 —3 70 1 0 — 0 7 2 1 ) 30 6 — 7

基 于 F GA 的 3 P 2位 RIC微 处 理 器 设 计 S

刘 览 郑 步 生 施 慧彬

(. 1 南京航 空航 天大学电子信息工程学院 , 南京 , 10 6 201;

2南 京 航 空 航 天 大学 计 算 机科 学 与 技 术 学 院 , 京 ,1 0 6 . 南 201)

的 C I 同 时 又 不 会使 流 水 线 出现 局 部 逻 辑 拥 堵 从 而 降 低 微 处 理 器 的主 频 。最后 给 出 了设 计 的 综 合 结 果 , 对该 P, 并 设 计进 行 了软 件 仿 真 和 硬 件 验 证 。在 F GA 芯 片 上 的 运 行 时 钟 频 率 可 达 1 6 6 8MHz P 4 . 2 。 关键 词 : 简指 令 集计 算 机 ; 处 理 器 ; 水 线 ; 支 预 测 精 微 流 分 中 图分 类 号 : P 0. T 322 文 献标 识 码 : A

基于FPGA的一种ALU设计与实现方法

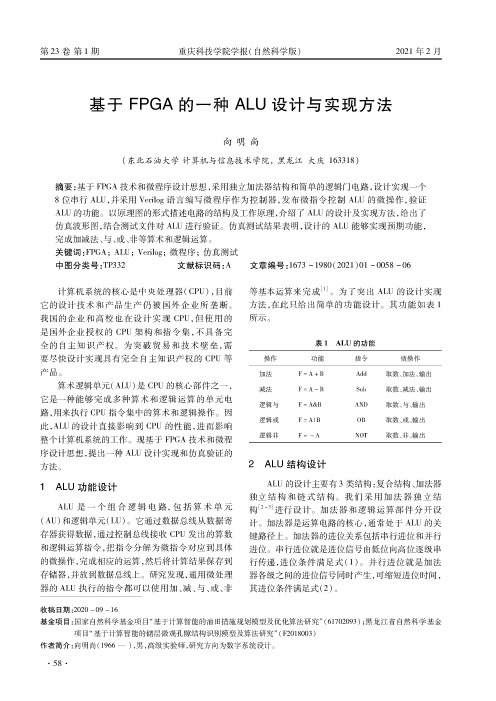

第23卷第1期重庆科技学院学报(自然科学版)2021年2月基于FPGA的一种ALU设计与实现方法向明尚(东北石油大学计算机与信息技术学院,黑龙江大庆163318)摘要:基于FPGA技术和微程序设计思想,采用独立加法器结构和简单的逻辑门电路,设计实现一个8位串行ALU,并采用Ver1mg语言编写微程序作为控制器,发布微指令控制ALU的微操作,验证ALU的功能。

以原理图的形式描述电路的结构及工作原理,介绍了ALU的设计及实现方法,给出了仿真波形图,结合测试文件对ALU进行验证。

仿真测试结果表明,设计的ALU能够实现预期功能,完成加减法、与、或、非等算术和逻辑运算。

关键词:FPGA;ALU;Veriloo;微程序;仿真测试中图分类号:TP332文献标识码:A文章编号:1673-1980(2021)01-0058-06计算机系统的核心是中央处理器!cpu),目前它的设计技术和产品生产仍被国外企业所垄断。

我国的企业和高校也在设计实现CPU,但使用的是国外企业授权的CPU架构和指令集,不具备完全的自主知识产权。

为突破贸易和技术壁垒,需要尽快设计实现具有完全自主知识产权的CPU等产品。

算术逻辑单元(ALU)是CPU的核心部件之一,它是一种能够完成多种算术和逻辑运算的单元电路,用来执行CPU指令集中的算术和逻辑操作。

因此,ALU的设计直接影响到CPU的性能,进而影响整个计算机系统的工作。

现基于FPGA技术和微程序设计思想,提出一种ALU设计实现和仿真验证的方法。

1ALU功能设计ALU是一个组合逻辑电路,包括算术单元(AU)和逻辑单元!LU)。

它通过数据总线从数据寄存器获得数据,通过控制总线接收CPU发出的算数和逻辑运算指令,把指令分解为微指令对应到具体的微操作,完成相应的运算,然后将计算结果保存到存储器,并放到数据总线上。

研究发现,通用微处理器的ALU执行的指令都可以使用加、减、与、或、非等基本运算来完成[1]o为了突出ALU的设计实现方法,在此只给出简单的功能设计。

基于FPGA的嵌入式系统的设计与实现

2、输入模块设计

输入模块主要包括乐曲信息的采集和传输。本系统中,乐曲信息采用MIDI格 式进行存储和传输。用户可以通过MIDI键盘或者其他MIDI设备将乐曲信息输入到 系统中。

3、处理模块设计

处理模块主要由FPGA完成,其主要任务是将输入的乐曲信息转换为硬件可以 识别的控制信号。

具体来说,FPGA首先需要将MIDI格式的乐曲信息解析为数字信号,然后通过 内部算法进行处理,生成控制音频硬件的信号。本系统中,FPGA主要通过VHDL编 程语言来实现上述功能。

基于FPGA的嵌入式系统的设计与实 现

目录

01 基于FPGA的嵌入式系 统设计与实现

02 参考内容

基于FPGA的嵌入式系统设计与 实现

随着科技的不断发展,嵌入式系统在各个领域的应用越来越广泛。FPGA(现 场可编程门阵列)作为一种灵活、高效的硬件设计技术,为嵌入式系统设计提供 了新的解决方案。本次演示将介绍基于FPGA的嵌入式系统的设计与实现。

经过以上步骤,我们可以得出基于FPGA的嵌入式系统的设计与实现具有以下 优点:首先,FPGA的可编程性使得硬件设计更加灵活,可以根据不同需求进行定 制和优化;其次,FPGA的高速并行处理能力可以提高整个嵌入式系统的运算效率 和性能;再次,使用FPGA可以降低系统功耗和成本,同时减小了系统的体积和重 量;最后,FPGA的可重构特性使得系统升级和维护更加简便。

1、硬件设计

系统的硬件部分主要包括DSP、FPGA、RAM、Flash等。其中,DSP用于实现 信号处理算法,接收GPS和惯性导航等传感器数据,计算出位置、速度等信息; FPGA用于实现硬件接口、数据传输和控制逻辑,连接各个硬件模块,保证系统的 正常运行;RAM用于存储运行时的数据和程序;Flash用于存储固件程序和常量数 据。

基于FPGA+MCU的大型LED显示屏系统设计

基于FPGA+MCU的大型LED显示屏系统设计传统的大型LED显示屏系统以单片机MCU、ARM 或PLD为核心控制芯片,以FPGA为核心的led显示屏控制系统设计实现起来比较复杂,并且需要以高性能的FPGA芯片作为基础,而以微处理器为核心的LED显示屏控制系统不够灵活,在改变LED屏幕显示尺寸时,需要大幅修改系统设计,PLD虽在处理速度上有较大提高且能很好地控制多模块显示,但其在时序电路描述方面明显不如FPGA。

提出了基于FPGA与单片机MCU的大型LED显示屏系统设计方案,该系统中FPGA为主控制单元,单片机为扫描控制单元,该方案简化电路,提高系统的灵活性和可靠性。

实践仿真结果表明:系统显示内容较多,能较好地支持彩色显示,降低了功耗,实现了现场实时控制显示。

随着平板显示技术的不断更新,大型LED显示系统利用发光二极管构成的点阵模块或像素单元组成大面积显示屏,主要显示字符、图像等信息,具有低功耗、低成本、高亮度、长寿命、宽视角等优点。

近年来广泛应用在证券交易所、车站机场、体育场馆、道路交通、广告媒体等场所。

通常用单一单片机作为主控器件控制和协调大屏幕显示。

由多片单片机构成的多处理器系统,其中一片作为主CPU,其他作为子CPU共同控制大屏幕的显示,该系统可以减轻主CPU 的负担,提高了LED点阵的刷新频率。

但单片机的驱动频率有限,无法驱动等分辨率LED屏幕,尤其是对于多灰度级彩色大屏幕,数据送到显示屏之前要进行灰度调制重现图像的色彩,对数据的处理速度要求更高,单片机控制在速度上无法满足上述要求。

因此该方案主要应用于实时性要求不高的场合,主要进行一些文字、图片等静态异步显示的控制。

视频图像信号频率高、数据量大,要求实时处理,采用FPGA/CPLD设计控制电路,其中的同步控制、主从控制、读写控制和灰度调制等大量电路进行了集成,简化系统结构,便于调试且系统结构紧凑,工作可靠。

与单片机控制电路相比,电路结构明显简洁,电路的面积减小,可靠性增强,调试也更为简单,由于FPGA/CPLD可以并行处理多个进程,比起单片机对任务的顺序处理效率更高,点阵的刷新频率也随之提高。

FPGA_ASIC-一种基于FPGA的通用微处理器设计

一种基于FPGA的通用微处理器设计作者:董明 王丰转贴自:微计算机信息摘要:本文详细介绍了一种借助VHDL硬件描述性语言实现基于FPGA硬件平台的通用微处理器设计的完整方案。

该型CPU具有实现简单快捷、成本低、通用性强、扩展容易的特性。

本文分两大部分阐述:第一部分给出了该型CPU详细的结构图、原理说明、与相应存贮器的连接、存贮器模型以及部分VHDL源代码及其分析说明;第二部分针对该型CPU较强的扩展性能,从位扩展、功能扩展、存贮器容量扩展与段式模型以及与外围电路的连接角度进行研究,充分发挥该型CPU的潜能,并给出了一个CPU协同外围电路实现全自动洗衣机定时控制的例子。

关键词:VHDL;可编程逻辑;微处理器;FPGA随着电子技术的飞速发展,传统的数字系统设计方式已逐渐被电子设计自动化(EDA)方法所取代,即利用计算机辅助设计软件为工具,采用高密度可编程逻辑器件(PLD)或现场可编程门阵列FPGA实现复杂数字系统。

本研究基于FPGA器件,以VHDL硬件描述语言为手段,给出了一个通用微处理器的完整设计细节,并讨论了该微处理器的扩展办法及应用实例,为了叙述方便起见,暂定名为DM1型CPU,并以16位方式进行说明。

1. DM1型CPU及存贮器模型分析1.1 CPU结构模型图1 CPU结构图其主要部件由控制单元CTRL、算术逻辑单元ALU、以及寄存器组REGARR和一些相关的寄存器(指令寄存器INSTRREG、临时寄存器OPREG、地址寄存器ADDREG、RESREG结果寄存器)组成。

ADDBUS为16位地址总线,DATABUS为16位数据总线。

1.2 设定指令格式A.单字指令:占用一行如00010 00000 011 010:前5位00010表示指令的操作码;最后3位010表示寄存器号,即第2号;倒数六至三位011表示寄存器号,即第3号。

所以如果我们约定00010操作码为存储store指令,这条指令即表示将3号寄存器中的内容存储到2号寄存器所存储的存贮器地址中。

毕业设计(论文)-基于fpga的函数信号发生器的设计与实现[管理资料]

基于FPGA的函数信号发生器的设计与实现摘要波形发生器己成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数波形发生器的研究背景和DDS的理论。

然后详尽地叙述了用FPGA完成DDS模块的设计过程,接着分析了整个设计中应处理的问题,根据设计原理就功能上进行了划分,将整个仪器功能划分为控制模块、外围硬件、FPGA器件三个部分来实现。

最后就这三个部分分别详细地进行了阐述。

本文利用Altera的设计工具QuartuSH并结合VeI’i1og一HDL语言,采用硬件编程的方法很好地解决了这一问题。

论文最后给出了系统的测量结果,并对误差进行了一定分析,结果表明,,、三角波、锯齿波、方波,通过实验结果表明,本设计达到了预定的要求,并证明了采用软硬件结合,利用FPGA技术实现波形发生器的方法是可行的。

关键词:函数发生器,直接数字频率合成,现场可编程门阵列The Design and Realize of DDS Based on FPGAAbstractArbitrary Waveform Generator(AWG) is one of the most popular instruments in modern testing domains,Which represents the developing direction of signal sources· Direct Digital frequency Synthesis(DDS) advance dearly in full digital technology for frequency synthesis,its LUT method for synthes waveform .Adapts togenerate arbitrary Waveform· Field programable GateArray(FPGA)has the feature sof Iargeseale integration,high working frequency and ean realize lal’ge Memory,50FPGAeaneffeetivelyrealizeDDS.The of Corporation Altera ehosen to do the main digitalProcessing work,which based on its large sale and highs Peed. The 53C2440MCU ehosenasa control ehip· Inthisdesign,how to design the fpga chip and theInter faee between the FPGA and the control ehiP the the method ofSoftware and hardware Programming,the design used the software Quartus11 and languageverilog一HDL solves ,the PrineiPle of DDS and Basis of EDA technology introdueed Problem is the design are analyzed and the whole fun into three Parts:masterehiP,FPGA deviee and PeriPheral three Parts are described indetail disadvantage and thing sneed toadv anceareal Of the dissertation,or asquare wave with in the frequency rangeto20MHz .Planed and the way to use software and hardware Programming method and DDS Technology to realize Functional Waveform Generatoravailable.Keywords:DDS;FPGA;Functional Waveform Generator目录第一章绪论 ................................................ IV ............................................................................................................... IV ................................................................................................................. V ......................................................................................................... V....................................................................................................... VI .............................................................................................................. VII ...................................................................................................... VIIDMA输出方式.......................................................................... VII...................................................................................................... VII..................................................................................................... V III 第二章直接数字频率合成器的原理及性能 ................................................ I .................................................................................................................. I .......................................................................................................... I......................................................................................................... I I DDS原理 ............................................................................................. I II 第三章基于FPGA的DDS模块的实现 .......................................................... I (FPGA)简介 ............................................................................................. I II软件并建立工程 ....................................................................... I I新建Block Diagram/Schematic File并添加模块电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

毕业设计(论文)设计(论文)题目基于FPGA的微处理器设计姓名:学号:学院:专业:年级指导教师:摘要本文使用结构化编程方法,将微处理器内核按照功能划分为不同的模块,采用VHDL语言设计每一个模块的内部功能和外围接口,设计实现了一种基于FPGA芯片的微处理器系统。

该微处理器主要由控制器、运算器和寄存器组成,具有指令控制、操作控制、时间控制和数据加工等基本功能,可实现四位操作数的各种运算,其指令长度为16位定长,采用了直接寻址方式。

最后采用QUARTUSII对设计进行了仿真测试,结果表明设计实现了微处理器的主要功能。

关键字:FPGA,微处理器,VHDLABSTRACTA microprocessor on FPGA is realized by using structured programming. This microprocessor core is divided into several different function modules which are designed using VHDL.The microprocessor consists of controller, arithmetic unit and registers. It realizes the instruction control, operation control, time sequence control and data processing functions. The direct addressing mode is adopted. The various operations for 4bit operand can be achieved. Its instruction length is 16 bit.The design is simulated by using QUARTUSII, and the results show that the main functions of a microprocessor are achieved.Key Words:FPGA, CPU, VHDL目录摘要 (I)ABSTRACT...................................................................................................................................... I I 第1章绪论. (1)1.1 背景 (1)1.2 微处理器的概况 (1)1.3 课题研究方法及技术背景 (1)1.3.1 研究方法 (1)1.3.2 技术背景 (2)1.4 课题工作内容 (3)第二章微处理器体系结构 (4)2.1 CPU的功能和构成 (4)2.2 指令系统分析 (5)2.2.1 RISC 与总线结构 (5)2.2.2 指令系统 (6)2.3 指令时序分析 (8)2.3.1 RISC与流水线 (8)2.3.2 程序计数器与流水线 (8)2.4 CPU整体结构即设计思想 (9)2.4.1 CPU的外部引脚规划 (9)2.4.2 CPU的整体框图 (10)2.4.3 CPU结构的层次划分 (11)第三章CPU数据通路设计 (12)3.1 程序计数器模块PC (12)3.2 程序存储器PC_RAM (13)3.3 指令寄存器模块 (14)3.4 时钟发生器模块 (14)3.5 寄存器堆TRAM (15)3.6 ALU模块 (16)第四章CPU控制单元的设计 (18)4.1 控制器Control模块 (18)4.2 有限状态机FSM模块 (19)4.2.1 有限状态机 (19)4.2.2 利用的VHDL语言进行状态机描述 (19)第五章RISC CPU的仿真验证 (21)5.1 各模块的组合 (21)5.2 综合RTL电路图 (21)5.3 RISCCPU的功能仿真验证 (24)5.3.1 算术运算类指令验证 (24)5.3.2 逻辑运算类指令验证 (25)5.3.3 移位类指令验证 (25)5.3.4 LD数据输出指令仿真 (26)5.3.5 ST运算数据存储仿真 (26)5.4 总结 (27)第六章总结和展望 (28)参考文献 (29)致谢 ...................................................................................................................错误!未定义书签。

附录 (30)第1章绪论1.1 背景随着数字通信和工业控制领域的高速发展,超大规模集成电路的集成度和工艺水平不断提高,要求专用集成电路(ASIC)的功能越来越强,功耗越来越低,生产周期越来越短,这些都对芯片设计提出了巨大的挑战,传统的芯片设计方法已经不能适应复杂的应用需求了,将整个应用电子系统集成在一个芯片中(SOC),已成为现代电子系统设计的趋势。

简单来说,SOC是一种将多个独立的VLSI设计拼合在一起,来形成某一应用所需的全部功能的集成电路,以其高集成度、低功耗等优点越来越受欢迎[1]。

中国的电子信息产业现在增长迅速,主要集中在移动通信设备、数据通信设备、计算机及消费产品领域。

考虑到我国电子信息市场的特殊性,即巨大的移动通信和数字家电市场的核心芯片主要依赖进口的状况。

巨大的市场的需求决定了开发SOC的必要性,现在数字家电的片上系统研究己经成为研究的热点之一。

研究SOC的设计方法和验证方法具有很大的现实意义[2-3]。

其中CPU是SOC的重要组成部分,可以完成简单的数据处理,内存的调度,中断处理等操作。

随着百万门级的FPGA芯片、功能复杂的IP核、可重构的嵌入式处理器核以及各种强大EDA 的开发工具的迅速发展,使得设计者在EDA工具的帮助下完成整个系统从行为算法级到物理结构级的全部设计,并最终将一个电子系统集成到一片FPGA中,即SOPC。

可见,SOPC是基于FPGA解决方案的SOC,是SOC发展的新阶段。

1.2 微处理器的概况微处理器是计算机系统中非常之重要的核心组成部分,它用来控制计算机的各种操作过程,通常也被称为CPU,即中央处理器。

随着科学技术的迅速发展,微处理器的发展也是非常迅速,它的处理能力已经由过去的4位发展到现在的64位,运算能力和处理能力大大提高,应用领域也从计算机系统扩展到各个相关领域,例如通信、航天和工业控制等。

通常,微处理器按照处理能力可以划分为4位、8位、16位、32位和64位微处理器,它的处理能力是逐步提高的。

但是,在微控制器的发展过程中,8位机始终是嵌入式低端应用的主要机型[4]。

现今市场上流行的典型的8位微控制器,可以在各种FPGA上实现,设计灵活方便而且易于进行功能扩展。

因此研究8位CPU内核具有广泛的现实意义,由于其具有较高的处理性能和较少的资源占用,故具有更加广泛的应用前景。

1.3 课题研究方法及技术背景1.3.1 研究方法本课题使用硬件描述语言VHDL采用自顶向下的设计方法设计一个满足要求的8位CPU内核及外部接口,使用EDA软件QUARTUSII软件完成编码、仿真验证。

自顶向下的设计方法就是设计者首先从整体上规划整个系统的功能和性能,然后利用功能分割手段对系统进行划分,分解为规模较小、功能较简单的局部模块,并确立它们之间的相互关系,将设计由上至下进行层次化和模块化,即分层次、分模块地对电子系统进行设计和仿真。

不难看出,采用自顶向下的设计方法实际上就是基于芯片的系统设计方法,这种方法有助于在设计早期发现结构设计中的错误,提高设计成功率。

1.3.2 技术背景1.硬件描述语言VHDL如今,大多数的EDA工具都采用VHDL作为主要的硬件描述语言,这主要源于VHDL强大的自身功能和特点,下面介绍一下VHDL的优点。

(1)具有强大的描述能力VHDL既可以描述系统级电路,也可以描述门电路;既可以采用行为描述、寄存器描述或者结构描述,可以方便地建立电子系统模型。

(2)具有共享与复用能力VHDL采用基于库的设计方法,从而大大减少了工作量,缩短了开发周期。

(3)具有独立于器件和工艺设计的能力VHDL独立于器件的特点可以使设计人员集中精力来进行电子系统的设计和性能优化,而不需要考虑其他问题。

(4)具有良好的可移植能力。

VHDL的可移植性源于它是一种标准化得硬件语言,因此同一个设计描述可以被不同的工具所支持。

(5)具有向ASIC移植的能力。

2.CISC指令集和RISC指令集CISC是一种为了便于编程和提高内存访问效率的芯片设计体系。

早期的计算机使用汇编语言编程,由于内存速度慢且价格昂贵,使得CISC体系得到了用武之地。

它的设计目的是要用最少的机器语言指令来完成所需的计算任务。

后来功能需求越来越丰富,因此越来越多的复杂指令被加入到指令系统中,但是还必须保持着前向的兼容性。

内容的不断扩充和兼容性的考虑,导致庞大的CISC指令系统形成了。

在20世纪90年代中期之前,大多数的微处理器都采用CISC体系包括Intel的80x86和Motorola的6sK系列等[6]。

CISC 体系结构几乎没有考虑流水线的因素,使得指令执行起来耗时而且寻址复杂。

1975年,IBM的设计师提出了一种新的体系结构和指令集设计方案,这就是RISC体系结构。

典型的RISC处理器具有以下特点:(1)指令功能简单,各指令的复杂度分布均衡,有利于形成流水线;(2)控制电路简单,多采用硬连线方式来实现。

因为不需要额外的存取微程序存储器来完成指令的执行,因此可以直接使用硬连线方式来设计;(3)指令定长,指令格式简单,指令编码固定。

这样字段固定,使操作码得译码与操作数的存取可以同时执行,使得控制单元的设计简单化;(4)ALU指令和访存指令分开,并且访存种类很少。

(5)以寄存器对寄存器的运算为主。

寄存器对寄存器的运算有助于减少对存储器的访问次数,提高数据的存取速度[7-8]。

1.4 课题工作内容本文一共分为七章。

各章节内容安排如下:第一章绪论。

第二章微处理器的体系结构。

研究了CPU的整体设计,指令系统和时序分析以及流水线的实现。

第三章CPU数据通路设计。

详细介绍了通路模块中的程序计数器、指令寄存器、程序存储器等的具体设计和功能实现。

第四章CPU控制单元的设计。

详细介绍了控制单元中的控制器和状态机的设计和功能实现。

第五章CPU的仿真验证。

验证CPU的部分功能。

第六章总结和展望。

第二章微处理器体系结构2.1 CPU的功能和构成CPU是计算机的核心组成部分。

计算机进行信息处理可分为以下两个步骤[9]。