【CN209330136U】一种基于FPGA采集多路ADC信息的以太网传输装置【专利】

基于FPGA的多通道ADC采集及DAC回放设计

基于FPGA的多通道ADC采集及DAC回放设计苏宁馨【摘要】在电子通信以及自动化等应用领域中,系统终端信号多以模拟量的形式直观存在并使用,因此模拟量采集和回放电路的设计尤为重要。

由于各系统对采集数据的速度、精度和可靠性指标的要求不同,现提出一种基于FPGA的多通道ADC模拟量采集及DAC回放电路的设计。

重点介绍了以5CEFA2F23CB规格的FPGA作为核心处理器,以VerilogHDL语言实现的采集和回放电路的设计过程,并分别采用SignalTap逻辑分析仪和示波器对数据进行捕获、分析和验证。

系统运行稳定可靠,功能完整实现,效率和精度高,可扩展性强。

【期刊名称】《太原学院学报:自然科学版》【年(卷),期】2019(037)001【总页数】6页(P60-65)【关键词】FPGA;ADC模拟量采集;DAC回放;SignalTap逻辑分析仪【作者】苏宁馨【作者单位】[1]安徽新华学院,安徽合肥230088【正文语种】中文【中图分类】TP2740 引言电子通信行业的蓬勃发展,带动了自动化、航天航空、电子制造等产业的革新。

在各产业系统终端数据的观察中,信号多以模拟量的形式直观存在并应用。

围绕系统终端模拟量采集的工作,行业上和技术上也提出了很多种方法和尝试,近年来模拟量采集电路的设计多以数模转换集成电路的形式出现,在机载系统和航天航空领域也逐渐提出了基于PLC、STM32的方式方法和尝试[1]。

由于不同系统存在环境的差异性,对多通道模拟信号采集数据的速度、精度、系统的稳定性的衡量和要求都有所不同,这就使得对采集系统提出了更高的要求。

为满足数据采集存储的可靠指标以及不同环境下的采集要求,现提出一种基于FPGA的多通道ADC模拟量采集及DAC回放电路的设计。

该电路可通过软件算法提高采集精度,并保证系统硬件电路运行的稳定性和可靠性,应用领域也得到了很好的扩展[2]。

1 系统开发工具及总体设计基于FPGA的多通道ADC模拟量采集及DAC回放设计,系统硬件部分采用Altera 公司现下最为流行的一款FPGA(Cyclone Ⅴ系列的5CEFA2F23CB核心处理器);模拟量采集部分选择ADC084S021 作为主要元件;回放部分则采用 DAC084S085 作为模拟信号回放输出。

基于FPGA的多路AD自动采集系统设计初稿

基于FPGA多路A/D自动采集采集系统设计摘要:在以往AD采集中,通过微控制器控制A/D芯片复杂的逻辑,不仅增加了微控制器干预,从而影响处理器运行速度,同时由于微控制器不断介入A/D控制会影响程序正常运行。

本文概述了基于FPGA的多路数据自动采集系统的设计和实现过程。

该系统采用高速A/D转换器将多路模拟信号转换成数字信号,以FPGA为控制核心产生各种控制时序,控制A/D和模拟量开关切换,并对转换结果进行数据读取保存在双口RAM中,通过试验验证表明该系统工作稳定,能够实现对多路采集信号实时采集处理,检测效果良好。

关键词:FPGA A/D转换自动采集Design of automatic acquisition and acquisition system based on FPGA multi A/DAbstract: In the past, A/D acquisition through the micro controller to control the complexity of the A/D chip logic. That not only increased the micro controller intervention, so that affecting the operating speed of the processor, but also affected the normal operation of the program when the micro controller continuous intervention the A/D conversion. This paper Summary the design and implementation of high speed multi channel data acquisition system based on FPGA, The system uses high speed A/D converter to convert multiple analog signals into digital signals. The FPGA is used as control core to generate various control timing, which is used to control A/D and analog switch, at the same time, the data that is converted is stored in dual port RAM. Through the experiment, the system is proved to can stably real-time process for multi-channel signal acquired system, and the examination effect is good. Key words: A/D FPGA Automatic Acquisition1 引言在高速多路数据采集系统中,通常采用数字信号处理器DSP或单片机作为微控制器,控制模数转换器AD及其他外围设备的工作。

基于FPGA的ADC采集系统的设计_毕业设计论文

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

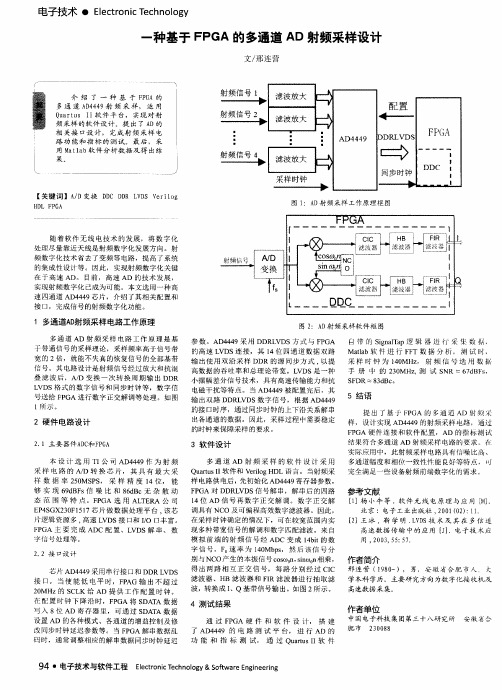

一种基于FPGA的多通道AD射频采样设计

参 数 。AD4449采 用 DDRLVDS方 式 与 FPGA 的高速 LVDS连接,其 14位 四通道 数据双路 输 出使 用 双 沿 采 样 DDR 的源 同步 方 式 ,以提 高 数 据 的吞 吐 率 和 总 理 论 带 宽 。LVDS是 一 种 小 摆 幅 差 分 信 号 技 术 , 具 有 高速 传 输 能 力和 抗 电磁 干 扰 等 特 点 。当 AD4449被 配 置 完 后 , 其 输 出双路 DDRLVDS数 字信 号,根据 AD4449 的接 口时序,通 过同步时钟的上下沿 关系解 串 出 各 通 道 的 数 据 。 因 此 , 采样 过 程 中 需 要稳 定 的 时 钟 来 保 障采 样 的要 求 。

2 硬 件 电 路 设 计

2.1 主要 器 件 ADC和 FPGA

本 设 计 选 用 TI公 司 AD4449作 为 射 频 采 样 电 路 的 A/D 转 换 芯 片 , 其 具 有 最 大 采 样 数 据 率 250MSPS, 采 样 精 度 14位, 能 够 实 现 69dBFs信 噪 比 和 86dBc无 杂 散 动 态 范 围 等 特 点 。FPGA 选 用 ALTERA 公 司 EP4SGX230F1517芯 片 做 数 据 处 理 平 台 .该 芯 片 逻 辑 资 源 多 ,高速 LVDS接 口和 I/O 口丰 富 。 FPGA 主 要 完 成 ADC 配 置 、LVDS解 串 、 数 字 信 号 处 理 等 。

一种基于FPGA的多通道数据采集系统设计与实现

一种基于FPGA的多通道数据采集系统设计与实现随着科技的发展和应用场景的日益多样化,对于数据采集系统的需求也愈发增长。

在许多应用领域中,需要同时采集多个通道的数据,并实时进行处理和分析。

为了满足这一需求,一种基于FPGA(现场可编程门阵列)的多通道数据采集系统应运而生。

本文将重点介绍这种系统的设计与实现。

在设计过程中,首先需要确定系统的性能指标和需求,以便为后续的设计和实施提供指导。

多通道数据采集系统的主要任务是同时采集多个通道的信号,并将其传输给后续的处理单元或存储单元。

因此,系统的设计需要考虑以下几个方面:1.采样率:系统需要能够支持高速的数据采集,以确保采集到的数据具有足够的准确性和精度。

因此,系统的设计中需要考虑到采样率,并选择适当的硬件资源来满足性能需求。

2.通道数:系统需要支持同时采集多个通道的数据。

这涉及到选择适当的输入接口和数据传输协议,并设计合理的硬件电路来实现这一功能。

4.实时性:多通道数据采集系统需要能够实时地采集和传输数据,以满足实时处理和分析的需求。

为了实现实时性,可以利用FPGA的并行计算和高速数据交换的能力,通过合理设计硬件电路和流水线,来提高系统的处理速度。

基于以上需求和考虑因素,可以按照以下步骤设计并实现多通道数据采集系统:1. 确定输入接口和传输协议:根据系统的应用场景和需求,选择适当的输入接口和数据传输协议。

例如,如果需要采集模拟信号,则可以选择适当的模数转换器(ADC)作为输入接口;如果需要高速数据传输,则可以选择PCIe或Ethernet等传输协议。

2.硬件电路设计:设计合理的硬件电路来实现多通道数据采集功能。

这涉及到选择适合的FPGA芯片,并设计模数转换电路、数据缓冲区和数据传输电路等。

3. 编程和配置:选择合适的开发工具和编程语言,对FPGA进行编程和配置。

可以选择使用相关的开发工具和设计语言,如VHDL(VHSIC Hardware Description Language)或Verilog等。

一种基于FPGA的多通道数据采集系统设计与实现

一种基于FPGA的多通道数据采集系统设计与实现摘要介绍一种多通道数据采集系统设计方法.该系统采用FPGA作为硬件平台,主要完成A/D转换控制、时序控制及数据记录等功能。

系统采用Verilog HDL 语言,通过软件编程控制硬件实现多通道的数据采集。

以雷达为应用背景,该系统的仿真验证结果显示,所设计的数据采集系统达到了预期的功能。

关键词数据采集;数据融合;数字下变频;时钟同步;FPGA0 引言数据采集(Data Acquisition)是获取目标信息的最直接和最有效的方法,它研究数据的采集、存储及处理,具有很强的应用性。

随着电子技术的不断发展,数据采集技术得到越来越广泛的应用。

数据采集在通信、雷达、遥测遥感、航空航天、电子对抗等领域里有广泛的应用前景,可以进行现场信号的采集与分析[1]。

由于对信号采集的要求不断的提高,首先在参数方面的要求越来越高,如精度、传输速度、采样通道数等。

其次在具体系统应用、测试和维护中,经常需要对数据进行采集,然后将采集到的数据送入计算机进行实时4分析处理[2]。

因此,数据采集成为系统中至关重要的部分。

鉴于对数据采集后数据分析的需求,采集的数据能够处理并能方便提取原始数据。

本文介绍一种基于FPGA的数据采集系统实现多通道数据采集,从而满足在系统中的应用。

1 数据采集系统的工作原理数据采集系统主要负责多路中频信号处理,完成控制A/D转换控制、时序控制及数据记录等功能。

其内部原理图如图1的数据采集系统原理框图所示. 本文主要介绍数据采集系统的中频接收,关于混频器、低噪放以及功放等模拟部分不做过多介绍。

来自天线收到的射频信号经过接收前端处理后变为中频信号,即模拟信号输入。

中频信号经过调理电路,送给ADC进行模数转换,在FPGA 内进行数字下变频(DDC)处理而得到基带IQ数据.来自外部的时序数据与基带IQ数据进行数据融合,再将融合的数据按照数据记录仪协议进行组帧,经过光模块的光电转换,从而送给数据记录仪的数据接口板。

基于FPGA的多通道数据采集系统设计与实现

基于FPGA的多通道数据采集系统设计与实现概述多通道数据采集系统是一种用于同时采集和处理多个信号通道的系统。

基于现场可编程门阵列(FPGA)的多通道数据采集系统具有高速、灵活、可编程性强等优点,因此在工业控制、医学诊断、科学研究等领域广泛应用。

本文将重点介绍基于FPGA的多通道数据采集系统的设计与实现。

系统设计多通道数据采集系统的设计主要分为硬件设计和软件设计两个部分。

在硬件设计方面,需要选择合适的FPGA芯片作为主控芯片。

FPGA芯片应具备较高的性能和丰富的资源,以满足系统的需求。

此外,还需要选择合适的ADC(模数转换器)芯片用于将模拟信号转换成数字信号。

通常情况下,每个通道需要一个独立的ADC芯片。

选择合适的ADC芯片需要考虑采样率、精度等参数。

在软件设计方面,需要编写FPGA的逻辑设计代码。

逻辑设计代码主要包括时序逻辑和组合逻辑。

时序逻辑用于控制ADC芯片的采样时钟、数据输入和输出时序等,保证数据的正确采集和传输。

组合逻辑用于实现数据的处理和存储等功能。

此外,还需要编写驱动程序用于控制FPGA芯片的配置和数据读写操作。

系统实现多通道数据采集系统的实现过程主要包括硬件实现和软件实现两个阶段。

在硬件实现阶段,首先需要进行FPGA芯片的引脚分配和连接。

根据系统需求,将FPGA芯片的输入输出引脚与ADC芯片的输入输出引脚相连接。

然后进行PCB设计和电路布线,制作板卡。

接下来进行电路调试和功能验证,确保系统的稳定性和功能正常。

在软件实现阶段,首先需要编写FPGA的逻辑设计代码。

根据系统需求,设计数据采集和处理的算法,并将其转化为FPGA的逻辑电路。

然后使用FPGA开发工具对逻辑设计代码进行综合、布局和时序优化。

最后生成可烧写到FPGA芯片的位文件。

总结基于FPGA的多通道数据采集系统实现了高速、灵活和可编程性强的优势。

通过合适的硬件设计和软件设计,可以实现较高的采样率和精度,满足不同领域的应用需求。

【CN209402499U】一种基于FPGA实现以太网传输多路DAC信息的装置【专利】

(19)中华人民共和国国家知识产权局(12)实用新型专利(10)授权公告号 (45)授权公告日 (21)申请号 201920270722.7(22)申请日 2019.03.04(73)专利权人 天津中德应用技术大学地址 300350 天津市津南区海河教育园区雅深路2号(72)发明人 曹鹏飞 (74)专利代理机构 天津市三利专利商标代理有限公司 12107代理人 徐金生(51)Int.Cl.H03M 1/66(2006.01)H04L 12/02(2006.01)(54)实用新型名称一种基于FPGA实现以太网传输多路DAC信息的装置(57)摘要本实用新型公开了一种基于FPGA实现以太网传输多路DAC信息的装置,包括晶振、FPGA芯片、八个DAC芯片、以太网PHY芯片、以太网光模块和上位机,其中:FPGA芯片,分别与晶振、八个DAC芯片、以太网PHY芯片和以太网光模块相连接;以太网PHY芯片和以太网光模块,分别与上位机相连接。

本实用新型提供了一种基于FPGA实现以太网传输多路DAC信息的装置,其能够将上位机产生的多路DAC数据信息,通过以太网电口或光口,经由FPGA芯片,远距离传输给DAC芯片上,有利于广泛地应用,具有重大的生产实践意义。

权利要求书1页 说明书4页 附图2页CN 209402499 U 2019.09.17C N 209402499U权 利 要 求 书1/1页CN 209402499 U1.一种基于FPGA实现以太网传输多路DAC信息的装置,其特征在于,包括晶振、FPGA芯片、八个DAC芯片、以太网PHY芯片、以太网光模块和上位机,其中:FPGA芯片,分别与晶振、八个DAC芯片、以太网PHY芯片和以太网光模块相连接;以太网PHY芯片和以太网光模块,分别与上位机相连接。

2.如权利要求1所述的基于FPGA实现以太网传输多路DAC信息的装置,其特征在于,上位机,用于生成多路DAC数据信息,然后分别通过以太网PHY芯片和以太网光模块发送给FPGA芯片;以太网PHY芯片,用于接收上位机发来的所述多路DAC数据信息,然后发送给FPGA芯片;以太网光模块,用于接收上位机发来的所述多路DAC数据信息,然后发送给FPGA芯片;FPGA芯片,用于接收以太网PHY芯片和以太网光模块发来的所述多路DAC数据信息,然后分别发送给八个DAC芯片;晶振,用于为FPGA芯片提供时钟信号;DAC芯片,用于接收FPGA芯片发来的DAC数据信息,然后进行数字信号和模拟信号的转换操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(19)中华人民共和国国家知识产权局

(12)实用新型专利

(10)授权公告号 (45)授权公告日 (21)申请号 201920270717.6

(22)申请日 2019.03.04

(73)专利权人 天津中德应用技术大学

地址 300350 天津市津南区海河教育园区

雅深路2号

(72)发明人 曹鹏飞 陈更力

(74)专利代理机构 天津市三利专利商标代理有

限公司 12107

代理人 徐金生

(51)Int.Cl.

H04L 12/02(2006.01)

G06F 3/05(2006.01)

G05B 19/042(2006.01)

(54)实用新型名称

一种基于FPGA采集多路ADC信息的以太网传

输装置

(57)摘要

本实用新型公开了一种基于FPGA采集多路

ADC信息的以太网传输装置,包括晶振、FPGA芯

片、四个ADC芯片、以太网PHY芯片、以太网光模块

和上位机,其中:FPGA芯片,分别与晶振、四个ADC

芯片、以太网PHY芯片和以太网光模块相连接;以

太网PHY芯片和以太网光模块,分别与上位机相

连接。

本实用新型公开的一种基于FPGA采集多路

ADC信息的以太网传输装置,其能够将多路ADC芯

片采集的数据信息,通过以太网电口或光口,远

距离传输给上位机,有利于广泛地应用,具有重

大的生产实践意义。

权利要求书1页 说明书5页 附图2页CN 209330136 U 2019.08.30

C N 209330136

U

权 利 要 求 书1/1页CN 209330136 U

1.一种基于FPGA采集多路ADC信息的以太网传输装置,其特征在于,包括晶振、FPGA芯片、四个ADC芯片、以太网PHY芯片、以太网光模块和上位机,其中:

FPGA芯片,分别与晶振、四个ADC芯片、以太网PHY芯片和以太网光模块相连接;

以太网PHY芯片和以太网光模块,分别与上位机相连接。

2.如权利要求1所述的基于FPGA采集多路ADC信息的以太网传输装置,其特征在于,晶振,用于为FPGA芯片提供时钟信号;

ADC芯片,用于采集外部的数据信息,然后发送给FPGA芯片;

FPGA芯片,用于接收ADC芯片采集的数据信息,然后发送给以太网PHY芯片和以太网光模块;

以太网PHY芯片,用于接收FPGA芯片发来的所述ADC芯片采集的数据信息,然后发送给上位机;

以太网光模块,用于接收FPGA芯片发来的所述ADC芯片采集的数据信息,然后发送给上位机;

上位机,用于接收并存储所述以太网PHY芯片和以太网光模块发来的所述ADC芯片采集的数据信息。

3.如权利要求1所述的基于FPGA采集多路ADC信息的以太网传输装置,其特征在于,所述FPGA芯片,通过Serial LVDS接口与ADC芯片相连接;

所述FPGA芯片,通过GMII接口与以太网PHY芯片相连接;

所述FPGA芯片,通过高速GTP收发器接口与以太网光模块相连接。

4.如权利要求1所述的基于FPGA采集多路ADC信息的以太网传输装置,其特征在于,上位机通过以太网电口与以太网PHY芯片相连接;

上位机通过以太网光口与以太网光模块相连接。

5.如权利要求4所述的基于FPGA采集多路ADC信息的以太网传输装置,其特征在于,以太网PHY芯片,通过双绞线与上位机具有的太网电口相连接;

以太网光模块,通过光纤与上位机具有的以太网光口相连接。

6.如权利要求1至5中任一项所述的基于FPGA采集多路ADC信息的以太网传输装置,其特征在于,所述FPGA芯片包括:四个Serial LVDS接口处理电路、数据存储转发电路、Block RAM电路、以太网数据帧处理电路、以太网电口处理电路、以太网光口处理电路和时钟管理电路,其中:

数据存储转发电路,分别与时钟管理电路、四个Serial LVDS接口处理电路、以太网数据帧处理电路和Block RAM电路相连接;

以太网数据帧处理电路,分别与以太网电口处理电路和以太网光口处理电路相连接。

2。