第4章 存储器接口电路设计

Part 4 硬件接口设计

0

0 0

0

0 1

0

1 0

E007h

3007h 4007h

15*CLKIN

10CLKIN 5CLKIN

0

1 1

1

0 0

1

0 1

1007h

F007h 0000h

2CLKIN

1CLMIN 1/2CLKIN

1

1

1

1

0

1

F000h

-

1/4CLKIN

Part 4 TMS320C54x硬件设计及接口技术

TRST

EMU0 EMU1 PD(VCC)

2

13 14 5

测试复位

仿真引脚0 仿真引脚1 存在检测。该引脚的高信号电平表示了 目标板已经通过JTAG接口连接到JTAG 线缆上,在目标系统中,该引脚应该连 接到系统电源VCC上。 接地

输出(O) 输入(I)

Part 4 TMS320C54x硬件设计及接口技术

4.1 基于C54x的DSP最小系统设计 • DSP最小系统就是指没有输入扩展、输出扩展、除了片 内通信通道也没有通信扩展的基本独立的、功能极其有 限的DSP系统。 最小系统是DSP系统硬件设计的基础 DSP最小系统的设计与DSP芯片结合的最紧密 最小系统正常工作是整个DSP硬件系统正常工作的基础

Part 4 TMS320C54x硬件设计及接口技术

目录 4.1 基于C54x的DSP最小系统设计 4.2 C54x外部总线结构 4.3 存储器扩展 4.4 A/D、D/A与DSP的接口技术 4.5 Bootloader功能的实现 4.6 C54x系统设计实例 4.7 DSP系统的调试与抗干扰措施

第4章-数字式移相信号发生器的设计

第4章

2. DDS DDS技术将输出波形的一个完整周期的幅度值都顺 序地存放在波形存储器中, 通过控制相位增量产生频 率、相位可控制的波形。DDS电路一般包括基准时钟、 相位增量寄存器、相位累加器、波形存储器、D/A转换 器和低通滤波器(LPF)等模块, 如图4.4所示。

第4章

相位 增量

相位

地址

K

m

ax

128 359 45

1021.55

则相位控制字K的位数取10 bit就能满足设计任务关于

移相的要求(分辨率为1°, 移相范围是0~359°)。

若“相位加法器”采用24 bit加法器实现, 则上述10 bit的相位控制字应扩展成24 bit, 具体扩展方法是在上述 10 bit相位控制字后面(右边)添加14个逻辑0就可以了。

基于DDS技术的数字式移相信号发生器的主 要模块框图如图4.5所示。

第4章

频率 控制 字 寄 存 器

相位 控制 字 寄 存 器

相位 累加 器

相位 加法 器

寄 存

Address1

器

寄 存

Address2

器

图4.5 基于DDS技术的数字式移相信号发生器主要模块框图

第4章

3. 1)确定系统时钟频率fcp 不妨设输出信号最高频率为fmax 、最高频率 fmax下的最少采样点数为Smin , 则有

第4章

4.3 系统硬件设计

4.3.1 DDS 1. DDS 1971年, 美国学者J.Tierncy、C.M.Rader和B.Gold提出了以全数

字技术从相位概念出发直接合成所需波形的一种新的频率合成原理。 随着电子技术的发展和水平的提高, 一种新的频率合成技术——直接数 字频率合成(DDS, Direct Digital Synthesis)技术得到了飞速发展。 DDS技术是一种把一系列数字形式的信号通过D/A转换而成模拟形式的 信号合成技术, 目前使用最广泛的一种DDS方式是利用高速存储器作查 找表, 然后通过高速D/A转换输出已经用数字形式存入存储器的正弦波。

微型计算机系统原理及应用 第4章 半导体存储器

17

4.3 半导体只读存储器(ROM)

4.3.1 掩膜式只读存储器ROM ROM制造厂家按用户提供的数据,在芯片制造时

写定。用户无法修改。

18

4.3.2 可编程的只读存储器PROM 只能写入一次。

19

4.3.3 可编程、可擦除的只读存储器EPROM

1. 紫外线擦除的EPROM 进行照射10~20min,擦除原存信息,成为全1状态。

8

2.静态RAM的结构 将多个存储单元按一定方式排列起来,就组成了一个静 态RAM存储器。

9

典型的SRAM 6116:2KB,A0~A10,D0~D7形成 128*16*8(每8列组成看作一个整体操作)的阵列

片选CS# 输出允许 OE#

读写控制 WE#

10

典型的SRAM芯片6264 (8KB)

29

存储器芯片的选用

RAM、ROM区别:

–ROM:ROM用来存放程序,为调试方便,多采用EPROM

–RAM:存储器容量不大,功耗较小时,可采用静态RAM;

系统较大,存储器容量很大,功能和价格成为主要矛盾, 要选择动态RAM,这时要考虑刷新问题。

组成存储器模块时,需要考虑的因素主要有:容

量、速度、负载等:

14

2. 双端口RAM举例

CY7C130/131/140/141 1K*8bit高速双端口SRAM A0~A9:地址线 I/O0~I/O7:数据线 CE#:片选 OE#:输出允许线 R/W#:读写控制 BUSY#: INT#:

15

存储器的基本组成 半导体存储器的内部结构为例

译码电路: 重合译码方式 存储体:核心。一个 基本存储电路可存入 一个二进制数码

A12 A7 A6 A5 A4 1 2 3 4 5 6 7 8 9 10 11 12 13 14 28 27 26 25 24 23 22 21 20 19 18 17 16 15 Vcc WE CS 2 A8 A9 A 11 OE A 10 CS 1 D7 D6 D5 D4 D3

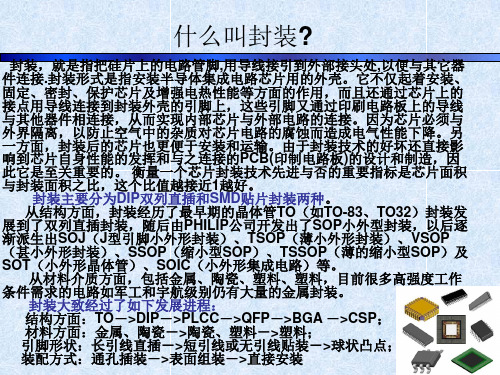

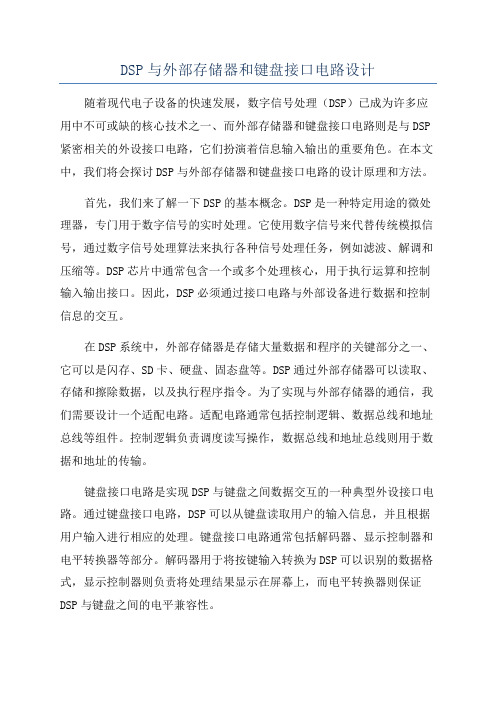

DSP与外部存储器和键盘接口电路设计

DSP与外部存储器和键盘接口电路设计随着现代电子设备的快速发展,数字信号处理(DSP)已成为许多应用中不可或缺的核心技术之一、而外部存储器和键盘接口电路则是与DSP 紧密相关的外设接口电路,它们扮演着信息输入输出的重要角色。

在本文中,我们将会探讨DSP与外部存储器和键盘接口电路的设计原理和方法。

首先,我们来了解一下DSP的基本概念。

DSP是一种特定用途的微处理器,专门用于数字信号的实时处理。

它使用数字信号来代替传统模拟信号,通过数字信号处理算法来执行各种信号处理任务,例如滤波、解调和压缩等。

DSP芯片中通常包含一个或多个处理核心,用于执行运算和控制输入输出接口。

因此,DSP必须通过接口电路与外部设备进行数据和控制信息的交互。

在DSP系统中,外部存储器是存储大量数据和程序的关键部分之一、它可以是闪存、SD卡、硬盘、固态盘等。

DSP通过外部存储器可以读取、存储和擦除数据,以及执行程序指令。

为了实现与外部存储器的通信,我们需要设计一个适配电路。

适配电路通常包括控制逻辑、数据总线和地址总线等组件。

控制逻辑负责调度读写操作,数据总线和地址总线则用于数据和地址的传输。

键盘接口电路是实现DSP与键盘之间数据交互的一种典型外设接口电路。

通过键盘接口电路,DSP可以从键盘读取用户的输入信息,并且根据用户输入进行相应的处理。

键盘接口电路通常包括解码器、显示控制器和电平转换器等部分。

解码器用于将按键输入转换为DSP可以识别的数据格式,显示控制器则负责将处理结果显示在屏幕上,而电平转换器则保证DSP与键盘之间的电平兼容性。

接下来,我们来讨论DSP与外部存储器和键盘接口电路的主要设计原则和方法。

首先,在DSP与外部存储器的接口电路设计中,我们需要考虑以下几个方面:1.数据传输的速度和带宽:在设计数据总线和地址总线时,我们需要确保传输速度足够快,以满足DSP对数据的要求。

同时,我们还需要根据存储器的数据位宽来选择总线的宽度,以确保数据传输的带宽足够大。

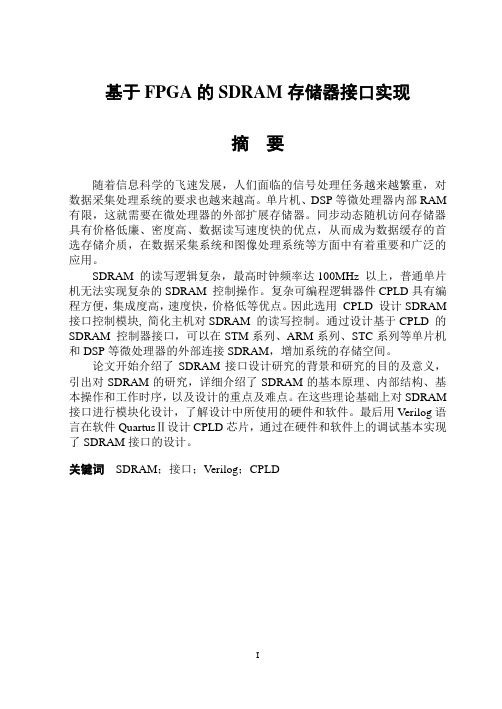

基于FPGA的Verilog语言描述的SDRAM接口电路设计

基于FPGA的SDRAM存储器接口实现摘要随着信息科学的飞速发展,人们面临的信号处理任务越来越繁重,对数据采集处理系统的要求也越来越高。

单片机、DSP等微处理器内部RAM 有限,这就需要在微处理器的外部扩展存储器。

同步动态随机访问存储器具有价格低廉、密度高、数据读写速度快的优点,从而成为数据缓存的首选存储介质,在数据采集系统和图像处理系统等方面中有着重要和广泛的应用。

SDRAM 的读写逻辑复杂,最高时钟频率达100MHz 以上,普通单片机无法实现复杂的SDRAM 控制操作。

复杂可编程逻辑器件CPLD具有编程方便,集成度高,速度快,价格低等优点。

因此选用CPLD 设计SDRAM 接口控制模块, 简化主机对SDRAM 的读写控制。

通过设计基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

论文开始介绍了SDRAM接口设计研究的背景和研究的目的及意义,引出对SDRAM的研究,详细介绍了SDRAM的基本原理、内部结构、基本操作和工作时序,以及设计的重点及难点。

在这些理论基础上对SDRAM 接口进行模块化设计,了解设计中所使用的硬件和软件。

最后用Verilog语言在软件QuartusⅡ设计CPLD芯片,通过在硬件和软件上的调试基本实现了SDRAM接口的设计。

关键词SDRAM;接口;Verilog;CPLDThe Implementation of SDRAM MemoryInterface Based on the EPM570AbstractWith the rapid development of information science, people face more and more onerous task of signal processing, the requirements of data acquisition and processing system are getting higher and higher. Microprocessor such as single-chip microprocessor, DSP etc, their RAM is limited, which requires external expansion in the microprocessor memory. Synchronous Dynamic Random Access Memory has a low cost, high density, fast read and write data on the merits, thereby becoming the first choice for data cache storage medium, which paly an important role and widely used in the data acquisition system and image processing systems.SDRAM read and write logic is complex, the maximum clock frequency reaches above 100MHz, the ordinary microcontroller can not achieve complex SDRAM control operation. Complex programmable logic device has advantages such as programming convenience, high integrity, high speed and low cost etc. Therefore select CPLD to design control module of SDRAM interface , to simplify the host to read and write control of the SDRAM. Through the design of SDRAM controller interface based on CPLD, you can connect SDRAM in the external of STM series, ARM series, STC series single chip microprocessor and the DSP, increase system storage space.At the beginning of paper introduces the research background, research purpose and significance of the study of SDRAM interface design, leads to the study of SDRAM, detailed introduces information of SDRAM about the basic principles, the internal structure, the basic operation and timing of work, and the design emphasis and difficulty. Based on these theories, modularing the designof SDRAM interface, understanding hardware and software used in the design. Finally, it uses Verilog language in Quartus Ⅱsoftware to design CPLD chip, Through the hardware and the software realization SDRAM the commissioning of the basic design of the interface.Keywords SDRAM; Interface; Verilog; CPLD目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景 (1)1.2 课题研究的目的及意义 (1)1.3 同步动态随机存储器简介 (2)1.4 论文的结构和框架 (3)第2章SDRAM的工作原理 (4)2.1 存储器的概述 (4)2.1.1 存储器的分类 (4)2.1.2 存储器的技术指标 (5)2.1.3 存储器的比较 (5)2.2 SDRAM的工作原理 (6)2.2.1 SDRAM存储的基本原理 (6)2.2.2 SDRAM的内部结构 (7)2.3 本章小结 (8)第3章SDRAM的基本操作 (9)3.1 SDRAM的基本操作 (9)3.1.1 芯片初始化 (9)3.1.2 行有效 (9)3.1.3 列读写 (10)3.1.4 读操作 (11)3.1.5 写操作 (12)3.2 SDRAM的工作特性 (13)3.2.1 模式寄存器的设置 (13)3.2.2 预充电 (14)3.2.3 刷新 (15)3.3 SDRAM接口设计的要求 (16)3.3.1 存储器接口解决数据存取的难点 (17)3.3.2 存储器接口在工作方式上的初步优化 (17)3.4 本章小结 (18)第4章系统结构及硬件设计 (19)4.1 SDRAM接口设计的整体结构 (19)4.1.1 控制接口模块 (19)4.1.2 CAS延迟模块 (20)4.1.3 突发长度模块 (22)4.1.4 地址转换模块 (22)4.2 EPM570芯片简介 (23)4.2.1 MAXⅡ系列芯片功能简介 (24)4.2.2 逻辑阵列 (25)4.2.3 全局时钟 (25)4.2.4 I/O端口结构 (26)4.3 MT48LC系列芯片简介 (26)4.4 本章小结 (28)第5章软件设计与实现 (30)5.1 利用QuartusⅡ进行设计的流程 (30)5.2 软件的设计 (31)5.2.1 Verilog语言的特点 (31)5.2.2 采用Verilog设计综合的过程 (32)5.2.3 SDRAM接口设计的仿真 (34)5.3 本章小结 (36)结论 (37)致谢 (38)参考文献 (39)附录A (41)附录B (46)附录C (51)第1章绪论1.1课题背景数据采集处理技术是现代信号处理的基础,广泛应用于雷达、声纳、软件无线电、瞬态信号测试等领域。

《微机原理与接口技术》实验指导书

《微机原理与接口技术》课程实验指导书实验内容EL-8086-III微机原理与接口技术教学实验系统简介使用说明及要求✧实验一实验系统及仪器仪表使用与汇编环境✧实验二简单程序设计实验✧实验三存储器读/写实验✧实验四简单I/0口扩展实验✧实验五8259A中断控制器实验✧实验六8253定时器/计数器实验✧实验七8255并行口实验✧实验八DMA实验✧实验九8250串口实验✧实验十A/D实验✧实验十一D/A实验✧实验十二8279显示器接口实验EL-8086-III微机原理与接口技术教学实验系统简介使用说明及要求EL-8086-III微机原理与接口技术教学实验系统是为微机原理与接口技术课程的教学实验而研制的,涵盖了目前流行教材的主要内容,该系统采用开放接口,并配有丰富的软硬件资源,可以形象生动地向学生展示8086及其相关接口的工作原理,其应用领域重点面向教学培训,同时也可作为8086的开发系统使用。

可供大学本科学习《微机原理与接口技术(8086)》,《单片机应用技术》等课程提供基本的实验条件,同时也可供计算机其它课程的教学和培训使用。

为配合使用EL型微机教学实验系统而开发的8086调试软件,可以在WINDOWS 2000/XP等多种操作系统下运行。

在使用本软件系统调试程序时,可以同时打开寄存器窗口、内存窗口、反汇编窗口、波形显示窗口等等,极大地方便了用户的程序调试。

该软件集源程序编辑、编译、链接、调试与一体,每项功能均为汉字下拉菜单,简明易学。

经常使用的功能均备有热键,这样可以提高程序的调试效率。

一、基本特点EL型微机教学实验系统是北京精仪达盛科技有限公司根据广大学者和许多高等院校实验需求,结合电子发展情况而研制的具有开发、应用、实验相结合的高科技实验设备。

旨在尽快提高我国电子科技发展水平,提高实验者的动手能力、分析解决问题能力。

系统具有以下特点:1、系统采用了模块化设计,实验系统功能齐全,涵盖了微机教学实验课程的大部分内容。

第4章 80C51单片机IO端口及应用最终

24

参考程序:

#include <reg51.h> void main(void) { unsigned char i; P2=0xff; for(;;) { i=P2; P1=i; } }

25

4.6单片机I/O口控制电磁继电器

在控制系统中,常常存在电子电路与电气电路的互 相连接问题,需要电子电路控制电气电路的执行元件, 例如电动机、电磁铁、电灯等,同时实现电子线路与电 气电路的电隔离,以保护电子电路和人身的安全,继电 器在其中起了重要的桥梁作用。

控制

T1

内部总线 写锁存器 读引脚

D P0.x Q 锁存器 Q

BUF2

MUX

P0.x引脚 T2

图4-1 P0口的位电路结构

4

2.P0口工作原理 (1)P0口作为地址/数据总线分时复用口

当80C51单片机外部扩展存储器或者I/O接口芯片,需要 P0口作为地址/数据总线分时使用时,“控制”信号输出高 电平;转换开关MUX 将T2与反相器输出端接通,同时“与 门”开锁,“地址或数据”信号通过与门驱动T1管,并通过 反相器驱动T2管,使得P0.x引脚的输出状态随“地址/数据” 状态的变化而变化。具体输出过程如下。

注意,当P0口作输出口使用时,输出级属开漏电路,在 P0.x引脚应外接上拉电阻。

6

② P0口作为I/O口输入时,端口中的两个三态缓冲器用于读 操作。有2种读操作:读锁存器和读引脚。

“读引脚”:当执行一般的端口输入指令时,引脚上的外部 信号既加在三态缓冲器BUF2的输入端,又加在场效应管T2 漏极上,若此时T2导通,则引脚上的电位被钳在0电平上。 为使读引脚能正确地读入,在输入数据时,要先向锁存器置 “1”,使其Q反端为0,使输出级T1和T2两个管子均被截止, 引脚处于悬浮状态;作高阻抗输入。“读引脚”脉冲把三态 缓冲器打开,于是引脚上的数据经缓冲器到内部总线;

计算机组成原理

2、总线规范

每个总线标准都有详细的规范说明,一般包括以下几个部分 1)机械性能规范:模板尺寸、插头、连接器的规格及位置 等。 2)功能规范:信号线的序号、名称及功能等。 3)电气特性的规范:信号线的电平种类、动态转换时间、 负载能力等。

五、总线的性能指标

评价总线性能的优劣 1、总线宽度:主要是指数据总线的数目。如4/8/16/32/64 直接影响总线的传输率(吞吐量) 2、标准传输率(总线带宽) 单位时间内总线上传输数据的位数。以MB/S表示。 例如:某总线工作频率为8.33MHZ,总线宽度为16位,则 标准传输率为 8.33M×2B/s=16.66MB/s 3、总线定时协议(握手机制) 数据传输采用何种时钟控制。分为同步、异步、半同步、 分离式几种 4、总线控制方式:如仲裁机制、自动配置等。 5、总线复用 两种不同时出现的信号共用一组物理线路,即分时使用同 一组总线,称为总线的多路分时复用。其目的在于减少芯 片的引脚数。 6、信号线数:总线所包含的全部信号线的总数。 7、其它指标:如负载能力、电源电压、能否扩展等。

第三章 系统总线

3.1 总线概述 3.2 常用的总线标准 3.3 总线结构

3.4 总线控制

3.1 总线概述

一、为什么要用总线

机内部件间互连方式:

早期:分散连接 以运算器为核心,内部连线复杂,尤其是当I/O 与存储器交换信息时,都需要经过运算器,严重影 响CPU的工作效率。

采用存储器为核心的分散连接结构,虽采用中断、 DMA等技术,仍无法解决I/0设备与主机之间连接的 灵活性。 目前:总线连接

MAR MDR 容量 10 8 1 K × 8位 16 32 64 K × 32位

1K = 210

2 b = 1 KB 1B = 23b 221b = 256 KB 80 GB

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. 编程 (1) 存储器读 写的汇编语言代码。 存储器读/写的汇编语言代码 写的汇编语言代码。 使用汇编语言向0x0c010000存储单 使用汇编语言向 存储单 元写一个字、 元写一个字、半字和字节或者从 0x0c010000存储单元读取一个字、 存储单元读取一个字、 存储单元读取一个字 半字、字节。 半字、字节。

和复位等命令 和复位等命令

• BooT FLASH 电路及编程 -------29LV160TE芯片 芯片 擦除

29LV160TE芯片具有 种擦除方式 整片擦除、 芯片具有3种擦除方式 整片擦除、 芯片具有 种擦除方式:整片擦除 扇区擦除和 扇区擦除和快擦除 扇区 擦除

: RESET( ); //芯片复位 芯片复位 _WR(0x555,0xaa); _WR(0x2aa,0x55); _WR(0x555,0x80); _WR(0x555,0xaa); _WR(0x2aa,0x55); _WR(BADDR2WADDR(targetAddr),0x30); _WAIT( ); //等待擦除结束 等待擦除结束 _RESET( ); //芯片复位 芯片复位 :

同步动态存储器SDRAM KM416S4020B芯片 同步动态存储器 芯片 •SDRAM全称是同步动态随机存储器(Synchronous 全称是同步动态随机存储器 Dynamic Random Access Memory)。 •SDRAM集成度高 存储容量大 读/写速度快 经 集成度高,存储容量大 写速度快,经 集成度高 存储容量大,读 写速度快 常用其作为主存储器。 常用其作为主存储器。 •SDRAM类型的存储器芯片有许多,其中 类型的存储器芯片有许多, 类型的存储器芯片有许多 KM416S4020B系列是一种容量为1M×16bit×4bank × × 的SDRAM。其工作电压为 。其工作电压为3.3V,支持自动刷新 , (Auto-Refresh)和自刷新(Self- Refresh)。 )和自刷新( )

编程写入 • BooT FLASH 电路及编程 -------编程写入

int _WAIT(void) //检测 检测DQ6输出是否停止翻转 检测 输出是否停止翻转 { volatile U16 flashStatus,old; old=*((volatile U16 *)0x0); while(1) { flashStatus=*((volatile U16 *)0x0); if( (old&0x40) == (flashStatus&0x40)) break; if( flashStatus&0x20 ) //测试超时标志位 测试超时标志位DQ5 测试超时标志位 { old=*((volatile U16 *)0x0);

பைடு நூலகம்

. . . . . . 输入 列 I/O 电路

A0 A2 A1 A9 CS WE

Intel 2114外特性示意图

4.2.4 动态随机存取存储器DRAM

• 1.动态RAM的基本单元电路

单管动态DRAM 4116芯片

• 16 K×1位的存储芯片 × 位的存储芯片

读时序

读时序

• 动态 动态RAM的刷新。刷新的过程 的刷新。 的刷新 实质上是先将原有信息读出, 实质上是先将原有信息读出,再 由刷新放大器形成原信息并重新 写入的再生过程 • 通常有三种方式刷新:集中刷 通常有三种方式刷新: 分散刷新和异步刷新。 新、分散刷新和异步刷新

( *((U16 *)(addr<<1)) )

• BooT FLASH 电路及编程 -------29LV160TE芯片擦除 芯片擦除

HY29LV160是HYUNDAI公司生产的 是 公司生产的Flash存储 公司生产的 存储 操作编程命令包括读 擦除、 器。HY29LV160操作编程命令包括读、擦除、编程

4.3 S3C44B0X存储系统实例 存储系统实例

系统中, 在EV44B0II系统中,使用 系统中 使用Bank0上的一 上的一 片1MB×16位的FLASH(29LV160TE)存 × 位 ( ) 储器来放置系统BIOS,系统上电以后,PC 储器来放置系统 ,系统上电以后, 指针自动指向Bank0的第一个单元,开始进 的第一个单元, 指针自动指向 的第一个单元 行系统自举。使用Bank6上的一片 上的一片4MB×16 行系统自举。使用 上的一片 × 位的SDRAM(KM416S4020B)存储器来存 位的 ( ) 放用户应用程序。 放用户应用程序。

4.2.5 只读存储器ROM

• 掩膜ROM

PROM一次性编程的只读存储器

EPROM可擦除可编程的只读存储器 可擦除可编程的只读存储器

4.2.6 Flash 存储器接口

F1ash闪速存储器又称快擦型存储器,它是在 闪速存储器又称快擦型存储器, 闪速存储器又称快擦型存储器 EPROM和EEPROM工艺基础上产生的种新型的、具有性 工艺基础上产生的种新型的、 能价格比更好、可靠性更高的可擦写非易失性存储器。 能价格比更好、可靠性更高的可擦写非易失性存储器。 Flash按内部构架和实现技术可以分为AND、NAND、 按内部构架和实现技术可以分为 、 、 NOR等几种,目前以NOR Flash和NAND Flash为主流。 等几种, 为主流。 NOR的特点是:芯片内执行,即应用程序可以不必 的特点是: 的特点是 芯片内执行, 内运行; 把代码读到系统RAM中而直接在Flash内运行;传输效率 很高, ~ 的小容量时具有很高的成本效益, 很高,在1~16MB的小容量时具有很高的成本效益,但 是很低的写入和擦除速度大大影响了它的性能。 是很低的写入和擦除速度大大影响了它的性能。 NAND的特点是:极高的单元密度,可以达到高存 的特点是: 的特点是 极高的单元密度, 储密度;写入和擦除的速度也很快, 储密度;写入和擦除的速度也很快,但NAND需要特殊 的系统接口来串行地存取数据。 的系统接口来串行地存取数据。对NAND的管理比较复 杂。

(2)可用 语言来编写,向addr地 可用C语言来编写 可用 语言来编写, 地 址单元写入数据data和从 和从addr地址单 址单元写入数据 和从 地址单 元读出数据。 元读出数据。

#define _WR(addr,data) *((U16 *)(addr<<1))=(U16)data

#define _RD(addr)

4.2.3 静态随机存取存储器 静态随机存取存储器SRAM

• 1.静态RAM基本单元电路

2114 RAM芯片的结构示意图

A3 A4 A5 A6 A7 A8

I / O1 I / O2 数据 I / O3 I / O4 控制 列选择 行 选 择 . . . . . . VCC GND 64× 64存储矩阵

2. NOR Flash型存储芯片 29LV160TE

HY29LV160是HYUNDAI公司生产的 是 公司生产的Flash存储器, 存储器, 公司生产的 存储器 主要特点有 其主要特点有: (1) 3V单电源供电,可使内部产生高电压进行编程 单电源供电, 单电源供电 和擦除操作; 和擦除操作; (2) 支持 支持JEDEC单电源 单电源Flash存储器标准和 存储器标准和CFMI 单电源 存储器标准和 (Common Flash Memory Interface)特性; )特性; (3) 只需向其命令寄存器写入标准的微处理器指令, 只需向其命令寄存器写入标准的微处理器指令, 具体编程、擦除操作由内部嵌入的算法实现, 具体编程、擦除操作由内部嵌入的算法实现,并且可 以通过查询特定的引脚或数据线监控操作是否完成; 以通过查询特定的引脚或数据线监控操作是否完成; (4) 可以对任一扇区进行读、写或擦除操作 ,而不 可以对任一扇区进行读、写或擦除操作, 影响其它部分的数据。 影响其它部分的数据

4.3.1 SDRAM存储器接口及编程

• 1. 电路

SDRAM由MCU专用 由 专用SDRAM片 专用 片 选信号nSCS0/nGCS6选通,地址 选通, 选信号 选通 空间为0x0C000000~0x0C800000。 ~ SDRAM分成 个Bank,每 分成4个 , SDRAM有16位数据宽度, 位数据宽度, 有 位数据宽度 个Bank的容量为1M×l6位。 的容量为 × SDRAM的A0引脚接到决定, 的 引脚接到决定, Bank的地址由 的地址由BAl、BAO决定 的地址由 、 S3C44B0X的A1地址线上, 的 地址线上, 00对应 对应Bank0,01对应 对应Bankl, 对应 , 地址线上, 对应 即ADDR[12:1]同A[11:0]对应 对应 10对应 对应Bank2,11对应 对应Bank3 , 对应 ,同 对应 BA1、 接到A22和A21引脚上。 引脚上。 接到 和 引脚上 连接 、BA0接到

• BooT FLASH 电路及编程 -------编程写入 编程写入

int F29LV160_ProgFlash(U32 realAddr,U16 data) { volatile U16 *tempPt; int temp,count=0; tempPt=(volatile U16 *)realAddr; _WR(0x555,0xaa); _WR(0x2aa,0x55); _WR(0x555,0xa0); 判断写入是否完成的 *tempPt=data; _WAIT()的过程 的过程 return _WAIT( ); }

4.2 半导体存储器

• 半导体存储器分类

半导体存储芯片结构

• 1.半导体存储芯片的基本结构 .

2.半导体存储芯片的译码驱动方式 .

16×1字节线选法芯片结构。用一根字选择线, × 字节线选法芯片结构 用一根字选择线, 字节线选法芯片结构。 直接选中一个存储单元的各位

1 K×1位重合法结构。只要用 根选 位重合法结构。 × 位重合法结构 只要用64根选 择线(X、 两个方向各 两个方向各32根 , 择线 、Y两个方向各 根),便可选择 32×32矩阵中的任一位 . × 矩阵中的任一位