EDA交通灯课程设计(带有测试平台testbench)

EDA课程设计报告交通灯控制系统

一、课程设计目的和要求目的:掌握基于FPGA 的复杂数字系统的设计和验证方法。

提高学生复杂数字系统的设计能力。

要求:使用实验箱为W48-PK2SOPC 试验开发系统,核心器件为Alatera 公司的EP1C6Q240C8芯片,开发软件为Quartus4.0.本实验环节要求学生以FPGA 器件为目标器件,设计典型的数字系统,如:A/D 、D/A 接口;电子密码锁,交通灯控制系统,数字表等复杂硬件电路,完成设计综合、仿真和硬件测试,并写实验报告。

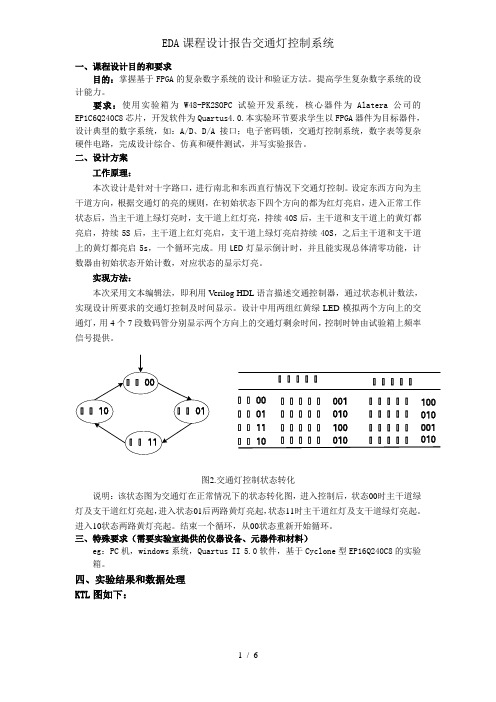

二、设计方案工作原理:本次设计是针对十字路口,进行南北和东西直行情况下交通灯控制。

设定东西方向为主干道方向,根据交通灯的亮的规则,在初始状态下四个方向的都为红灯亮启,进入正常工作状态后,当主干道上绿灯亮时,支干道上红灯亮,持续40S 后,主干道和支干道上的黄灯都亮启,持续5S 后,主干道上红灯亮启,支干道上绿灯亮启持续40S ,之后主干道和支干道上的黄灯都亮启5s ,一个循环完成。

用LED 灯显示倒计时,并且能实现总体清零功能,计数器由初始状态开始计数,对应状态的显示灯亮。

实现方法:本次采用文本编辑法,即利用Verilog HDL 语言描述交通控制器,通过状态机计数法,实现设计所要求的交通灯控制及时间显示。

设计中用两组红黄绿LED 模拟两个方向上的交通灯,用4个7段数码管分别显示两个方向上的交通灯剩余时间,控制时钟由试验箱上频率信号提供。

状状状状状状状状状状状状00状状10状状11状状01状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状001100010010001010100010图2.交通灯控制状态转化说明:该状态图为交通灯在正常情况下的状态转化图,进入控制后,状态00时主干道绿灯及支干道红灯亮起,进入状态01后两路黄灯亮起,状态11时主干道红灯及支干道绿灯亮起。

进入10状态两路黄灯亮起。

结束一个循环,从00状态重新开始循环。

EDA交通灯课程设计(带有测试平台testbench)精讲

EDA技术课程设计`十字路口交通灯控制器设计学院电气与信息工程专业电子信息工程^班级0934111课程名称EDA技术学号0934111**姓名*俊豪}指导教师***成绩评定·一、指导教师评语(根据学生设计报告质量、答辩情况及其平时表现综合评定)。

%。

二、评分/课程设计成绩评定【、目录一、设计题目 ....................................... 错误!未定义书签。

二、设计任务和要求 ................................. 错误!未定义书签。

三、EDA设计........................................ 错误!未定义书签。

、明确系统的功能,并进行逻辑抽象................ 错误!未定义书签。

、模块功能说明.................................. 错误!未定义书签。

、波形仿真及分析................................ 错误!未定义书签。

、代码...................................... 错误!未定义书签。

、各模块rtl电路及功能仿真和时序仿真........ 错误!未定义书签。

四、硬件测试 ....................................... 错误!未定义书签。

五、实验困难问题及解决措施 ......................... 错误!未定义书签。

参考文献 ........................................... 错误!未定义书签。

附录................................................ 错误!未定义书签。

前言伴随着社会的发展以及人类生活水平的提高, EDA技术在电子信息、通信、自动、控制及计算机应用等领域的重要性日益突出。

eda交通灯课程设计

eda交通灯课程设计一、教学目标本课程旨在让学生了解和掌握交通灯系统的基本原理和设计方法。

通过本课程的学习,学生将能够:1.知识目标:理解交通灯系统的原理和组成,包括信号灯、控制器、传感器等;掌握交通灯系统的设计和实施方法,包括硬件设计和软件编程。

2.技能目标:能够使用相关工具和软件进行交通灯系统的设计和仿真;具备一定的实际操作能力,能够进行交通灯系统的安装和调试。

3.情感态度价值观目标:培养学生对交通安全和秩序的重视,提高学生的社会责任感和公民意识。

二、教学内容本课程的教学内容主要包括以下几个部分:1.交通灯系统的原理和组成:介绍交通灯系统的工作原理和基本组成,包括信号灯、控制器、传感器等。

2.交通灯系统的设计和实施:讲解交通灯系统的设计方法和步骤,包括硬件设计和软件编程。

3.交通灯系统的仿真和实验:使用相关工具和软件进行交通灯系统的仿真,并进行实际操作和实验。

4.交通安全和秩序的重要性:强调交通安全和秩序对社会的的重要性,培养学生的社会责任感和公民意识。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括:1.讲授法:讲解交通灯系统的原理和组成,设计和实施方法等基本知识。

2.讨论法:学生进行小组讨论,分享学习心得和经验,提高学生的思维能力和团队合作能力。

3.案例分析法:分析真实的交通灯系统案例,让学生了解交通灯系统的实际应用和效果。

4.实验法:进行交通灯系统的仿真和实验,让学生亲身体验交通灯系统的设计和实施过程。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将准备以下教学资源:1.教材:选择一本适合学生水平的交通灯系统设计教材,作为学生学习的基本参考资料。

2.参考书:提供一些相关的参考书籍,供学生深入学习和研究。

3.多媒体资料:制作一些教学PPT、视频等多媒体资料,帮助学生更好地理解和掌握交通灯系统的原理和设计方法。

4.实验设备:准备一些实验设备,包括交通灯控制器、传感器等,供学生进行实际操作和实验。

eda交通灯课程设计

eda交通灯课程设计一、课程目标知识目标:1. 学生能理解并掌握交通灯的基本原理及其在现代社会交通管理中的作用。

2. 学生能了解EDA(电子设计自动化)的基本概念,并运用其原理设计简单的交通灯控制系统。

3. 学生掌握交通灯工作周期的计算方法,以及不同交通情况下信号灯变换的逻辑规则。

技能目标:4. 学生能够通过EDA软件进行交通灯电路的设计与仿真,具备基本的电子设计能力。

5. 学生能够运用所学知识分析并解决交通灯控制中的实际问题,具备一定的创新设计思维。

情感态度价值观目标:6. 学生通过设计交通灯控制系统,培养对工程技术的兴趣,增强社会责任感和团队合作意识。

7. 学生能够在项目实践中体验科学探究的乐趣,提高学习科学的积极性,形成良好的学习习惯。

8. 学生通过课程学习,认识到科技在生活中的应用,增强对现代科技改善生活品质的认识,培养创新精神和实践能力。

本课程设计针对的是具有一定电子学基础的中高年级学生,课程性质为实践性强的综合设计课。

在分析课程性质、学生特点和教学要求的基础上,课程目标旨在分解为具体的学习成果,以便通过后续的教学设计和评估,有效提升学生对交通工程和电子设计自动化知识的综合应用能力。

二、教学内容本章节教学内容紧密围绕课程目标,结合课本相关章节,科学系统地组织以下内容:1. 交通灯基本原理:讲解交通灯的功能、结构及工作原理,对应教材第3章“交通信号控制基础”。

2. EDA软件介绍:介绍EDA软件的基本功能、操作方法及其在电子设计中的应用,对应教材第5章“电子设计自动化技术”。

3. 交通灯控制系统设计:a. 设计要求:分析交通灯控制系统的需求,明确设计目标和功能要求。

b. 电路设计:学习并运用EDA软件设计交通灯控制电路,对应教材第6章“数字电路设计”。

c. 仿真测试:利用EDA软件对设计电路进行仿真测试,验证设计方案的可行性。

4. 交通灯控制逻辑:学习并掌握交通灯工作周期的计算方法,以及不同交通情况下的信号灯变换规则,对应教材第3章“交通信号控制策略”。

eda交通灯课程设计

eda交通灯课程设计一、课程目标知识目标:1. 学生能理解并掌握EDA交通灯的基本原理,包括信号灯的工作原理、时序控制等。

2. 学生能够运用所学知识,分析并设计简单的交通灯控制系统。

3. 学生了解交通灯在现实生活中的应用,认识到其在交通安全中的重要性。

技能目标:1. 学生能够运用EDA软件进行交通灯电路的设计与仿真。

2. 学生通过小组合作,提高沟通协调能力和团队协作能力。

3. 学生掌握基本电路调试方法,具备解决实际问题的能力。

情感态度价值观目标:1. 学生培养对电子设计与应用的兴趣,激发创新意识。

2. 学生认识到交通灯在保障交通安全、提高道路通行效率方面的重要性,增强社会责任感。

3. 学生在学习过程中,培养严谨、细致、勇于探索的科学态度。

本课程针对初中年级学生,结合学科特点,注重理论与实践相结合,以提高学生的动手能力和创新能力。

在教学过程中,教师需关注学生的个体差异,激发学生的学习兴趣,鼓励学生积极参与讨论和实践,培养其团队协作能力。

通过本课程的学习,期望学生能够掌握交通灯的基本原理,提高电子设计与应用能力,并树立正确的价值观。

二、教学内容本章节教学内容主要包括以下三个方面:1. 交通灯基本原理:- 介绍交通灯的起源、发展及其在现代交通中的应用。

- 讲解交通灯的信号控制原理,包括红绿灯的切换机制和时序控制。

2. EDA软件应用:- 介绍EDA软件的基本功能和使用方法。

- 结合教材章节,教授如何使用EDA软件进行交通灯电路设计与仿真。

3. 实践操作与小组讨论:- 安排学生进行交通灯电路设计实践,指导学生完成电路搭建、调试与优化。

- 组织小组讨论,让学生分享设计心得,互相学习,提高团队协作能力。

教学大纲安排如下:第一课时:交通灯基本原理介绍,占总课时的1/4。

第二课时:EDA软件应用教学,占总课时的1/4。

第三课时:实践操作与小组讨论,占总课时的1/2。

教学内容与教材紧密关联,确保科学性和系统性。

在教学过程中,教师需关注学生对知识点的掌握情况,及时调整教学进度,确保教学效果。

EDA交通灯控制器课程设计

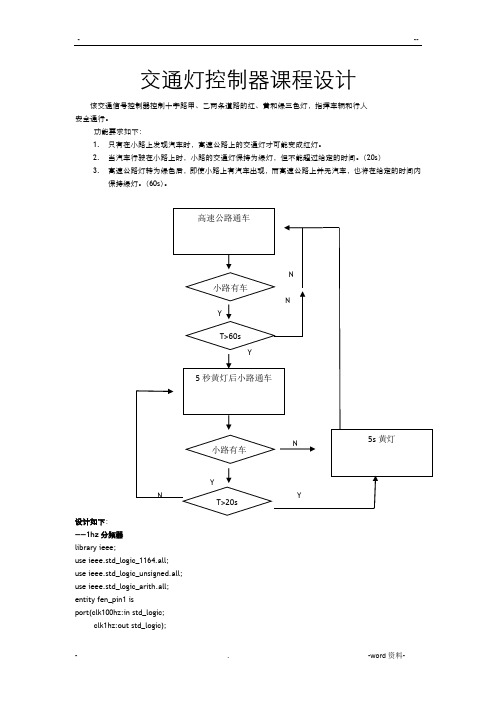

交通灯控制器课程设计该交通信号控制器控制十字路甲、乙两条道路的红、黄和绿三色灯,指挥车辆和行人安全通行。

功能要求如下:1.只有在小路上发现汽车时,高速公路上的交通灯才可能变成红灯。

2.当汽车行驶在小路上时,小路的交通灯保持为绿灯,但不能超过给定的时间。

(20s)3.高速公路灯转为绿色后,即使小路上有汽车出现,而高速公路上并无汽车,也将在给定的时间内保持绿灯。

(60s)。

设计如下:——1hz分频器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen_pin1 isport(clk100hz:in std_logic;clk1hz:out std_logic);end fen_pin1;architecture bhv of fen_pin1 issignal qan:std_logic_vector(3 downto 0); signal qbn:std_logic_vector(3 downto 0); signal cin:std_logic;beginprocess(clk100hz)beginif(clk100hz'event and clk100hz='1')thenif qan="1001"then qan<="0000";cin<='1';else qan<=qan+1;cin<='0';end if;end if;end process;process(clk100hz,cin)beginif(clk100hz'event and clk100hz='1')thenif cin='1' thenif qbn="1001" then qbn<="0000";else qbn<=qbn+1;end if ;end if ;end if ;end process;process(qan,qbn)beginif (qan="1001"and qbn="1001")then clk1hz<='1'; else clk1hz<='0';end if;end process;end bhv;——2hz分频器library ieee;use ieee.std_logic_1164.all;entity fen_pin2 isport (clk100hz:in std_logic;clk2hz:out std_logic);end fen_pin2;architecture bhv of fen_pin2 isbeginprocess(clk100hz)variable cnt:integer range 0 to 24;variable tmp:std_logic;beginif(clk100hz'event and clk100hz='1')thenif cnt=24 thencnt:=0;tmp:=not tmp;elsecnt:=cnt+1;end if;end if;clk2hz<=tmp;end process;end bhv;——主干道控制library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity contralz isport(clk:in std_logic;ra,ga,ya:out std_logic;timeah,timeal:out std_logic_vector(3 downto 0)); end contralz;architecture bhv of contralz istype rg is(green,red,yellow2);beginprocess(clk)variable a:std_logic;variable th,tl:std_logic_vector(3 downto 0);variable state:rg;beginif clk'event and clk='1'thencase state iswhen green=>if a='0'thenth:="0101";tl:="1001";a:='1';ga<='1';ra<='0';ya<='0';elseif not(th="0000"and tl="0001")thenif tl="0000"thentl:="1001";th:=th-1;elsetl:=tl-1;elseth:="0000";tl:="0000";a:='0';state:=red;end if;end if;when red=>if a='0'thenth:="0001";tl:="1001";a:='1';ra<='1';ya<='0';ga<='0';elseif not(th="0000"and tl="0001")then if tl="0000"thentl:="1001";th:=th-1;elsetl:=tl-1;end if;elseth:="0000";tl:="0000";a:='0';ra<='0';ga<='0';state:=yellow2;end if;end if;when yellow2=>if a='0'thenth:="0000";tl:="1001";a:='1';ya<='1';ga<='0';ra<='0';elseif not(th="0000"and tl="0001")then if tl="0000"thentl:="1001";th:=th-1;tl:=tl-1;end if;elseth:="0000";tl:="0000";ga<='0';ra<='0';ya<='0';a:='0';state:=green;end if;end if;end case;end if;timeah<=th;timeal<=tl;end process;end bhv;——支路控制library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity contralx isport(clk:in std_logic;rb,gb,yb,chu:out std_logic;timeah,timeal:out std_logic_vector(3 downto 0)); end contralx;architecture bhv of contralx istype rgy is(red,yellow1,green,yellow2);beginprocess(clk)variable a:std_logic;variable th,tl:std_logic_vector(3 downto 0);variable state:rgy;beginif clk'event and clk='1'thencase state iswhen yellow1=>if a='0'thenth:="0000";tl:="0100";a:='1';yb<='1';gb<='0';chu<='1';elseif not(th="0000"and tl="0001")then if tl="0000"thentl:="1001";th:=th-1;elsetl:=tl-1;end if;elseth:="0000";tl:="0000";a:='0';state:=green;end if;end if;when green=>if a='0'thenth:="0001";tl:="1001";a:='1';gb<='1';rb<='0';yb<='0';chu<='1';elseif not(th="0000"and tl="0001")then if tl="0000"thentl:="1001";th:=th-1;elsetl:=tl-1;end if;elseth:="0000";tl:="0000";a:='0';state:=yellow2;end if;end if;when red=>if a='0'thenth:="0101";tl:="0100";a:='1';yb<='0';chu<='1';elseif not(th="0000"and tl="0001")then if tl="0000"thentl:="1001";th:=th-1;elsetl:=tl-1;end if;elseth:="0000";tl:="0000";a:='0';state:=yellow1;end if;end if;when yellow2=>if a='0'thenth:="0000";tl:="0100";a:='1';yb<='1';gb<='0';rb<='0';chu<='1';elseif not(th="0000"and tl="0001")then if tl="0000"thentl:="1001";th:=th-1;elsetl:=tl-1;end if;elseth:="0000";tl:="0000";a:='0';chu<='0';state:=red;end if;end if;end case;end if;timeah<=th;timeal<=tl;end process;end bhv;——反馈器library ieee;use ieee.std_logic_1164.all;entity smen isport( sm ,re,gr,ye:in std_logic;jinji:out std_logic);end smen;architecture se of smen isbeginprocess isbeginif(sm='1' and re='0' and gr='0' and ye='0') then jinji<='1'; elsejinji<='0';end if;end process;end se;——消抖电路library ieee;use ieee.std_logic_1164.all;entity xiaodou isport(jinji,clk1hz:in std_logic;b:out std_logic);end xiaodou;architecture bhv of xiaodou issignal temp1:std_logic;beginprocess(clk1hz,jinji)variable temp2:std_logic;beginif(clk1hz'event and clk1hz='0')thentemp1<=jinji;temp2:=not temp1;end if;b<=temp1 and temp2 and clk1hz;end process;end bhv;——状态转换library ieee;use ieee.std_logic_1164.all;entity no isport(a:in std_logic;en:out std_logic);end no;architecture no_arc of no isbeginprocess(a)variable tmp:std_logic;beginif(a'event and a='1')thentmp:=not tmp;end if;en<=tmp;end process;end no_arc;——mux4llibrary ieee;use ieee.std_logic_1164.all;entity mux41 isport(sel:in std_logic_vector(2 downto 0);d0,d1,d2,d3:in std_logic_vector(3 downto 0); q:out std_logic_vector(3 downto 0);so:out std_logic_vector(1 downto 0));end mux41;architecture bhv of mux41 isbeginprocess(sel)begincase sel iswhen"100"=>q<=d2;so<="00"; when"101"=>q<=d3;so<="01"; when"000"=>q<=d0;so<="10";when others=>q<=d1;so<="11";end case;end process;end bhv;——译码器library ieee;use ieee.std_logic_1164.all;entity dec7s isport(d:in std_logic_vector(3 downto 0);q0,q1,q2,q3,q4,q5,q6:out std_logic);end dec7s;architecture bhv of dec7s isbeginprocess(d)variable q:std_logic_vector(6 downto 0); begincase d iswhen"0000"=>q:="0111111"; when"0001"=>q:="0000110"; when"0010"=>q:="1011011"; when"0011"=>q:="1001111"; when"0100"=>q:="1100110"; when"0101"=>q:="1101101"; when"0110"=>q:="1111101"; when"0111"=>q:="0100111"; when"1000"=>q:="1111111"; when"1001"=>q:="1101111";when others=>q:="1111001";end case;q0<=q(0);q1<=q(1);q2<=q(2);q3<=q(3);q4<=q(4);q5<=q(5);q6<=q(6);end process;end bhv;--- - . -word 资料- 仿真图如下:Ya,ra,ga 表示主干道黄红绿灯;yb,rb,gb 表示乡村小路黄红绿灯。

毕业设计-EDA技术交通灯控制器(课程设计)

课程设计报告课程设计:交通灯控制器一:实验目的:实现高速公路与乡间小路的交叉路口红绿灯的控制二:功能要求:1.只有在小路上发现汽车时,高速公路上的交通灯才可能变为红灯。

2.当汽车行驶在小路上时、小路的交通灯保持为绿灯,但不能超过给定的延迟时间.〔注;这段时间定义为20S时间)。

3.高速公路灯转为绿灯后,即使小路上有汽车出现,而高速公路上并无汽车,也将在给定的时间内保持高速公路绿灯(注:这段时间定义为60S)。

三:设计思路:五:VHDL源程序:LIBRARY ieee;USE ieee.std_logic_1164.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TrafficLight ISPORT (Clk : IN STD_LOGIC;S,Reset : IN STD_LOGIC;mg,my,mr,cg,cy,cr : OUT STD_LOGIC );END TrafficLight ;ARCHITECTURE rtl OF TrafficLight ISTYPE TrafficState IS (mgcr, mycr, mrcg, mrcy);SIGNAL current_state,next_state : TrafficState ;SIGNAL Count : STD_LOGIC_VECTOR(5 DOWNTO 0);SIGNAL Clrn : STD_LOGIC ;BEGINCounter : PROCESS(clk)BEGINIF Reset = '1' OR (Clrn = '1' AND NOT(Count = "000000")) THEN Count <= "000000";ELSIF clk'EVENT AND clk = '1' THENIF NOT(s='0' AND current_state = mgcr) THEN Count <= Count + 1;END IF;END IF;END PROCESS Counter;StateTransition : PROCESS(clk,Count, current_state)BEGINIF Reset = '1' THEN next_state <= mgcr;Clrn <= '0';ELSIF clk'EVENT AND clk = '1' THENCASE current_state ISWHEN mgcr => mr<='0';mg<='1';my<='0';cr<='1';cg<='0';cy<='0';IF Count >= "111011" AND S = '1' THEN next_state <= mycr;Clrn <= '1';ELSE Clrn <= '0';END IF;WHEN mycr => mr<='0';mg<='0';my<='1';cr<='1';cg<='0';cy<='0';IF Count >= "000100" THEN next_state <= mrcg;Clrn <= '1';ELSE Clrn <= '0';END IF;WHEN mrcg => mr<='1';mg<='0';my<='0';cr<='0';cg<='1';cy<='0';IF Count >= "010011" OR S = '0' THEN next_state <= mrcy;Clrn <= '1';ELSE Clrn <= '0';END IF;WHEN mrcy => mr<='1';mg<='0';my<='0';cr<='0';cg<='0';cy<='1';IF Count >= "000100" THEN next_state <= mgcr;Clrn <= '1';ELSE Clrn <= '0';END IF;WHEN OTHERS => NULL;END CASE;END IF;END PROCESS StateTransition;PROCESS(clk)BEGINIF clk'EVENT AND clk='1' THENcurrent_state <= next_state;END IF;END PROCESS;END rtl;仿真图如下:六:实验心得:通过本次课程设计,使用进一步熟悉了MAX-PLUSLL这种EDA软件工具。

EDA课程设计(交通灯控制器)

课程设计年月日大课程设计任务书课程EDA技术课程设计题目交通灯控制器专业姓名学号主要内容、基本要求、主要参考资料等主要内容:设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。

基本要求:1、红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号,实验电路用逻辑开关代替。

2、主干道处于常允许通行的状态,支干道有车来时才允许通行。

主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。

3、主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路,选择1HZ时钟脉冲作为系统时钟。

4、在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。

主要参考资料:[1] 潘松著.EDA技术实用教程(第二版). 北京:科学出版社,2005.[2] 康华光主编.电子技术基础模拟部分. 北京:高教出版社,2006.[3] 阎石主编.数字电子技术基础. 北京:高教出版社,2003.完成期限2010.3.12指导教师专业负责人2010年3月8日一、总体设计思想1.基本原理计数模块、置数模块、主控制器模块和译码器模块。

置数模块将交通灯的点亮时间预置到置数电路中,计数模块以秒为单位倒计时,当计数值减为零时,主控电路改变输出状态,电路进入下一个状态的倒计时。

其中,核心部分是主控2.设计框图图一.交通灯控制系统的原理框图图二.交通灯控制器的流程图脉冲发生器 控制器 译码器甲车信号灯乙车信号灯定时器1.设计思路:在某一十字路口交叉地带,可设计东西走向的道路为甲车道,南北走向的道路为乙车道。

甲乙车道的交通灯需按交通法则来依次交替运行。

则可设计一个状态循环的逻辑电路。

2.分析系统的逻辑功能:交通灯控制系统的原理框图如图一所示。

EDA交通灯的课程设计

EDA交通灯的课程设计一、课程目标知识目标:1. 让学生理解EDA交通灯的基本原理,掌握交通灯控制系统的设计方法和步骤。

2. 使学生掌握交通灯控制系统中各模块的功能和相互关系,如时钟模块、控制器模块、显示模块等。

3. 帮助学生了解交通灯控制系统的实际应用,提高对电子设计自动化技术的认识。

技能目标:1. 培养学生运用所学知识,设计并实现一个简单的EDA交通灯控制系统的能力。

2. 培养学生使用相关软件(如Multisim、Protel等)进行电路仿真、绘制和调试的能力。

3. 提高学生的团队协作和沟通能力,培养他们在项目实践中解决问题的能力。

情感态度价值观目标:1. 培养学生对电子设计自动化技术的兴趣,激发他们探索未知、创新实践的热情。

2. 培养学生关注社会问题,认识到交通灯控制系统在提高道路通行效率、保障交通安全方面的重要性。

3. 引导学生树立正确的价值观,认识到科技发展应服务于社会、造福于人类。

课程性质:本课程为实践性较强的电子设计课程,以项目为导向,注重培养学生的实际操作能力和团队协作能力。

学生特点:学生具备一定的电子技术基础知识,具有较强的学习兴趣和动手能力,但对EDA技术及其应用尚不熟悉。

教学要求:结合学生特点,采用讲授与实践相结合的教学方法,注重引导学生主动参与、积极探索,提高他们的实际操作能力和创新能力。

在教学过程中,关注学生的个体差异,给予个性化的指导和支持。

通过本课程的学习,使学生能够达到上述课程目标,为后续相关课程的学习和实践奠定基础。

二、教学内容1. 交通灯控制系统概述:介绍交通灯控制系统的基本概念、分类及其在现实生活中的应用。

相关教材章节:第一章 电子设计自动化概述2. EDA技术基础:讲解EDA技术的基本原理、发展历程和常用软件工具。

相关教材章节:第二章 EDA技术基础3. 交通灯控制器设计:a. 时钟模块设计:介绍时钟电路的原理与设计方法。

b. 控制器模块设计:讲解控制器的工作原理、编程方法。

eda交通灯控制器课程设计

eda交通灯控制器课程设计课程设计:EDA交通灯控制器1. 课程背景和目标:EDA交通灯控制器是使用EDA(电子设计自动化)工具进行交通灯控制系统设计的课程。

学习该课程的目标是使学生能够熟练运用EDA工具进行交通灯控制系统设计,并能够理解交通灯控制系统的原理和设计方法。

2. 课程内容和安排:(1) 交通灯控制系统原理介绍:介绍交通灯控制系统的基本原理,包括信号机、信号控制方法和交通流量检测等。

(2) EDA工具介绍:介绍常用的EDA工具,如Verilog、VHDL等,并讲解其基本使用方法。

(3) 交通灯控制器设计流程:介绍交通灯控制器的设计流程,包括需求分析、功能设计、模块设计和系统集成等。

(4) 交通灯控制器设计实践:学生通过实践项目,使用EDA工具设计交通灯控制器。

项目涵盖设计、仿真、验证和生成等环节,学生需要独立完成设计并提交设计报告。

3. 课程教学方法:(1) 理论讲解:通过课堂讲解,介绍交通灯控制系统的原理和设计方法,以及EDA工具的使用方法。

(2) 实践项目:学生通过实践项目,运用所学知识设计交通灯控制器,并进行仿真、验证和生成等环节。

(3) 讨论和案例分析:通过课堂讨论和案例分析,加深学生对交通灯控制系统的理解和应用能力。

(4) 指导和批评:教师对学生的设计进行指导和批评,帮助学生不断提高设计能力。

4. 评估方式:(1) 实践项目报告:学生独立完成实践项目,并提交设计报告,包括设计过程、仿真结果和验证结果等。

(2) 课堂测试:通过课堂测试检验学生对交通灯控制系统原理和EDA工具的理解程度。

(3) 课堂表现:评估学生的课堂出勤情况、学习态度和参与度等。

5. 参考教材:(1) 《交通信号控制原理与技术》高新泽(2) 《EDA与数字电路设计》陈骏等(3) 《数字电路与系统设计》刘敏衡等(4) 《系统设计自动化技术与EDA工具应用》杨学庆等以上是对EDA交通灯控制器课程设计的简要介绍。

课程内容涵盖了交通灯控制系统的原理和设计方法,以及EDA工具的使用方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

情况

(20分)

课程设计

报告质量

(40分)

表达情况

(10分)

回答问题

情况

(10分)

工作态度与纪律

(10分)

独立工作

能力

(10分)

得分

课程设计成绩评定

、

前 言

伴随着社会的发展以及人类生活水平的提高, EDA技术在电子信息、通信、自动、控制及计算机应用等领域的重要性日益突出。随着技术市场与人才市场对DEA需求的不断增加,交通的问题日益突出,单单依靠人力来指挥交通已经不可行了,所以设计交通灯来完成这个需求就显的越加迫切了。为了确保十字路口的行人和车辆顺利、畅通地通过,往往采用电子控制的交通信号来进行指挥。以下就是运用数字电子设计出的交通灯:其中红灯亮,表示该条路禁止通行;黄灯亮表示停车;绿灯亮表示允许通行。

if ati(3 downto 0)="0000" then

ati(3 downto 0)<="1001";--因为总时间使用的是十六进制

ati(7 downto 4)<=ati(7 downto 4)-1;

else ati(3 downto 0)<=ati(3 downto 0)-1;

ati(7 downto 4)<=ati(7 downto 4);

4.译码模块(yima):根据控制信号,驱动交通灯即LED的显示。

5.计数模块(jishu):用来设定A方向和B方向计时器的初值,并为显示模块提供倒计时时间。

6.顶层模块jiaotongdeng,连接各模块设计,使之成为一个有机体。

前5个模块分别进行仿真测试,成功后把所有.vhdl文件包含在工程jiaotongdeng,实现模块化设计。

2.每个方向用两位数码管显示当前状态剩余时间;

3.系统复位后进入东西直行,南北禁行状态;

4.直行状态最后3秒内,绿灯闪烁状态;

三、

由于本设计实验的功能较多,所以就采用模块化设计。整个程序设计基于8种状态,如下表所示:

交通灯状态转换表

状态S

S1S2S3ຫໍສະໝຸດ S4S5S6

S7

S0

A方向

左拐a1

黄灯ay

绿灯ag

[3]王锁萍编.电子设计自动化教程.成都:电子科技大学出版社.2000.

[4]徐志军,徐光辉编.CPLD/FPGA的开发与应用.北京:电子工业出版社.2002 .

[5]杨旭,刘盾等编.EDA技术基础与实验教程.北京:清华大学出版社.2010.

七、

附录一:

本系统采用用硬件描述语言VHDL描述。分为五个模块,分别为控制模块、计时模块、显示模块、译码模块和分频模块,下面针对每个模块给出相应的程序:

图5 计时模块(jishi)rtl图

图6计时模块(jishi)仿真图

模块三:显示模块(xianshi)

图7 显示模块(xianshi)rtl图

图8 显示模块(xianshi)仿真图

模块四:译码模块(yima)

图9 译码模块(yima)rtl图

图10 译码模块(yima)仿真图

模块五:分频模块(fenpin)

process (clk,clr,s)begin

if clr='1' then ati<=x"33";bti<=x"24";

--系统复位后A方向直行绿灯剩余时间为33s,B方向直行红灯剩余时间为24s;

elsif (clk'event and clk ='1') then

if(ati=x"01") or (bti=x"01") then

一、

十字路口交通灯控制器设计。

二、

用EDA技术设计一个十字路口的交通信号灯控制器,控制A、B两条交叉道路上的车辆通行,具体要求如下:

设计一个十字路口交通信号管理控制器。对于每个路口,可实现直行、停止、左转指示,并显示当前状态剩余时间

1.每个方向有直行红灯、直行绿灯、停行黄灯和左转绿灯共4个LED指示灯组成;

2.显示模块(xianshi):显示倒计时时间和工作状。其输出用来驱动4位共阴数码管,并显示倒计时时间(动态扫描)。

3.分频模块(fenpin):本系统动态扫描需要1KHZ的脉冲而系统时钟需要1HZ的脉冲,分频器主要为系统提供所需要的时钟脉冲。该模块将1KHZ的脉冲信号进行分频,产生周期为1hz的方波,作为系统时钟信号的倒计时闪烁信号。

s:in std_logic_vector(2 downto 0);

at,bt:out std_logic_vector(7 downto 0)

);

end jishi;

architecture rtl of jishi is--结构体

signal ati,bti :std_logic_vector(7 downto 0);--中间信号

如图1本方案可实现在确定时刻,倒计数数字显示能够及时变化,红黄绿灯能准确变化,考虑到实际应用,加入人工监督功能,通过改变频率来控制交通灯亮灭的时间的长短。本设计采用模块化设计,图2为本设计十字路口交通等系统的层次结构框图。

3.2、模块功能说明

1.主控制模块(kongzhi):控制系统输入输出之间联系。

case s is--在每个状态,赋给相应初始时间;

when "000"=>ati<=alt;bti<=brt;

when "001"=>ati<=abyt;

when "010"=>ati<=agt;

when "011"=>ati<=abyt;

when "100"=>ati<=art;bti<=blt;

3、设置JTAG链。Altera器件基本都支持JTAG在系统编程方式,这种方式简单易行,不需要专门的编程器。

4、选用模式NO.5,分配引脚,并编译后,把生成*.sof文件下载到基于Cyclone型GW48系列FPGA实验箱开发板上,成功查看结果,CLK时钟频率用1Hz,可通过实验箱上“键7”控制Reset全局复位。

signal q :std_logic_vector(2 downto 0);

begin

-- main logic

process (clk,clr,at,bt)

begin

if clr='1' then q<="011";--系统复位后,系统的状态是A干道绿灯;

B干道红灯;

elsif (clk'event and clk ='1') then

黄灯ay

红灯ar

红灯ar

红灯ar

红灯ar

亮灯时间

10s

4s

20s

4s

33

B方向

红灯br

红灯br

红灯br

红灯br

左拐b1

黄灯by

绿灯bg

黄灯by

亮灯时间

38s

10s

4s

15s

4s

注释:系统复位后进入A方向直行绿灯,B方向直行红灯的状态即S3。

图1 A、B方向示意图

图2 整体模块示意图

3.1、明确系统的功能,并进行逻辑抽象

3.3、

3.3.1、代码

见附录一。

3.3.2、各模块rtl电路及功能仿真和时序仿真

各模块分别建立工程文件,并进行功能仿真、时序仿真,前六个模块成功编译,得到正确仿真结果后,建立顶层模块。

模块一:控制模块(kongzhi)

图3 控制模块(kongzhi)rtl图

图4 控制模块(kongzhi)仿真图

模块二:计时模块(jishi)

/***********为A,B方向设置初值 ***********/

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jishi is--实体部分

port (

clk, clr : in std_logic;

entity kongzhi is--实体部分;

port (

clk,clr : in std_logic;

at,bt:in std_logic_vector(7 downto 0);

s : out std_logic_vector(2 downto 0)

);

end kongzhi;

architecture rtl of kongzhi is--结构体部分;

when "101"=>bti<=abyt;

when "110"=>bti<=bgt;

when "111"=>bti<=abyt;

when others=>ati<=ati;bti<=bti;

end case;

end if;

if ati/=x"01" then--当前时间大于1s时,则相应位进行减一;

图11 分频模块(fenpin)rtl图

图12 分频模块(fenpin)仿真图

模块六:顶层模块

图13 本设计整体rtl图

四、

编程下载和硬件测试的步骤如下:

1、 打开下载窗口。选择菜单“Tool“项的”programmer“,便可打开下载窗口。

2、 设置下载电缆。将ByteBlaster电缆的一端与微机的并行口相连,另一端10针插头与装有目标器件的PCB板上的插座相连。并在”Hardware Setup”中设置下载电缆。