半导体第五讲硅片清洗(4课时)——芯片制造流程课件PPT

合集下载

半导体第五讲硅片清洗

RCA与超声波振动共同作用,可以有更好的去颗粒作用 20~50kHz 或 1MHz左右。

平行于硅片表面的声压波使粒子浸润, 然后溶液扩散入界面,最后粒子完全浸 润,并成为悬浮的自由粒子。

23

机器人自动清洗机

24

清洗容器和载体

✓SC1/SPM/SC2 – 石英( Quartz )或 Teflon容器 ✓HF – 优先使用Teflon,其他无色塑料容器也行。 ✓硅片的载体 – 只能用Teflon 或石英片架

1 2 3 4 粒子和硅片表面的电排斥

• 去除方法:SC-1, megasonic(超声清洗)

15

金属的玷污

➢ 来源:化学试剂,离子注入、反应离子刻蚀等工艺

❖量级:1010原子/cm2

Fe, Cu, Ni, Cr, W, Ti… Na, K, Li…

➢ 影响:

✓在界面形成缺陷,影响器件性能,成品率下降

➢去除方法:使金属原子氧化变成可溶性离子

氧化

M

Mz+ + z e-

还原

➢去除溶液:SC-1, SC-2(H2O2:强氧化剂)

18

有机物的玷污

➢ 来源: • 环境中的有机蒸汽 • 存储容器 • 光刻胶的残留物

➢ 去除方法:强氧化 - 臭氧干法 - Piranha:H2SO4-H2O2 - 臭氧注入纯水

alkali ions.

22

SC-2: HCl(73%):H2O2(30%):DIH2O=1:1:6~1:2:8 70~80C, 10min 酸性(pH值<7)

✓可以将碱金属离子及Al3+、Fe3+和Mg2+在SC-1溶 液中形成的不溶的氢氧化物反应成溶于水的络合物 ✓可以进一步去除残留的重金属污染(如Au)

平行于硅片表面的声压波使粒子浸润, 然后溶液扩散入界面,最后粒子完全浸 润,并成为悬浮的自由粒子。

23

机器人自动清洗机

24

清洗容器和载体

✓SC1/SPM/SC2 – 石英( Quartz )或 Teflon容器 ✓HF – 优先使用Teflon,其他无色塑料容器也行。 ✓硅片的载体 – 只能用Teflon 或石英片架

1 2 3 4 粒子和硅片表面的电排斥

• 去除方法:SC-1, megasonic(超声清洗)

15

金属的玷污

➢ 来源:化学试剂,离子注入、反应离子刻蚀等工艺

❖量级:1010原子/cm2

Fe, Cu, Ni, Cr, W, Ti… Na, K, Li…

➢ 影响:

✓在界面形成缺陷,影响器件性能,成品率下降

➢去除方法:使金属原子氧化变成可溶性离子

氧化

M

Mz+ + z e-

还原

➢去除溶液:SC-1, SC-2(H2O2:强氧化剂)

18

有机物的玷污

➢ 来源: • 环境中的有机蒸汽 • 存储容器 • 光刻胶的残留物

➢ 去除方法:强氧化 - 臭氧干法 - Piranha:H2SO4-H2O2 - 臭氧注入纯水

alkali ions.

22

SC-2: HCl(73%):H2O2(30%):DIH2O=1:1:6~1:2:8 70~80C, 10min 酸性(pH值<7)

✓可以将碱金属离子及Al3+、Fe3+和Mg2+在SC-1溶 液中形成的不溶的氢氧化物反应成溶于水的络合物 ✓可以进一步去除残留的重金属污染(如Au)

芯片制造流程ppt课件

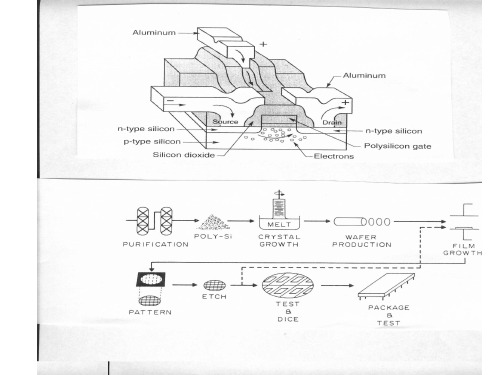

芯片制作过程– 电路连接

The portions of a chip that conduct electricity form the chip’s interconnections. A conducting metal (usually a form of aluminum) is deposited on the entire wafer surface. Unwanted metal removed during lithography and etching leaves microscopically thin lines of metal interconnects. All the millions of individual conductive pathways must be connected in order for the chip to function. This includes vertical interconnections between the layers as well as horizontal Interconnections across each layer of the chip.

SMIC

0.13u

Cu

BEOL

Flow

1M L D D FL O W

C V D S IN D E P FSG D EP S IO N D E P V IA P H O T O V IA D R Y E T C H V IA C L E A N B A R C C O A T IN G PLUG ETCH BACK M TO X PH O TO M T DRY ETCH M T CLEAN STO P LA Y ER R EM O V E P O S T -S L R C L E A N T a N /T a & C u S E E D C U P L A T IN G M 2CU CM P

半导体制造工艺流程_图文

MOS电容

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

主要制程介绍

矽晶圓材料(Wafer)

圓晶是制作矽半導體IC所用之矽晶片,狀似圓 形,故稱晶圓。材料是「矽」, IC( Integrated Circuit)厂用的矽晶片即為 矽晶體,因為整片的矽晶片是單一完整的晶體 ,故又稱為單晶體。但在整體固態晶體內,眾 多小晶體的方向不相,則為复晶體(或多晶體 )。生成單晶體或多晶體与晶體生長時的溫度 ,速率与雜質都有關系。

外延层电阻

SiO2

R

N+

R

P+

P

P+

N-epi

P-SUB

集成电路中电阻5

MOS中多晶硅电阻

多晶硅

SiO2氧化层Si源自其它:MOS管电阻集成电路中电容1

SiO2 P+

A-

N+E P+-I

N+-BL P-SUB

B+

A-

B+

N P+ Cjs

发射区扩散层—隔离层—隐埋层扩散层PN电容

集成电路中电容2

N+

後段backend构装packaging测试制程initialtestandfinaltest一晶圆处理制程晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件如电晶体电容体逻辑闸等为上述各制程中所需技术最复杂且资金投入最多的过程以微处理器microprocessor为例其所需处理步骤可达数百道而其所需加工机台先进且昂贵动辄数千万一台其所需制造环境为为一温度湿度与含尘particle均需控制的无尘室cleanroom虽然详细的处理程序是随著产品种类与所使用的技术有关

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

主要制程介绍

矽晶圓材料(Wafer)

圓晶是制作矽半導體IC所用之矽晶片,狀似圓 形,故稱晶圓。材料是「矽」, IC( Integrated Circuit)厂用的矽晶片即為 矽晶體,因為整片的矽晶片是單一完整的晶體 ,故又稱為單晶體。但在整體固態晶體內,眾 多小晶體的方向不相,則為复晶體(或多晶體 )。生成單晶體或多晶體与晶體生長時的溫度 ,速率与雜質都有關系。

外延层电阻

SiO2

R

N+

R

P+

P

P+

N-epi

P-SUB

集成电路中电阻5

MOS中多晶硅电阻

多晶硅

SiO2氧化层Si源自其它:MOS管电阻集成电路中电容1

SiO2 P+

A-

N+E P+-I

N+-BL P-SUB

B+

A-

B+

N P+ Cjs

发射区扩散层—隔离层—隐埋层扩散层PN电容

集成电路中电容2

N+

後段backend构装packaging测试制程initialtestandfinaltest一晶圆处理制程晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件如电晶体电容体逻辑闸等为上述各制程中所需技术最复杂且资金投入最多的过程以微处理器microprocessor为例其所需处理步骤可达数百道而其所需加工机台先进且昂贵动辄数千万一台其所需制造环境为为一温度湿度与含尘particle均需控制的无尘室cleanroom虽然详细的处理程序是随著产品种类与所使用的技术有关

半导体制程简=PPT课件

– 例如:硅、硅化 物、金属导线等 等。

– 另外,在去除光 阻止后,通常还 需要有一步清洗, 以保证晶园表面 的洁净度。

-

30

2.7 金属蚀刻

• Metal Etch

– 金属蚀刻用于制作芯片中的金属导线。 – 导线的形状由Photo制作出来。 – 这部分工作也使用等离子体完成。

-

31

2.8 薄膜生长

– Develop & Bake

• 曝光完毕之后,晶园送回Track进行显影,洗掉被曝 过光的光阻。

• 然后再进行烘烤,使没有被洗掉的光阻变得比较坚硬 而不至于在下一步蚀刻的时候被破坏掉。

-

24

2.4 酸蚀刻

• Acid Etch

– 将没有被光阻覆盖的薄膜腐蚀掉,是酸蚀刻的 主要任务。

– 蚀刻完毕之后,再将光阻洗去。

• 一般而言通常使用 正光阻。只有少数 层次采用负光阻。

-

20

• 曝光

– Exposure

• 曝光动作的目的是将光罩上的图形传送到晶园上。 • 0.13um,0.18um就是这样做出来的。 • 曝光所采用的机台有两种:Stepper和Scanner。

-

21

• 左图是当今 市场占有率 最高的ASML 曝光机。

半导体制程简介

——芯片是如何制作出来的

-

1

基本过程

• 晶园制作 – Wafer Creation

• 芯片制作 – Chip Creation

• 后封装 – Chip Packaging

-

2

第1部分 晶园制作

-

3

1.1 多晶生成

• Poly Silicon Creation 1

– 目前半导体制程所使用的主要原料就是晶园 (Wafer),它的主要成分为硅(Si)。

– 另外,在去除光 阻止后,通常还 需要有一步清洗, 以保证晶园表面 的洁净度。

-

30

2.7 金属蚀刻

• Metal Etch

– 金属蚀刻用于制作芯片中的金属导线。 – 导线的形状由Photo制作出来。 – 这部分工作也使用等离子体完成。

-

31

2.8 薄膜生长

– Develop & Bake

• 曝光完毕之后,晶园送回Track进行显影,洗掉被曝 过光的光阻。

• 然后再进行烘烤,使没有被洗掉的光阻变得比较坚硬 而不至于在下一步蚀刻的时候被破坏掉。

-

24

2.4 酸蚀刻

• Acid Etch

– 将没有被光阻覆盖的薄膜腐蚀掉,是酸蚀刻的 主要任务。

– 蚀刻完毕之后,再将光阻洗去。

• 一般而言通常使用 正光阻。只有少数 层次采用负光阻。

-

20

• 曝光

– Exposure

• 曝光动作的目的是将光罩上的图形传送到晶园上。 • 0.13um,0.18um就是这样做出来的。 • 曝光所采用的机台有两种:Stepper和Scanner。

-

21

• 左图是当今 市场占有率 最高的ASML 曝光机。

半导体制程简介

——芯片是如何制作出来的

-

1

基本过程

• 晶园制作 – Wafer Creation

• 芯片制作 – Chip Creation

• 后封装 – Chip Packaging

-

2

第1部分 晶园制作

-

3

1.1 多晶生成

• Poly Silicon Creation 1

– 目前半导体制程所使用的主要原料就是晶园 (Wafer),它的主要成分为硅(Si)。

半导体工业流程图

(涂怖光阻)

光 4.Expouse (暴光) (Stepper)

光

Photo mask 光掩膜

5.Developing (显影) (Developer)

6.Etching (蚀刻)

7.不純物注入 (离子(ion)注入法、拡散法)

8.Resist stripping (剥离) (Stripper)

以上1~(7)、8を繰返し、回路 Pattern を形成する。 反复操作以上 1 到(7),8 程序,形成回路 Pattern。

(涂怖光阻)

4.Expouse (暴光) (Stepper)

5.Developing (显影) (Developer)

Chemical Dispense System

6.Etching (蚀刻) WET bench

Day Tank

P

MDM pump 7.不純物注入 (离子(ion)注入法、拡散法)

8.Resist stripping (剥离) (Stripper)

测试工序

製品

产品

出荷

发货

Semiconductor manufac工程

基板工序

1.Cleaning (洗净) Silicon wafer 2.Deposition (成膜) (CVD 法/熱酸化法等)

3.Photoresist Coating (Spin coater)

Semiconductor manufacturing process (半导体工艺流程)

基板工程と pump

基板工序和 pump

1.Cleaning (洗净) machine WET bench

2.Deposition (成膜) (CVD 法/熱酸化法等)

半导体制造工艺课件(PPT 98页)

激活杂质:使不在晶格位置上的离子运动到晶格 位置,以便具有电活性,产生自由载流子,起到 杂质的作用

消除损伤

退火方式:

炉退火

快速退火:脉冲激光法、扫描电子束、连续波激 光、非相干宽带频光源(如卤光灯、电弧灯、石墨 加热器、红外设备等)

氧化工艺

氧化:制备SiO2层 SiO2的性质及其作用 SiO2是一种十分理想的电绝缘材料,

去掉氮化硅层

P阱离子注入,注硼

推阱

去掉N阱区的氧化层 退火驱入

形成场隔离区

生长一层薄氧化层 淀积一层氮化硅

光刻场隔离区,非隔离区被 光刻胶保护起来

反应离子刻蚀氮化硅 场区离子注入 热生长厚的场氧化层 去掉氮化硅层

形成多晶硅栅

生长栅氧化层 淀积多晶硅 光刻多晶硅栅 刻蚀多晶硅栅

掺杂的均匀性好 温度低:小于600℃ 可以精确控制杂质分布 可以注入各种各样的元素 横向扩展比扩散要小得多。 可以对化合物半导体进行掺杂

离子注入系统的原理示意图

离子注入到无定形靶中的高斯分布情况

退火

退火:也叫热处理,集成电路工艺中所有的 在氮气等不活泼气氛中进行的热处理过程都 可以称为退火

Salicide工艺

淀积多晶硅、刻蚀 并形成侧壁氧化层;

淀积Ti或Co等难熔 金属

RTP并选择腐蚀侧 壁氧化层上的金属;

最后形成Salicide 结构

形成硅化物

淀积氧化层 反应离子刻蚀氧化层,形成侧壁氧化层 淀积难熔金属Ti或Co等 低温退火,形成C-47相的TiSi2或CoSi 去掉氧化层上的没有发生化学反应的Ti或Co 高温退火,形成低阻稳定的TiSi2或CoSi2

氧化层刻蚀掉,并去掉光刻胶 进行大剂量As+注入并退火,形成n+埋层

消除损伤

退火方式:

炉退火

快速退火:脉冲激光法、扫描电子束、连续波激 光、非相干宽带频光源(如卤光灯、电弧灯、石墨 加热器、红外设备等)

氧化工艺

氧化:制备SiO2层 SiO2的性质及其作用 SiO2是一种十分理想的电绝缘材料,

去掉氮化硅层

P阱离子注入,注硼

推阱

去掉N阱区的氧化层 退火驱入

形成场隔离区

生长一层薄氧化层 淀积一层氮化硅

光刻场隔离区,非隔离区被 光刻胶保护起来

反应离子刻蚀氮化硅 场区离子注入 热生长厚的场氧化层 去掉氮化硅层

形成多晶硅栅

生长栅氧化层 淀积多晶硅 光刻多晶硅栅 刻蚀多晶硅栅

掺杂的均匀性好 温度低:小于600℃ 可以精确控制杂质分布 可以注入各种各样的元素 横向扩展比扩散要小得多。 可以对化合物半导体进行掺杂

离子注入系统的原理示意图

离子注入到无定形靶中的高斯分布情况

退火

退火:也叫热处理,集成电路工艺中所有的 在氮气等不活泼气氛中进行的热处理过程都 可以称为退火

Salicide工艺

淀积多晶硅、刻蚀 并形成侧壁氧化层;

淀积Ti或Co等难熔 金属

RTP并选择腐蚀侧 壁氧化层上的金属;

最后形成Salicide 结构

形成硅化物

淀积氧化层 反应离子刻蚀氧化层,形成侧壁氧化层 淀积难熔金属Ti或Co等 低温退火,形成C-47相的TiSi2或CoSi 去掉氧化层上的没有发生化学反应的Ti或Co 高温退火,形成低阻稳定的TiSi2或CoSi2

氧化层刻蚀掉,并去掉光刻胶 进行大剂量As+注入并退火,形成n+埋层

芯片生产工艺流程ppt课件

SiO 2

外延层

发射区

基区

集电区

55

背金合金

SiO 2

外延层

发射区

基区

集电区

56

芯片测试

SiO 2

外延层

发射区

基区

集电区

测试系统

57

N型片制造(一般)工艺流程

N

一次氧化

基区光刻

干氧氧化

硼离子注入

基区扩散

发射区光刻

发射区磷预淀积

发射区扩散

发射区低温氧化

氢气处理

3次光刻

铝蒸发

四次光刻

氮氢合金

铝上CVD

先进光刻曝光设备

11

单项工艺-光刻(2)

现场用光刻曝光设备

12

单项工艺-光刻(3)

检查用显微镜

13

单项工艺-光刻(4)

清洗

淀积/生长隔离层

(SiO2 Si3N4 金属…)

匀胶

-HMDS喷淋(增加Si的粘性) -匀光刻胶

14

单项工艺-光刻(5)

前烘

-增加黏附作用 -促进有机溶剂挥发

对版

-对每个圆片必须按要求对版

匀胶

-用弧光灯将光刻版上的图案转 移到光刻胶上。

15

单项工艺-光刻(6)

显影/漂洗

-将圆片进行显影/漂洗,不需要的 的光刻胶溶解到有机溶剂。

坚

膜

-硬化光刻胶。 -增加与硅片的附着性。

腐蚀

-干法腐蚀/湿法腐蚀

去胶

16

单项工艺-光刻(7)

光刻工艺过程

17

单项工艺-CVD(1)

18

单项工艺-CVD(2)

溅射原理示意图

27

单相工艺-蒸发(3)

半导体工艺流程简介ppt

半导体工艺流程的成就与挑战

进一步缩小特征尺寸

三维集成技术

绿色制造技术

智能制造技术

未来半导体工艺流程的发展趋势

01

02

03

04

THANKS

感谢观看

互连

通过金属化过程,将半导体芯片上的电路元件连接起来,实现芯片间的通信和电源分配功能。

半导体金属化与互连

将半导体芯片和相关的电子元件、电路板等封装在一个保护壳内,以防止外界环境对芯片的损伤和干扰。

封装

对封装好的半导体进行功能和性能的检测与试验,以确保其符合设计要求和实际应用需要。

测试

半导体封装与测试

半导体工艺流程概述

02

半导体制造步骤-1

1

半导体材料的选择与准备

2

3

通常使用元素半导体,如硅(Si)、锗(Ge)等,或化合物半导体,如砷化镓(GaAs)、磷化铟(InP)等。

材料类型

高纯度材料对于半导体制造至关重要,杂质含量需要严格控制。

纯净度要求

材料应具有立方、六方或其他特定晶体结构。

晶格结构

蚀刻

使用化学试剂或物理方法,将半导体基板表面未被光刻胶保护的部分进行腐蚀去除。根据蚀刻方法的不同,可以分为湿蚀刻和干蚀刻两种。

去胶

在完成蚀刻后,使用去胶液等化学试剂,去除光刻胶。去胶过程中需要注意控制温度和时间,以避免对半导体基板造成损伤或污染。

半导体的蚀刻与去胶

05

半导体制造步骤-4

金属化

通常使用铝或铜作为主要材料,通过溅射、蒸发或电镀等手段,在半导体表面形成导线图案。

涂布

在半导体基板上涂覆光刻胶,使其覆盖整个基板表面。通常使用旋转涂布法,将光刻胶滴在基板中心,然后通过旋转基板将其展开并涂布在整个表面上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

70~80C, 10min

碱性(pH值>7)

✓可以氧化有机膜

✓和金属形成络合物

✓缓慢溶解原始氧化层,并再氧化——可以去除颗粒

✓NH4OH对硅有腐蚀作用

RCA clean is

OH-

OH-

OH-

OH- OH-

OH-

“standard process” used to remove organics,

heavy metals and

=0.02 ppb !!

12

颗粒粘附

所有可以落在硅片表面的都称作颗粒。

颗粒来源:

✓空气 ✓人体 ✓设备 ✓化学品

超级净化空气

风淋吹扫、防护服、面罩、 手套等,机器手/人

超纯化学品 去离子水

特殊设计及材料 定期清洗

13

各种可能落在芯片表面的颗粒

14

❖粒子附着的机理:静电力,范德华力,化学键等 ❖去除的机理有四种:

19

自然氧化层(Native Oxide)

➢ 在空气、水中迅速生长 ➢ 带来的问题:

✓ 接触电阻增大 ✓ 难实现选择性的CVD或外延 ✓ 成为金属杂质源 ✓ 难以生长金属硅化物

➢ 清洗工艺:HF+H2O(ca. 1: 50)

20

2、硅片清洗

有机物/光刻 胶的两种清 除方法:

SPM:sulfuric/peroxide mixture H2SO4(98%):H2O2(30%)=2:1~4:1 把光刻胶分解为CO2+H2O (适合于几乎所有有机物)

alkali ions.

22

SC-2: HCl(73%):H2O2(30%):DIH2O=1:1:6~1:2:8 70~80C, 10min 酸性(pH值<7)

✓可以将碱金属离子及Al3+、Fe3+和Mg2+在SC-1溶 液中形成的不溶的氢氧化物反应成溶于水的络合物 ✓可以进一步去除残留的重金属污染(如Au)

硅片背面高浓 度掺杂,淀积 多晶硅

本节课主要内容

净化的必要性

器件:少子寿命,VT改变,Ion Ioff,栅击穿电压,可靠性 电路:产率,电路性能

净化的三个层次:环境、硅片清洗、吸杂

The bottom line is chip yield. “Bad” die manufactured alongside “good” die. Increasing yield leads to better profitability in manufacturing chips.

氧等离子体干法刻蚀:把光刻胶分解 为气态CO2+H2O (适用于大多数高分子膜)

注意:高温工艺过程会使污染物扩散进入硅片或薄膜 前端工艺(FEOL)的清洗尤为重要

21

RCA——标准清洗

SC-1(APM,Ammonia Peroxide Mixture):

NH4OH(28%):H2O2(30%):DIH2O=1:1:5~1:2:7

产率提高3.8%,将带来年利润1千万美元!

10

Contaminants may consist of particles, organic films (photoresist), heavy metals or alkali ions.

11

外来杂质的危害性

例2. MOS阈值电压受碱金属离子的影响

例1. 一集成电路厂 产量=1000片/周×100芯片/片,芯 片价格为$50/芯片,如果产率为50%,则正好保本。若 要年赢利$10,000,000,50 52

年开支=年产能 为1亿3千万

1000×100×52×$50×50%

=$130,000,000

1

硅片清洗技术

第五讲

2

本节课主要内容

硅片清洗 湿法清洗:Piranha,RCA(SC-1,SC-2),HF:H2O 物理清洗 干法清洗:气相化学

吸杂三步骤:激活,扩散,俘获 碱金属:PSG,超净化+Si3N4钝化保护 其他金属:本征吸杂和非本征吸杂 ——大密度硅间隙原子+体缺陷

SiO2的成核 生长。

➢去除方法:使金属原子氧化变成可溶性离子

氧化

M

Mz+ + z e-

还原

➢去除溶液:SC-1, SC-2(H2O2:强氧化剂)

18

有机物的玷污

➢ 来源: • 环境中的有机蒸汽 • 存储容器 • 光刻胶的残留物

➢ 去除方法:强氧化 - 臭氧干法 - Piranha:H2SO4-H2O2 - 臭氧注入纯水

1 2 3 4 粒子和硅片表面的电排斥

• 去除方法:SC-1, megasonic(超声清洗)

15

金属的玷污

➢ 来源:化学试剂,离子注入、反应离子刻蚀等工艺

❖量级:1010原子/cm2

Fe, Cu, Ni, Cr, W, Ti… Na, K, Li…

➢ 影响:

✓在界面形成缺陷,影响器件性能,成品率下降

Vth VFB 2 f

2 sqNA (2 f ) qQM

Cox

Cox

当tox=10 nm,QM=6.5×1011 cm-2(10 ppm)时,DVth=0.1 V

例3. MOS DRAM的刷新时间对重金属离子含量Nt的要求

G

1

vth Nt

=10-15 cm2,vth=107 cm/s 若要求G=100 ms,则Nt1012 cm-3

净化级别 高效净化

杂质种类:颗粒、有机 物、金属、天然氧化层

本征吸杂和非本 征吸杂

强氧化

HF:DI H2O

4

三道防线: ✓环境净化(clean room) ✓硅片清洗(wafer cleaning) ✓吸杂(gettering)

5

1、空气净化

From Intel Museum

6

净化级别:每立方英尺空气中含有尺度大于0.5mm的粒子 总数不超过X个。

0.5um

7

排气除尘

8

高效过滤

超细玻璃纤 维构成的多 孔过滤膜: 过滤大颗粒, 静电吸附小 泵 颗粒 循 环 系 统

20~22C 40~46%RH

9

由于集成电路內各元件及连线相当微细,因此制造过程中,如

果遭到灰尘、金属的污染,很容易造成芯片内电路功能的损坏, 形成短路或断路,导致集成电路的失效!在现代的VLSI工厂中, 75%的产品率下降都来源于硅芯片上的颗粒污染。

✓增加p-n结的漏电流,减少少数载流子的寿命

16

不同工艺过程引入的金属污染

离子注入

干法刻蚀 去胶 水汽氧化

9

Fe Ni Cu

10

11

12

13

Log (concentration/cm2)

17

➢金属杂质沉淀到硅表面的机理

– 通过金属离子和硅表面终端的氢原子之间的电荷 交换,和硅结合。(难以去除)

– 氧化时发生:硅在氧化时,杂质会进入