反激同步整流芯片FAN6024应用资料中文版

,OPA602BP,OPA602AU2K5,OPA602AU2K5E4,OPA602APG4,OPA602AUE4,OPA602AUG4, 规格书,Datasheet 资料

Copyright © 1987, Texas Instruments Incorporated

芯天下--/

ABSOLUTE MAXIMUM RATINGS(1)

Supply Voltage ............................................................................... ±18VDC Internal Power Dissipation (TJ ≤ +175°C) .................................... 1000mW Differential Input Voltage .............................................................. Total VS Input Voltage Range ............................................................................ ±VS Storage Temperature Range P and U Packages ....................................................... –40°C to +125°C Operating Temperature Range P and U Packages ........................................................ –25°C to + 85°C Lead Temperature U Package, SO (3s) .................................................................... +260°C Output Short-Circuit to Ground (+25°C) ................................... Continuous Junction Temperature .................................................................... +175°C NOTE: (1) Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

主流微波雷达人体红外感应LD602芯片规格书

主流微波雷达人体红外感应LD602芯片规格书一、概括LD602是一款专为热释电红外传感器信号放大及处理输出的数模混合专用芯片,内部集成了运算放大器、双门限电压比较器、参考电压源、延时时间定时器和封锁时间定时器及状态控制器等,专用于防盗报警系统、人体门控制装置、照明控制开关等场合。

LD602电源工作电压为+3V~+6V,采用CMOS工艺数模混合相结合的集成电路,8个引脚数封装设计,降低了外围电路元件数和整体成本,节省了PCB板空间。

二、应用场合■红外报警器/语音迎宾器■红外感应灯■自动门控控制■自动灯光照明系统■微波雷达感应开关■森林防火报警器三、主要特点●静态功耗小,3V工作电源时功耗小于45uA,5V工作电源时功耗小于75uA,非常适合电池供电系统应用,QQ:298391364●高输入阻抗运算放大器,可与多种传感器匹配,进行信号处理,可作为微波人体感应处理芯片●双向鉴幅器,可有效抑制干扰●内置参考电压,供内部比较器和运放的参考电压●内设延时时间定时器和封锁时间定时器,改变振荡器频率即可设定定时延时时间●8脚红外热释电专用芯片,外围电路简单,成本低●外围元器件少,只需配置第一级运放的增益和振荡器的RC器件即能可靠工作●工作电压+3V~+6V●封装形式SOP8●包装方式管装四、引脚定义五、引脚说明引脚号引脚名功能描述1OUT1内部第一级运放的输出端2IN1内部第一级运放的输入端3VC 触发禁止端当该脚VC电压<0.2Vdd时,禁止触发,即输出信号OUT一直保持低电平当该脚VC电压>0.2Vdd时,允许触发,即输出状态跟随输入信号触发4A 可重复触发和不可重复触发控制端当A=“1”时,允许重复触发当A=“0”时,不可重复触发5GND芯片地6OUT2控制信号输出端,高电平有效输出7CT 振荡器控制端,该脚需对地外接一个振荡电容和对Vdd外接一个上拉电阻8VIN电源输入端,范围3V~6V六、经典常用电路红外感应应用电路微波人体感应方案其中Q2为微波三极管,天线为板载微波天线。

ADC12062CIVF中文资料

TL H 11490ADC12062 12-Bit1 MHz 75 mW A D Converter with Input Multiplexer and Sample HoldDecember1994 ADC1206212-Bit 1MHz 75mW A D Converterwith Input Multiplexer and Sample HoldGeneral DescriptionUsing an innovative multistep conversion technique the12-bit ADC12062CMOS analog-to-digital converter digitizessignals at a1MHz sampling rate while consuming a maxi-mum of only75mW on a single a5V supply TheADC12062performs a12-bit conversion in three lower-res-olution‘‘flash’’conversions yielding a fast A D without thecost and power dissipation associated with true flash ap-proachesThe analog input voltage to the ADC12062is tracked andheld by an internal sampling circuit allowing high frequencyinput signals to be accurately digitized without the need foran external sample-and-hold circuit The multiplexer outputis available to the user in order to perform additional exter-nal signal processing before the signal is digitizedWhen the converter is not digitizing signals it can be placedin the Standby mode typical power consumption in thismode is100m WFeaturesY Built-in sample-and-holdY Single a5V supplyY Single channel or2channel multiplexer operationY Low Power Standby modeKey SpecificationsY Sampling rate1MHz(min)Y Conversion time740ns(typ)Y Signal-to-Noise Ratio f IN e100kHz69 5dB(min)Y Power dissipation(f s e1MHz)75mW(max)Y No missing codes over temperature GuaranteedApplicationsY Digital signal processor front endsY InstrumentationY Disk drivesY Mobile telecommunicationsY Waveform digitizersBlock DiagramTL H 11490–1 Ordering InformationIndustrial(b40 C s T A s a85 )PackageADC12062BIV V44Plastic Leaded Chip CarrierADC12062BIVF VGZ44A Plastic Quad Flat PackageADC12062CIV V44Plastic Leaded Chip CarrierADC12062CIVF VGZ44A Plastic Quad Flat PackageADC12062EVAL Evaluation BoardTRI-STATE is a registered trademark of National Semiconductor CorporationC1995National Semiconductor Corporation RRD-B30M75 Printed in U S AAbsolute Maximum Ratings(Notes1 2)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage(V CC e DV CC e AV CC)b0 3V to a6V Voltage at Any Input or Output b0 3V to V CC a0 3V Input Current at Any Pin(Note3)25mA Package Input Current(Note3)50mA Power Dissipation(Note4)875mW ESD Susceptibility(Note5)2000V Soldering Information(Note6)V Package Infrared 15seconds a300 C VF PackageVapor Phase(60seconds)a215 C Infrared(15seconds)a220 C Storage Temperature Range b65 C to a150 C Maximum Junction Temperature(T JMAX)150 C Operating Ratings(Notes1 2)Temperature Range T MIN s T A s T MAX ADC12062BIV ADC12062CIVADC12062BIVF ADC12062CIVF b40 C s T A s a85 C Supply Voltage Range(DV CC e AV CC)4 5V to5 5VConverter Characteristics The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limit)Resolution12BitsDifferential Linearity Error T A e25 C g0 4g0 8LSB(max)T MIN to T MAX g0 95LSB(max)Integral Linearity Error T MIN to T MAX(BIV Suffix)g0 4g1 0LSB(max) (Note9)TA e a25 C(CIV Suffix)g0 4g1 0LSB(max)T MIN to T MAX(CIV Suffix)g1 5LSB(max) Offset Error T MIN to T MAX(BIV Suffix)g0 3g1 25LSB(max)T A e a25 C(CIV Suffix)g0 3g1 25LSB(max)T MIN to T MAX(CIV Suffix)g2 0LSB(max) Full Scale Error T MIN to T MAX(BIV Suffix)g0 2g1 0LSB(max)T A e a25 C(CIV Suffix)g0 2g1 0LSB(max)T MIN to T MAX(CIV Suffix)g1 5LSB(max) Power Supply Sensitivity DV CC e AV CC e5V g10%g1 0LSB(max) (Note15)R REF Reference Resistance750500X(min) 1000X(max)V REF(a)V REF a(SENSE)Input Voltage AV CC V(max)V REF(b)V REF b(SENSE)Input Voltage AGND V(min)V IN Input Voltage Range To V IN1 V IN2 or ADC IN AV CC a0 05V V(max)AGND b0 05V V(min) ADC IN Input Leakage AGND to AV CC b0 3V0 13m A(max) C ADC ADC IN Input Capacitance25pFMUX On-Channel Leakage AGND to AV CC b0 3V0 13m A(max)MUX Off-Channel Leakage AGND to AV CC b0 3V0 13m A(max) C MUX Multiplexer Input Cap7pFMUX Off Isolation f IN e100kHz92dB2Dynamic Characteristics(Note10)The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND R S e25X f IN e100kHz 0dB from fullscale and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limit)SINAD Signal-to-Noise Plus T MIN to T MAX7168 0dB(min) Distortion RatioSNR Signal-to-Noise Ratio T MIN to T MAX7269 5dB(min) (Note11)THD Total Harmonic Distortion T A e a25 C b82b74dBc(max) (Note12)T MIN to T MAX b70dBc(max) ENOB Effective Number of Bits T MIN to T MAX11 511 0Bits(min) (Note13)IMD Intermodulation Distortion f IN e102 3kHz 102 7kHz b80dBc DC Electrical Characteristics The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limit)V IN(1)Logical‘‘1’’Input Voltage DV CC e AV CC e a5 5V2 0V(min)V IN(0)Logical‘‘0’’Input Voltage DV CC e AV CC e a4 5V0 8V(max) I IN(1)Logical‘‘1’’Input Current0 11 0m A(max) I IN(0)Logical‘‘0’’Input Current0 11 0m A(max)V OUT(1)Logical‘‘1’’Output Voltage DV CC e AV CC e a4 5VI OUT e b360m A2 4V(min)I OUT e b100m A4 25V(min) V OUT(0)Logical‘‘0’’Output Voltage DV CC e AV CC e a4 5V0 4V(max)I OUT e1 6mAI OUT TRI-STATE Output Pins DB0–DB110 13m A(max)Leakage CurrentC OUT TRI-STATE Output Capacitance Pins DB0–DB115pFC IN Digital Input Capacitance4pFDI CC DV CC Supply Current23mA(max) AI CC AV CC Supply Current1012mA(max) I STANDBY Standby Current(DI CC a AI CC)PD e0V20m A3AC Electrical Characteristics The following specifications apply for DV CC e AV CC e a5V V REF a(SENSE)e a4 096V V REF b(SENSE)e AGND and f s e1MHz unless otherwise specified Boldface limits apply for T A e T J from T MIN to T MAX all other limits T A e T J e a25 CSymbol Parameter ConditionsTyp Limit Units (Note7)(Note8)(Limits)f s Maximum Sampling Rate1MHz(min)(1 t THROUGHPUT)t CONV Conversion Time740600ns(min) (S H Low to EOC High)980ns(max)t AD Aperture Delay20ns (S H Low to Input Voltage Held)t S H S H Pulse Width5ns(min)550ns(max)t EOC S H Low to EOC Low9560ns(min) 125ns(max)t ACC Access Time C L e100pF1020ns(max) (RD Low or OE High to Data Valid)t1H t0H TRI-STATE ControlR L e1k C L e10pF2540ns(max) (RD High or OE Low to Databus TRI-STATE)t INTH Delay from RD Low to INT High C L e100pF3560ns(max)t INTL Delay from EOC High to INT Low C L e100pFb25b35ns(min) b10ns(max)t UPDATE EOC High to New Data Valid515ns(max)t MS Multiplexer Address Setup Time50ns(min) (MUX Address Valid to EOC Low)t MH Multiplexer Address Hold Time50ns(min) (EOC Low to MUX Address Invalid)t CSS CS Setup Time20ns(min) (CS Low to RD Low S H Low or OE High)t CSH CS Hold Time20ns(min) (CS High after RD High S H High or OE Low)t WU Wake-Up Time1m s (PD High to First S H Low)Note1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is functional These ratings do not guarantee specific performance limits however For guaranteed specifications and test conditions see the Electrical Characteris-tics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not operated under the listed test conditionsNote2 All voltages are measured with respect to GND(GND e AGND e DGND) unless otherwise specifiedNote3 When the input voltage(V IN)at any pin exceeds the power supply rails(V IN k GND or V IN l V CC)the absolute value of current at that pin should be limited to25mA or less The50mA package input current limits the number of pins that can safely exceed the power supplies with an input current of25mA to twoNote4 The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX i JA and the ambient temperature T A The maximum allowable power dissipation at any temperature is P D e(T JMAX b T A) i JA or the number given in the Absolute Maximum Ratings whichever is lower i JA for the V (PLCC)package is55 C W i JA for the VF(PQFP)package is62 C W In most cases the maximum derated power dissipation will be reached only during fault conditions4Note5 Human body model 100pF discharged through a1 5k X resistor Machine model ESD rating is200VNote6 See AN-450‘‘Surface Mounting Methods and Their Effect on Product Reliability’’or the section titled‘‘Surface Mount’’found in a current National Semiconductor Linear Data Book for other methods of soldering surface mount devicesNote7 Typicals are at a25 C and represent most likely parametric normNote8 Tested limits are guaranteed to National’s AOQL(Average Outgoing Quality Level)Note9 Integral Linearity Error is the maximum deviation from a straight line between the measured offset and full scale endpointsNote10 Dynamic testing of the ADC12062is done using the ADC IN input The input multiplexer adds harmonic distortion at high frequencies See the graph in the Typical Performance Characteristics section for a typical graph of THD performance vs input frequency with and without the input multiplexerNote11 The signal-to-noise ratio is the ratio of the signal amplitude to the background noise level Harmonics of the input signal are not included in its calculation Note12 The contributions from the first nine harmonics are used in the calculation of the THDNote13 Effective Number of Bits(ENOB)is calculated from the measured signal-to-noise plus distortion ratio(SINAD)using the equation ENOB e(SINAD b 1 76) 6 02Note14 The digital power supply current takes up to10seconds to decay to its final value after PD is pulled low This prohibits production testing of the standby current Some parts may exhibit significantly higher standby currents than the20m A typicalNote15 Power Supply Sensitivity is defined as the change in the Offset Error or the Full Scale Error due to a change in the supply voltageTRI-STATE Test Circuit and WaveformsTL H 11490–2TL H 11490–3TL H 11490–4TL H 11490–55Typical Performance CharacteristicsReference VoltageError Change vs Offset and Fullscale vs Reference VoltageLinearity Error Change Input VoltageMux ON Resistance vs vs Temperature Digital Supply Current vs TemperatureAnalog Supply Current on Digital Input PinsStandby Mode vs Voltage Current Consumption in vs Temperature Conversion Time (t CONV )vs TemperatureEOC Delay Time (t EOC )Spectral Response(ADC IN)SINAD vs Input Frequency (ADC IN)SNR vs Input Frequency (ADC IN)THD vs Input Frequency TL H 11490–276Typical Performance Characteristics(Continued)(Through Mux)SINAD vs Input Frequency (Through Mux)SNR vs Input Frequency (Through Mux)THD vs Input Frequency Impedance SNR and THD vs Source Reference VoltageSNR and THD vs TL H 11490–28Timing DiagramsTL H 11490–9FIGURE 1 Interrupt Interface Timing (MODE e 1 OE e 1)7Timing Diagrams (Continued)TL H 11490–10FIGURE 2 High Speed Interface Timing (MODE e 1 OE e 1 CS e 0 RD e 0)TL H 11490–11FIGURE 3 CS Setup and Hold Timing for S H RD and OEConnection DiagramsTL H 11490–13Top ViewTL H 11490–29Top View8Pin DescriptionsAV CC These are the two positive analog supplyinputs They should always be connectedto the same voltage source but arebrought out separately to allow for sepa-rate bypass capacitors Each supply pinshould be bypassed to AGND with a0 1m F ceramic capacitor in parallel with a10m F tantalum capacitorDV CC This is the positive digital supply input Itshould always be connected to the samevoltage as the analog supply AV CC Itshould be bypassed to DGND2with a0 1m F ceramic capacitor in parallel with a10m F tantalum capacitorAGND These are the power supply ground pins DGND1 There are separate analog and digital DGND2ground pins for separate bypassing of theanalog and digital supplies The groundpins should be connected to a stablenoise-free system ground All of theground pins should be returned to thesame potential AGND is the analogground for the converter DGND1is theground pin for the digital control linesDGND2is the ground return for the outputdatabus See Section6 0LAYOUT ANDGROUNDING for more informationDB0–DB11These are the TRI-STATE output pins en-abled by RD CS and OEV IN1 V IN2These are the analog input pins to the mul-tiplexer For accurate conversions no in-put pin(even one that is not selected)should be driven more than50mV belowground or50mV above V CCMUX OUT This is the output of the on-board analoginput multiplexerADC IN This is the direct input to the12-bit sam-pling A D converter For accurate conver-sions this pin should not be driven morethan50mV below AGND or50mV aboveAV CCS0This pin selects the analog input that willbe connected to the ADC12062during theconversion The input is selected based onthe state of S0when EOC makes its high-to-low transition Low selects V IN1 highselects V IN2MODE This pin should be tied to DV CCCS This is the active low Chip Select controlinput When low this pin enables the RDS H and OE inputs This pin can be tiedlowINT This is the active low Interrupt outputWhen using the Interrupt Interface Mode(Figure1) this output goes low when aconversion has been completed and indi-cates that the conversion result is avail-able in the output latches This output isalways high when RD is held low(Figure2)EOC This is the End-of-Conversion control out-put This output is low during a conversion RD This is the active low Read control inputWhen RD is low(and CS is low) the INToutput is reset and(if OE is high)data ap-pears on the data bus This pin can be tiedlowOE This is the active high Output Enable con-trol input This pin can be thought of as aninverted version of the RD input(see Fig-ure6) Data output pins DB0–DB11areTRI-STATE when OE is low Data appearson DB0–DB11only when OE is high andCS and RD are both low This pin can betied highS H This is the Sample Hold control input Theanalog input signal is held and a new con-version is initiated by the falling edge ofthis control input(when CS is low) PD This is the Power Down control input Thispin should be held high for normal opera-tion When this pin is pulled low the devicegoes into a low power standby mode V REF a(FORCE) These are the positive and negative volt-V REF b(FORCE)age reference force inputs respectivelySee Section4 REFERENCE INPUTS formore informationV REF a(SENSE) These are the positive and negative volt-V REF b(SENSE)age reference sense pins respectivelySee Section4 REFERENCE INPUTS formore informationV REF 16This pin should be bypassed to AGND witha0 1m F ceramic capacitorTEST This pin should be tied to DV CC9Functional DescriptionThe ADC12062performs a12-bit analog-to-digital conver-sion using a3step flash technique The first flash deter-mines the six most significant bits the second flash gener-ates four more bits and the final flash resolves the two least significant bits Figure4shows the major functional blocks of the converter It consists of a2 -bit Voltage Estimator a resistor ladder with two different resolution voltage spans a sample hold capacitor a4-bit flash converter with front end multiplexer a digitally corrected DAC and a capacitive volt-age dividerThe resistor string near the center of the block diagram in Figure4generates the6-bit and10-bit reference voltages for the first two conversions Each of the16resistors at the bottom of the string is equal to of the total string resist-ance These resistors form the LSB Ladder and have a voltage drop of of the total reference voltage(V REF a b V REF b)across each of them The remaining resistors form the MSB Ladder It is comprised of eight groups of eight resistors each connected in series(the lowest MSB ladder resistor is actually the entire LSB ladder) Each MSB Ladder section has of the total reference voltage across it Within a given MSB ladder section each of the eight MSB resistors has of the total reference voltage across it Tap points are found between all of the resistors in both the MSB and LSB ladders The Comparator MultipIexer can connect any of these tap points in two adjacent groups of eight to the sixteen comparators shown at the right of Figure4 This function provides the necessary reference voltages to the comparators during the first two flash con-versionsThe six comparators seven-resistor string(Estimator DAC ladder) and Estimator Decoder at the left of Figure4form Note The weight of each resistor on the LSB ladder is actually equivalent to four12-bit LSBs It is called the LSB ladder because it has thehighest resolution of all the ladders in the converter the Voltage Estimator The Estimator DAC connected be-tween V REF a and V REF b generates the reference volt-ages for the six Voltage Estimator comparators The com-parators perform a very low resoIution A D conversion to obtain an‘‘estimate’’of the input voltage This estimate is used to control the placement of the Comparator Multiplex-er connecting the appropriate MSB ladder section to the sixteen flash comparators A total of only22comparators(6 in the Voltage Estimator and16in the flash converter)is required to quantize the input to6bits instead of the64that would be required using a traditional6-bit flashPrior to a conversion the Sample Hold switch is closed allowing the voltage on the S H capacitor to track the input voItage Switch1is in position1 A conversion begins by opening the Sample Hold switch and latching the output of the Voltage Estimator The estimator decoder then selects two adjacent banks of tap points aIong the MSB ladder These sixteen tap points are then connected to the sixteen flash converters For exampIe if the input voltage is be-tween and of V REF(V REF e V REF a b V REF b) the estimator decoder instructs the comparator multiplexer to select the sixteen tap points between and ( and )of V REF and connects them to the sixteen comparators The first flash conversion is now performed producing the first6MSBs of dataAt this point Voltage Estimator errors as large as of V REF will be corrected since the comparators are connect-ed to ladder voltages that extend beyond the range speci-fied by the Voltage Estimator For example if( )V REF k V IN k( )V REF the Voltage Estimator’s comparators tied to the tap points below( )V REF will output‘‘1’’s (000111) This is decoded by the estimator decoder to‘‘10’’ The16comparators will be placed on the MSB ladderTL H 11490–14FIGURE4 Functional Block Diagram10Functional Description(Continued)tap points between( )V REF and( )V REF This overlap of ( )V REF will automatically cancel a Voltage Estimator er-ror of up to256LSBs If the first flash conversion deter-mines that the input voltage is between( )V REF and (( )V REF b LSB 2) the Voltage Estimator’s output code will be corrected by subtracting‘‘1’’ resulting in a corrected value of‘‘01’’for the first two MSBs If the first flash conver-sion determines that the input voltage is between( )V REF b LSB 2)and( )V REF the voltage estimator’s output code is unchangedThe results of the first flash and the Voltage Estimator’s output are given to the factory-programmed on-chip EEPROM which returns a correction code corresponding to the error of the MSB ladder at that tap This code is convert-ed to a voltage by the Correction DAC To generate the next four bits SW1is moved to position2 so the ladder voltage and the correction voltage are subtracted from the input voltage The remainder is applied to the sixteen flash con-verters and compared with the16tap points from the LSB ladderThe result of this second conversion is accurate to10bits and describes the input remainder as a voltage between two tap points(V H and V L)on the LSB ladder To resolve the last two bits the voltage across the ladder resistor(between V H and V L)is divided up into4equal parts by the capacitive voltage divider shown in Figure5 The divider also creates 6LSBs below V L and6LSBs above V H to provide overlap used by the digital error correction SW1is moved to posi-tion3 and the remainder is compared with these16new voltages The output is combined with the results of the Voltage Estimator first flash and second flash to yield the final12-bit resultBy using the same sixteen comparators for all three flash conversions the number of comparators needed by the multi-step converter is significantly reduced when compared to standard multi-step techniquesApplications Information1 0MODES OF OPERATIONThe ADC12062has two interface modes An interrupt read mode and a high speed mode Figures1and2show the timing diagrams for these interfacesIn order to clearly show the relationship between S H CS RD and OE the control logic decoding section of the ADC12062is shown in Figure6Interrupt InterfaceAs shown in Figure1 the falling edge of S H holds the input voltage and initiates a conversion At the end of the conver-sion the EOC output goes high and the INT output goes low indicating that the conversion results are latched and may be read by pulling RD low The falling edge of RD re-sets the INT line Note that CS must be low to enable S H or RDHigh Speed InterfaceThis is the fastest interface shown in Figure2 Here the output data is always present on the databus and the INT to RD delay is eliminatedTL H 11490–15FIGURE5 The Capacitive Voltage Divider11Applications Information (Continued)TL H 11490–16FIGURE 6 ADC Control Logic2 0THE ANALOG INPUTThe analog input of the ADC12062can be modeled as two small resistances in series with the capacitance of the input hold capacitor (C IN ) as shown in Figure 7 The S H switch is closed during the Sample period and open during Hold The source has to charge C IN to the input voltage within the sample period Note that the source impedance of the input voltage (R SOURCE )has a direct effect on the time it takes to charge C IN If R SOURCE is too large the voltage across C IN will not settle to within 0 5LSBs of V SOURCE before the conversion begins and the conversion results will be incor-rect From a dynamic performance viewpoint the combina-tion of R SOURCE R MUX R SW and C IN form a low pass filter Minimizing R SOURCE will increase the frequency re-sponse of the input stage of the converterTypical values for the components shown in Figure 7are R MUX e 100X R SW e 100X and C IN e 25pF The set-tling time to n bits ist SETTLE e (R SOURCE a R MUX a R SW ) C IN n ln (2) The bandwidth of the input circuit isf b 3dB e 1 (2 3 14 (R SOURCE a R MUX a R SW ) C IN )For maximum performance the impedance of the source driving the ADC12062should be made as small as possible A source impedance of 100X or less is recommended A plot of dynamic performance vs source impedance is given in the Typical Performance Characteristics sectionIf the signal source has a high output impedance its output should be buffered with an operational amplifier capable of driving a switched 25pF 100X load Any ringing or instabili-ties at the op amp’s output during the sampling period can result in conversion errors The LM6361high speed op amp is a good choice for this application due to its speed and its ability to drive large capacitive loads Figure 8shows the LM6361driving the ADC IN input of an ADC12062 The 100pF capacitor at the input of the converter absorbs some of the high frequency transients generated by the S H switching reducing the op amp transient response require-ments The 100pF capacitor should only be used with high speed op amps that are unconditionally stable driving ca-pacitive loadsTL H 11490–17FIGURE 7 Simplified ADC12062Input Stage12Applications Information (Continued)TL H 11490–18FIGURE 8 Buffering the Input with an LM6361High Speed Op AmpAnother benefit of using a high speed buffer is improved THD performance when using the multiplexer of the ADC12062 The MUX on-resistance is somewhat non-linear over input voltage causing the RC time constant formed by C IN R MUX and R SW to vary depending on the input voltage This results in increasing THD with increasing frequency Inserting the buffer between the MUX OUT and the ADC IN terminals as shown in Figure 8will eliminate the loading on R MUX significantly reducing the THD of the multiplexed sys-temCorrect converter operation will be obtained for input volt-ages greater than AGND b 50mV and less than AV CC a50mV Avoid driving the signal source more than 300mV higher than AV CC or more than 300mV below AGND If an analog input pin is forced beyond these voltages the cur-rent flowing through that pin should be limited to 25mA or less to avoid permanent damage to the IC The sum of all the overdrive currents into all pins must be less than 50mA When the input signal is expected to extend more than 300mV beyond the power supply limits for any reason (un-known uncontrollable input voltage range power-on tran-sients fault conditions etc )some form of input protection such as that shown in Figure 9 should be usedTL H 11490–19FIGURE 9 Input Protection13Applications Information(Continued)3 0ANALOG MULTIPLEXERThe ADC12062has an input multiplexer that is controlled by the logic level on pin S0when EOC goes low as shown in Figures1and2 Multiplexer setup and hold times with re-spect to the S H input can be determined by these two equationst MS(wrt S H)e t MS b t EOC(min)e50b60e b10ns t MH(wrt S H)e t MH a t EOC(max)e50a125e175ns Note that t MS(wrt S H)is a negative number this indicates that the data on S0must become valid within10ns after S H goes low in order to meet the setup time requirements S0must be valid for a length of(t MH a t EOC(max))b(t MS b t EOC(min))e185ns Table I shows how the input channels are assignedTABLE I ADC12062InputMultiplexer ProgrammingS0Channel0V IN11V IN2The output of the multiplexer is available to the user via the MUX OUT pin This output allows the user to perform addi-tional signal processing such as filtering or gain before the signal is returned to the ADC IN input and digitized If no additional signal processing is required the MUX OUT pin should be tied directly to the ADC IN pinSee Section9 0(APPLICATIONS)for a simple circuit that will alternate between the two inputs while converting at full speed4 0REFERENCE INPUTSIn addition to the fully differential V REF a and V REF b refer-ence inputs used on most National Semiconductor ADCs the ADC12062has two sense outputs for precision control of the ladder voltage These sense inputs compensate for errors due to IR drops between the reference source and the ladder itself The resistance of the reference ladder is typically750X The parasitic resistance(R P)of the package leads bond wires PCB traces etc can easily be0 5X to 1 0X or more This may not be significant at8-bit or10-bit resolutions but at12bits it can introduce voltage drops causing offset and gain errors as large as6LSBsThe ADC12062provides a means to eliminate this error by bringing out two additional pins that sense the exact voltage at the top and bottom of the ladder With the addition of two op amps the voltages on these internal nodes can be forced to the exact value desired as shown in Figure10TL H 11490–20FIGURE10 Reference Ladder Force and Sense Inputs14。

XC6204C30A资料

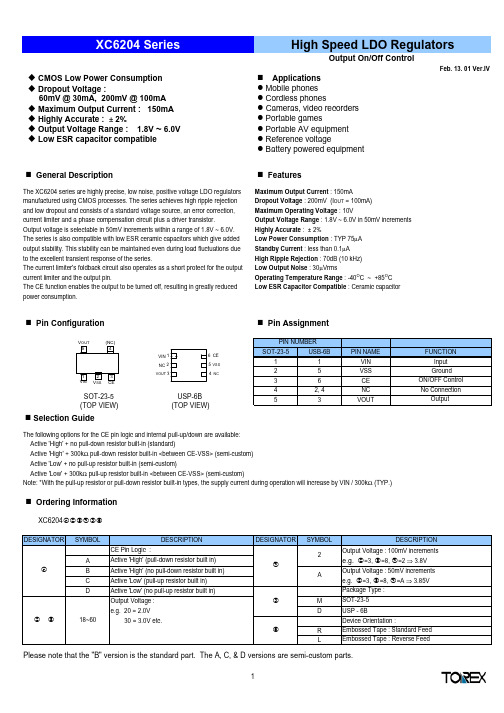

XC6204 Series

! CMOS Low Power Consumption ! Dropout Voltage : 60mV @ 30mA, 200mV @ 100mA ! Maximum Output Current : 150mA ! Highly Accurate : ± 2% ! Output Voltage Range : 1.8V ~ 6.0V ! Low ESR capacitor compatible

see table next page 75 0.3 0.01 2 0.20 10 100 30 70 300 50 1.6 VIN 0.25 0.1 0.1

IOUT=30mA IOUT=30mA -40OC≤Topr≤85OC 300Hz~50kHz IOUT=50mA, f=10kHz

VCE=VIN VCE=VSS

%

M D

"'#

18~60

30 = 3.0V etc.

&

R L

Please note that the "B" version is the standard part. The A, C, & D versions are semi-custom parts.

1

元器件交易网

PARAMETER Output Voltage Maximum Output Current Load Regulation Dropout Voltage Supply Current Standby Current Line Regulation Input Voltage Output Voltage Temp. Characteristics Output Noise Ripple Rejection Rate Current Limiter Short-circuit Current CE "High" Voltage CE "Low" Voltage CE "High" Current CE "Low" Current

FAN6204同步整流芯片应用

385 µ H 60 T

8 T 55 kHz 41 T 6 T 6.8 700 µH 52 kHz

输出

输出电压 (Vo) 输出功率 (Po)

NBOOST 60T D5

100kΩ RHV

41T RCLAMP CCLAMP 51kΩ NP

6T NS

680uF 470uF 470uF 470uF V =19V 25V 25V 25V 25V OUT + 16Ω RSN 36kΩ RRES1 9.1kΩ RRES2 COUT1 COUT2 COUT3 COUT4

V R2 ( IN .MAX VOUT ) 4 R1 R2 n R4 1 VOUT 4 R3 R4

(2) (3)

R4 VOUT 4 R3 R4

的取值为 5~5.5。

再考虑到分压电阻和内部电路的公差,分压比 (K)

K

R2 R4 R1 R2 R3 R4

0.83 V R2 IN .MIN 0.05VOUT 0.3 R1 R2 n

(5)

应该考虑 LPC 和 RES (1~4 V) 的线性工作范围,则 :

V R2 IN .MAX 4 R1 R2 n

(6) (7)

另一方面,需要考虑 LPC 和 RES (1~4 V) 的线性工 作范围,则:

表

2中总结了关键参数。

关键系统参数

表 2.

PFC电路

PFC 输出电压电平 1 (PFCVo1) PFC 输出电压电平 2 (PFCVo2) 250 V 400 V

输入

输入电压范围 电源频率范围 90~264 VAC 47~63 Hz

PFC 电感 (Lb) PFC 电感匝数 (Nb)

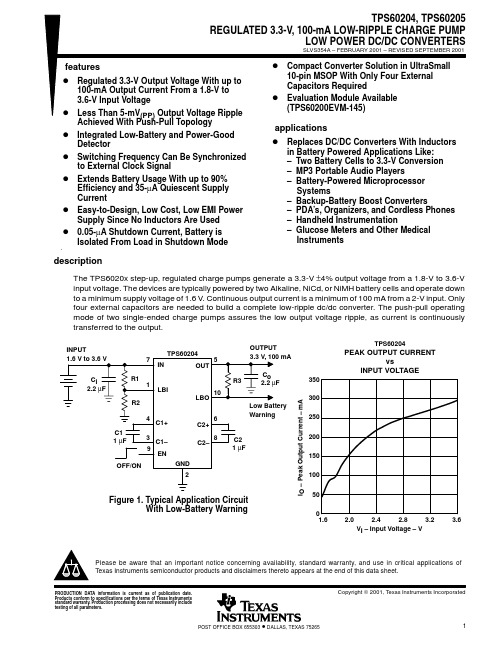

TPS60204资料

Figure 10t – Time – µs12345678910Figure 1150100150200250300350400450500V OENI It – Time – µsV I = 2.4 VFigure 12LOAD TRANSIENT RESPONSE100 mA10 mA501001502002503003.263.283.303504004505003.24t – Time – µsV I = 2.4 V012345678910t – Time – msFigure 13元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. To minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third–party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Mailing Address:Texas InstrumentsPost Office Box 655303Dallas, Texas 75265Copyright 2001, Texas Instruments Incorporated。

MBI6024 Preliminary Datasheet V2.00-EN

6F-4, No.18, Pu-Ting Rd., Hsinchu, Taiwan 30072, R.O.C.Sink Driver for LED StripsFeaturesz 3x4-channel constant-current sink driver for LED strips z Constant current range: 3~45mAz 3 groups of output current, each group is set by an external resistor z Sustaining voltage at output channels: 17V (max.) z Supply voltage 3V~5.5VzEmbedded 16-bit PWM generator- Gray scale clock generated by the embedded oscillator - S-PWM patented technologyz Two selectable modes to trade off between image quality and transmission bandwidth- 16-bit gray scale mode (with optional 8-bit dot correction) - 10-bit gray scale mode (with optional 6-bit dot correction)z Reliable data transmission- Daisy-chain topology- Two-wire transmission interface - Phase-inversed output clock- Built-in buffer for long distance transmission zFlexible PWM reset modes - Auto-synchronization mode - Manual-synchronization mode z RoHS-compliant packagesApplicationz LED strips z Mesh display z Architectural lightingProduct DescriptionMBI6024 is a 3x4-channel, constant-current, PWM-embedded sink driver for LED strips. MBI6024 provides constant current ranging from 3mA to 45mA for each output channel and are adjustable with three corresponding external resistors. Besides, MBI6024 can support both 3.3V and 5V power systems and sustain 17V at output channels.With Scrambled-PWM (S-PWM) technology, MBI6024 enhances pulse width modulation by scrambling the “on” time into several “on” periods to increase visual refresh rate at the same gray scale performance. Besides, the gray scale clock (GCLK) is generated by the embedded oscillator. Moreover, MBI6024 provides two selectable gray scale modes to trade off between image quality and transmission: 16-bit gray scale mode and 10-bit gray scale mode. The 16-bit gray scale mode provides 65,536 gray scales for each LED to enrich the color. Subject to the 16-bit gray scale mode, the 8-bit dot correction may adjust each LED by 256-step gain to compensate the LED brightness. Furthermore, the 10-bit gray scale mode provides 1,024 gray scales. Subject to the 10-bit gray scale mode, 6-bit dot correction may adjust each LED by 64-step gain.In addition, MBI6024 features a two-wire transmission interface to make cluster-to-cluster connection easier. To improve the transmission quality, MBI6024 provides phase-inversed output clock to eliminate the accumulation of signal pulse width distortion. MBI6024 is also flexible for either manual-synchronization or auto-synchronization. The manual-synchronization is to maintain the synchronization of image frames between ICs. The auto-synchronization is to achieve accurate gray scale, especially when using the built-in oscillator.2413V R-EXTA R-EXTCOUTAn OUTBnMBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsSymbo l tSU tHD tPHL1 tPHL2 tPHL3 tPHL4 tPHL5 tPHL6 tPLH3 tPLH4 tPLH5 tPLH6 tw(I) tWDM tOR tOR1 tOF tOF1 FCKI FOSC VLED=4V VDS=1.0V VIH=VDD VIL=GND IOUT=20mA RL=150Ω CL=10pF C1=4.7uF C2=0.1uF C3=4.7uF CCKO=8pF CSDO=8pFSwitching Characteristics (VDD=3.3V, Ta=25°C)Characteristics Setup Time Hold Time SDI–CKI↓ CKI↓–SDI CKI↑–CKO↓ CKI↓–SDO↑↓ GCLK↑– OUTB0 , OUTA1 , Propagatio n Delay Time (“H” to “L”)OUTB2 ↓ConditionMin. 7.5 7.5 32 40 48 56 32 40 48 56 20 38 3.0 12.0 3.0 30.0 0.2 -Typ. 50 38 40 48 56 64 40 48 56 64 6.0 18.0 6.0 35.0 24.0Max. 48 56 64 72 48 56 64 72 9.0 24.0 9.0 40.0 10 -Unit ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns MHzGCLK↑– OUTC1 , OUTA3 ,OUTC3↓ ↓GCLK↑– OUTA0 , OUTC0 ,OUTA2GCLK↑– OUTB1 , OUTC2 , OUTB3 ↓ GCLK↑– OUTB0 , OUTA1 ,OUTB2 ↑Propagatio n Delay Time (“L” to “H”)GCLK↑– OUTC1 , OUTA3 ,OUTC3↑ ↑GCLK↑– OUTA0 , OUTC0 ,OUTA2GCLK↑– OUTB1 , OUTC2 , OUTB3 ↑ Pulse Width Minimum Pulse Width of PWM Rise Time CKI*OUTAn ~ OUTCnCKO/SDOOUTAn ~ OUTCnFall TimeCKO/SDOOUTAn ~ OUTCnCKI* Frequency Internal Oscillator*The maximum frequency may be limited by different application conditions. Please refer to the application note for details.- 11 -October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsTest Circuit for Electrical / Switching Characteristics- 12 -October 2011, V2.00MBI6024Timing WaveformPWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsSignal Input and Output with Phase-inversed Output ClockOutput Timing- 13 -October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsPrinciple of OperationMBI6024 provides SPI-like interface (CKI, SDI), a two-wire transmission interface, to address the data, so that MBI6024 receives the data directly without a latch command. The sequence of operation should follow the steps below: Step 1. Set the configuration register Step 2. Send the dot correction data Step 3. Send the gray scale data MBI6024 receives the data packet containing targeted gray scale (GS) data from the controller, and turns on the output channels according to the gray scale data. The gray scale clock of PWM generator, GCLK, is generated by the embedded oscillator.Control Interface: SPI-Like Interface (CKI, SDI)MBI6024 adopts the SPI-like interface (CKI/SDI). By SPI-like interface, MBI6024 samples the data (SDI) at the falling edge of the clock (CKI).The following waveforms is the example of the SPI-like interface.Phase-inversed Output Clock MBI6024 enhances the capability of cascading MBI6024 by phase-inversed output clock function. By phase-inversed output clock, the clock phase will be inversed from CKI to CKO to eliminate the accumulation of the pulse width deviation. This improves the signal integrity of data transmission. The following chart illustrates the phase-inversed output clock results.Original: CKI1 Original: CKO1 Phase-Inverse Clock I:CKO2 Phase-Inverse Clock II: CKO3- 14 -October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsThe Structure of Data PacketMBI6024’s data packet contains three parts: 1. Prefix: The prefix is a symbol of “Silent-to-Reset”, i.e. a time period for MBI6024 to distinguish two data packets. During the prefix, both CKI and SDI should be tied-low and stop for more than 172 CKI cycles. 2. Header: The header defines the cascaded IC numbers and also contains a command to decide the data type. 3. Data: This is the data for each IC. It may be gray scale data, dot correction data, or configuration data. Structure of a data packet:PrefixHeaderData- 15 -October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsSetting the Data Types by the CommandMBI6024 provides six kinds of commands and input data types shown as the table below: Command H[5:0] 6’b11 1111 6’b10 1011 6’b11 0011 6’b10 0111 6’b10 0011 6’b11 0111 Data Type 16-bit gray scale data 10-bit gray scale data 8-bit dot correction data 6-bit dot correction data 16-bit configuration data 10-bit configuration dataOnce MBI6024 receives the SDI=1 (1’b1), MBI6024 will start to check if the data is a valid command or not. If the 6-bit data is a valid command, the driver will latch the specific data according to the protocol. If the 6-bit data is not a valid command, MBI6024 will wait for another SDI=1 (1’b1) to check the validity of the next command. Time-Out Reset for Transmission Abort Time-out reset is to prevent ICs from misreading during the data transmission. If the CKI is tied-low for more than 95 CKI cycles, MBI6024 may identify the wires as disconnection. To prevent from misreading, MBI6024 will ignore the present input data and continuously show the previous image data until the next image data is correctly recognized. The Prefix in the Beginning of a Data Packet MBI6024 identifies the data as a new data packet after time-out, so the prefix in the beginning of a data packet should be more than 172 CKI cycles. If both CKI and SDI are tied-low and stop for more than the setting of CKI time-out period, MBI6024 will start to check the valid command of the next data packet. The prefix between two data packets helps MBI6024 identify the data packet correctly. The following timing diagram illustrates the interval between two data packets in 16-bit gray scale mode.The prefix > 172 CKI cycles- 16 -October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsDefinition of Configuration RegisterMBI6024 provides two configuration register sections: configuration register 1 (CF1) and configuration register 2 (CF2) as defined in the tables below.Configuration Register 1 (CF1):MSB Bit Default Value 9 10 8 7 0 6 11 5 4 1 3 1 2 11 1 LSB 0 0Note: Bit [15:10] should be set as “0” to avoid signal misjudgment. Bit Definition Value 11 9:8 GCLK frequency 10 (default) 01 00 7 6:5 4 Dot correction mode Reserved PWM counter reset PWM data synchronization Phase-inversed output clock Parity check 0 (default) 1 11 (default) 1 (default) 0 1 (default) 0 11 (default) 1 0 (default) Function GCLK=frequency of internal oscillator, i.e. 24MHz (typical). GCLK=oscillator frequency divided by two, i.e. 12MHz (typical). GCLK=oscillator frequency divided by four, i.e. 6MHz (typical). GCLK= oscillator frequency divided by eight, i.e. 3MHz (typical). enable dot correction, bypass dot correction Must fill in ‘11’ Reset PWM counter after programming configuration register Do not reset PWM counter after programming configuration register Automatic synchronization Manual synchronization The waveform is inversed from CKI to CKO; please set the two bits as 2b’11. Other combinations are reserved for internal tests. Enable Disable32:10- 17 -October 2011, V2.00MBI6024GCLK FrequencyPWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsMBI6024 provides four kinds of internal GCLK frequency, which is the internal oscillator frequency divided by 1, 2, 4, and 8, for different applications according to the bits of CF1[9:8]. The internal oscillator frequency is 24MHz (typ.); e.g. if the internal oscillator frequency is divided by 8, the GCLK frequency is 3MHz. Higher GCLK frequency provides higher visual refresh rate, but also higher EMI. If the output current is larger than 40mA, the GCLK frequency is suggested to be lower than 8MHz to keep good linearity at low gray scale level. Dot Correction Mode MBI6024 also provides 8-bit or 6-bit dot correction in 16-bit or 10-bit gray scale mode respectively. Dot correction control helps compensate LED brightness and reduces the loading of calculation in controllers. In addition, with the built-in multiplier, MBI6024 operates dot correction without sacrificing the visual refresh rate. PWM Counter Reset MBI6024 can optionally reset the PWM counter by setting the bit of CF1[4] after programming configuration register. The default setting is to reset the PWM counter to start a new PWM cycle to align the PWM output data for new setting. PWM Data Synchronization MBI6024 is also flexible for either manual-synchronization or auto-synchronization by setting the bit of CF1[3]. For auto-synchronization, the bit of CF1[3] is set to “1” (default). MBI6024 will automatically process the synchronization of previous data and next data for PWM counting. The next image data will be updated to output buffers and start PWM counting when the previous data finishes one internal PWM cycle. For manual-synchronization, the bit of CF1[3] is set to “0”. Once the next input data is correctly recognized, MBI6024 will stop the present PWM cycle and restart a new PWM cycle to show the new data immediately. The advantage of manual-synchronization is to maintain the synchronization of image frames between ICs, but the PWM cycle may not be finished, so the gray scale accuracy is slightly affected. Since S-PWM scrambles the 16-bit PWM cycle into 64 small periods, the gray scale accuracy remains good. For better gray scale performance, auto-synchronization keeps accurate gray scale especially when using the built-in oscillator, but the drawback is the synchronization of image frames between ICs. Parity Check Parity check is to check the data in the header for any error, especially to prevent the configuration register and dot correction register from miswriting.- 18 -October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsConfiguration Register 2 (CF2):Default Value MSB Bit Value 2 1 111 LSB 0Note: Bit [15:3] should be set as “0” to avoid signal misjudgment. Bit 2 1:0 Definition Reserved Reserved Value 1 (default) 11 (default) Function Must fill in ‘1’ Must fill in ‘11’16-bit Configuration DataFor 16-bit configuration data, each word is 16 bits. Each MBI6024 needs 3 words (3x16=48 bits) for the configuration data. However, each configuration data has only 10 bits, and the MSB 6 bits of each word are invalid. Prior to the configuration data, there is a 48-bit header. MBI6024 provides parity check function to check the count of bit to prevent the data transmission error. The data format is shown below:Prefix Both CKI and SDI should be tied-low and stop for more than 172 CKI cycles. 48-bits header Bit Definition 47:42 H[5:0] 41:32 A[9:0] 31:26 25:16 H[5:0] L[9:0]Value 100011 0000000000 100011 N-1 N=Number of IC in seriesFunction The command of 16-bit configuration data Address data. Always send 10’b 0000000000 Double check the command. It should be the same as the prior H[5:0], otherwise the data packet will be ignored. Set the number of IC in series P[3:0] are parity check bits, If it is incorrect, the data packet will be ignored. P[0] is the parity check bit of L[9:0] P[0]=1 if the count of “1” within L[9:0] is odd; P[0]=0 if the count of “1” within L[9:0] is even.15:12P[3:0]0000~1111P[1] is the parity check bit of A[9:0] P[1]=1 if the count of “1” within A[9:0] is odd; P[1]=0 if the count of “1” within A[9:0] is even. P[2] is the parity check bit of H[5:0] P[2]=1 if the count of “1” within H[5:0] is odd; P[2]=0 if the count of “1” within H[5:0] is even. - 19 October 2011, V2.00MBI6024PWM-Embedded 3x4-Channel Constant-Current Sink Driver for LED StripsP[3] is the parity check bit of P[2:0] P[3]=1 if the count of “1” within P[2:0] is odd; P[3]=0 if the count of “1” within P[2:0] is even.11:10 9:0X1[1:0] L[9:0]XX N-1 N=Number of IC in seriesDon’t care. The value is suggested to be “0”. Double check the number of IC in series48-bit configuration data Bit Definition Value Function X2[5:0] are “don’t care” bits. The value is suggested to be “0”. CF1N[9:0] are 10 bits data of configuration register 1 (CF1). The 2nd 47:0 X2[5:0]~CF1N[9:0]~ X2[5:0]~CF1N[9:0]~ X3[12:0]~CF2N[2:0] CF1[9:0] double checks the data of configuration register bank 1 48b’0~48b’1 (CF1). It should be the same as the 1st CF1N[9:0]; otherwise the data will not be written into register. X3[12:0] are “don’t care” bits. The value is suggested to be “0”. CF2N[2:0] are 3 bits data of configuration register 2 (CF2) The configuration data of the last IC is sent first, followed by the previous ICs, and the first IC’s configuration data is sent in the end of the packet.- 20 -October 2011, V2.00PrefixBoth CKI and SDI should be tied-low and stop for more than 172 CKI cycles.30-bit headerBit Definition Value FunctionThe command of 10-bit configuration dataBoth CKI and SDI should be tied-low and stop for more than 172 CKI cycles. 48-bit headerBit DefinitionBoth CKI and SDI should be tied-low and stop for more than 172 CKI cycles. Bit DefinitionAccording to the above equation, the following table shows the examples:The ratio of output turn-on time1/256 x gray scale data2/256 x gray scale dataAccording to the above equation, the following table shows the examples:The ratio of output turn-on time1/64 x gray scale data2/64 x gray scale dataBoth CKI and SDI should be tied-low and stop for more than 172 CKI cycles. Bit DefinitionBoth CKI and SDI should be tied-low and stop for more than 172 CKI cycles. 30-bits headerBit DefinitionMBI6024GP Outline DrawingMBI6024GFN Outline Drawing (Max) (Max)Note 1: The unit for the outline drawing is mm.DisclaimerMacroblock reserves the right to make changes, corrections, modifications, and improvements to their products and documents or discontinue any product or service. Customers are advised to consult their sales representative for the latest product information before ordering. All products are sold subject to the terms and conditions supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. Macroblock’s products are not designed to be used as components in device intended to support or sustain life or in military applications. Use of Macroblock’s products in components intended for surgical implant into the body, or other applications in which failure of Macroblock’s products could create a situation where personal death or injury may occur, is not authorized without the express written approval of the Managing Director of Macroblock. Macroblock will not be held liable for any damages or claims resulting from the use of its products in medical and military applications.Related technologies applied to the product are protected by patents. All text, images, logos and information contained on this document is the intellectual property of Macroblock. Unauthorized reproduction, duplication, extraction, use or disclosure of the above mentioned intellectual property will be deemed as infringement.。

F24-60软件使用说明书

後再執行讀取動作。.

1.將 F24-60 軟體燒錄線接到發射或接收機。 2.按下“讀取設定”。 3.完成後按下“確定” 鍵即可。

3

燒錄新設定至遙控器 *使用軟體讀取/燒錄發射機或接收機時,請確實關閉電源或取出電池 後再執行讀取動作。

1.將 F24-60 軟體燒錄線接到發射或接收機。 2.按下”燒錄設定” 。 3.完成後按下”確定”鍵即可。

關閉/離開 F24-60 程式 如需關閉程式,按下離開鍵即可。

子有

电

鼎

禹

海

上

4

I. 繼電器數量

選擇發射機上各動作如按鍵﹐選擇開關及搖桿使用之繼電器數量

(1) 選擇 RS232/USB 所在使用中的 COM (2) 按下“讀取設定”(需等待數秒鐘) (3) 讀取完畢後,選擇需更改的動作之繼電器數量(選取 0 當不選用該動作) (4) 選擇完畢後,按“下一頁”

功能需在發射器為「持續發射」模式才有效,「不持續發射」時放開按

有 鍵即不耗電,故不需設定。

發射機停用關機 LED 燈 亮燈/關燈

有效/無效﹕當選擇有效時是指發射機有一段時間未操作而進入停用

子 省電前,會發射急停信號使接收機進入關機狀態。

是指正常操作中發射機指示燈是否亮起當選擇 LED 燈“關燈”時,操作

司 出

(2) 更改完畢後按“下一頁”

公 (3) 重複以上程序直到 4 個軸向設定完畢 限 注意 (a) 如設定中有需回上一頁做更改,任何時間可以按“上一頁” 回到所需更改的

有 頁面。

(b) 參考附件 I 關於加速延遲,抑制延遲及吋動功能設定解釋。

子 (c) 根據第一頁裡(繼電器數量)裡所設定每一個軸向繼電器數量,其可用之繼電器 將會顯 电 鼎 禹 海

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

外部器件设计

(a) 反激整流的应用 如图 1 所示, LPC和RES管脚的电阻需要根据LPT 控制 进行适当设计。根据图3,当LPC端电压在一个消隐时 序( tLPC-EN )内高于 VLPC-EN 时, SR 的栅极准备输出。 当 LPC 端电压跌落到低于 VLPC-TH-HIGH (0.05VOUT) 时, SR MOSFET 开始输出。因此, VLPC-EN 必须高于 VLPCTH-HIGH ,否则 SR MOSFET 不能导通。所以, LPC 端的 电压分压器R1和R2, 应该满足下式:

VIN .MIN VO ) R1 R2 n 30.4 2 VO R2 0.3 40 根据方程(2)可以得到LPC的分压比的最小值为: 0.83 (

R1 R2 R2 ( VIN .MAX VOUT ) n 24.4 4

R2

Clamping circuit could be a voltage regulator or voltage clamping components

1 R3 R4 19 VO 3.8 4 R4 4.96

因此,R3和R4分别选为36kΩ和9.1kΩ。

© 2011 Fairchild Semiconductor Corporation Rev. 1.0.0 • 7/29/11

3

AN-6204

VLPC

VLPC-HIGH 0.83VLPC-HIGH 0.05VOUT

T

Figure 4.

VIN/n VIN/n+VOUT VOUT

采用FAN6204时正激续流整流的典型波形

VLPC

VLPC-HIGH 0.83VLPC-HIGH 0.05VOUT

Blanking time

Figure 3. 采用FAN6204时QR反激变换器的典型波形

V R2 0.83 ( IN .MIN VOUT ) 0.05VOUT 0.3 R1 R2 n

(1)

(b) 双管正激式续流整流的应用 图2给出了一种将FAN6204应用于正激续流二极管整流 的典型应用电路。由于VLPC-EN 必须大于 VLPC-TH-HIGH, 因此LPC端的电压分压器R1和R2,需要满足下式:

Table 1. 系统指标 输入 输入电压范围 电源频率范围 输出 输出电压(Vo) 输出功率(Po) 19V 90W 90~264VAC 47~63Hz

根据设计指南,计算出关键参数,并在表 2 中给予总 结。

Table 2. 关键系统参数 PFC 部分 PFC输出电压电平1 (PFCVo1) PFC 输出电压电平 2 (PFCVo2) PFC 电感量 (Lb) PFC 电感匝数(Nb) 副边绕组匝数 (NAUX) 最小开关频率 (fs,min,PFC) PWM部分 PWM 变压器原边电感匝数(NP) PWM 变压器副边绕组匝数(NAUX) PWM 变压器的匝比 (n) 原边电感 (LP) 最小开关频率(fs,min,PWM) 41T 6T 6.8 700µ H 52kHz 250V 400V 385µ H 60T 8T 55kHz

(4)

由 于 RES 和 LPC 之 间 的 分 压 比 ( Voltage Scale-Down Ratio)(K)是5,所以CT (tCT.DIS) 的放电时间和电感 电流的放电时间( tL.DIS )相等。然而,考虑到分压电 阻和内部电路的公差,为了保证tCT.DIS小与tL.DIS,分压 比(Scale-Down Ratio) (K )应该大于5。K的典型值为 5~5.5。

AN-6204

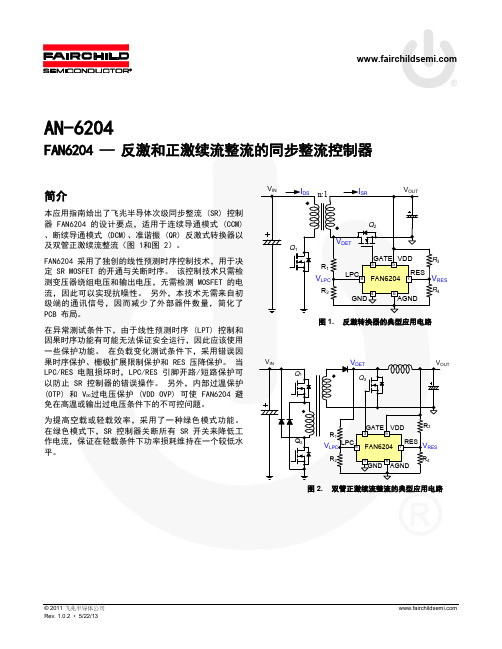

FAN6204 — 反激和正激续流整流的同步整流控制器

引言

本应用手册给出了飞兆半导体次级同步整流控制器 ( SR ) FAN6204 的 设 计 要 点 , 适 用 于 连 续 导 通 模 式 (CCM)、断续导通模式(DCM)、准谐振(QR)反 激式变换器以及双管正激续流整流(图1和图2)。 FAN6204采用了独创的线性预测时序控制技术,用于决 定 SR MOSFET 的开通与关断时序。该控制技术只需检 测变压器绕组电压和输出电压,无需检测 MOSFET的电 流,因此可以实现抗噪性。另外,本技术无需来自原边 的通讯信号,因而减少了外部器件数量,简化了PCB布 局。 在异常测试条件下,由于线性预测时序(LPT)控制和 因果時序功能 (Causal Function) 有可能无法保证安全运 行,因此应该使用一些保护功能。在负载变化的测试条 件 下 , 本芯片使用了错误因果时序保护 (Fault Causal Timing Protection) 、栅極扩展限制保护( Gate Expand Limit Protection ) 和 RES 瞬 降 保 护 ( RES Dropping Protection )。当LPC/RES电阻损坏时,LPC/RES管脚悬 浮 / 短接保护可以防止 SR 控制器的错误操作。另外,内 部过温度保护( OTP )和 VDD 过电压保护(VDD OVP ) 可使FAN6204避免在高温和输出过电压条件下的不可控 问题。 本芯片使用了一种绿色模式功能来提高空载和轻载下的 效率。在绿色模式下, SR 控制器关断 SR 的驱动电路来 降低工作电流,保证在轻载条件下功率损耗维持在一个 较低水平。

(2)

R4 VOUT 4 R3 R4

(7)

再考虑到分压电阻和内部电路的公差,分压比 (ScaleDown Ratio)K的取值为5~5.5。

R4 1 VOUT 4 R3 R4

K

(3)

R2 R4 R1 R2 R3 R4

Body diode of SR MOSFET Body diode of SR MOSFET Primary MOSFET

4

RES

VRES

R4

GND

6

AGND

Figure 2. 双管正激续流整流的典型应用电路

© 2011 Fairchild Semiconductor Corporation Rev. 1.0.0 • 7/29/11

AN-6204

APPLICATION NOTE

( 设计范例 ) 假设在一反激系统中的输入线电压的最

VDD部分 当输出端电压VO控制在5V和24V之间时,可以将VO用 作 FAN6204 的 VDD 。如果 VO 不在这个范围,则可使用 变压器的一个额外绕组给VDD提供能量。图5给出了电 路简图。为了阻止 VDD 电源电压的变化,可以使用稳 压器或者电压钳位元件,比如使用稳压二极管将 VDD 钳位在一个适当的范围。

VOUT

Q2 Q1 D1

R1

LPC 8 8 5 5 VDD 3 3 GATE RES 7 7

R3

Clamping Circuit

FAN6204 FAN6204

4 4 6 6

大值( VIN.MAX )和最小值( VIN. Min )分别为373V 和 127V ;输出电压是 19V ;变压器匝比(n )是4.75 。 根据方程(1)可以得到LPC的分压比最大值为:

NBOOST 60T D5

100kΩ RHV

41T RCLAMP CCLAMP 51kΩ NP

6T NS

0.83 V R2 IN .MIN 0.05VOUT 0.3 R1 R2 n

(5)

应该考虑LPC和RES(1~4V)的线性工作范围,则:

V R2 IN .MAX 4 R1 R2 n

(6)

另一方面,需要考虑 LPC 和 RES ( 1~4V )的线性工作 范围,则:

V R2 ( IN .MAX VOUT ) 4 R1 R2 n

Q1 R1

VIN

IDS

n:1

ISR

VOUT

Q2

VDET

GATE VDD

3 5

R3

VLPC

R2

LPC

8

FAN6204

4 6

RES

7

VRES

R4

GND

AGND

Figure 1. 反激式变换器的典型应用电路

VIN Q1

VDET

Q3

VOUT

GATE VDD Q2 R1 R2

3 5 7

R3

VLPC LPC 8 FAN6204

4

AN-6204

APPLICATION NOTE

设计范例

本节给出了采用 FAN6921 时 90W ( 19V/4.74A )适配器 的 设 计 实 例 。 PFC 输 出 电 压 在 低 输 入 交 流 电 压 时 为 250V ,高输入交流电压时为 400V 。根据技术规格,所 有的关键器件都经过了处理,并且给出了最终的实验结 果。

VGS

Primary MOSFET Synchr onous Rectifier MOSFET

VDET

R2 R4 K R1 R2 R3 R4

Body diode of SR MOSFET Body diode of SR MOSFET

VIN/n

(4)

VOUT

VGS

Primary MOSFET Synchr onous Rectifier MOSFET

APPLICATION NOTE

印刷电路板的布局

图6 给出了 FAN6204 在某一变换器中的原理图。良好的 PCB布局可以提高电源系统效率、最大限度抑制EMI, 并且防止电源在浪涌/静电释放试验中的损坏。 IC侧: LPC和RES管脚的参考地直接连接到IC的AGND。 (轨迹1) IC 的 GND 和 AGND 管脚应该通过一条短粗的布线 或者较宽区域的布线连在一起。(轨迹 1 和轨迹 2) VDD 的参考地应该连接到 IC的这个接地区域,然 后VDD的参考地连接到COUT的地。(轨迹3) LPC和RES的布线应该远离磁性元件。 系统侧: 由于轨迹4是二次侧的功率环路,因此越短越好。 在次级,Y-CAP应该通过一条粗线连接到COUT的 地(轨迹5)。