第5章 集成触发器

基本R-S触发器

RD

SD

Qn

Qn+1

000

1

001

1

010

0

011

0

100

1

101

1

11001111来自禁止态 置0 置1 保持

5.2 基本R-S触发器

2 次态卡诺图

3 特征方程

SD RD Qn 00

0

01 11 10 100

1 1 1 0

Q n1 S D RD Q n

R D SD 1 (约束条件)

55..22基基本本RSR触-发S触器发器

数字电路与逻辑设计

第5章 集成触发器

5.1 概述

1.触发器的定义

时序逻辑电路的最基本单元;能够存储一位二进制信息。

2.触发器特点:

(1)有两个能够自行保持的稳定状态,分别用来表示逻辑0和 逻辑1; (2)根据不同时输入信号可以置成0态和1态。

5.1 概述

3.触发器分类

基本R-S触发器

电路结构和 动作特点

钟控触发器 主从触发器

边沿触发器

逻辑功能

R-S触发器 D触发器 J-K触发器 T触发器

5.2 基本R-S触发器

5.2.1 基本R-S触发器的电路组成和工作原理

1. 电路结构

G1

SD

&

Q

G2

&

输入端

RD

Q

输出端

以Q端的状态表示触发器状态:Q=1即触发器为状态1 Q=0即触发器为状态0

4

5.2 基本R-S触发器

2. 工作原理

1)当RD 0 , SD 1时 , 则Q 0 , Q 1 ——0态 触发器置0

1 G1

SD

电子教案《数字电子技术(第5版_杨志忠)》教学资源第5章练习题参考答案

电压波形。

图 P5 2

图[题 ] 图[题 ]

5 2 A

5 2 B

[题 5 3] 在同步 RS 触发器中,已知 CP、R、S 输入的电压波形如图 P5 3 所示,试画出

输出 Q 端的电压波形。设触发器的初始状态为 Q =0。

[解] 根据由与非门组成同步 RS 触发器的逻辑功能画输出 Q 的电压波形。Q 电压波形中

[解] 先画出 、 Q0 Q0 和 、 Q1 Q1 的电压波形,再根据 Y1 = Q0 Q1 和 Y2 = Q0 Q1 的与非关系,

画出输出 Y1 和 Y2 的电压波形,如图[题 5 14]所示。

图 P5 14

图[题 5 14]

第 5 章 集成触发器 127

[题 5 15] 图 P5 15 是一个用 TTL 边沿双 JK 触发器组成的单脉冲发生器,CP 为连续脉 冲,试分析其工作原理,并画出 uO 的电压波形图。 [解] 由图 P5 15 可知,平时 S 开关接地,FF0 的 J0 接地,同时 K0 = ,1 FF1 的直接置 0 端通过 S 开关接地。因此,触发器 FF0 和 FF1 都处于 0 状态,Q0 = Q1 = 0,输出 uO 为低电平 0。 当 S 开关按下时,接高电平 1,这时 FF0 和 FF1 都为 T′触发器,处于计数状态。在 CP 下 降沿作用下,FF0 由 0 状态翻到 1 状态,Q0 = 1,输出 uO 由低电平 0 跃到高电平 1。 当输入下一个 CP 的下降沿时,FF0 由 1 状态翻到 0 状态,Q0 输出一个负跃变,输出 uO 由高电平 1 跃到低电平 0,与此同时,Q0 输出的负跃变使 FF1 由 0 状态翻到 1 状态,Q1 输出 的低电平使 FF0 置 0,从而保证了 S 开关每按一次,uO 输出一个正脉冲,输入和输出电压波形 如图[题 5 15]所示。 当 S 开关放开时,S 又接地,FF0 和 FF1 又回到初始的 0 状态,为下一次输出正脉冲做好准备。

实验五集成触发器

Qn=1 说明

且每次测试时都要将

0→1

触发器异步清零或置1。

0 0 1→0

按照右表测试并记录结果。

(c)将J、K触发器

0

接成 T’触发器。

CP接1kHz连续脉冲;

1

通过示波器双踪观察

CP和Q的波形,

1

画图并分析结果。

0→1

1 1→0

0 0→1

1→0

1

0→1

1→0

实验五 触发器

4. 实验内容及要求

(2)测试双D触发器74LS74的逻辑功能。

Q

Q

1J C1 1K J CP K SD

74LSll2双JK触发器引脚排列及逻辑符号

实验五 触发器

实验五 触发器

(3)D触发器

可用作数字信号的寄存、移位寄存、分频和波形发生等。

Q n+1 = D

14 13 12 11 10 9 8

Vcc 2RD 2D CP SD 2Q 2Q

74LS74

Q

Q

C1 1D

(5)单脉冲发生器实验 (选做) 用74LS74双D型触发器,设计一个单发脉冲发生器的实验线路。要

求将频率为1Hz的信号脉冲和手控触发脉冲分别作为两个触发器的CP 脉冲输入。只要手控脉冲送出一个脉冲,该脉冲与手控触发脉冲的时 间长短无关。

实验五 触发器

试问:能实现单发脉冲输出的原理是什么?画出电路的输出时序波形图. 下图是用双JK触发器组成的单发脉冲发生器,以供设计时参考。

实验五 触发器

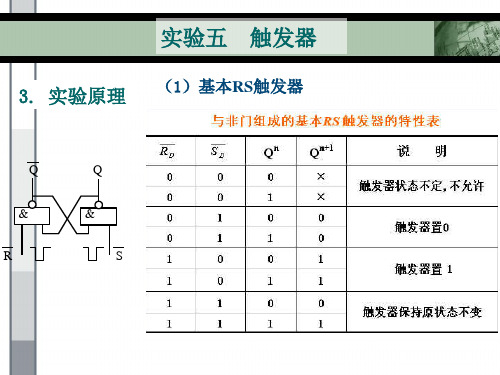

3. 实验原理 (1)基本RS触发器

Q & R

Q &

S

实验五 触发器

(2)JK触发器

常用作缓冲存储器、移位寄存器和计数器。 Qn+1 = JQn + KQn

数电第5章

第五章 触 发 器

图 5 – 7 由与非门构成的基本RS触发器

第五章 触 发 器

1. 功能描述 (1) 当Rd=1, Sd=0时,不管触发器原来处于什么状态, 其次态一定为“1”,即Qn+1=1,故触发器处于置位状态。 (2) 当Rd=0, Sd=1时,Qn+1=0,触发器处于复位状态。 (3) 当Rd=Sd=1 时,触发器状态不变,处于维持状态, 即Qn+1=Qn。 (4) 当Rd=Sd=0 时,Qn+1=Q n+1=1,破坏了触发器的正常 工作,使触发器失效。而且当输入条件同时消失时,触发 器是“0”态还是“1”态是不定的,这种情况在触发器工作 时是不允许出现的。因此使用这种触发器时, 禁止 Rd=Sd=0出现。

发生的。这种电路中没有统一的时钟脉冲。任何输入信

号的变化都可能立刻引起异步时序电路状态的变依从关系来分,又可分为米里 (Mealy)型和莫尔(Moore)型两类。米里型电路的输出是输 入变量及现态的函数,即

F (t ) f [ x(t ),Qn (t )]

器和JK触发器。在基本RS触发器的基础上, 加两个与非

门即可构成钟控RS触发器, 如图 5-10 所示。

第五章 触 发 器

图 5 – 10 钟控RS触发器

第五章 触 发 器

1. 功能描述 当CP=0时,触发器不工作,此时C、D门输出均为 1, 基本RS触发器处于保持态。此时无论R、S如何变化,均 不会改变C、D门的输出,故对状态无影响。 当CP=1 时,触发器工作,其逻辑功能如下: R=0, S=1, Qn+1=1,触发器置“1”; R=1, S=0, Q n+1=0,触发器置“0”; R=S=0, Qn+1=Qn,触发器状态不变; R=S=1, 触发器失效,工作时不允许。

第5章 触发器

表5-1 或非门组成的基本RS触发器的真值表

R

பைடு நூலகம்

S

Q

Q

不变 0 1 0*

触发器 状态 保持 置1 置0 不定

0 0 1 1

0 1 0 1

不变 1 0 0*

7

对于图5-1(b),可作同样分析。这种触发器是以 低电平作为输入有效信号的,在逻辑符号的输入端用小 圆圈表示低电平输入信号有效,它的真值表如表5-2所示。 由于S=R=0时出现了Q==1的状态,而且当S和R同时 撤去(变到1)后,触发器的状态将不能确定是1还是0。 因此这种情况也应当避免。

18

图5-5 开关触点抖动消除电路 图5-5不仅可以消除开关的抖动,而且从波形可以看出,此电路还可 作为手动单次脉冲产生电路使用,譬如可以应用在数字电路实验设备中。

19

5.2 D触发器

导读: 导读 在这一节中,你将学习: 在这一节中,你将学习: 电平触发与边沿触发的概念 电平触发D触发器的特点与逻辑功能 电平触发 触发器的特点与逻辑功能 边沿触发D触发器的特点与逻辑功能 边沿触发 触发器的特点与逻辑功能 异步清0与异步置 与异步置1 异步清 与异步置 集成D触发器 触发器74LS74 集成 触发器

10

2.集成基本RS触发器 .集成基本 触发器 触发器74LS279

集成基本RS触发器74LS279的内部包含4个基 本RS触发器,输入信号均为低电平有效,其逻辑符 号和引脚图如图5-3所示,应该注意的是图中有两个 基本RS触发器具有两个输入端S1和S2,这两个输入 端的逻辑关系为与逻辑,每个基本RS触发器只有一 个Q输出端。

21

图5-6 D触发器

22

R=D

当CP=1时,将 S = D ,R = D ,代入钟控RS 时 代入钟控 触发器的特性方程( ),即得到 触发器的特性方程(5.2.1),即得到 触发器的特 ),即得到D触发器的特 性方程为: 性方程为:

第五章 触发器

图5.5.2 带异步置位、复位端的CMOS边沿触发器

CMOS边沿触发器的特性表

CP

D

Q

n

Q n 1

0 0

0

0 0

1

0

1 1

1 1

1

(4-33)

二、维持阻塞触发器 1、阻塞RS触发器

S

①置1 维持 线

1

0

S’

& G5 0 1

③置0 阻塞线

&

G3 L1 L2

1 0 1

& G1

Q 0 1

§5.3 电平触发的触发器

一、电路结构及工作原理

(1)CP=0,状态不变。

(2)CP=1,工作,同SR锁存器一样约束条件为:SR=0。

电平触发RS触发器的特性表

*CP回到低电平后状态不定 在使用电平触发RS触发器的过程中,有时还需要CP信号到 来之前将触发器预先置成指定的状态,为此在实用的电平触发 RS触发器电路上往往还设置有专门异步置位输入端和异步复位 输入端,如下页图:1717

1

1 0

1 0

01 10

0 1 0 1

设触发器的初始状态Q=0。

CP=0:基本RS触发器的状态通过A,A’得以保持。

CP变为高电平以后:门 B,B’ 首先解除封锁,若此时输入 为J=1,K=0,则P=0,P’=1 ,…状 态无影响。 CP下降沿到达时:门 B,B’ 首先封锁,P,P’ 的电平不会立

第五章 触发器

§5.1 概述 §5.2 SR锁存器 §5.3 电平触发的触发器

§5.4 脉冲触发的触发器

§5.5 边沿触发的触发器 §5.6 触发器的逻辑功能及其描述方法

数字电子技术习题解答_杨志忠_第五章练习题_部分

教材:数字电子技术基础(“十五”国家级规划教材) 杨志忠 卫桦林 郭顺华 编著高等教育出版社2009年7月第2版; 2010年1月 北京 第2次印刷;第五章 集成触发器(部分习题答案)练习题5解答:(P213页)【5.1】、由与非门构成的基本RS 触发器,S D 和R D 端输入如图P5.1所示波形,试画出Q 和Q 的输出波形。

设触发器的初始状态为“0”。

解题思路:根据基本RS 触发器功能分段画图,并要注意与非门的基本RS 触发器是低电平有效。

当D S 和D R 端同时为有效低电平时,出现强制1态,有效电平同时撤去后(无效高电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ【5.2】、由或非门构成的基本RS 触发器,S D 和R D 端输入如图P5.2所示波形信号,试画出Q 和Q 的输出波形。

(设触发器的初始状态为“1”)。

解题思路:根据基本RS 触发器功能分段画图,并要注意或非门的基本RS 触发器是高电平有效,功能与与非门组成的RS 触发器功能相同。

当R D 和S D 端同时为有效高电平时,出现强制0态,有效电平同时撤去后(无效低电平)会出现不定态。

(不确定的状态,具体的状态取决两个与非门的翻转速度快慢)DS D RQ1≥1≥【5.4】、已知同步RS 触发器的输入CP,R 和S 的电压波形如题P5-4图所示的波形,试画出Q 和Q 的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步钟控RS 触发器是电位型触发器(高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,n 1n Q R S Q+=+,约束条件:RS=0,R=S=1时出现1Q Q 1n 1n ==++。

CPSQR【5.5】、已知同步D 触发器CP 和D 端的输入电压波形如P5.5图所示,试画出Q 端的输出波形。

(设触发器的初始状态nQ =0)解题思路:同步式触发器是电位型触发器(假定高电平敏感CP=1),在CP 有效触发期间的状态随输入信号发生变化,D Q1n =+。

第5章 触发器

山东大学(威海)机电与信息工程学院 邹晓玉 25

主从JK触发器特性表 CP J K Q Q* Q 0 1 0 0 1 1 1 0

功能 保持 保持 置0

× × × × 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1

根据特性表可写出Q*关于 J、K、Q的函数表达式, 并化简为最简形式,即特 性方程

山东大学(威海)机电与信息工程学院 邹晓玉 17

为适应单输入信号的需要,电平触发的SR触发器 可做成如下的电平触发的D触发器(D锁存器):

电平触发D触发器的特性表

CP

0

D Q

× ×

Q*

Q

功 能

保持

1

1 1 1

0 0

0 1 1 0 1 1

0

0 1 1

置0

置1

CP高电平触发;CP=0时不动作; D=0时,触发器置0; D=1时,触发器置1。

山东大学(威海)机电与信息工程学院 邹晓玉 18

例:已知电平触发的SR触发器的输入信号波形,画出的输出 波形 。设触发器初始状态为0。 保持原态 使输出全为1 Reset Set

CP R

S Q

Q

山东大学(威海)机电与信息工程学院 邹晓玉 19

CP撤去后 状态不定

电平触发的触发器的空翻现象 电平触发的触发器在一个CP脉冲作用期间,出现两次或 两次以上翻转的现象称为空翻。 电平触发的SR触发器, CP=1期间,输入信号仍 直接控制触发器输出端 状态。 CP=1时,S、R状态多次 变化,触发器输出状态随 着变化,触发器的抗干扰 能力较差。

0

1

1

0

1

0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

上一页 下一页

返回

5. 2

同步(可控)RS触发器

5.状态转换图 同步RS触发器的状态转换图如图5-5所示。 6.状态波形图 同步RS触发器的状态波形图如图5-6所示。

上一页

返回

5. 3

主从JK触发器

同步RS触发器与基本RS触发器相比较,其性能有所改善。但同步RS触 发器的触发方式为脉冲触发,因此实际应用中存在空翻现象,即在CP =1期间,触发器的状态可能发生多次翻转。另外这种触发器的输入状态 不能同时为“1”所以在应用中往往受到限制,而采用边沿触发器就能解 决在CP脉冲一个周期内.输出状态只改变一次.主从JK触发器就能克服上 述不足。 1.电路结构及符号 主从JK触发器的电路结构及符号如图5-7所示。 主从JK触发器在由两个相同的同步RS触发器组成的主从RS触发器的基 础上,又加上两条反馈线构成的。G1~G4组成的同步RS触发器为从触发 器; G5~G8组成的同步RS触发器为主触发器。

上一页 下一页

返回

5. 2

同步(可控)RS触发器

3.真值表 主从JK触发器的逻辑功能如表5-5所示。 4.特征方程 根据主从JK触发器的功能特性(表5-5),可以得到特征方程为 Qn+1=JQn + KQn 5.状态转换图 根据主从JK触发器的功能特性(表5-5) ,可得到主从JK触发器的状态转 换图如图5-8所示。 6.波形图 根据主从JK触发器的功能特性(表5-5),可得到主从JK触发器的状态波 形图如图5-9所示。

上一页 下一页

返回

5. 2

同步(可控)RS触发器

在CP =1期间,G7和G8被打开,主触发器的状态根据J, K输入信号的变 化而改变,并存在主触发器中等待输出。因G3和G4被封锁,所以从触发 器保持原状态不变。 在CP由“1”变“0”时刻,G3和G4被打开.从触发器按主触发器的状态翻 转,而G7和G8被封锁,此后J,K输入信号的改变不会引起主触发器的 变化,而从触发器的状态也不会改变,就保证了在CP脉冲的一个周期 内,触发器的输出状态只在脉冲的下降沿时刻改变一次,具体分析如下。 (1)无论触发器的原态是“0”或“1”。在CP = 1期间。J=1、K=0时,根 据同步RS触发器的功能。主触发器置“1”态。当CP脉冲的下降沿到来 时,从触发器也置“1”态,即Qn+1 = 1 。在CP=0期间, G7和G8被封锁, 主触发器的状态保持不变。

下一页

返回

5. 2

同步(可控)RS触发器

同步RS触发器是在基本RS触发器中增加两个“与非门” G3和G4组成时 钟控制门构成的。逻辑图如图5-4 (a)所示,逻辑符号如图5-4(b)所示。 2.电路的工作原理 由于它含有基本RS触发器.不受时钟脉冲控制,所以同步RS触发器有置 “1”和置“0”的功能,只有当Sd=Rd=1时,才能反映输入变量R, S在 CP脉冲控制下的输出状态。但是在CP=0时, G3和G4均被封闭,R、S 信号根本进不去,相当于基本RS触发器的输入为1,所以触发器的状态保 持不变,输出Qn+1 = Qn ;当CP=1时,G3和G4才能打开,其逻辑功能如 下。 (1) S=0, R=0时,G3=1,G4 =1, Qn+1 = Qn 。 (2) S=0, R=1时,G3=1,G4 =0, Qn+1 = 0 。 (3) S=1, R=0时,G3=0,G4 =1, Qn+1 = 1 。

下一页

返回

第 5章

集成触发器

在数字电路中,组合逻辑电路的输出状态仅取决于电路当前的输入状态, 而与电路以前的状态无关。但数字电路也需要对各种数字信号进行处理 和运算,因此就需要将以前的运算结果保存起来,以备使用。这就需要 数字电路具有记忆功能)本章讲述的触发器就是可以实现存储一位二进制 数字信号的功能。可以通过将多个触发器组合成集成触发器实现多位二 进制信号的存储。 触发器具有3个基本特性。 (1)有两个能自行保持的稳定状态,可分别表示二进制数码0和1。 (2)在输入信号作用下,两个稳态可相互转换(称为翻转)。 (3)已转换的稳定状态在输入信号消失之后仍能长期保持下来,这就使得 触发器能够记忆二进制信息。常用作二进制存储单元。

上一页

返回

5. 1

基本RS触发器

1.逻辑结构及符号 基本RS触发器电路结构最简单,它是构成其他触发器的基本组成单元, 逻辑电路如图5-1 (a)所示、逻辑符号如图5-1 (b)所示,它由两个“与非 门”G1和G2的输入端和输出端相互交叉反馈连接而成。Q、Q为输出端, Q与Q端的电平总是一高一低,互为“0”“1”。Sd、Rd端为输入端,小圆 圈表示低电平有效,即只有输入信号为低电平(“0”)时,才能触发电路, 为高电平(“1”)时,对电路无影响。 2.电路的工作原理 触发器逻辑功能分析方法,是根据电路结构建立输入、输出之间的逻辑 关系。然后分析其逻辑功能。几种情况分析如下。

上一页 下一页

返回

5. 2

同步(可控)RS触发器

因此从触发器的状态也不变,主从JK触发器在CP=0期间状态保持不变。 (2)无论触发器的原态是“0”或“1”态。在CP=1期间。J=1, K=0时,根 据同步RS触发器的功能,主触发器置1态。当CP脉冲的下降沿到来时, 从触发器也置1态,即Qn+1 = 1 。在CP=0期间, G7和G8被封锁,主触 发器的状态保持不变,因此从触发器的状态也不变,即主从K触发器在 CP=0期间状态保持不变——置“1”功能。 (3)无论触发器的原态是“0”或“1”态,在CP=1期间,J=0, K=1时,根 据同步RS触发器的功能,主触发器置“0”态。当CP脉冲的下降沿到来 时.从触发器也置0态,即Qn+1=0。在CP=0期间, G7和G8被封锁,主触 发器的状态保持不变,因此从触发器的状态也不变,即在CP=0期间状 态保持不变——置“0”功能。

下一页

返回

5. 1

基本RS触发器无论触发器原来是何状态,其次态一定为“1”,即 Qn+1=1,触发器处于置位状态。 (2)当Sd=1, Rd=0时,无论触发器原来是何状态.其次态一定为“0”,即 Qn+1 = 0,触发器处于复位状态。 (3)当Sd=Rd=1时,触发器状态不变,维持原态,即Qn+1 = Qn。 (4)当Sd=Rd=0时,即Qn+1 = Qn+1=1 ,破坏了触发器的正常工作,使触 发器失效,而且当输入条件同时消失时,触发器处于不定状态这种情况 是不允许的,因此使用时禁止Sd=Rd=0出现。 3.真值表 基本RS触发器的真值表是将输入、输出的逻辑关系列成如表5-1所示的 表格。

上一页 下一页

返回

5. 2

同步(可控)RS触发器

(5)如果触发器的原态是“0”态,在CP=1期间,J=1, K=1时, G7=0、 G8 =1,根据同步RS触发器的功能.主触发器置“1”态,当CP脉冲的下 降沿到来时,从触发器也置“1”态,即Qn+1 =1, Qn+1=Qn ——翻转功能。 (6)如果触发器的原态是“1”态,在CP = 1期间,J=1, K=1时,G7=1、 G8 =0 ,根据同步RS触发器的功能,主触发器置“0”态,当CP脉冲的 下降沿到来时,从触发器也置“0”态,即Qn+1 =0, Qn+1=Qn ——翻转功 能。 根据以上分析,总结主从.T K触发器的逻辑关系如下。 (1)若J,K端相异,则下一个输出状态:Qn+1 = J。 (2)若J=K=0,则下一个输出状态: Qn+1=Qn 。 (3)若J=K=1,则下一个输出状态: Qn+1=Qn 。

上一页 下一页

返回

5. 1

基本RS触发器

从真值表5-1中可以看出基本RS触发器的逻辑功能是:保持记忆、置“1”、 置“0”的功能,如表5-2所示。在表中Qn为触发器目前的状态,Qn+1为 触发器在输入端信号作用下的下一个状态(即次态) 。 4.特征方程 特征方程又称为状态方程或特性方程,根据表5-1可以用卡诺图化简得 到输入与输出之间的逻辑函数表达式,不允许出现的情况就采用约束条 件表示,即 Qn+1 =Sd+ RdQn Sd+ Rd =1 约束条件表示,基本RS触发器的输入端不允许同时出现为0的情况。 5.状态转换图

下一页

返回

5. 2

同步(可控)RS触发器

从触发器的输入信号是主触发器的输出信号Q和Q。G5门是一个非门, 其作用是将CP反相后控制从触发器逻辑电路如图5-7 (a)所示,逻辑符号 如图5-7 (b)所示。输出端Q和Q交叉反馈到G7和G8的输入端,以保证G7 和G8的输入为互补状态。J , K端为信号输入端,Q和Q为触发器的两个 互补输出端。 由于时钟脉冲的下降沿到来时,触发器的状态发生改变,因此主从.lK触 发器的触发方式为下降沿触发,在如图5-7(b)中CP端加小圆圈表示下降 沿触发。 2.电路的工作原理(Sd=Rd=1)

第 5章

1 2

集成触发器

5.1

5.2 5.3 5. 4 5.5

基本RS触发器

同步(可控)RS触发器 主从JK触发器 D触发器 触发器的转换

下一页 返回

3

4 5

第一章 保持阳光心态

6 7

5.6

触发器的应用

实验技能训练八

上一页

返回

第 5章

集成触发器

教学目标 1.熟悉各种触发器的电路结构和逻辑功能分类。 2.理解各种触发器的触发方式、工作特点以及逻辑功能描述方法。 3.熟悉各种触发器的使用方法和相互转换方法。 触发器是数字逻辑电路中的另一类基本单元电路。它是一种最简单的时 序电路。是构成其他时序电路的最基本的单元电路。触发器具备两个稳 定状态,即“0”态和“1”态.这两种稳定状态可以分别代表二进制数码。 和1如果外加合适的触发信号,触发器的状态可以相互转换。这种电路 的特点是具有记忆功能。