IC设计流程之实现篇全定制设计

ic设计的流程

ic设计的流程IC设计的流程IC设计是指在集成电路技术的基础上,通过设计和制造过程将电路功能集成到单个芯片上的过程。

在IC设计的流程中,通常包括以下几个步骤。

一、需求分析在IC设计之前,首先需要进行需求分析。

这一步主要是确定设计的目标和要求,包括电路的功能、性能指标、功耗要求等。

通过与客户的沟通和理解,确定设计的方向和重点。

二、电路设计电路设计是IC设计的核心步骤。

在电路设计中,设计师需要根据需求分析的结果,选择合适的电路拓扑结构和器件参数,设计各个功能模块的电路。

在设计过程中,需要考虑电路的稳定性、抗干扰能力、功耗等因素,并进行电路仿真和优化。

三、逻辑设计逻辑设计是电路设计的重要环节。

在逻辑设计中,设计师需要将电路的功能转化为逻辑门电路的形式,确定各个模块之间的逻辑关系。

通过使用逻辑设计工具,设计师可以进行逻辑门电路的综合、优化和布局。

四、物理设计物理设计是将逻辑设计转化为实际的物理结构的过程。

在物理设计中,设计师需要进行布局设计和布线设计。

布局设计是指将逻辑门电路的元件布置在芯片上的过程,布线设计是指将逻辑门之间的连线进行规划和布线的过程。

物理设计的目标是在满足电路功能和性能要求的前提下,尽可能减小芯片的面积和功耗。

五、验证与仿真验证与仿真是确保设计的正确性和可靠性的重要步骤。

在验证与仿真中,设计师需要使用专业的EDA工具对设计进行验证,包括逻辑仿真、时序仿真和功能仿真等。

通过仿真验证,可以检查设计中是否存在逻辑错误、时序冲突等问题,并进行相应的优化和调整。

六、物理制造物理制造是将设计好的电路转化为实际的芯片的过程。

在物理制造中,设计师需要将物理设计导出为制造文件,并与制造厂商进行合作。

制造厂商将根据制造文件进行芯片的制造,包括光刻、薄膜沉积、离子注入等工艺步骤。

制造完成后,芯片将进行测试和封装。

七、测试与封装测试与封装是确保芯片质量和可靠性的重要步骤。

在测试与封装中,芯片将进行功能测试、可靠性测试和温度测试等,以确保芯片的性能和品质。

IC设计流程

IC设计流程⼤体是1. ⾸先是使⽤HDL语⾔进⾏电路描述,写出可综合的代码。

然后⽤仿真⼯具作前仿真,对理想状况下的功能进⾏验证。

这⼀步可以使⽤Vhdl或Verilog作为⼯作语⾔,EDA⼯具⽅⾯就我所知可以⽤Synopsys的VSS(for Vhdl)、VCS(for Verilog)Cadence的⼯具也就是著名的Verilog-XL和NC Verilog2.前仿真通过以后,可以把代码拿去综合,把语⾔描述转化成电路⽹表,并进⾏逻辑和时序电路的优化。

在这⼀步通过综合器可以引⼊门延时,关键要看使⽤了什么⼯艺的库这⼀步的输出⽂件可以有多种格式,常⽤的有EDIF格式。

综合⼯具Synopsys的Design Compiler,Cadence的Ambit3,综合后的输出⽂件,可以拿去做layout,将电路fit到可编程的⽚⼦⾥或者布到硅⽚上这要看你是做单元库的还是全定制的。

全定制的话,专门有版图⼯程师帮你画版图,Cadence的⼯具是layout editor 单元库的话,下⾯⼀步就是⾃动布局布线,auto place & route,简称apr cadence的⼯具是Silicon Ensembler,Avanti的是Apollolayout出来以后就要进⾏extract,只知道⽤Avanti的Star_rcxt,然后做后仿真如果后仿真不通过的话,只能iteration,就是回过头去改。

4,接下来就是做DRC,ERC,LVS了,如果没有什么问题的话,就tape out GDSII格式的⽂件送制版⼚做掩膜板,制作完毕上流⽔线流⽚,然后就看是不是work了做DRC,ERC,LVSAvanti的是Hercules,Venus,其它公司的你们补充好了btw:后仿真之前的输出⽂件忘记说了,应该是带有完整的延时信息的设计⽂件如:*.VHO,*.sdfRTL->SIM->DC->SIM-->PT-->DC---ASTRO--->PT----DRC,LVS--->TAPE OUT1。

IC设计流程

IC设计流程IC设计流程是指将集成电路的功能目标转化为结构目标、物理目标,然后进行细化和描述,最终实现设计的过程。

整个流程包括从设计规格开始到验证和测试结束的一系列步骤。

以下是完整版IC设计流程。

1.设计规格:根据应用需求和市场要求,确定集成电路的功能、性能、功耗等规格参数。

其中包括电路的输入输出要求、逻辑功能、时钟频率、功耗等。

2.架构设计:根据设计规格,确定电路的整体结构,包括功能模块的划分、通信接口、数据传输路径等。

通过分析复杂度和资源占用情况,确定电路的实现方案。

3. RTL设计:采用硬件描述语言(如Verilog或VHDL),进行寄存器传输级(RTL)设计,即对电路的功能模块进行一级抽象和描述。

包括确定信号的操作和数据流路径、控制逻辑等。

4.验证:对RTL设计进行功能验证和时序验证,以确保设计符合规格要求。

功能验证通过仿真工具进行,时序验证主要通过时序约束和时序仿真判断。

5.合成:将RTL设计转换为逻辑门级的电路描述,包括电路的布局、布线、时钟资源分配等。

实现方式可以是手工合成和自动合成。

6.物理设计:进行布局规划和布线,生成物理级别的网表。

包括将电路各个单元放置在芯片平面上并规划连线路径,最小化连线长度和面积,并考虑信号的延迟和功耗。

7.物理验证:对布局和布线的结果进行物理验证,包括电路的连通性、电子规则检查、功耗、时序等。

通过使用专业的物理验证工具,确保电路布局和布线无误。

8.版图生成:根据物理设计结果生成版图,包括版图的规划、标准单元的放置、连线等。

版图生成时需考虑电路性能、功耗和面积等因素。

9.版图验证:对版图进行验证,包括电路的连通性、电子规则检查、功耗、时序等。

验证通过后,生成版图文件,供后续工艺流程使用。

10.功率分析和时序分析:对设计进行功耗和时序分析,以评估电路的工作性能和功耗情况。

通过仿真和静态分析工具进行分析,确认设计满足需求。

11.生成GDSII文件:将版图文件转换为GDSII文件格式,以供后续的芯片制造流程使用。

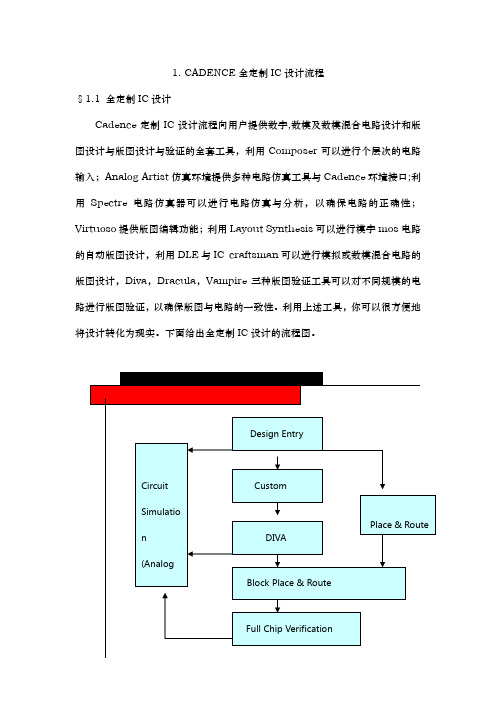

CADENCE全定制IC设计流程图

1. CADENCE全定制IC设计流程§1.1 全定制IC设计Cadence定制IC设计流程向用户提供数字,数模及数模混合电路设计和版图设计与版图设计与验证的全套工具,利用Composer可以进行个层次的电路输入;Analog Artist仿真环境提供多种电路仿真工具与Cadence环境接口;利用Spectre电路仿真器可以进行电路仿真与分析,以确保电路的正确性;Virtuoso提供版图编辑功能;利用Layout Synthesis可以进行模字mos电路的自动版图设计,利用DLE与IC craftsman可以进行模拟或数模混合电路的版图设计,Diva,Dracula,Vampire三种版图验证工具可以对不同规模的电路进行版图验证,以确保版图与电路的一致性。

利用上述工具,你可以很方便地将设计转化为现实。

下面给出全定制IC设计的流程图。

2.Cadence cdsSPICE 的使用说明Cadence cdsSPICE 也是众多使用SPICE 内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE 相同。

这里我将侧重讲一下它的一些特殊用法。

§ 2-1 进入Cadence 软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb 调出Cadence 软件。

出现的主窗口如图2-1-1所示: 图 2-1-1Candence 主窗口二.在PC 机上使用1)将PC 机的颜色属性改为256色(这一步必须);2)打开Exceed 软件,一般选用xstart 软件,以下是使用步骤:start method 选择REXEC (TCP-IP ) ,Programm 选择Xwindow 。

Host 选择10.13.71.32 或10.13.71.33。

host type 选择sun 。

IC芯片行业介绍及设计全流程

2 设 计 流 程 OPERATIONAL PRINCIPLE

源于对处理信号类型的不同,芯片主要分为数字与模拟 两大类。芯片设计这个环节分为前端和后端两部分,但岗位 并不只是两个这么简单,这个下面会讲,以数字IC举例。如 果要给小白解释的话,可以这样简单的讲: 设计一款芯片, 明确需求(功能和性能)之后,先由架构工程师设计架构, 得出芯片设计方案,前端设计工程师形成RTL代码,验证物理版图。设计环节到此为止,后面则是制造和封测环节。

IC芯片行业介绍及设计全流程

1 芯片介绍

DEFUNE INTRODUCE

IC是Integrated Circuit的缩写,即集成电路,是我们 所说的芯片,IC设计就是芯片设计。 这里就需要科普一个概 念:一颗芯片是如何诞生的? 就目前来说,有两种芯片产出 的模式。 1)一条龙全包 IC制造商(IDM)自行设计,由自 己的产业线进行加工、封装、测试、最终产出芯片。 2)环 节组合 IC设计公司(Fabless)与IC制造公司(Foundry)相 结合,设计公司将最终确定的物理版图交给Foundry加工制造, 封装测试则交给下游厂商。 而IC设计,即上游设计中所处的 部分。

2 设 计 流 程 OPERATIONAL PRINCIPLE

物理版图以GDSII的文件格式交给Foundry(台积电、中 芯国际这类公司)在晶圆硅片上做出实际的电路,再进行封 装和测试,就得到了芯片。如果要专业一点来讲解的话: 数 字前端以设计架构为起点,以生成可以布局布线的网表为终 点,是用设计的电路实现需求。主要包括RTL编程和仿真,前 端设计还可以划分为IC系统设计、验证、综合、STA、逻辑等 值验证 。其中IC系统设计最难掌握,它需要多年的IC设计经 验和熟悉那个应用领域,就像软件行业的系统架构设计一样, 而RTL编程和软件编程相当。

IC设计流程范文

IC设计流程范文集成电路设计是新一代电子电路设计的一个重要方向。

它着眼于如何将大量的电子器件和电路封装在一个芯片上,从而实现高度集成和多功能的电子系统。

IC设计的流程可以分为以下几个主要步骤:1.需求分析:这是IC设计的起点。

在设计开始之前,需要明确设计的目标和要求。

这包括确认电路的主要功能、性能参数、电路资源、工作温度范围等。

同时,还需要考虑电源电压、尺寸要求、接口标准、测试要求等。

2.架构设计:根据需求分析得到的设计目标,进行IC的整体架构设计。

这一步骤将设计分解成多个功能模块,并确定每个模块之间的接口和通信方式。

通过对整个系统的分析,确定在芯片上的电路结构和电路层次。

3.电路设计:在架构设计的基础上,进行电路设计。

这包括设计各个功能模块的电路,选择适合的器件,进行电路的放大、滤波、混频、建模等操作。

在这一步骤中,设计工程师需要考虑电路参数、功耗、电源噪声等因素。

4.物理设计:物理设计是将电路设计转化为物理结构的过程。

主要包括芯片的布局和布线。

在布局过程中,需要考虑芯片的面积利用率、布局的曝光等技术指标。

在布线过程中,需要优化信号传输的延迟、功率消耗等因素。

5.验证和仿真:在物理布局和布线完成后,需要对设计进行验证和仿真。

这一步骤可以通过模拟仿真或数字仿真进行。

通过仿真可以检测到设计中的错误,优化电路性能并确保设计满足需求。

6.原型制作:在验证和仿真完成后,可以进行原型的制作。

这涉及到将设计文件提交给芯片制造厂商,并进行掩膜生产。

完成掩膜生产后,可以制作出硅芯片,并进行功能测试。

7.测试和调试:在制作完原型芯片后,需要对芯片进行测试和调试。

这包括功能测试、性能测试、功耗测试、温度测试等。

通过测试和调试可以发现设计中的问题,并进行相应的修正。

8.量产和集成:在测试和调试完成后,可以进行芯片的量产。

这包括将设计数据交付给制造工厂,进行大规模芯片生产。

在芯片生产过程中,需要进行晶圆切割、封装和测试等步骤。

CADENCE全定制IC设计流程

CADENCE全定制IC设计流程CADENCE是一种广泛应用于集成电路(IC)设计的软件工具。

它提供了完整的设计流程和工具,用于设计、验证和制造IC芯片。

在基于CADENCE的全定制IC设计流程中,在IC设计的每个阶段都使用到了CADENCE工具套件,包括电路和物理设计工具、模拟和数字仿真工具、布图工具以及物理验证工具等。

下面是使用CADENCE进行全定制IC设计的一般流程:1.设计需求分析:根据所需的功能和性能需求,进行设计需求分析。

这包括确定电路拓扑结构、电路规范和性能指标等。

2. 电路设计:使用CADENCE中的Schematic设计工具,绘制电路原理图。

根据设计需求,选择合适的电子元件并进行电路布线。

使用CADENCE的仿真工具,验证电路的功能和性能。

3.物理设计:将电路原理图转换为布局图。

使用CADENCE的布局工具,在设计规范的限制下进行器件布局和连线布线。

这包括选择合适的器件大小和排列方式,以优化电路性能和功耗。

4.物理验证:使用CADENCE的物理验证工具,对电路布局进行验证。

这包括电路的电性能分析、功耗分析、时序等效验证以及电磁兼容性分析等。

根据验证结果进行布局优化和改进。

5.交互测试:将设计与其他模块和子系统进行集成测试。

使用CADENCE的模拟工具和数字仿真工具,对整个系统进行功能验证和性能评估。

7.物理制造:通过CADENCE的布局生成工具,生成用于物理制造的设计数据库文件。

这包括物理制造规则检查、填充、光刻掩膜生成等。

8.物理验证:使用CADENCE的物理验证工具,对物理制造的设计进行验证。

这包括工艺模拟、功耗分析、封装和信号完整性分析等。

9.物理制造:将设计数据库文件发送给制造厂商进行实际制造。

这包括掩膜制造、芯片加工、封装和测试等。

10.性能评估:对实际制造的芯片进行性能评估和测试。

使用CADENCE的集成测试工具,进行功能测试、速度测试和功耗测试等。

11.系统集成:将IC芯片集成到目标系统中,并进行系统级测试和验证。

IC制作流程范文

IC制作流程范文IC(Integrated Circuit,集成电路)制作流程是指将电子元器件中的电晶体、电阻、电容等元件及其连接线等,通过特定的工艺步骤在半导体材料上制造出集成电路的过程。

下面将详细介绍IC制作的主要流程。

IC制作的主要流程包括芯片设计、掩膜制作、晶圆加工、电极制作、封装测试等几个主要步骤,具体如下:1.芯片设计:首先是根据需要设计出芯片电路。

设计师根据电路功能和性能要求,使用仿真软件进行电路设计,并通过仿真验证电路的准确性和可行性。

2.掩膜制作:设计好的电路通过计算机辅助设计软件(CAD)生成芯片的图形信息,然后将图形信息转化为半导体晶圆的光刻掩膜。

掩膜制作一般使用光刻技术,将电路设计的图形信息通过激光束刻写到光刻胶上,并通过光刻机将图形转移到硅片上。

3.晶圆加工:在晶圆加工过程中,需要将芯片的电路图案通过蚀刻、离子注入、扩散等工艺步骤加工到硅片上。

首先是将掩膜映射到硅片上,然后通过蚀刻工艺去除掉不需要的材料,留下芯片电路所需要的结构。

再通过离子注入或扩散工艺改变硅片的导电性能,形成导电区和绝缘区。

4.电极制作:在硅片表面形成电极是制作IC的重要步骤之一、首先是将金属薄膜或者金属线路沉积在硅片表面,通过各种光刻和蚀刻技术形成电极引线。

然后通过热处理来实现电极与半导体器件之间的连接,并形成稳定的电路结构。

5.封装测试:在IC制作完成后,需要将元器件和电路在硅片上面封装成IC。

同时还需要进行电性能测试、可靠性测试等。

封装是将芯片放置到适当的封装载体中,并通过焊接或粘接进行可靠地连接。

6.封装完成后,对IC进行电性能测试和可靠性测试。

测试包括功能测试、性能测试、温度测试、电压测试、电流测试等。

这些测试主要是为了验证芯片的各项电性能指标的准确性和稳定性。

以上是IC制作的主要流程,其中每个步骤都包括了一系列的操作和工艺方法。

整个IC制作流程需要高度的技术和严格的控制,以确保制造出优质的集成电路产品。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IC设计流程之实现篇——全定制设计要谈IC设计的流程,首先得搞清楚IC和IC设计的分类。

集成电路芯片从用途上可以分为两大类:通用IC(如CPU、DRAM/SRAM、接口芯片等)和专用IC(ASIC)(Application Specific Integrated Circuit),ASIC是特定用途的IC。

从结构上可以分为数字IC、模拟IC和数模混合IC三种,而SOC(System On Chip,从属于数模混合IC)则会成为IC设计的主流。

从实现方法上IC设计又可以分为三种,全定制(full custom)、半定制(Semi-custom)和基于可编程器件的IC设计。

全定制设计方法是指基于晶体管级,所有器件和互连版图都用手工生成的设计方法,这种方法比较适合大批量生产、要求集成度高、速度快、面积小、功耗低的通用IC或ASIC。

基于门阵列(gate-array)和标准单元(standard-cell)的半定制设计由于其成本低、周期短、芯片利用率低而适合于小批量、速度快的芯片。

最后一种IC设计方向,则是基于PLD或FPGA器件的IC设计模式,是一种“快速原型设计”,因其易用性和可编程性受到对IC制造工艺不甚熟悉的系统集成用户的欢迎,最大的特点就是只需懂得硬件描述语言就可以使用EDA工具写入芯片功能。

从采用的工艺可以分成双极型(bipolar),MOS和其他的特殊工艺。

硅(Si)基半导体工艺中的双极型器件由于功耗大、集成度相对低,在近年随亚微米深亚微米工艺的的迅速发展,在速度上对MOS管已不具优势,因而很快被集成度高,功耗低、抗干扰能力强的MOS管所替代。

MOSFET工艺又可分为NMOS、PMOS和CMOS三种;其中CMOS工艺发展已经十分成熟,占据IC市场的绝大部分份额。

GaAs器件因为其在高频领域(可以在0.35um下很轻松作到10GHz)如微波IC中的广泛应用,其特殊的工艺也得到了深入研究。

而应用于视频采集领域的CCD传感器虽然也使用IC一样的平面工艺,但其实现和标准半导体工艺有很大不同。

在IC开发中,常常会根据项目的要求(Specifications)、经费和EDA工具以及人力资源、并考虑代工厂的工艺实际,采用不同的实现方法。

其实IC设计这个领域博大精深,所涉及的知识工具领域很广,本系列博文围绕EDA工具展开,以实现方法的不同为主线,来介绍这三种不同的设计方法:全定制、半定制和基于FPGA的IC设计,这三种方法在EDA工具和流程上都有各自鲜明的特色,通过介绍这三种IC设计方法可以让大家对IC设计有个清晰的思路,也顺便介绍了其中涉及到的大多数EDA工具,并且避免了读者陷入IC领域的某些细节中而不能一窥全貌之嫌。

其实,无论是IC和ASIC,还是I/O芯片、CPU芯片在EDA工具上的区别都不明显,并且涉及某些应用领域的特定的知识,需要读者具备一定的背景知识,不适合用来作为介绍IC的设计流程的入门级题材。

全定制IC设计方法,是按照规定的功能与性能要求,先设计出满足功能的电路,然后对电路的布局与布线进行专门的优化设计,以达到芯片的最佳性能。

全定制IC设计的主要EDA 工具有Cadence的Virtuoso、Synopsys的Custom Designer(CD)等,这两款工具实际上提供一个集成设计环境,在这个环境里用户可以方便地配置和利用各家EDA的工具来完成各个设计阶段的任务。

首先来看一看它的设计基本流程(如下图)。

图11. 定义设计规格(Design Specification)典型的设计规格书描述了电路的功能(电流放大能力、信噪比、带宽等),最大可容许的延时,以及其他的物理性能,如功耗等。

通常设计规格书给予电路设计者以较大的设计自由度:如选择特定的电路拓扑结构,特定器件的位置,输入输出pin角的位置,MOSFET的宽长比等。

下面是一个一个全加器的规格说明书:-------0.8um双井CMOS工艺“加法”“进位”的传递延时小于1.2ns“加法”“进位”的转换时间小于1.2ns电路面积小于1500平方微米动态功耗<1mW(VDD=5V,fmax=20MHZ)-------2. 绘制电路图电路图绘制工具称为Schematic Capture(下图是Virtuoso中的Composer工具),可以提供门级和晶体管级的电路图绘制功能,该步骤完成后可以生成网表文件供电路仿真之用。

需要说明的是,各家产生的Schematic文件不完全兼容,要从Synopsys的CD中读入Virtuoso产生的电路图似乎有些困难。

再有一点就是从网表反过来生成电路图这一功能在这两家的工具中都没有被支持,有一个第三方工具spicevison有此功能,但是否能导入Virtuoso或CD中者不得而知,spicevison这个工具的用处在于晶体管级的调试(对照网表和电路图),不在于其生成的电路图的通用性。

图23. 产生子电路或电路单元符号在有层次结构(hierarchical)的电路中,使用用户自定义的电路图符号来代替整个子电路块,有利于减少重复绘制这些频繁出现的子电路块,使整个顶层的电路整洁而有序,避免出现一个一大片的扁平(flatten)的电路图。

如反相器INV,NOR和NADN等,在设计中一般都使用自定义的电路符号代替,这也是代工厂提供PDK中常用的一个手法。

4. 电路仿真这一步将调用电路仿真器,如HSPICE、SPECTRE、ELDO等来实现电路的仿真,用以验证电路的各项电性指标是否符合规格说明书。

在集成设计环境中用户可以通过配置自由地选择使用这些仿真器,如在Virtuoso ADE(Analog Design Environment),可以方便地使用HSPICE 来仿真,当然前提是生成HSPICE格式的网表。

在图1中有一个迭代-循环的箭头,说明这一步可能需要迭代,若仿真的结果不满足规格说明书,需要调整电路图,然后再做仿真。

这一步由于没有寄生参数加入网表,通常叫做版图前仿真(Pre-layout simulation)。

另外,电路仿真需要代工厂提供的元器件库(代工厂一般以PDK包提供给客户,里面包含各种器件的spice模型,technology file,Design rule等)5. 生成版图版图的生成是至关重要的一环,是连接电路设计与芯片代工厂的一个桥梁,版图不仅反映了电路图的连接关系和各种元器件规格,还反映了芯片的制造过程和工艺(具体将在另一篇博文中专门叙述)。

由电路图Schematic到版图绘制一般使用集成开发环境中的Layout Editor。

生成版图有两种途径,一是手工绘制而成(根据具体的工艺文件-technology file),另一种是自动生成(具体可参考Virtuoso Layout,Synopsys的ICWB)。

生成的文件格式为GDSII 或CIF,都是国际流行的标准格式。

6. DRC检查DRC——Design Rule Check,版图生成完成后,还需要进行“设计规则检查”,这是一些由特定的制造工艺水平确定的规则,如poly-poly contact的最小间距,metal-metal的最小间距和metal的最大宽度等等。

这些规则体现了芯片制造的“良率(即合格率)”和芯片性能的折衷。

(图3 显示出有两处违反DRC,都是metal的宽度超过设计规则要求)EDA工具有Cadence Virtuoso iDRC、Dracula(这是一个独立的版图验证工具,具有DRC/ERC、LVS、寄生参数提取等多种功能),Synopsys的Hercules(DRC、LVS检查)。

图37. 寄生参数提取当版图的DRC完成之后,需要提取该电路的寄生参数以用来比较精确地模拟现实芯片的工作情形,寄生参数包含寄生电阻和寄生电容,在高频电路设计中还需要提取寄生的电感。

EDA工具主要有StarRC,Calibre,Dracula等。

这些寄生参数一般都简化成一个或多个lumped R/C/L,“插入”相应的电路节点处,一般都是与电压无关的线性无源器件。

这样经过寄生参数提取后生成的网表文件,被称为“post-layout netlist”。

8. LVS检查Layout-versus-Schematic (LVS) Check,LVS将比较原来的电路图的“拓扑网络”与从版图提取出来的拓扑结构,并证明二者是完全等价的。

LVS提供了另一个层次的检查以保证设计的完整性和可靠性——这个版图是原来设计的物理实现。

LVS只能保证电路的拓扑结构是一致的,并不能保证最后电路的电学性能一定满足设计规格书。

典型的LVS错误为,两个晶体管的不当连接关系,或遗漏的连线等。

9. 后仿真可以从图1看到,在DRC和LVS这两步上都有返回layout的迭代,说明若要设计流程成功进行到“post-layout simulation”即后仿真这一阶段,需要清除所有DRC和LVS的错误信息。

后仿真的输入是包含原始电路信息以及寄生信息的网表,是最接近真实电路的网表文件。

通过“后仿真”,可以获得该设计完整真实的性能:延时、功耗、逻辑功能、时序信息等信息,这一过程也是验证整个设计是否成功的“最后一关”,若不满足规格说明书要求则需要从头来过——从调整Schematic开始重新走完新一轮的设计流程。

与pre-layout仿真(第4步)不同的是,HSPICE或SPECTRE的输入文件除了原始网表外,还须要一些寄生参数的文件(如spf、spef),这一种电路仿真又称“back-annotation simulation”(具体参见HSPICE用户手册)。

评价与说明以上的9个步骤只能保证该设计在simulation的角度是经过“验证了的”,并不保证制造出来的电路一定和simulation出来的结果一致,所以在大规模投放代工厂制造(又称“流片”)之前,还需要经过一些小批量的“试流片”,这叫做“硅验证”(silicon verification)。

通过硅验证后的设计才是真正成功的设计,我们经常听说的“硬IP”就是指这一类经过硅验证过的成功的设计,“软IP”通常指的是只是通过以上9步的EDA工具验证的设计。

另外,与下一篇博文将要介绍的半定制IC设计流程相比,全定制设计缺少“综合(synthesis)、布局布线(place and route)”等步,说明全定制设计不可能或者很困难实现综合和自动布局布线,历史上曾经有很多公司致力于此,但都中道崩殂。

目前的EDA设计流程很多步骤要靠手工操作,这就需要很多的技巧和设计经验。

其次,全定制设计的电路是一些规模比较小,需要非常好的性能,并且重复利用率很高的“关键电路模块”,很多是模拟电路,或数模混合电路,由于其设计过程复杂而对设计者的经验要求甚高,被业界称之为“艺术品级电路设计”。