电子科技大学数字逻辑设计及应用-2005真题(复试)

电子科技大学期末数字电子技术考试题a卷-参考答案

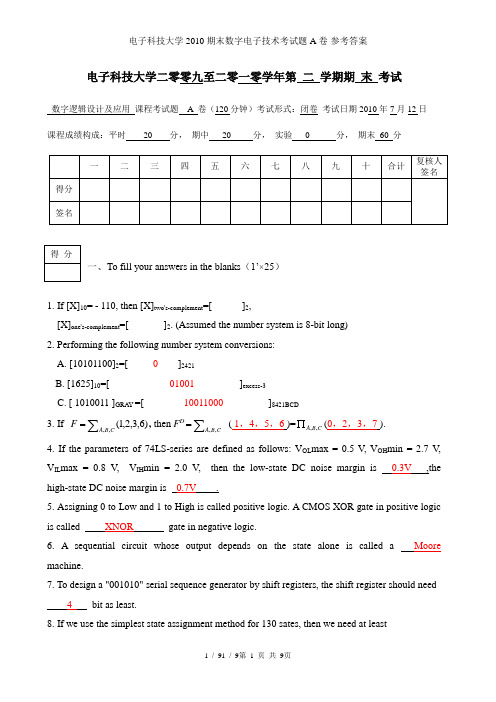

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分一、To fill your answers in the blanks (1’×25)1. If [X]10= - 110, then [X]two's-complement =[ ]2,[X]one's-complement =[ ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 0 ]2421B. [1625]10=[01001 ]excess-3C. [ 1010011 ]GRAY =[10011000 ]8421BCD3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ).4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is 0.3V ,the high-state DC noise margin is 0.7V .5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic.6. A sequential circuit whose output depends on the state alone is called a Moore machine.7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least.8. If we use the simplest state assignment method for 130 sates, then we need at least8state variables.9. One state transition equation is Q*=JQ'+K'Q. If we use D flip-flop to complete the equation, the D input terminal of D flip-flop should be have the function D= JQ'+K'Q.10.Which state in Fig. 1 is ambiguous D11.A CMOS circuit is shown as Fig. 2, its logic function z= A’B’+ABFig. 1 Fig. 212.If number [A]two's-complement =01101010 and [B]one's-complement =1001, calculate [A-B]two's-complement and indicate whether or not overflow occurs.(Assumed the number system is 8-bit long)[A-B]two's-complement = 01110000, overflow no13. If a RAM’s capacity is 16K words × 8 bits, the address inputs should be 14bits; We need 8chips of 8K ⨯8 bits RAM to form a 16 K ⨯ 32 bits ROM..14. Which is the XOR gate of the following circuit A .15.There are 2n-n invalid states in an n-bit ring counter state diagram.16.An unused CMOS NOR input should be tied to logic Low level or 0 .17.The function of a DAC is translating the Digital inputs to the same value of analogoutputs.二、Complete the following truth table of taking a vote by A,B,C, when more than two of A,B,C approve a resolution, the resolution is passed; at the same time, the resolution can’t go through if A don’t agree.For A,B,C, assume 1 is indicated approval, 0 is indicated opposition. For the F,A B C F三、The circuit to the below realizes a combinational function F of four variables. Fill in the Karnaugh map of the logic function F realized by the multiplexer-based circuit. (6’)四、(A) Minimize the logic function expressionF = A·B + AC’ +B’·C+BC’+B’D+BD’+ADE(H+G) (5’)F = A·B + AC’ +B’·C+BC’+B’D+BD’ = A·(B ’C )’ +B’·C+BC’+B’D+BD’= A +B’·C+BC’+B’D+BD’+C ’D (或= A +B’·C+BC’+B’D+BD’+CD ’)= A +B’·C+BD’+C ’D (或= A + BC’+B’D +CD ’)(B) To find the minimum sum of product for F and use NAND-NAND gates to realize it (6’)),,,(Z Y X W F Π(1,3,4,6,9,11,12,14)------3分 F= X ’Z ’+XZ -----2分 =( X ’Z ’+XZ)’’=(( X ’Z ’)’(XZ)’)’ ------1分五、Realize the logic function using one chip of 74LS139 and two NAND gates.(8’)∑=)6,2(),,(C B A F ∑=)3,2,0(),,(E D C GF(A,B,C)=C’∑(1,3) ---- 3分 G(C,D,E)=C’∑(0,2,3) ----3分-六、Design a self-correcting modulo-6 counter with D flip-flops. Write out the excitation equations and output equation. Q2Q1Q0 denote the present states, Q2*Q1*Q0* denote the next states, Z denote the output. The state transition/output table is as following.(10’)Q2Q1Q0Q2*Q1*Q0*Z000 100 0100 110 0110 111 0111 011 0011 001 0001 000 1激励方程式:D2=Q0’(2分,错-2分)D1=Q2 (2分,错-2分)D0=Q1 (2分,错-2分)修改自启动:D2=Q0 +Q2Q1’(1分,错-1分)D1=Q2+Q1Q0’(1分,错-1分)D0=Q1+Q2Q0 (1分,错-1分)输出方程式:Z=Q1’Q0 (1分,错-1分)得分七、Construct a minimal state/output table for a moore sequential machine, that will detect the input sequences: x=101. If x=101 is detected, then Z=1.The input sequences DO NOT overlap one another. The states are denoted with S0~S3.(10’)For example:X:0 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 ……Z:0 0 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 ……state/output table八、Please write out the state/output table and the transition/output table and theexcitation/output table of this state machine.(states Q2 Q1=00~11, use the state name A~D )(10’)Transition/output table State/output table Excitation/output table(4分) (3分) (3分)评分标准:转移/输出表正确,得4分;每错一处扣0.5分,扣完4分为止;由转移/输出表得到状态/输出表正确,得3分;每错一处扣0.5分,扣完3分为止;激励/输出表正确,得3分;每错一处扣0.5分,扣完3分为止。

电子科技大学14秋《数字逻辑设计及应用》在线作业1答案

一,单选题

1. T触发器中,当T=1时,触发器实现()功能

A.置1

B.置0

C.计数

D.保持

?

正确答案:C

2. L=AB+C的对偶式为:()

A. A+BC

B. (A+B)C

C. A+B+C

D. ABC

?

正确答案:B

3.和8421BCD码1000等值的余3BCD码是

A.错误

B.正确

?

正确答案:B

A.

B. 0001

C. 1011

D. 1000

E. 10源电压VCC=

A. 0.2V

B. 0.8V

C. 3.6V

D. 5V

?

正确答案:D

5.只能按地址读出信息,而不能写入信息的存储器为

A. RAM

B. ROM

C. PROM

D. EPROM

?

正确答案:B

6.只能按地址读出信息,而不能写入信息的存储器为

A.错误

B.正确

?

正确答案:A

5.(1000)8421BCD表示十进制数10。

A.错误

B.正确

?

正确答案:A

6. n级触发器构成的计数器最多可计2n个数。

A.错误

B.正确

?

正确答案:B

7. CMOS电路的电源电压只能使用+5V。

A.错误

B.正确

?

正确答案:A

8. n个变量构成的任一个最小项,它总共有另外n个最小项和它是逻辑相邻的。

A. RAM

B. ROM

C. PROM

D. EPROM

数字逻辑设计及实践电子科技大学试卷及答案

数字逻辑设计及实践1、存储单元是时序状态机不可缺少的组成部分;( √ )2、7485为4位二进制比较器。

如果二进制数A=B ,则其输出必将是Y (A=B )有效;(Х )3、所有类型的触发器其状态更新都发生在时钟触发沿上;(Х )4、米利型时序逻辑的输出仅仅取决于当前现态的值;(Х )5、穆尔型时序逻辑的输出仅仅取决于当前现态的值;( √ )6、异步时序逻辑电路中各个触发器所用的时钟触发沿不完全相同;( √ )7、如果两个时序逻辑的状态转换关系以及所选择的触发器都相同,则其逻辑图也相同;( Х)8、时序逻辑可以没有输出,但是组合逻辑必须有输出;( √ )9、要实现模为100的计数器(有效计数循环圈的状态数为100),则需要10片74160(十进制计数器)来实现;( Х)10、环形计数器的有效状态个数,与其位数相同;( √ )1、 将十进制运算(-125-3)转换成带符号的8位(包括符号位)二进制补码运算,其结果为:①. 00000000 ②. 10000000 ③. 11111111 ④. 100000112、请问下列逻辑中,与(A ·B)/相同的逻辑是 ;①. A /+B / ②. A+B ③. A ·B ④. A /·B /3、已知逻辑F(ABC)=Σm (1,3,5,7),则下面的描述为正确的是:①. F(ABC)=ПM (0,2,4,6) ②. F=C③. F D =Σm (0,2,4,6) ④. F=A+B4、要实现8选1的数据选择器,则地址输入(选择输入)和多路数据端得个数分别为:①. 8、3 ②. 3 、8 ③. 8、8 ④. 3、35、如果实现5-32的译码器电路,需要 个74138(3-8译码器)来实现:①. 2 ②. 3 ③. 4 ④. 86、要实现256进制(模为256)的二进制计数器,需要 个74163(4位二进制加计数器)来实现①. 2 ②. 3 ③. 8 ④. 167、要实现有效状态数为8的环形计数器,则所需移位寄存器中的触发器个数为:①. 8 ②. 4 ③. 3 ④. 28、如果用触发器和门电路来实现12进制的计数器,则至少需要 个触发器:①. 2个 ②. 3个 ③. 4个 ④. 5个9、一个JK 触发器的驱动方程为X K J ==,则其逻辑功能与以下哪种触发器相同:①. JK 触发器 ②. SR 触发器③. D 触发器 ④. T 触发器10、下面关于移位寄存器型计数器的反馈函数的描述不正确的是:①. 反馈函数输入输出到移位寄存器的串行输入端②. 反馈函数是现态的函数③. 反馈函数中可以有存储单元④. 反馈函数是个组合逻辑单元1、下面有关带符号的二进制运算,描述正确的是,其中X 是被加数,Y 是加数,S 为和:①. [X]原码+[Y]原码=[S]原码 ②. [X]补码+[Y]补码=[S]补码③. [X]反码+[Y]反码=[S]反码 ④. [X]原码+[Y]原码=[S]补码2、逻辑函数式AC+ABCD+ACD /+A /C=①. AC ②. C ③. A ④. ABCD3、请问F=A ⊕B 的对偶式=DF①. A+B ②. A ⊙B ③. AB ④. AB /+A /B4、已知门电路的电平参数如下:,,,,V 8.0V V 0.2V V 5.0V V 7.2V max IL min IH max OL min OH ====请问其高电平的噪声容限为:①.2.2V ②.1.2V ③.0.7V ④.0.3V5、下面描述方法,对于一个组合逻辑而言,具备唯一性的是:①.逻辑函数式 ②.真值表③.卡诺图 ④.逻辑电路图6、下面电路中,属于时序逻辑电路的是:①.移位寄存器 ②.多人表决电路③.比较器 ④.码制变换器7、一个D 触发器的驱动方程为Q X D ⊕=,则其逻辑功能与以下哪种触发器相同:①. JK 触发器 ②. SR 触发器③. D 触发器 ④. T 触发器8、n 位环形计数器,其计数循环圈中的状态个(模)数为:①.n 个 ②.2n 个③.2n 个 ④.2n -1个9、n 位扭环计数器,其计数循环圈中的状态个(模)数为:①.n 个 ②.2n 个③.2n 个 ④.2n -1个10、如果用JK 触发器来实现T 触发器,则JK 触发器的驱动端需要做如下的连接:①.J=K=0②.J=K=T③.J=T;K=T’④.J=T’;K=T1、CMOS 集成逻辑OD 门,可以用以线与操作;(√ )2、三态门的附加控制端输入无效时,其输出也无效;( Х )3、三态门的三个状态分别为高电平、低电平和高阻态;(√ )4、施密特触发输入的门电路,当输入从高电平变换到低电平,和从低电平变换到高电平,它的输出变化轨迹相同;( Х )5、组合逻辑和时序逻辑的区别主要在于前者与时间无关,而后者时间的因素必须考虑进去;( √ )6、一个逻辑的函数式并不唯一,但是最简的与或表达式是唯一的;(Х )7、模拟信号是连续的,而数字信号是离散的;(√ )8、当两个组合逻辑的真值表相同是,则表明这两个逻辑是相等的;( √ )9、对于一个优先编码器而言,当输入多个有效时,其输出很难讨论;(Х )10、串行加法器比超前进位加法器速度更快,且电路更为简单;( Х)1、以下有关原码、反码和补码的描述正确的是:①.二进制补码就是原码除符号位外取反加1;②.补码即是就是反码的基础上再加1;③.负数的原码、反码和补码相同;④.正数的原码、反码和补码相同;2、下列逻辑表达式中,与D BC C A AB F ///1++=不等的逻辑是:①.///BC C A AB ++②.////D BC C A AB ++③.//C A AB +④.BD C A AB ++//3、已知门电路的电平参数如下:,,,,V 3.0V V 0.3V V 25.0V V 2.3V L I IH OL OH ≤≥≤≥请问其低电平的噪声容限为: ①. 0.05V ②. 0.2V ③. 2.95V ④. 2.7V4、下列逻辑中,与/A Y =相同的逻辑是:①.1A Y ⊕= ②.0A Y ⊕=③.A A Y ⊕= ④./)A A (Y ⊕=5、有如下所示波形图,已知ABC 为输入变量,Y 为输出变量,我们可以得到该逻辑的函数式为:①.AC AB Y += ②.C B A Y ++=③.C B A Y ⋅⋅= ④.///C B A Y ++=6、在同步状态下,下面哪种时序逻辑器件的状态更新仅仅发生在时钟触发沿来临的瞬间,并且状态更新的依据也仅仅取决于当时的输入情况:①.锁存器②.电平触发的触发器③.脉冲触发的触发器④.边沿触发的触发器器7、或非门所构成的SR 触发器的输入为S 和R ,则其工作时的约束条件为:①.1R S =+ ②.0R S =⋅③.0R S //=+ ④.R S =8、要实现有效状态数为8的扭环计数器,则所需移位寄存器中的触发器个数为:①.8 ②.4 ③.3 ④.29、下面的电路,属于组合逻辑的电路是:①.串行数据检测器②.多路数据选择器③.顺序信号发生器④.脉冲序列发生器10、下面哪些器件不能够实现串行序列发生器①.计数器和组合门电路②.数据选择器和组合门电路③.移位寄存器和组合门电路④.触发器和组合门电路1、如果逻辑AB=AC ,则B=C ;( Х)2、如果逻辑A+B=A+C ,则B=C ;(Х )3、如果逻辑AB+AC=1,则A=1;( √ )4、如果逻辑AB+AC=0,则A=0;(Х )5、若干个逻辑信号进行异或操作,如果这些信号中逻辑“1”的个数为奇数,则输出结果为1;( √ )6、A ⊕1=A /;( √ )7、A+A+A=A ·A ·A ;( √ )8、对于CMOS 集成门电路而言,与门的结构比与非门的结构更为简单一些;(Х )9、TTL 逻辑比CMOS 逻辑的运行功耗更低,所以更利于集成;(Х )10、影响CMOS 集成门电路的运行速度主要是传输延迟和转换时间;( √ )图2-5。

成都电子科技大学2005年中职高职计算机原理工硕考题考研真题考研试题

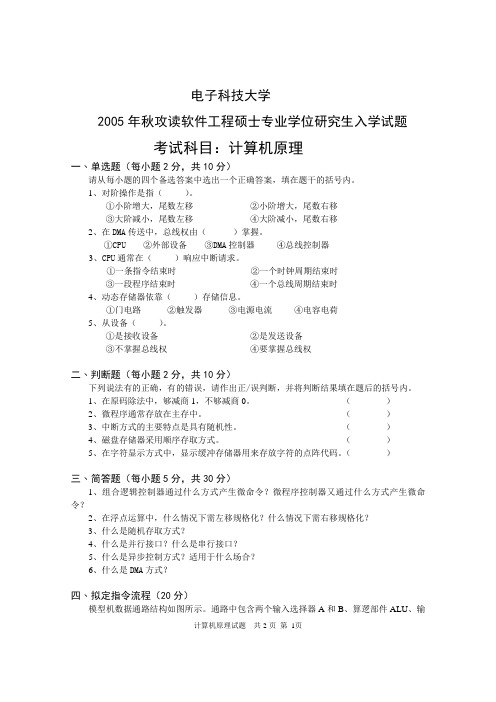

电子科技大学2005年秋攻读软件工程硕士专业学位研究生入学试题考试科目:计算机原理一﹑单选题(每小题2分,共10分)请从每小题的四个备选答案中选出一个正确答案,填在题干的括号内。

1、对阶操作是指()。

①小阶增大,尾数左移②小阶增大,尾数右移③大阶减小,尾数左移④大阶减小,尾数右移2、在DMA传送中,总线权由()掌握。

①CPU ②外部设备③DMA控制器④总线控制器3、CPU通常在()响应中断请求。

①一条指令结束时②一个时钟周期结束时③一段程序结束时④一个总线周期结束时4、动态存储器依靠()存储信息。

①门电路②触发器③电源电流④电容电荷5、从设备()。

①是接收设备②是发送设备③不掌握总线权④要掌握总线权二﹑判断题(每小题2分,共10分)下列说法有的正确,有的错误,请作出正/误判断,并将判断结果填在题后的括号内。

1、在原码除法中,够减商1,不够减商0。

()2、微程序通常存放在主存中。

()3、中断方式的主要特点是具有随机性。

()4、磁盘存储器采用顺序存取方式。

()5、在字符显示方式中,显示缓冲存储器用来存放字符的点阵代码。

()三﹑简答题(每小题5分,共30分)1、组合逻辑控制器通过什么方式产生微命令?微程序控制器又通过什么方式产生微命令?2、在浮点运算中,什么情况下需左移规格化?什么情况下需右移规格化?3、什么是随机存取方式?4、什么是并行接口?什么是串行接口?5、什么是异步控制方式?适用于什么场合?6、什么是DMA方式?四﹑拟定指令流程(20分)模型机数据通路结构如图所示。

通路中包含两个输入选择器A和B、算逻部件ALU、输计算机原理试题共2页第1页。

电子科大数字电路,期末试题101102半期考试试卷-答案

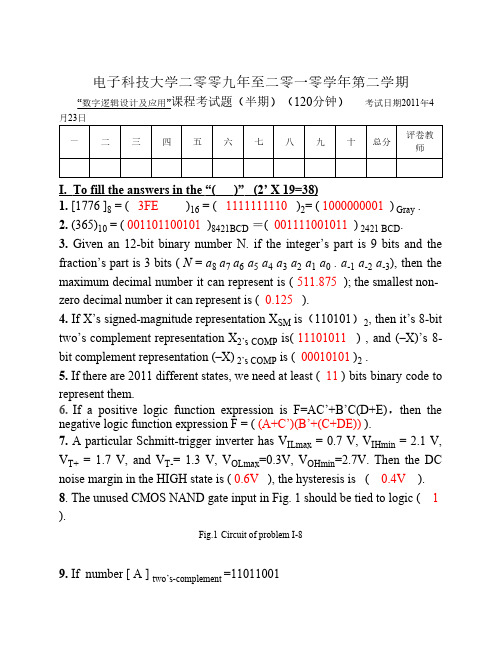

电子科技大学二零零九年至二零一零学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟)考试日期2011年4月23日一二三四五六七八九十总分评卷教师I. To fill the answers in the “( )” (2’ X 19=38)1. [1776 ]8 = ( 3FE )16 = ( 1111111110 )2= ( 1000000001 ) Gray .2. (365)10 = ( 001101100101 )8421BCD=( 001111001011 ) 2421 BCD.3.Given an 12-bit binary number N. if the integer’s part is 9 bits and the fraction’s part is 3 bits ( N = a8 a7 a6 a5 a4 a3 a2 a1 a0 . a-1 a-2 a-3), then the maximum decimal number it can represent is ( 511.875 ); the smallest non-zero decimal number it can represent is ( 0.125 ).4. If X’s signed-magnitude representation X SM is(110101)2, then it’s 8-bit two’s complement representation X2’s COMP is( 11101011 ) , and (–X)’s 8-bit complement representation (–X) 2’s COMP is ( 00010101 )2 .5. If there are 2011 different states, we need at least ( 11 ) bits binary code to represent them.6.If a positive logic function expression is F=AC’+B’C(D+E),then the negative logic function expression F = ( (A+C’)(B’+(C+DE)) ).7. A particular Schmitt-trigger inverter has V ILmax = 0.7 V, V IHmin = 2.1 V, V T+= 1.7 V, and V T-= 1.3 V, V OLmax=0.3V, V OHmin=2.7V. Then the DC noise margin in the HIGH state is ( 0.6V ), the hysteresis is ( 0.4V ). 8.The unused CMOS NAND gate input in Fig. 1 should be tied to logic ( 1 ).Fig.1Circuit of problem I-89. If number [ A ] two’s-complement =11011001and [ B] two’s-complement=10011101 , calculate[-A-B ]two’s-complement, [-A+B ]two’s-complement and indicate whether or not overflow occurs.[-A-B ] two’s-complement=[ 10001010 ], overflow: [ yes ][-A+B ] two’s-complement=[ 11000100 ], overflow: [ no ].10.The following logic diagram Fig.2 implements a function of 3-variable with a 74138. The logic function can be expressed as F (A,B,C) = ∑A,B,C ( 0,1,2 ).Fig.2 Circuit of problem I-10II. There is only one correct answer in the following questions.(3’ X 9 = 27)1. Which of the following Boolean equations is NOT correct? ( B )A) A+0=A B) A1 = AC) D)2. Suppose A2’s COMP =(1011),B2’s COMP =(1010),C2’s COMP =(0010). In the following equations, the most unlikely to produce overflow is( C )。

电子科技大学微机原理复试试题题库

电子科技大学微机原理复试试题微机原理第一章练习题及解一:单项选择题●若二进制数为010111.101,则该数的十进制表示为( B )。

A:23.5 B:23.625C:23.75 D:23.5125●若无符号二进制数为11000110,则该数的十进制表示为( A )。

A:198 B:70C:126 D:49●十进制数81的8421BCD码为( A )。

A:81H B:51HC:18H D:15H●11000110为二进制原码,该数的真值为( A )。

A:-70 B:+70C:-198 D:+198●11000110为二进制补码,该数的真值为( D )。

A:+198 B:-198C:+58 D:-58●01000110为二进制补码, 该数的真值为( A )。

A:+70 B:-70C:+58 D:-58●字符A的ASCII码为41H,字符a的ASCII码为( C )。

A:41H B:42HC:61H D:62H●字符A的ASCII码为41H,字符B的ASCII码为( B )。

A:41H B:42HC:61H D:62H●字符9 的ASCII码为( C )。

因为9与A之间有7个字符A:09H B:9C:39H D:99●8位二进制数的原码表值范围为( C )。

A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●8位二进制数的反码表值范围为( C )。

A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●8位二进制数的补码表值范围为( B )。

A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●8位二进制数的无符号数表值范围为( A )。

即无符号位A:0 ~ 255 B:-128 ~ +127C:-127 ~ +127 D:-128 ~ +128●n+1位符号数X的原码表值范围为( A )。

电子科技大学自动化学院研究生复试大纲

自动化工程学院复试考试大纲更新时间:2012/9/27 点击数:2585微机原理及数字电路复试考试大纲(闭卷)(200分)(推免生复试总分100分,微机原理和数字电路各占50%)对象:报考自动化工程学院080400仪器科学与技术、081100控制科学与工程、085203仪器仪表工程、085210控制工程的学生《微机原理及应用》(100分)一.参考书目:《微处理器系统结构及嵌入式系统设计(第二版)》李广军电子工业出版社《微机系统原理与接口技术》李广军电子科技大学出版社二.本大纲适合专业本大纲适用于自动化、仪器与测量技术等各类工科电子类非计算机专业。

三.内容要求1.概述要求内容:计算机发展历程,集成电路与SoC设计,先进的处理器技术,信息在计算机中的表示方法。

指令、程序的概念以及程序的执行过程。

嵌入式系统的概念、特点、组成、发展现状与趋势。

2.计算机系统的结构组成与工作原理要求内容:计算机系统的基本结构与组成,计算机系统的工作原理,微处理器体系结构的改进,计算机主要性能评测指标。

3.微处理器体系结构及关键技术要求内容:微处理器体系结构,处理器设计技术,指令系统设计,流水线技术,典型微处理体系结构。

4.总线技术与总线标准要求内容:总线技术概述、总线仲裁、总线操作与时序,总线标准(片内AMBA总线、PCI系统总线、异步串行通信总线。

5.存储器系统要求内容:存储器件的分类,半导体存储器的基本结构与性能指标;存储系统的层次结构,主存储器设计技术(存储器地址分配原则;译码电路设计方法;存储器接口设计设计;存储器系统设计方法)。

6.输入输出接口要求内容:输入/输出接口基础(接口和端口的概念,输入/输出接口功能与结构,端口的编址方法,端口地址的分配原则);接口地址译码;接口信息传输方式;并行接口,串行接口,定时/计数接口、AD/DA 接口的结构特点及设计要点7.ARM微处理器编程模型要求内容:ARM 内核体系结构,ARM 编程模型(处理器工作状态、处理器运行模式、寄存器组织、数据类型和储存格式、异常)。

电子科技大学《数字逻辑设计及应用》20春期末考试

电子科技大学《数字逻辑设计及应用》20春期末考试

一、单选题

1.EPROM是指()

A.随机读写存储器

B.只读存储器

C.可擦可编程只读存储器

D.电可擦可编程只读存储器

正确答案:C

2.下面各个组成部分,对于一个时序逻辑来说,不可缺少的是()

A.mealy型输出

B.输入

C.moore型输出

D.存储单元

正确答案:D

3.n级触发器构成的环形计数器,其有效循环的状态数为()

A.n个

B.2n个

C.2n-1个

D.2n个

正确答案:A

4.脉冲异步时序逻辑电路的输入信号可以是()

A.模拟信号

B.电平信号

C.脉冲信号

D.以上都不正确

正确答案:C

5.组合逻辑电路输出与输入的关系可用()描述

A.真值表

B.状态表

C.状态图

D.以上均不正确

正确答案:A

6.一块十六选一的数据选择器,其数据输入端有()个

A.16

B.8

C.4

D.2

正确答案:A

7.数字系统中,采用()可以将减法运算转化为加法运算

A.原码

B.补码

C.Gray码。