半导体工艺及芯片制造技术问题答案(全)

半导体工艺及芯片制造技术问题答案全

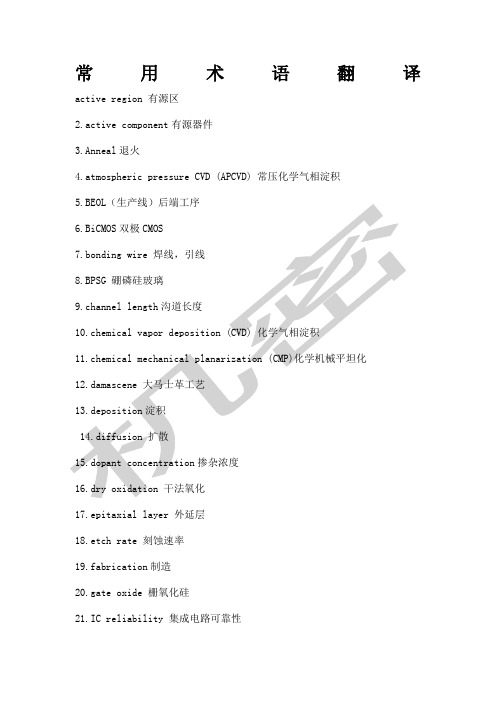

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺及芯片制造技术问题答案全

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7、bonding wire 焊线,引线8、BPSG 硼磷硅玻璃9、channel length沟道长度10、chemical vapor deposition (CVD) 化学气相淀积11、chemical mechanical planarization (CMP)化学机械平坦化12、damascene 大马士革工艺13、deposition淀积14、diffusion 扩散15、dopant concentration掺杂浓度16、dry oxidation 干法氧化17、epitaxial layer 外延层18、etch rate 刻蚀速率19、fabrication制造20、gate oxide 栅氧化硅21、IC reliability 集成电路可靠性22、interlayer dielectric 层间介质(ILD)23、ion implanter 离子注入机24、magnetron sputtering 磁控溅射25、metalorganic CVD(MOCVD)金属有机化学气相淀积26、pc board 印刷电路板27、plasma enhanced CVD(PECVD) 等离子体增强CVD28、polish 抛光29、RF sputtering 射频溅射30、silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1、什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2、写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试与拣选)Assembly and packaging (装配与封装)Final test(终测)3、写出半导体产业发展方向?什么就是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺及芯片制造技术问题答案(全)综述

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺及芯片制造技术问题答案(全)

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOSwire 焊线,引线硼磷硅玻璃length沟道长度vapor deposition (CVD) 化学气相淀积mechanical planarization (CMP)化学机械平坦化大马士革工艺淀积扩散concentration掺杂浓度oxidation 干法氧化layer 外延层rate 刻蚀速率制造oxide 栅氧化硅reliability 集成电路可靠性dielectric 层间介质(ILD)implanter 离子注入机sputtering 磁控溅射CVD(MOCVD)金属有机化学气相淀积board 印刷电路板enhanced CVD(PECVD) 等离子体增强CVD抛光sputtering 射频溅射on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路写出集成电路发展的五个时代及晶体管的数量(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万20世纪70年代前期到后期超大规模(VLSI) 10万到100万20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万20世纪90年代后期到现在2. 写出IC 制造的5个步骤(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向什么是摩尔定律(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺标准规范标准及其芯片制造技术问答规范标准答案(全)

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺及芯片制造技术问题答案全

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

提高芯片可靠性——严格控制污染。

降低成本——线宽降低、晶片直径增加。

摩尔定律指:IC 的集成度将每隔一年翻一番。

半导体工艺及芯片制造技术问题答案全

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺及芯片制造技术问题答案全

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺标准规范标准及其芯片制造技术问答规范标准答案(全)

常用术语翻译active region 有源区2.active component有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万 20世纪70年代前期到后期超大规模(VLSI) 10万到100万 20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万 20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

半导体工艺设计与芯片制造技术问题答案解析(全)

常用术语翻译active regi on 有源区2. active comp onent 有源器件3. A nn eal 退火4. atmospheric pressure CVD (APCVD)常压化学气相淀积5. BEOL (生产线)后端工序6. BiCMOS 双极CMOS7. bonding wire 焊线,引线8. BPSG硼磷硅玻璃9. cha nn el le ngth 沟道长度10. chemical vapor deposition (CVD)化学气相淀积11. chemical mecha ni cal pla narization (CMP化学机械平坦化12. damasce ne大马士革工艺13. deposition 淀积14. diffusion 扩散15. dopa nt concen trati on 掺杂浓度16. dry oxidati on 干法氧化17. epitaxial layer 夕卜延层18. etch rate刻蚀速率19. fabrication 制造20. gate oxide栅氧化硅21.IC reliability集成电路可靠性22.interlayer dielectric 层间介质(ILD )23.ion implanter离子注入机24. magnetron sputtering 磁控溅射25. metalorganic CVD(MOCVD)金属有机化学气相淀积26. pc board印刷电路板27. plasma en ha need CVD(PECVD)等离子体增强CVD28. polish 抛光29. RF sputteri ng 射频溅射30. silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1•什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

常用术语翻译active region 有源区2.active ponent有源器件3.Anneal退火4.atmospheric pressure CVD (APCVD) 常压化学气相淀积5.BEOL(生产线)后端工序6.BiCMOS双极CMOS7.bonding wire 焊线,引线8.BPSG 硼磷硅玻璃9.channel length沟道长度10.chemical vapor deposition (CVD) 化学气相淀积11.chemical mechanical planarization (CMP)化学机械平坦化12.damascene 大马士革工艺13.deposition淀积14.diffusion 扩散15.dopant concentration掺杂浓度16.dry oxidation 干法氧化17.epitaxial layer 外延层18.etch rate 刻蚀速率19.fabrication制造20.gate oxide 栅氧化硅21.IC reliability 集成电路可靠性22.interlayer dielectric 层间介质(ILD)23.ion implanter 离子注入机24.magnetron sputtering 磁控溅射25.metalorganic CVD(MOCVD)金属有机化学气相淀积26.pc board 印刷电路板27.plasma enhanced CVD(PECVD) 等离子体增强CVD28.polish 抛光29.RF sputtering 射频溅射30.silicon on insulator绝缘体上硅(SOI)第一章半导体产业介绍1. 什么叫集成电路?写出集成电路发展的五个时代及晶体管的数量?(15分)集成电路:将多个电子元件集成在一块衬底上,完成一定的电路或系统功能。

集成电路芯片/元件数产业周期无集成 1 1960年前小规模(SSI) 2到50 20世纪60年代前期中规模(MSI) 50到5000 20世纪60年代到70年代前期大规模(LSI) 5000到10万20世纪70年代前期到后期超大规模(VLSI) 10万到100万20世纪70年代后期到80年代后期甚大规模(ULSI) 大于100万20世纪90年代后期到现在2. 写出IC 制造的5个步骤?(15分)Wafer preparation(硅片准备)Wafer fabrication (硅片制造)Wafer test/sort (硅片测试和拣选)Assembly and packaging (装配和封装)Final test(终测)3. 写出半导体产业发展方向?什么是摩尔定律?(15分)发展方向:提高芯片性能——提升速度(关键尺寸降低,集成度提高,研发采用新材料),降低功耗。

提高芯片可靠性——严格控制污染。

降低成本——线宽降低、晶片直径增加。

摩尔定律指:IC 的集成度将每隔一年翻一番。

1975年被修改为:IC 的集成度将每隔一年半翻一番。

4. 什么是特征尺寸CD?(10分)最小特征尺寸,称为关键尺寸(Critical Dimension,CD)CD常用于衡量工艺难易的标志。

5. 什么是More moore定律和More than Moore定律?(10分)“More Moore”指的是芯片特征尺寸的不断缩小。

从几何学角度指的是为了提高密度、性能和可靠性在晶圆水平和垂直方向上的特征尺寸的继续缩小。

与此关联的3D结构改善等非几何学工艺技术和新材料的运用来影响晶圆的电性能。

“More Than Moore”指的是用各种方法给最终用户提供附加价值,不一定要缩小特征尺寸如从系统组件级向3D集成或精确的封装级(SiP)或芯片级(SoC)转移。

6. 名词解释:high-k; low-k; Fabless; Fablite; IDM; Foundry;Chipless(20分)high-k:高介电常数。

low-k:低介电常数。

Fabless:IC 设计公司,只设计不生产。

Fablite:轻晶片厂,有少量晶圆制造厂的IC公司。

IDM:集成器件制造商(IDM-Integrated Device Manufactory Co.),从晶圆之设计、制造到以自有品牌行销全球皆一手包办。

Foundry:标准工艺加工厂或称专业代工厂商。

Chipless:既不生产也不设计芯片,而是设计IP内核,授权给半导体公司使用。

7. 例举出半导体产业的8种不同职业并简要描述. (15分)1.硅片制造技师:负责操作硅片制造设备。

一些设备维护以及工艺和设备的基本故障查询。

2.设备技师:查询故障并维护先进设备系统,保证在硅片制造过程中设备能正确运行。

3.设备工程师:从事确定设备设计参数和优化硅片生产的设备性能。

4.工艺工程师:分析制造工艺和设备的性能以确定优化参数设置。

5.实验室技师:从事开发实验室工作,建立并进行试验。

6:成品率/失效分析技师:从事与缺陷分析相关的工作,如准备待分析的材料并操作分析设备以确定在硅片制造过程中引起问题的根源。

7.成品率提高工程师:收集并分析成品率及测试数据以提高硅片制造性能。

8.设施工程师:为硅片制造厂的化学材料、净化空气及常用设备的基础设施提供工程设计支持。

第二章半导体材料特性第五章半导体制造中的化学品第六章硅片制造中的玷污控制1.最通常的半导体材料是什么?该材料使用最普遍的原因是什么?(第二章)(10分)答:最通常的半导体材料是硅。

原因:1.硅的丰裕度;2.更高的融化温度允许更高的工艺容限;3.更宽的工作温度范围;4.氧化硅的自然生成.2.砷化镓相对于硅的优点是什么?(第二章)(5分)答:砷化镓具有比硅更高的电子迁移率,因此多数载流子也移动得比硅中的更快。

砷化镓也有减小寄生电容和信号损耗的特性。

这些特性使得集成电路的速度比由硅制成的电路更快。

GaAs器件增进的信号速度允许它们在通信系统中响应高频微波信号并精确地把它们转换成电信号。

硅基半导体速度太慢以至于不能响应微波频率。

砷化镓的材料电阻率更大,这使得砷化镓衬底上制造的半导体器件之间很容易实现隔离,不会产生电学性能的损失。

3.描述在硅片厂中使用的去离子水的概念。

(第五章)(5分)答:去离子水:在半导体制造过程中广泛使用的溶剂,在它里面没有任何导电的离子。

DI Water 的PH值为7,既不是酸也不是碱,是中性的。

它能够溶解其他物质,包括许多离子化合物和供价化合物。

当水分子(H2O)溶解离子化合物时,它们通过克服离子间离子键使离子分离,然后包围离子,最后扩散到液体中。

4.例举出硅片厂中使用的五种通用气体。

(第五章)(5分)答:氧气(O2)、氩气(Ar)、氮气(N2)、氢气(H2)和氦气(He)5.对净化间做一般性描述。

(第六章)(10分)答:净化间是硅片制造设备与外部环境隔离,免受诸如颗粒、金属、有机分子和静电释放(ESD)的玷污。

一般来讲,那意味着这些玷污在最先进测试仪器的检测水平范围内都检测不到。

净化间还意味着遵循广泛的规程和实践,以确保用于半导体制造的硅片生产设施免受玷污。

6.什么是硅片的自然氧化层?由自然氧化层引起的三种问题是什么?(第六章)(10分)答:自然氧化层:如果曝露于室温下的空气或含溶解氧的去离子水中,硅片的表面将被氧化。

这一薄氧化层称为自然氧化层。

硅片上最初的自然氧化层生长始于潮湿,当硅片表面暴露在空气中时,一秒钟内就有几十层水分子吸附在硅片上并渗透到硅表面,这引起硅表面甚至在室温下就发生氧化。

自然氧化层引起的问题是:①将妨碍其他工艺步骤,如硅片上单晶薄膜的生长和超薄氧化层的生长。

②另一个问题在于金属导体的接触区,如果有氧化层的存在,将增加接触电阻,减少甚至可能阻止电流流过。

③对半导体性能和可靠性有很大的影响7.例举硅片制造厂房中的7种玷污源。

(第六章)(10分)答:硅片制造厂房中的七中沾污源:(1)空气:净化级别标定了净化间的空气质量级别,它是由净化室空气中的颗粒尺寸和密度表征的;(2)人:人是颗粒的产生者,人员持续不断的进出净化间,是净化间沾污的最大来源;(3)厂房:为了是半导体制造在一个超洁净的环境中进行,有必要采用系统方法来控制净化间区域的输入和输出;(4)水:需要大量高质量、超纯去离子水,城市用水含有大量的沾污以致不能用于硅片生产。

去离子水是硅片生产中用得最多的化学品(5)工艺用化学品:为了保证成功的器件成品率和性能,半导体工艺所用的液态化学品必须不含沾污;(6)工艺气体:气体流经提纯器和气体过滤器以去除杂质和颗粒;(7)生产设备:用来制造半导体硅片的生产设备是硅片生产中最大的颗粒来源。

8.解释空气质量净化级别。

(第六章)(5分)答:净化级别标定了净化间的空气质量级别,它是由净化室空气中的颗粒尺寸和密度表征的。

这一数字描绘了要怎样控制颗粒以减少颗粒玷污。

净化级别起源于美国联邦标准2009.如果净化间级别仅用颗粒数来说明,例如1级净化间,则只接受1个0.5um的颗粒。

这意味着每立方英尺中尺寸等于或大于0.5um的颗粒最多允许一个。

9.描述净化间的舞厅式布局。

(第六章)(10分)答:净化间的舞厅式布局为大的制造间具有10000级的级别,层流工作台则提供一个100级的生产环境。

10.解释水的去离子化。

在什么电阻率级别下水被认为已经去离子化?(第六章)(10分)答:用以制造去离子水的去离子化过程是指,用特制的离子交换树脂去除电活性盐类的离子。

18MΩ-cm电阻率级别下水被认为已经去离子化。

11.描述RCA清洗工艺。

(第六章)(10分)答:工业标准湿法清洗工艺称为RCA清洗工艺,由美国无线电公司(RCA)于20世纪60年代提出。

RCA湿法清洗由一系列有序的浸入两种不同的化学溶液组成:1号标准清洗液(SC-1)和2号标准清洗液(SC-2)。

SC-1的化学配料为NH4OH/H2O2/H2O这三种化学物按1:1:5到1:2:7的配比混合,它是碱性溶液,能去除颗粒和有机物质,SC-1湿法清洗主要通过氧化颗粒或电学排斥起作用。

SC-2的组分是HCL/H2O2/H2O,按1:1:6到1:2:8的配比混合,用于去除硅片表面的金属。

改进后的RCA清洗可在低温下进行,甚至低到45摄氏度12.例出典型的硅片湿法清洗顺序。

(第六章)(10分)硅片清洗步骤:(1)H2SO4/H2O2(piranha):有机物和金属;(2)UPW清洗(超纯水):清洗;(3)HF/H2O(稀HF):自然氧化层;(4)UPW清洗:清洗;(5)NH4OH/H2O2/H2O(SC-1):颗粒;(6)UPW清洗:清洗;(7)HF/H2O:自然氧化层;(8)UPW清洗:清洗;(9)HCL/H2O2/H2O(SC-2):金属;(10)UPW清洗:清洗;(11)HF/H2O:自然氧化层;(12)UPW清洗:清洗;(13)干燥:干燥第三章器件技术基础1.按构成集成电路基础的晶体管分类可以将集成电路分为哪些类型?每种类型各有什么特征?(40分)答:分为三种,双极集成电路,MOS集成电路,双极-MOS(BiMOS)集成电路。