(完整版)基于FPGA的psk调制

基于FPGA的MSK调制解调器设计与应用

邮局订阅号:82-946360元/年技术创新PLD CPLD FPGA 应用《PLC 技术应用200例》您的论文得到两院院士关注基于FPGA 的MSK 调制解调器设计与应用Designing and Application of MSK Modulator and Demodulator basade on FPGA(常州工学院)肖闽进XIAO Min-jin摘要:提出了一种基于FPGA 的数字MSK 调制解调器设计方法,应用VHDL 语言进行了模块设计和时序仿真。

硬件部分在Altera 公司EP2C15AF256C8N FPGA 上实现。

结果表明,数字MSK 调制解调器具有相位连续,频带利用率高的优点。

关键词:现场可编程逻辑阵列;最小频移键控;调制;时序仿真中图分类号:TN911.3;TP302.1文献标识码:A Abstract:A method for designing Minimum Frequency Shift Keying modulator and demodulate is developed.The VHDL Models aredesigned and simulated,the results show the MSK enjyos the characteristics of phase continuation and high band utilization.Key words:FPGA;MSK;Modulator;Simulation文章编号:1008-0570(2009)09-2-0139-02数字调制解调器在点对点的数据传输中得到了广泛的应用。

通常的二进制数字调制解调器是建立在模拟载波上的,在电路实现时需要模拟信号源,这会给全数字应用场合带来不方便。

本文分析了MSK(最小频移键控)数字调制信号特征,提出一种全数字固定数据速率MSK 调制解调器的设计方法,应用VHDL 语言进行了模块设计和时序仿真。

PSK(DPSK)调制与解调资料讲解

P S K(D P S K)调制与解调实验题目——PSK(DPSK)调制与解调一、实验目的1、掌握绝对码、相对码的概念以及它们之间的变换关系和变换方法。

2、掌握产生PSK(DPSK)信号的方法。

3、掌握PSK(DPSK)信号的频谱特性。

二、实验内容1、观察绝对码和相对码的波形。

2、观察PSK(DPSK)信号波形。

3、观察PSK(DPSK)信号频谱。

4、观察PSK(DPSK)相干解调器各点波形。

三、实验仪器1、信号源模块2、数字调制模块3、数字解调模块4、20M双踪示波器5、导线若干四、实验原理1、2PSK(2DPSK)调制原理2PSK信号是用载波相位的变化表征被传输信息状态的,通常规定0相位载波和π相位载波分别代表传1和传0,其时域波形示意图如图所示。

2PSK 信号是用载波的不同相位直接去表示相应的数字信号而得出的,在这种绝对移相的方式中,由于发送端是以某一个相位作为基准的,因而在接收系统也必须有这样一个固定基准相位作参考。

如果这个参考相位发生变化,则恢复的数字信息就会与发送的数字信息完全相反,从而造成错误的恢复。

这种现象常称为2PSK 的“倒π”现象,因此,实际中一般不采用2PSK 方式,而采用差分移相(2DPSK )方式。

2DPSK 方式即是利用前后相邻码元的相对载波相位值去表示数字信息的一种方式。

如图为对同一组二进制信号调制后的2PSK 与2DPSK 波形。

0 0 0 1 0 1 1 1 0 0 0 1 1 1 0 0 1数字信息(绝对码)PSK 波形DPSK 波形相对码从图中可以看出,2DPSK 信号波形与2PSK 的不同。

2DPSK 波形的同一相位并不对应相同的数字信息符号,而前后码元相对相位的差才唯一决定信息符号。

这说明,解调2DPSK 信号时并不依赖于某一固定的载波相位参考值。

只要前后码元的相对相位关系不破坏,则鉴别这个关系就可以正确恢复数字信息,这就避免了2PSK 方式中的“倒π”现象发生。

FPGA课程设计 二进制相位键控(PSK)调制器与解调器设计

附件1:学号:课程设计二进制相位键控(PSK)调制题目器与解调器设计学院信息工程学院专业通信工程班级姓名指导教师陈适2014年 6月18日课程设计任务书学生姓名:专业班级:通信工程指导教师:陈适工作单位:信息工程学院题目:二进制相位键控(PSK)调制器与解调器设计初始条件:(1) Quartus II、ISE 等软件;(2)课程设计辅导书:《Xilinx FPGA 设计与实践教程》(3)先修课程:数字电子技术、模拟电子技术、通信原理主要任务:(1)掌握2CPSK、2DPSK的调制与解调原理;(2)掌握仿真软件Quartus II的使用方法;(3)完成对2CPSK、2DPSK的调制与解调仿真电路设计,并对仿真结果进行分析。

时间安排:(1)2014 年6月11日--2014 年6月18日理论设计、仿真设计地点:鉴主13 楼通信工程综合实验室、鉴主15 楼通信工程实验室。

(2)2014 年6 月18 日进行理论答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日移动通信迅速发展的得以实现,离不开数字处理技术。

其中,数字调制与解调技术在通信领域中发挥着重大作用。

为了使数字信号在带通信道中传输,必须使用数字基带信号对载波进行调制,以使信号与信道的特性匹配,再在接收端通过解调恢复出原始数字信号,实现数字信息的传递。

相移键控(PSK)就是数字信号调制的一种有用并且广泛使用的方式。

为了很好地完成本次FPGA课程设计,我对2CPSK、2DPSK的调制与解调原理进行了深入的了解和研究;利用仿真软件Quartus II,对2CPSK、2DPSK 进行调制与解调的设计和仿真,并对仿真结果进行了分析。

关键词:PSK;Quartus II;数字调制;仿真Realizing the rapid development of mobile communication, cannot do without the digital processing technology. additionly, digital modulation and demodulation technology plays an important role in the field of communication. In order to make the digital signaltransmit in a communication channel, digital baseband signal must be on the carrier modulation, so that the characteristics of the signal must match with channel .Then the receiver through demodulation restores the original digital signal by demodulation, so transmission of digital information is accomplished. Phase shift keying (PSK)is one kind of digital signal modulation that is useful and widely . In order to complete the FPGA curriculum design, I have conducted a deep study and research about the modulation and demodulation principle of 2CPSK and 2DPSK .by using the simulation software Quartus II,I design and emulate the modulation and demodulation of 2CPSK and 2DPSK, and the simulation results are analyzed.Key word:PSK;Quartus II;digital modulation;emulation目录摘要 (I)Abstract (II)1. 前言 (1)2. 基本原理及数学模型 (2)2.1 相移键控PSK的原理 (2)2.2 2CPSK的调制与解调原理 (2)2.2.1 2CPSK的调制 (2)2.2.2 2CPSK的解调 (4)2.3 2DPSK的调制与解调原理 (4)2.3.1 2DPSK的调制 (4)2.3.2 2DPSK的解调 (7)2.4 2 CPSK和2DPSK的比较 (8)3. 仿真结果记录与分析 (10)3.1 仿真环境介绍 (10)3.2 仿真波形结果分析 (10)3.2.1 2CPSK的调制与解调 (11)3.2.2 2DPSK的调制与解调 (12)3.3 仿真生成的电路图 (13)3.3.1 2CPSK调制与解调仿真生成的RTL视图及电路图 (13)3.3.3 2DPSK调制与解调仿真生成的RTL视图及电路图 (15)4. 设计及实现过程中遇到的问题 (16)5. 心得体会 (18)参考文献 (19)附录 (20)附录1 2CPSK调制器的程序代码 (20)附录2 2CPSK解调器的程序代码 (21)附录3 2DPSK调制器绝对码转换为相对码的程序代码 (22)附录4 2DPSK解调器相对码转换为绝对码的程序代码 (23)1. 前言调制解调在通信系统中具有十分重要的作用。

eda

课程设计说明书学生姓名:张燕学号:0906220220学院:信息工程学院班级: 通信092题目:指导教师:职称:年月日一 摘 要基于FPGA 的调制和解调数字信号的方法有多种,包括2ASK 、2FSK 、2PSK 等,本文基于FPGA 芯片,采用VHDL 语言,利用层次化、模块化设计方法,提出了一种2FSK 调制解调器的实现方法。

仿真结果表明此设计方案是可行的,系统具有较高的实用性和可靠性。

二 引言随着通信理论和计算机技术的发展,数字信号的调制、解调和识别是高科技的发展趋势。

调制解调效果的好坏直接关系着通信系统的性能。

而数字解调技术的关键在于瞬时幅度,瞬时频率和瞬时相位参数的准确估计。

基带数字信号在远距离传输,特别是在有限带宽的高频信道如无线或光纤信道上传输时,必须对数字信号进行载波调制。

数字信号对载波频率调制称为频移键控即FSK 。

FSK 是用不同频率的载波来传送数字信号,是信息传输中使用较早的一种调制方式。

它的主要特点是:抗干扰能力较强,不受信道参数变化的影响,传输距离远,误码率低,抗噪声与抗衰减的性能较好,实现起来较容易等。

在中低速数据传输中,特别是落信道中传输数据时,有着广泛的应用。

但传统的FSK 调制解调器采用"集成电路+连线"的硬件实现方式进行设计,集成块多、连线复杂且体积较大,特别是相干解调需要提取载波,设备相对比较复杂,成本高。

基于FPGA 的2FSK 调制和解调设计过程采用VHDL 语言实现,设计灵活、修改方便,具有良好的可移植性及产品升级的系统性。

三 系统设计 (一)FSK 信号调制 1、 FSK 信号调制原理频移键控即FSK 主要通过数字基带信号控制载波信号的频率来传递数字信息。

在二进制情况下,"1"对应于载波频率W 1,"0"对应于载波频率W 2,但是二者振幅和初始相位不变,表达式为⎭⎬⎫⎩⎨⎧++=)sin()cos()(2211φφt w A t w A t s式中A 为常数表示码元的包络是矩形脉冲。

通过FPGA生成Gold码并进行PSK调制以实现扩...

IO B1 l0 矗0 B0

信道进行传输。

4实验结果及分析

图5

图6

4.1 Gold码的设计及其仿真 通过MATLAB中的DSP Builder画出Gold码的

产生原理图,用数字信号发生器来代替信源码,使信

图7

万方数据

通信技术及应用

有线电视技术

源码与伪随机Gold码进行异或,即对信源码进行了 扩频。如图4所示。

产生Gold码的方法有两种,它是用一对优选的 周期和速率均相同的m序列的移位寄存器串联或并 联后得到的。通常多使用并联结构,即将两个m序列 进行模2和后输出。

其原理图如图2所示。 以n=6级为例,其结构图如图3所示。

万方数据

通信技术及应用

图2

有线电视技术

Gold序列的主要性质有以下三点: Gold序列具有三值自相关特性,其旁瓣的极大值 满足优选对的条件。 两个m序列优选对不同移位相加产生的新序列 都是Gold序列。因为总共有2n—1个不同的相对位 移,加上原来的两个Ill序列本身,所以,两个m级移 位寄存器可以产生2n+1个Gold序列。因此,Gold序 列的序列数比m序列数多得多。 同类Gold序列互相关特性满足优选对条件,其 旁瓣的最大值较低。 本次试验就是以六级Gold码为例,通过FPGA 产生并进行了仿真。

万方数据

通过FPGA生成Gold码并进行PSK调制以实现扩频通信

作者: 作者单位: 刊名:

英文刊名: 年,卷(期):

刘少伟, 汤锋 国家广电总局节目传输中心

有线电视技术 CABLE TELEVISION TECHNOLOGY 2009,16(8)

本文链接:/Periodical_yxdsjs200908019.aspx

基于FPGA的FSK调制解调器设计与实现

基于FPGA的FSK调制解调器设计与实现FSK调制解调器是一种常用的数字通信技术,可用于数据传输、无线通信等领域。

本文将介绍基于FPGA的FSK调制解调器的设计和实现,包括原理介绍、系统设计、硬件实现和性能分析等方面。

一、引言FSK调制解调器是一种数字通信系统,它通过改变载波频率的方式来传输数字信号。

本文基于FPGA实现FSK调制解调器,利用FPGA 的灵活性和可重构性,提供了一种高效、可靠的数字通信解决方案。

二、FSK调制解调原理介绍FSK调制解调器是通过将数字信号映射到两个不同频率的载波上,实现信息传输的。

调制过程中,二进制数据0和1分别对应两个特定频率的载波,解调过程中通过判断输入信号的频率来还原原始数据。

三、系统设计1. FSK调制器在FPGA中设计FSK调制器,需要使用相应的调制算法将数字信号转换为两个不同频率的载波。

可以采用数字频率合成技术合成两个不同频率的信号,并通过逻辑电路实现相应的调制功能。

2. FSK解调器FSK解调器的设计目标是通过输入信号的频率变化来判定数字信号的0和1。

可以采用数字滤波器和频率判决电路实现解调功能,将输入的频率信号转换为相应的数字信号。

四、硬件实现1. FPGA配置基于FPGA的FSK调制解调器的硬件实现,首先需要将相应的调制解调算法和电路设计编写为硬件描述语言如VHDL,并经过综合、布局布线等步骤生成比特流。

2. ADC和DAC为了接收和发送模拟信号,需要使用ADC(模数转换器)将模拟信号转换为数字信号,并使用DAC(数模转换器)将数字信号转换为模拟信号。

3. 时钟模块与控制模块为了保持系统的同步和稳定性,需要设计时钟模块和控制模块。

时钟模块用于在固定的时间间隔内,对输入信号进行采样和调制;控制模块用于控制时钟、数据流等系统参数,保证系统的正常运行。

五、性能分析1. 调制误差分析通过对比输入信号与调制后的信号的频谱图,可以评估FSK调制器的性能,主要包括频率偏移、频谱扩展等指标。

基于FPGA的PSK解调器实现

有关数字解调器及其 FPGA ( f ie ld prog ra mm ab le gate array)实现已有大量的研究 , 基于 FPGA 的数字 解调器与模拟电路解调器相比, 具有功耗低、 结构简 单、 性能优越等特点, 故在实际工程中得到了广泛的 应用。文献 [ 1] 提出了一种 QPSK ( quadrature phase sh ift keying) 数字解调器, 而通过对此解调器部分电

I mplem entation of FPGA based PSK demodulator

LV Y i bo , FAN X in gang , X I E Dong fu

1 2 3

( 1 K ey Lab ofM ob ile C omm un icat ion in Ch ongq ing, Chongqing U n ivers ity of Posts and T elecommun ications , Chongqing 400065 , P. R. Ch in a ; 2 D epartm ent of E lectronic In for m ation Eng ineering, G uangzhou C ity C onst r u ct ion College , Conghua 510925, P. R. Ch ina 3 D epartm ent of E lectron ic eng ineering, X iam en U n ivers ity, X iam en 361008 , P. R. Ch in a)

2k - L 0 2 3 L0 [ 1- ( ) ], k = 1, 2 , 2 2 L0 - 1 L0 ( 5) ( k ) 为平滑函数 ; L 0 = 36 表示导频 ( k ) 定为一固

实验10、PSK调制解调

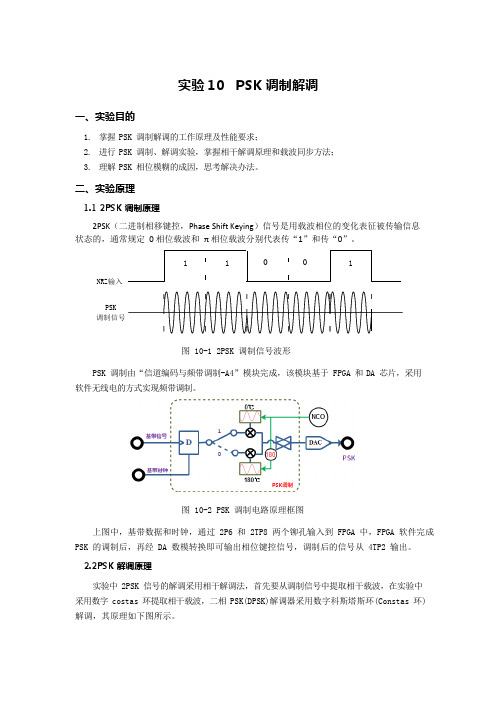

实验 10 PSK 调制解调一、实验目的1.掌握 PSK 调制解调的工作原理及性能要求;2.进行 PSK 调制、解调实验,掌握相干解调原理和载波同步方法;3.理解 PSK 相位模糊的成因,思考解决办法。

二、实验原理1.1 2PSK 调制原理2PSK(二进制相移键控,Phase Shift Keying)信号是用载波相位的变化表征被传输信息状态的,通常规定0 相位载波和π 相位载波分别代表传“1”和传“0”。

1 1 0 0 1NRZ输入PSK调制信号图 10-1 2PSK 调制信号波形PSK 调制由“信道编码与频带调制-A4”模块完成,该模块基于 FPGA 和 DA 芯片,采用软件无线电的方式实现频带调制。

图 10-2 PSK 调制电路原理框图上图中,基带数据和时钟,通过 2P6 和 2TP8 两个铆孔输入到 FPGA 中,FPGA 软件完成PSK 的调制后,再经 DA 数模转换即可输出相位键控信号,调制后的信号从 4TP2 输出。

2.2PSK 解调原理实验中 2PSK 信号的解调采用相干解调法,首先要从调制信号中提取相干载波,在实验中采用数字 costas 环提取相干载波,二相 PSK(DPSK)解调器采用数字科斯塔斯环(Constas 环)解调,其原理如下图所示。

图 10-3 数字科斯塔斯特环原理图设已调信号表达式为 s (t ) = A 1 ⨯cos(ωt +ϕ(t ))(A 1 为调制信号的幅值),经过乘法器与载波信号 A 2 cos ωt (A2 为载波的幅值)相乘,得:e (t ) = 1A A [cos(2ωt + ϕ(t )) + cos ϕ(t )] 02 1 21可知,相乘后包括二倍频分量 2A 1 A 2 cos(2ωt + ϕ(t )) 和cos ϕ(t ) 分量(ϕ(t ) 为时间的函数)。

因此,需经低通滤波器除去高频成分cos(2ωt +ϕ(t )) ,得到包含基带信号的低频信号,然后同向端和正交端两路信号相乘,其差值作为环路滤波器的输入,然后控制 VCO 载波频率和相位,得到和调制信号同频同相的本地载波。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

c<=7'b1000000;

else

begin

c[2]<=c[1];

c[3]<=c[2];

c[4]<=c[3];

c[5]<=c[4];

c[6]<=c[5];

c[7]<=c[6];

c[1]<=c[2Fc[3Fc[4Fc[7];

end

end

assign dataoutm = c[7];

Controller CONTROLLER( .clk(clk),.reset_n(reset_n),.dataoutm(dataoutm), .address(address),.clk_DA(clk_DA),.blank_DA_n( blank_DA_n),.sync_DA_n(sync_DA_n) );

parameter N= 128;

always@(posedge clk or negedge reset_n)if(! reset_n)

begin count<=1'b0; clk1<=1'b0;

end

else if(count< 63)

begin count<=count+1'b1;

end else begin count<=1'b0; clk1<=~clk1;

西南交通大学

信息科 学与技 术学院

通信工程专业

工程实习报告

(

年级:2010

学号:20100147

姓名:刘 妍

专业:通信工程

二零一三年七月

(psk

基本原理

PSK调制原理

相移键控(PSK):一种用载波相位表示输入信号信息的调制技术。移相键控分为绝对移

相和相对移相两种 为例,取码元为“ 调载波反相;“1PSK调制原理图:

。以未调载波的相位作为基准的相位调制叫作绝对移相。以二进制调相

1”时,调制后载波与未调载波同相;取码元为“0”时,调制后载波与未 ”和“0”时调制后载波相位差180度。

S 3.fl PSK

二、详细设计

顶层模块module bpsk( clk, reset_n, clk_DA, blank_DA_n, sync_DA_n, dataout, dm_out

end else

begin

address_data1<=address_data1+7'b000_0001;//地址依次加一

address_data2<=address_data2+7'b000_0001;

end

end

always@(posedge clk or negedge reset_n)begin

// begin

//

//

//

case(dataoutm)

1'b0:

//

begin

address_data=address_data2;

end

//

//

1'b1:

//

//

//

//

begin

address_data=address_data1;

end

default:begin

address_data=5'bzzzzz;

LookUpTable LOOKUPTABLE(.clk(clk),.reset_n(reset_n),

.address(address),

.dataout(dataout) );

depsk depsk( .clk (clk),

.reset_n (reset_n), .data (dataout),

wire

clk1 ;

wire[ 7 :

0 ] dataout;

counter

COUNTER(

.clk

( clk ),

.reset_n (reset_n),

.count (count),

.clk1 ( clk1 )

h

_Seq PN_SEQ(

.clk1

( clk1 ),

.reset_n(reset_n),.dataoutm(dataoutm) );

end endmodule M序列产生模块module PN_Seq(clk1,reset_n,dataoutm);

input clk1; input reset_n;

output dataoutm;

reg[ 7 : 1 ]c;

always@(posedge clk1 or negedge reset_n)begin

end

//

endcase

//

end

always@(posedge clk or negedge resddress_data1<=7'b011_1111;//000_0000;//

address_data2<=7'b000_0000;//111_0011;//

);

input

clk ;

input

reset_n ;

output

clk_DA ;

output

blank_DA_n;

output

sync_DA_n ;

output[ 7

: 0 ] dataout ;

output[ 7

: 0 ] dm_out;

wire[ 6 :

0 ] address ;

wire

dataoutm ;

if(!reset_n) address_data<=7'b000_0000;//赋初值

else if(!dataoutm)

address_data<=address_data2;〃如果m序列输出为0,则为address_data2值

endmodule

控制器模块

module Controller( clk, reset_n, dataoutm, address, clk_DA, blank_DA_n, sync_DA_n

);

inputclk

inputreset_n

input dataoutm

output [ 6 : 0 ] address

output output output reg [ 6

clk_DA ; sync_DA_n ; blank_DA_n ;

0 ] address_data1;

reg [ 6 : 0 ] address_data2; reg [ 6 : 0 ] address_data;

// always @(dataoutm)

.dataout (dm_out)

);

endmoduleendmodule分频模块module counter(clk,reset_n,count,clk1);

input clk,reset_n; output clk1; output[6:0] count;

reg clk1; reg[6:0] count;