74ls74中文资料

74l系列型号逻辑功能描述

74l系列型号逻辑功能描述

74L系列是一种高性能低功耗半导体器件,由集成在芯片中的多个晶体管和电子元件

构成。

这种器件具有多种逻辑功能,可用于各种数字电路应用中。

在本篇文章中,我们将

对74L系列的一些常见型号进行逻辑功能描述。

1. 74LS00

74LS00是一种四输入NAND门。

它具有四个输入端口和一个输出端口。

当所有输入端

口电平都为高电平时,输出端口电平为低电平。

当任意一个输入端口电平为低电平时,输

出端口电平为高电平。

74LS74是一种双稳态触发器。

它具有两个输入端口和两个输出端口。

当输入端口电平变化时,输出端口的状态会保持不变,直到另一个输入端口电平变化。

总之,74L系列具有多种逻辑功能,包括AND门、OR门、NAND门、NOR门、XOR门和触发器等。

这些器件广泛应用于各种数字电路、计算机芯片、通讯设备、工业自动化等领域,为现代电子技术的发展做出了重要贡献。

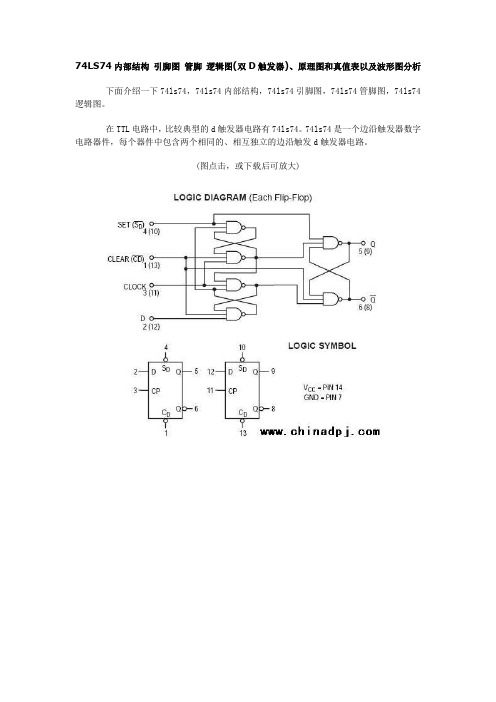

74LS74资料

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

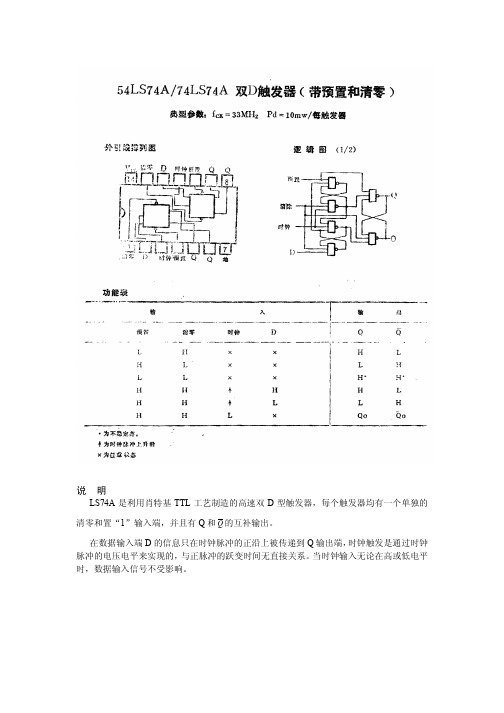

74LS74A中文资料

说明

LS74A 是利用肖特基 TTL 工艺制造的高速双 D 型触发器,每个触发器均有一个单独的 清零和置“1”输入端,并且有 Q 和 Q 的互补输出。

在数据输入端 D 的信息只在时钟脉冲的正沿上被传递到 Q 输出端,时钟触发是通过时钟 脉冲的电压电平来实现的,与正脉冲的跃变时间无直接关系。当时钟输入无论在高或低电平 时,数据输入信号不受影响。

IOL=4mA IOL=8mA

VCC =最小 VIL =最大 VIH =2.0V

VCC =最大 VI =7.0V

VCC =最大 VI =2.7V

VCC =最大 VCC =最大 VCC =最大

VI =0.4V VO =0V VCK =0V 注

VCC =5.0V CL=15pF RL=2kΩ

元器件交易网

规范表

符号

参数名称

VCC 电源电压

54 74

IOH 输出高电平电流

IOL

输出低电平电流 54

74

fCK 时钟频率

tW 脉冲宽度

高电平数据

tsu

建立时间

低电平数据

th

维持时间

TA 工作温度

54 74

参 最小 4.5 4.75

0 25 25↑ 20↑ 5↑ -55 0

数 典型

5 5

值 最大 5.5 5.25 -400

4 8 25

125 70

单位

V μA mA MHz ns ns ns ℃

符号

参数名称

VIH 输入高电平

54

VIL 输入低电平

74

VCD 输入钳位电压

54

VOH 输出高电平

74

参数值 最小 典型 最大

74LS74触发器知识讲解

74LS74触发器一、实验目的:1. 测试触发器的工作原理。

2. 掌握触发器相关电路设计方法。

二、实验原理:触发器是构成时序逻辑电路的基本单元。

它是一种具有记忆功能,能储存1位二进制信息的逻辑电路。

触发器特点:具有两个稳定的状态,用来表示电路的两个逻辑状态;②在输入信号作用下,可以被置成“0”态或“1”状态;③当输入信号撤消后,所置成的状态能够保持不变。

三、实验内容:1、测试74LS74D触发器的逻辑功能。

电路图如图所示:字发生器内参:逻辑分析仪分析图:2、测试74LS76JK触发器的逻辑功能,并将其填入下表。

电路图如图所示:字发生器内参:逻辑分析仪分析图:3、思考题:试设计一个3人抢答器,要求如下:每位参赛者有一个按钮;主持人有一个复位按钮,能够完成电路的复位;当其中一位参赛者按动按钮对应的数码管亮之后,其他参赛者再按动按钮无效。

设计说明:当其中一个触发器工作时,~1Q端输出低电平,与该端相连的LED发光,数码管显示相应的数字(1、2、3)。

这时该低电平将与非门锁住,使时钟脉冲无法到达各触发器,其他触发器便不能工作。

当给清零信号时,~1Q端输出高电平,与该端相连的LED 熄灭,数码管显示0,与非门重新打开,时钟脉冲进入各触发器。

如此循环,就达到了设计要求。

电路设计图如下:四、实验分析:1、通过实验,进一步熟悉了触发器的原理。

2、能利用触发器进行简单的电路设计,如抢答器。

3、在进行实验设计时,查阅相关资料很重要。

在对所得资料进行自己的改进,就得到了自己的设计电路。

在设计抢答器时,我在资料上找到了用LED显示的设计电路,经过思考,我加进了数码管显示器,这样就使的显示结果更直观,更具有实用性。

74LS74资料

74LS74内部结构引脚图管脚逻辑图(双D触发器)、原理图和真值表以及波形图分析下面介绍一下74ls74,74ls74内部结构,74ls74引脚图,74ls74管脚图,74ls74逻辑图。

在TTL电路中,比较典型的d触发器电路有74ls74。

74ls74是一个边沿触发器数字电路器件,每个器件中包含两个相同的、相互独立的边沿触发d触发器电路。

(图点击,或下载后可放大)原理图和真值表以及波形图分析边沿D 触发器:负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G 6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G 5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

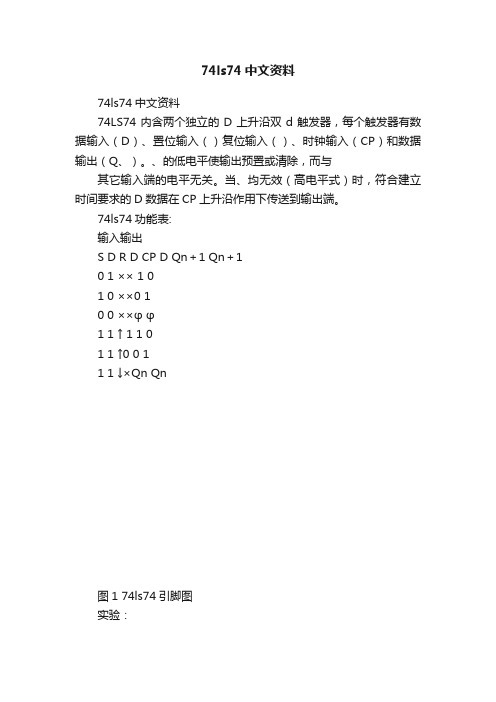

74ls74中文资料

74ls74中文资料74ls74中文资料74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:输入输出S D R D CP D Qn+1 Qn+10 1 ×× 1 01 0 ××0 10 0 ××φ φ1 1 ↑ 1 1 01 1 ↑0 0 11 1 ↓×Qn Qn图1 74ls74引脚图实验:用74LS74构成4位寄存器一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;(3) 先清零;(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

并入并出:D3D2D1D0=10111个CP脉冲Q3Q2Q1Q0=结论:并入串出D3D2D1D0=10114个CP脉冲Q3=结论串入并出D3=10114个CP脉冲Q3Q2Q1Q0=结论串入串出D3=10118个CP脉冲Q3=结论图274ls153芯片管脚图引脚逻辑功能以及封装2007年12月17日 23:53 本站原创作者:本站用户评论()关键字:74ls153管脚图逻辑功能图封装:74LS163引脚功能表及管脚定义图(带时序波形图)发布:2011-08-30 | 作者: | 来源: huangjiapeng| 查看:2620次 | 用户关注:定时器由与系统秒脉冲(由时钟脉冲产生器提供)同步的计数器构成,要求计数器在状态信号ST作用下,首先清零,然后在时钟脉冲上升沿作用下,计数器从零开始进行增1计数,向控制器提供模5的定时信号TY和模25的定时信号TL。

SN74LS74AD中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)JM38510/00205BCA OBSOLETE CDIP J14TBD Call TI Call TIJM38510/00205BDA OBSOLETE CFP W14TBD Call TI Call TIJM38510/00205BDA OBSOLETE CFP W14TBD Call TI Call TIJM38510/07101BCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCJM38510/07101BCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCJM38510/07101BDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NCJM38510/07101BDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NCJM38510/30102B2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NCJM38510/30102B2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NCJM38510/30102BCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCJM38510/30102BCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCJM38510/30102BDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NCJM38510/30102BDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NCJM38510/30102SCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCJM38510/30102SCA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCJM38510/30102SDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NCJM38510/30102SDA ACTIVE CFP W141TBD Call TI Level-NC-NC-NC SN5474J OBSOLETE CDIP J14TBD Call TI Call TISN5474J OBSOLETE CDIP J14TBD Call TI Call TISN54LS74AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN54LS74AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN54S74J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN54S74J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SN7474DR OBSOLETE SOIC D14TBD Call TI Call TISN7474DR OBSOLETE SOIC D14TBD Call TI Call TISN7474N OBSOLETE PDIP N14TBD Call TI Call TISN7474N OBSOLETE PDIP N14TBD Call TI Call TISN7474N3OBSOLETE PDIP N14TBD Call TI Call TISN7474N3OBSOLETE PDIP N14TBD Call TI Call TISN74LS74AD ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74AD ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADBR ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADBR ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADBRE4ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADBRE4ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS74ADE4ACTIVE SOIC D1450Green(RoHS&CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)no Sb/Br)SN74LS74ADR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ADRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LS74AJ OBSOLETE CDIP J14TBD Call TI Call TISN74LS74AJ OBSOLETE CDIP J14TBD Call TI Call TISN74LS74AN ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS74AN ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NC SN74LS74AN3OBSOLETE PDIP N14TBD Call TI Call TISN74LS74AN3OBSOLETE PDIP N14TBD Call TI Call TISN74LS74ANE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS74ANE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74LS74ANSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ANSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ANSRG4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74LS74ANSRG4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74S74N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74S74N3OBSOLETE PDIP N14TBD Call TI Call TIOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)SN74S74N3OBSOLETE PDIP N14TBD Call TI Call TISN74S74NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74S74NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74S74NSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74NSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74S74NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ5474J OBSOLETE CDIP J14TBD Call TI Call TISNJ5474J OBSOLETE CDIP J14TBD Call TI Call TISNJ5474W OBSOLETE CFP W14TBD Call TI Call TISNJ5474W OBSOLETE CFP W14TBD Call TI Call TI SNJ54LS74AFK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54LS74AFK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54LS74AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54LS74AJ ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54LS74AW ACTIVE CFP W141TBD Call TI Level-NC-NC-NC SNJ54LS74AW ACTIVE CFP W141TBD Call TI Level-NC-NC-NC SNJ54S74FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54S74FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NCSNJ54S74J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCSNJ54S74J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NCSNJ54S74W ACTIVE CFP W141TBD Call TI Level-NC-NC-NCSNJ54S74W ACTIVE CFP W141TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it isprovided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

74LS74触发器的原理及应用

74LS74触发器的原理及应用1. 概述74LS74是一种常见的触发器芯片,属于TTL(Transistor-Transistor Logic,双极型晶体管逻辑)系列。

它由两个D触发器组成,可以实现各种逻辑功能。

本文将介绍74LS74触发器的工作原理以及常见的应用场景。

2. 工作原理74LS74触发器的内部结构包含两个D触发器,每个D触发器有两个输入端(D和时钟)和两个输出端(Q和/ Q)。

D触发器采用正边沿触发方式,即在时钟上升沿进行数据更新。

74LS74的工作原理如下: - 当时钟上升沿到达时,输入信号D的值会被存储到D触发器的门级传输门内部。

- 当时钟上升沿到达时,存储在D触发器内部的值会根据触发器的类型进行更新。

- 更新之后的值会通过输出端Q和/ Q输出。

3. 应用场景74LS74触发器在数字电路中有广泛的应用。

以下是一些常见的应用场景:3.1 时序电路74LS74触发器可以用于时序电路中。

通过控制时钟脉冲的频率和输入信号的变化,可以实现多种时序逻辑功能,如计数器、频率分频器和触发器。

3.2 数据存储74LS74触发器可以作为数据存储元件使用。

通过将输入信号D和时钟信号连接到适当的输入端口,可以实现数据的存储和读取。

这种功能使得74LS74可以在计算机存储器和寄存器等应用领域中发挥重要作用。

3.3 状态机74LS74触发器可以用于构建状态机。

状态机是一种组合逻辑电路,可以根据当前的状态和输入信号来决定下一个状态和输出信号。

74LS74触发器可以用作状态机的存储单元,帮助实现复杂的逻辑功能和控制。

3.4 触发器串联多个74LS74触发器可以串联使用,从而扩展触发器的位宽和功能。

这种串联连接方式可以实现更高位数的计数器和存储器,同时也可以实现更复杂的逻辑功能。

4. 总结74LS74触发器是一种常见的数字电路元件,具有广泛的应用场景。

本文介绍了74LS74触发器的工作原理以及常见的应用场景,包括时序电路、数据存储、状态机和触发器串联等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

74ls74中文资料

时间:2010-06-04 16:32:22 来源:资料室作者:

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入

()复位输入()、时钟输入(CP)和数据输出(Q、)。

、的低电平使输出预

置或清除,而与其它输入端的电平无关。

当、均无效(高电平式)时,符合建立时间要求的D数据在CP上升沿作用下传送到输出端。

74ls74功能表:

图1 74ls74引脚图

实验:

用74LS74构成4位寄存器

一个D触发器可实现一位二进数的存储,因此应采用4个D触发器实现4位寄存器。

由于要实现移位寄存,4个D触发器之间应相互联接。

(1)首先在图2中完成相应的联线,构成可实现并入并出、串入串出、并入串出、串入并出的多功能移位寄存。

按图接好电路。

(2) D3 D2 D1 D0分别接逻辑开关,Q3 Q2 Q1 Q0接发光二极管;

(3) 先清零;

(4) 按下列要求,实现相应功能,观察结果,并描述工作过程。

并入并出:

使数据输入端D3D2D1D0=1011,给CP端输入一个正单脉冲,观察Q3Q2Q1Q0发光二极管的状态,、将结果填入表中。

并入串出:

使数据输入端D3D2D1D0=1011,给CP端输入4个正单脉冲,观察Q3端发光二极管的状态,将结果填入表6中。

串入并出:

使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲将D0端的4 个数据送入寄存器。

观察Q3Q2Q1Q0端发光二极管的状态,将结果填入表中。

串入串出:

使数据输入端D0分别为1011,同时通过给CP端输入正单脉冲,将D0端的4 个数据送入寄存器。

在CP端输完8个脉冲后,观察Q3端发光二极管的状态,将结果填入表2中。

图2。