verilog m序列发生器

m序列发生器的作用

m序列发生器的作用

m序列发生器是一种能够产生伪随机序列的电子设备或算法。

它的主要作用有:

1. 加密通信:m序列发生器可以用于生成加密密钥序列,用于对通信数据进行加密,保护通信内容的安全性。

2. 伪随机数生成:m序列发生器可以用于生成伪随机数序列,可以应用在密码学中的伪随机数生成算法、模拟实验、随机化算法等应用中。

3. 信号处理:m序列发生器可以用于产生具有特定性质的信号序列,如具有较好频谱特性的序列、跳频信号序列等,广泛应用于通信领域、雷达系统、无线电测量等各种信号处理应用中。

4. 探测器测试:m序列发生器可以用于对数字通信中的接收机进行性能测试,通过与已知正常输入进行比较,可以检测接收机的误码率、误比特率、误帧率等性能指标。

总之,m序列发生器的作用主要体现在加密通讯、伪随机数生成、信号处理和探测器测试等方面。

一次输出8bit_n4_m序列Simulink仿真Verilog实现

1.4阶m序列生成器一开始希望通过使用8个PN序列生成器并行实现,但是,每个生成器都不能得到后8个状态的值。

由于后面的8bit PN序列,通过一个clk不可能通过状态转换实现,所以,只能通过计算得到利用Matlab计算得到后8位PN码与初始状态的关系,得到一个输出生成矩阵,使用生成矩阵与初始状态相乘,即可得到8位PN码同时,计算得到生成第8位PN码时移位寄存器的状态,得到一个初始值生成矩阵,使用此矩阵与初始状态相乘,即可得到生成第8位PN码时移位寄存器的状态,从而为下一次迭代提供初始状态。

两个矩阵在PN码生成过程中保持不变,而初始状态得到不断更新,8位PN码不断输出。

clc; clear;n = 4; % 4 orderbit = zeros(9,n^2);bit(1,:) = [1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1];initial = [1 0 0 0];for i = 2:9% generate polynimial, 1 + x + x^4, ==========x + x^4,bit(i,:) = [ mod( bit(i-1,1:n)+bit(i-1,3*n+1:4*n), 2), bit(i-1,1:3*n)];endgenmatrix = bit(2:9,3*n+1:4*n) % generate matrix remain the samefor j = 1:1mseq = mod(genmatrix*initial', 2)% Update initialtemp = initial;for k = 1:ninitial(k) = mod( sum(bit(9,(k-1)*n+1:k*n)*temp'), 2);endend输出生成矩阵为:genmatrix =0 0 1 00 1 0 01 0 0 01 0 0 11 0 1 11 1 1 10 1 1 11 1 1 0初始状态值生成矩阵为:gm_init =1 1 0 11 0 1 00 1 0 11 1 1 0Verilog代码:`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 15:24:21 05/01/2012// Design Name:// Module Name: PNcode8bit//////////////////////////////////////////////////////////////////////////////////// module PNcode8bit(clk,rst,init,PNout);// PN code n = 4, f(x) = 1 + x + x^4// Output 8 bit per clkparameter order = 4;input clk;input rst;output [order-1 : 0] init;output [7 : 0] PNout;// Output use registerreg [7 : 0] PNout = 0;reg [order-1 : 0] init = 0;// Generate matrix of output, use memoryreg [order-1 : 0] gm_out [7 : 0];// Generate matrix of initial state, use memoryreg [order-1 : 0] gm_init [3 : 0];integer i, j;//////////////////////////////////////////// Memory initialization file read here, generate by Matlabinitialbegin$readmemb("gm_out.txt", gm_out, 7, 0);$readmemb("gm_init.txt", gm_init, 3, 0);end//////////////////////////////////////////always @ (posedge clk)if(rst == 1)beginPNout <= 8'b0;init <= 4'b1000;endelsebeginfor(i=0; i<8; i=i+1)PNout[i] <= (gm_out[i][3] & init[3]) ^ (gm_out[i][2] & init[2]) ^ (gm_out[i][1] & init[1]) ^ (gm_out[i][0] & init[0]);for(j=0; j<4; j=j+1)init[j] <= (gm_init[j][0] & init[0]) ^ (gm_init[j][1] & init[1]) ^ (gm_init[j][2] & init[2]) ^ (gm_init[j][3] & init[3]);endendmodule说明:1.使用readmemb实现存储器数据的初始化,读取二进制内容,因为两个生成矩阵会比较大$readmemb("gm_out.txt", gm_out, 7, 0);"gm_out.txt"为读取的文件,gm_out为存放的存储器名字,7, 0为起始地址和结束地址,最好注明地址范围,不注明好像不太确定2.按位与、按位异或实现二进制矩阵乘法第一个for是输出生成矩阵(8x4)与初始值(4x1)相乘,得到8bit PN码的输出第二个for是初始状态值生成矩阵(4x4)与初始值(4x1)相乘,得到新的初始值gm_out.txt内容:没有空格00100100100010011011111101111110gm_init.txt内容:没有空格1101101001011110测试文件代码:`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 16:27:38 05/01/2012// Design Name: PNcode8bit// Module Name: E:/me/CAST/Project/FPGAcomm/PNcode8bit/PNcode8bit_tb.v// Project Name: PNcode8bit////////////////////////////////////////////////////////////////////////////////// module PNcode8bit_tb;// Inputsreg clk;reg rst;// Outputswire [3:0] init;wire [7:0] PNout;// Instantiate the Unit Under Test (UUT)PNcode8bit uut (.clk(clk),.rst(rst),.init(init),.PNout(PNout));initial begin// Initialize Inputsclk = 0;rst = 1;// Wait 100 ns for global reset to finish#100;rst = 0;// Add stimulus hereendalways beginforever #10 clk = !clk;endendmoduleModelSim仿真结果局部放大图,绿色竖线为周期间隔,一个周期的PN码为:001111010110010。

基于VHDL可编程m序列发生器的设计及应用

m 序列 广泛应 用 于数字基 带信 号进行 加扰 , 改 善 数字 序列 的位 定 时质 量 与 帧 同步 和 自适 应 时 域 均 衡性 能 , 同时 也是 构 造 平衡 G L O D码 的基 础 . 目 前 , 序 列产 生 电路 的实 现方 法主要 有 3种 : i n 1 )门电路实 现 . 方法设 计简 单 , 随移位 寄 该 但 存 器级 数 的增长 , 电路 装 调 困难 , 占用 的 印制 板 且

计输 入 、 速处 理和器 件编 程 引. 快

线 性反 馈移 位寄存 器 的特征 多项 式 :

摘要 : 介绍 了在 实 际教 学 中应 用 V L设计 出一 种能产 生 1 序 列数 字信 号 的发 生 器. HD T I 该序 列发 生 器具 有序 列长 度 和反 馈 连 接 设 置 , 能产 生 多种 i 列 波形 的 特 点. 软 件 上 采 用 Ata公 司 的 n序 在 lr e

种 序列 . 在今 天 的数 字 信 号 的传 输 中 , 发送 机往

往要 加扰码 器 , 对应 的接 收 端要 加 解 扰器 , n 相 而 l

序列 属 于伪 噪声 序列 和 伪 随 机序 列 , 容 易产 生 、 它

规律 性强 、 很 好 的 自相 关 性 和 较 好 的互 相 关 特 有

一

2 S 程实现 . )D P编 该方 法专 业性 过强 , 适合 不

实际教 学 中应 用. 3 H L与 C L )V D P D实现 . 由于 C L P D的高 集成

度, 而且 V L语 言 编程 较 为 方便 , 可 以大 大减 HD 故

少 电路 的装调 的 困难.

V D H L已成 为 电子工 程 领 域 事实 上 的 通 用硬

基于FPGA的m序列信号发生器设计

基于FPGA的m序列信号发生器设计摘要:m序列是一种伪随机序列(PN码),广泛用于数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域。

基于FPGA与Verilog硬件描述语言设计井实现了一种数据率按步进可调、低数据误码率、反馈多项式为的m序列信号发生器。

系统时钟为20MHz,m序列信号发生器输出的数据率为20~100 kbps,通过2个按键实现20 kbps步进可调与系统复位,输出误码率小于1%。

m序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种伪随机序列。

是由移位寄存器、反馈抽头及模2加法器组成。

m序列一旦反馈多项式及移位寄存器初值给定,则就是可以预先确定并且可以重复实现的序列,该特点使得m序列在数据白噪化、去白噪化、数据传输加密、解密等通信、控制领域使用广泛。

因此,深入学习研究m序列具有重要的实际意义。

1 m序列信号发生器的组成基于FPGA的m序列信号发生器硬件结构极其简单,仅需两个独立按键(一个是复位按键与另一个控制数据率切换按键)、一个48 MHz 的用于提供系统时钟有源晶振、系统电源、一块配置芯片、几个简单的电阻与电容即可实现。

按键去抖动、按键复位、按键切换数据率、时钟分频等功能均在FPGA内部编程实现。

2 m序列信号发生器的关键设计本文中m序列信号发生器的反馈多项式为。

其反馈及移位寄存器的关系图如图2所示。

从本设计中的反馈及移位寄存器的关系图可以看出,一个时钟周期,移位寄存器右移一位,最高位输入为x0、x2、x3、x4及x8的异或(模2相加)。

m序列的输出是移位寄存器的最低位。

图2所示的关系是m序列呈现为随机性、周期性的根本原因。

为了满足信号发生器输出数据率20 kbps的步进通过按键可调,则生成按步进20 kbps可调的时钟是实现该功能的关键。

当按键发生,时钟的输出频率加20 kbps。

在实际电路中,按键会有很大抖动,对系统会造成很大的不稳定性,因此,必须想办法减小这样的不利影响。

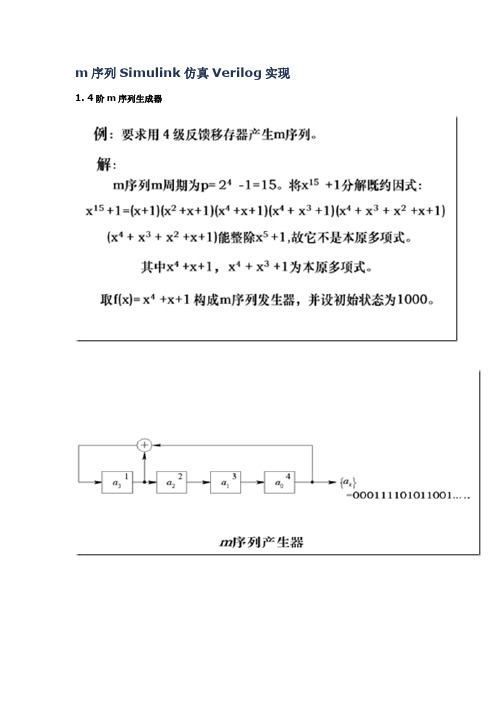

m序列Simulink仿真实现

m序列Simulink仿真Verilog实现1. 4阶m序列生成器Simulink模型如下:其中,可以在Unit Delay属性中设置初始值为1000,由于Unit Delay输出为double,所以要将其转为Boolean以便进行模二加运算,使用XOR实现。

下面分别是最后一级和所有级的输出波形,可以看出,与上面的是一致的。

Verilog实现`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 11:02:17 05/01/2012// Design Name:// Module Name: PNcode// Project Name:////////////////////////////////////////////////////////////////////////////////// module PNcode(clk,rst,PNstate,PNout);input clk;input rst;output PNstate;output PNout;// PN code n = 4, f(x) = 1 + x + x^4parameter order = 4;reg PNout = 0;reg [order-1 : 0] PNstate = 0;always @ (posedge clk)if(rst == 1)beginPNout <= 0;PNstate <= 4'b1000; // PN seed = b1000endelsebeginPNout <= PNstate[0];PNstate <= {PNstate[3]+PNstate[0], PNstate[3:1]};endendmodule测试文件:`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 14:37:43 05/01/2012// Design Name: PNcode// Module Name: E:/me/CAST/Project/FPGAcomm/PNcode/PNcode_tb.v// Project Name: PNcode////////////////////////////////////////////////////////////////////////////////// module PNcode_tb;// Inputsreg clk;reg rst;// Outputswire [3:0] PNstate;wire PNout;// Instantiate the Unit Under Test (UUT)PNcode uut (.clk(clk),.rst(rst),.PNstate(PNstate),.PNout(PNout));initial begin// Initialize Inputsclk = 0;rst = 1;// Wait 100 ns for global reset to finish#100;rst = 0;// Add stimulus hereendalways beginforever #10 clk = !clk;endendmoduleclk使用一个单独的always模块输出序列:0 0 0 1 1 1 1 0 1 0 1 1 0 0 1 0 0 0 1 2. 8阶m序列生成器,初始全为11。

基于FPGA的VHDL语言m序列生成详解+源码

说明可控m序列产生器我分成四个小模块来做,M,M1,M2,M3分别对应为:m序列产生器、控制器、码长选择器、码速率选择器。

一、M: m序列产生器这是该设计的核心部分,原理就是设计一个通用m序列产生子单元,然后由外部选择器来写入码型,码长等参数,加以循环可连接成任意长度的m序列产生器,其子单元结构如下:如上图,若N=15,就有15个这样的子单元首尾相接。

注意:开头和结尾的两个子单元会有所不同,因为首单元需要输入初值,尾单元要进行直通反馈,在程序里请多留意。

图中,主要部件是一个D触发器,Q(N+1)为上一级输出;Q(N)既是本级输出;CP为选择后的时钟脉冲;B(N)为本级参数选择控制;A(N)受控于B(N),决定本级输出Q(N)是否反馈(B(N)为1时反馈);C(N)为本级反馈;C(N-1)为下一级反馈。

具体原理参看m序列组成结构。

此外,本程序还加入了EN(发送控制)、RN(首单元置数)、SEL1(码长选择,即N的选择,N=2-15)、SEL2(码型选择,即正逆码选择)四个控制端,可满足设计要求。

OP为码输出端。

二、M1:控制器控制器主要是将外部的序列发送控制信号STA转换为EN和RN 两个控制信号。

其中,EN与STA的波形基本一致,只是它与CP进行了同步处理;RN在EN为‘1’的头一个脉冲周期里置高电平,以达到为序列发生器的首端置数的目的。

如果不清楚的话可以看一下它的模拟波形。

(注意:STA要采用自锁定开关,高电平有效)三、M2:码长选择序列的码长选择既是N值的选择,码长=2**N-1。

核心就是一个计数器,可从2计到15。

按一次PUSH就可以自动加一(注意:按键建议采用自弹跳按键,如过需要软件清除按键震颤的话,我再做发给你),没有0,1两个状态。

如果需要的话还可以扩展7段数码管的接口,以显示N值。

四、M3:码速率选择器码的传输速率是靠CP来控制的,CP的频率就等于码元速率。

这段程序包含一个倍频器,一个5分频的分频器,可把5MHZ的脉冲源CLK扩展成1MHZ和10MHZ。

课程设计论文基于FPGA的m序列发生器

基于FPGA的m序列发生器摘要m序列广泛应用于密码学、通信、雷达、导航等多个领域,本文提出了一种基于FPGA的伪随机序列产生方法,应用移位寄存器理论从序列的本原多项式出发,获得产生该序列的移位寄存器反馈逻辑式,结合FPGA芯片结构特点,在序列算法实现中采用元件例化语句。

算法运用VHDL语言编程,以A1tera的QuartusⅡ软件为开发平台,给出了序列的仿真波形。

序列的统计特性分析表明:该方法产生的序列符合m序列的伪随机特性,验证了算法的正确性。

关键词:m序列;移位寄存器理论;VHDL语言目录摘要 (I)1 m序列 (1)1.1 理论基础 (1)1.1.1 线性反馈移位寄存器 (2)2 m序列的性质 (5)2.1 均衡性 (5)2.2游程特性 (5)2.4 自相关特性 (5)2.5 伪噪声特性 (7)3 m序列的应用 (9)3.1 扩展频谱通信 (9)3.2 通信加密 (10)4 开发工具简介 (11)4.1 Quartus II简介 (11)4.2 数字系统开发流程 (12)4.3 FPGA简介 (12)5 m序列生成器仿真分析 (16)5.1 反馈系数表存储器设计 (16)5.2 移位存储器设计 (17)5.3 仿真分析 (18)参考文献 (20)附录 (22)1 m序列m序列是伪随机序列的一种 ,结构简单 ,实现方便。

在现代工程实践中 , m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。

例如 , 在连续波雷达中可用作测距信号 , 在遥控系统中可用作遥控信号 , 在多址通信中可用作地址信号 , 在数字通信中可用作群同步信号 ,还可用作噪声源及在保密通信中起加密作用等。

伪噪声发生器在测距、通信等领域的应用日益受到人们重视。

目前,m序列产生实现方法主要有3种:(1)门电路实现该方法设计简单,但随移位寄存器级数的增长,电路装调困难,且占用的印制板面积较大。

(2)DSP编程实现该方法专业性过强,不适合一般用户。

M序列发生器设计实验指导书

M序列发生器设计实验一、实验原理:M序列码也称伪随机序列码,其主要特点是:(1)每个周期中,“1”码出现2n-1次,“0”码出现2n-1次,即0、1出现概率几乎相等。

(2)序列中连1的数目是n,连0的数目是n-1。

(3)分布无规律,具有与白噪声相似的伪随机特性。

由于具有这些特点,m序列码在通信、雷达、系统可靠性测试等方面获得了广泛地应用。

m序列码发生器是一种反馈移位型结构的电路,它由n位移位寄存器加异或反馈网络组成,其序列长度M=2n-1,只有一个多余状态即全0状态,所以称为最大线性序列码发生器。

由于其结构已定型,且反馈函数和连接形式都有一定的规律,因此利用查表的方式就设计出m 序列码。

列出部分m序列码的反馈函数F和移存器位数n的对应关系。

如果给定一个序列信号长度M,则根据M=2n-1求出n,由n查表便可以得到相应的反馈函数F。

二、基于DSP Builder 的设计M 序列发生器可由线性反馈寄存器(Linear Feedback Shift Registers,LFSR )来产生,如图1所示。

图1 线性反馈移位寄存器的构成其特征多项式可表示为:∑==ni i i x C x F 1)(在图1中涉及的乘法和加法都是指模二运算的乘法和加法,即逻辑与和逻辑或。

要产生最长的线性反馈移位寄存器序列的n 级移位寄存器,其特征多项式必须是n 次本原多项式。

例如n=5,可以生成M 序列的5级LFSR 的特征多项式,即:125++x x ,此式可生成的M 序列的周期为:125-。

下面以M 序列发生器模型125++x x 为例,利用DSP Builder 构建一个伪随机序列发生器。

图2显示了上式的DSP Builder 模型表述,这里采用相连的延时单元级作为移位寄存器,用异或(XOR )完成模二加运算,输出为Output 。

图2 M 序列发生器模型但应注意,图2所示的电路一般无法正常工作。

这是由于在DSP Builder 默认的延时单元在开始工作时,存储内容为0,而对于M 序列来说,起始序列为全0,那么根据多项式,输出序列也将为0.全0序列不是正常的M 序列。